4 Сл

00 СЛ

() 00

Изобретение относится к вычислительной технике и может быть использовано при построении устройств межмашинного обмена и обмена с периферийными модулями.

Целью изобретения является упрощение преобразователя и повьшение его бы ст р од ей ст ВИЯ о

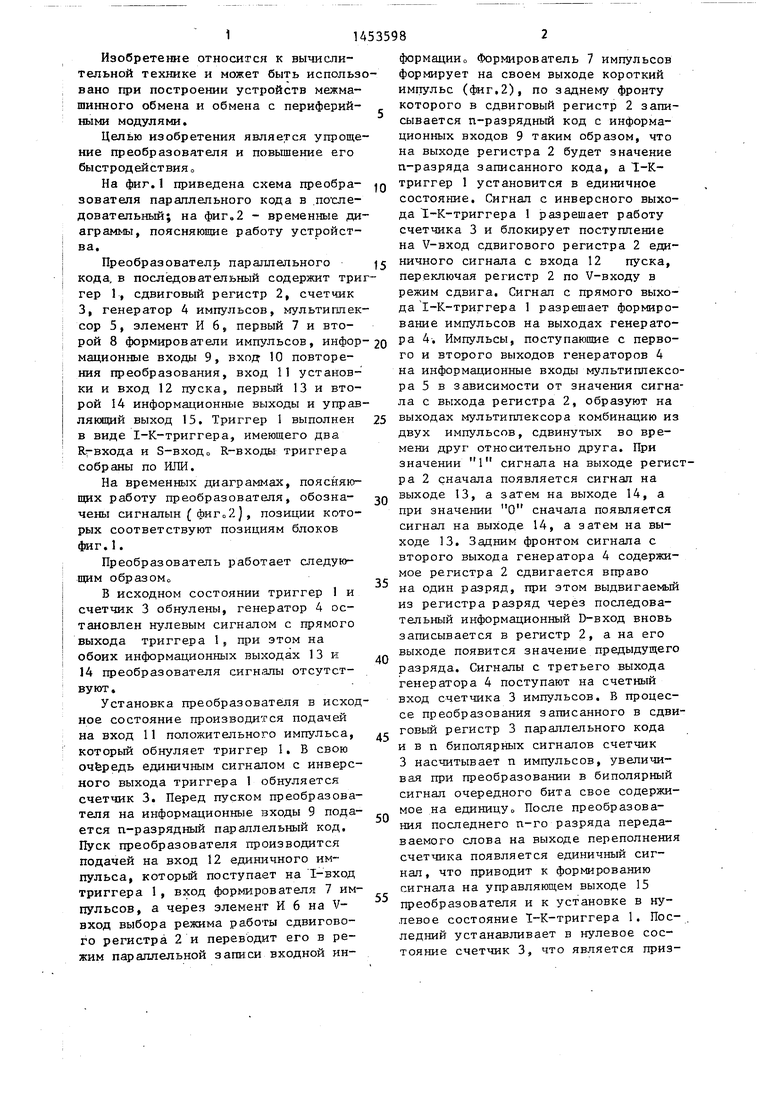

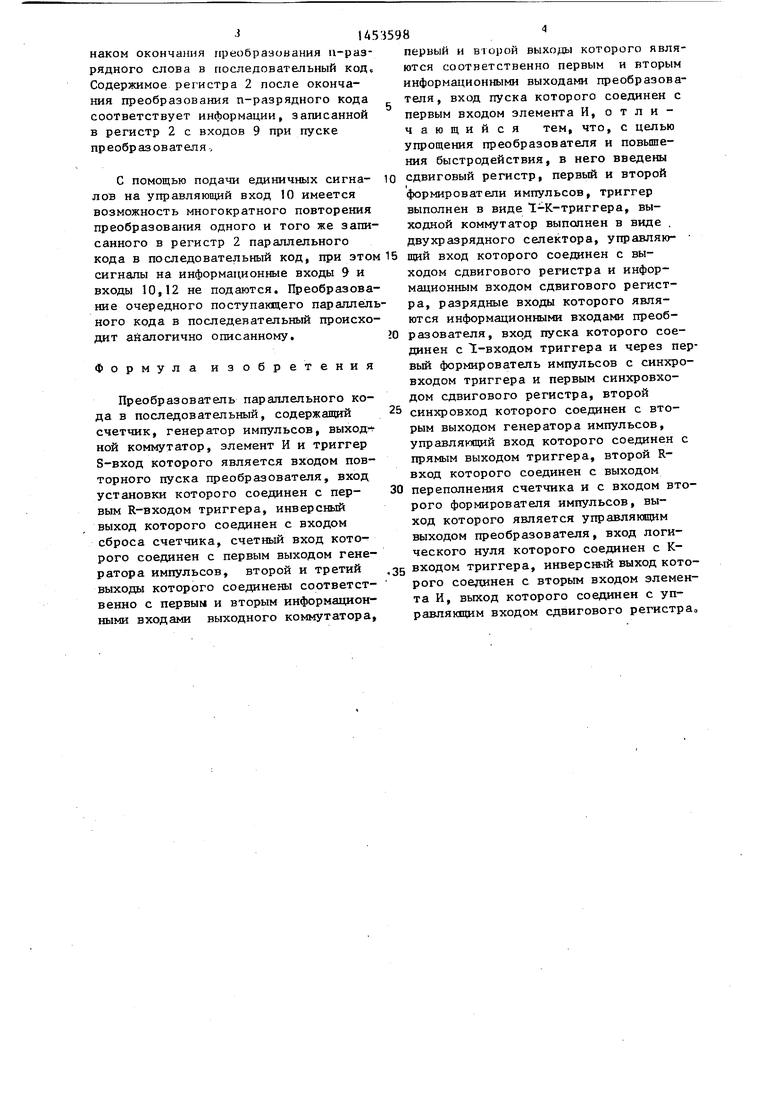

На фиг.1 приведена схема преобра- д зователя параллельного кода в .по сле- довательный; на фиг«2 - временные диаграммы, поясняющие работу устройства.

Преобразователь пapaJшeльнoгo 5

кода, в последовательный содержит триггер 1, сдвиговый регистр 2, счетчик 3, генератор 4 импульсов, мультиплексор 5, элемент И 6, первый 7 и втоформациио Формирователь 7 импульсов формирует на своем выходе короткий импульс (фиг,2), по заднему фронту которого в сдвиговый регистр 2 записывается п-разрядный код с информационных входов 9 таким образом, что на выходе регистра 2 будет значение п-разряда записанного кода, а 1-К- триггер 1 установится в единичное состояние. Сигнал с инверсного выхода 1-К-триггера 1 разрешает работу счетчика 3 и блокирует поступление на V-вход сдвигового регистра 2 единичного сигнала с входа 12 пуска, переключая регистр 2 по V-входу в режим сдвига. Сигнал с прямого выхода 1-К-триггера 1 разрешает формирование импульсов на выходах генераторой 8 формирователи импульсов, инфор-20 Р Импульсы, поступающие с первого и второго выходов генераторов 4 на информационные входы мультиплексора 5 в зависимости от значения сигнала с выхода регистра 2, образуют на выходах мультиплексора комбинацию из двух импульсов, сдвинутых во времени друг относительно друга. При значении 1 сигнала на выходе регист ра 2 сначала появляется сигнал на выходе 13, а затем на выходе 14, а при значении О сначала появляется сигнал на выходе 14, а затем на выходе 13. Задним фронтом сигнала с второго выхода генератора 4 содержимое регистра 2 сдвигается вправо на один разряд, при этом выдвигаемый из регистра разряд через последовательный информационный D-БХОД вновь записывается в регистр 2, а на его выходе появится значение предыдущего разряда. Сигналы с третьего выхода генератора 4 поступают на счетный вход счетчика 3 импульсов. В процессе преобразования записанного в сдвиговый регистр 3 параллельного кода и в п биполярных сигналов счетчик 3 насчитывает п импульсов, увеличивая при преобразовании в биполярный сигнал очередного бита свое содержимое на единицу После преобразования последнего п-го разряда передаваемого слова на выходе переполнения счетчика появляется единичный сигнал, что приводит к формированию сигнала на управляющем выходе 15 преобразователя и к установке в нулевое состояние 1-К-триггера 1. Пос- ледний устанавливает в нулевое состояние счетчик 3, что является призмационные входы 9, вход 10 повторения преобразования, вход 11 установки и вход 12 пуска, первый 13 и второй 14 информационные выходы и управ ляюшрнй выход 15. Триггер 1 выполнен в виде 1-К-триггера, имеющего два R-входа и S-входо R-входы триггера собраны по ИЛИ.

На временных диаграммах, поясняющих работу преобразователя, обозна- чены сигналын ( фиго2J, позиции которых соответствуют позициям блоков фиг.1.

Преобразователь работает следующим образомо

В исходном состоянии триггер 1 и счетчик 3 обнулены, генератор 4 остановлен нулевым сигналом с прямого выхода триггера 1, при этом на обоих информационных выходах 13 и

14 преобразователя сигн,злы отсутствуют .

Установка преобразователя в исходное состояние производится подачеЛ на вход 11 положительного импульса, который обнуляет триггер 1. В свою очередь единичным сигналом с инверсного выхода триггера 1 обнуляется счетчик 3. Перед пуском преобразователя на информационные входы 9 подается п-разрядный параллельный код. Пуск преобразователя производится подачей на вход 12 единичного импульса, которьй поступает на 1-вход триггера 1, вход формирователя 7 импульсов, а через элемент И 6 на V- вход выбора режима работы сдвигового регистра 2 и переводит его в режим параллельной запи:си входной ин

формациио Формирователь 7 импульсов формирует на своем выходе короткий импульс (фиг,2), по заднему фронту которого в сдвиговый регистр 2 записывается п-разрядный код с информационных входов 9 таким образом, что на выходе регистра 2 будет значение п-разряда записанного кода, а 1-К- триггер 1 установится в единичное состояние. Сигнал с инверсного выхода 1-К-триггера 1 разрешает работу счетчика 3 и блокирует поступление на V-вход сдвигового регистра 2 единичного сигнала с входа 12 пуска, переключая регистр 2 по V-входу в режим сдвига. Сигнал с прямого выхода 1-К-триггера 1 разрешает формирование импульсов на выходах генерато0 Р Импульсы, поступающие с перво5

0

с

Q

5

0

5

го и второго выходов генераторов 4 на информационные входы мультиплексора 5 в зависимости от значения сигнала с выхода регистра 2, образуют на выходах мультиплексора комбинацию из двух импульсов, сдвинутых во времени друг относительно друга. При значении 1 сигнала на выходе регистра 2 сначала появляется сигнал на выходе 13, а затем на выходе 14, а при значении О сначала появляется сигнал на выходе 14, а затем на выходе 13. Задним фронтом сигнала с второго выхода генератора 4 содержимое регистра 2 сдвигается вправо на один разряд, при этом выдвигаемый из регистра разряд через последовательный информационный D-БХОД вновь записывается в регистр 2, а на его выходе появится значение предыдущего разряда. Сигналы с третьего выхода генератора 4 поступают на счетный вход счетчика 3 импульсов. В процессе преобразования записанного в сдвиговый регистр 3 параллельного кода и в п биполярных сигналов счетчик 3 насчитывает п импульсов, увеличивая при преобразовании в биполярный сигнал очередного бита свое содержимое на единицу После преобразования последнего п-го разряда передаваемого слова на выходе переполнения счетчика появляется единичный сигнал, что приводит к формированию сигнала на управляющем выходе 15 преобразователя и к установке в нулевое состояние 1-К-триггера 1. Пос- . ледний устанавливает в нулевое состояние счетчик 3, что является приз 145

наком окончания преобразования п-раз- рядного слова в последовательный код. Содержимое регистра 2 после окончания преобразования п-разрядного кода соответствует информации, записанной в регистр 2 с входов 9 при пуске преобразователя,

С помощью подачи единичных сигналов на управляющий вход 10 имеется возможность многократного повторения преобразования одного и того же запи- саиного в регистр 2 параллельного кода в последовательный код, при этом сигналы на информационные входы 9 и входы 10,12 не подаются. Преобразование очередного поступающего параллель ного кода в последевательный происходит аналогично описанному.

Формула изобретения

Преобразователь параллельного кода в последовательный, содержащий счетчик, генератор импульсов, выход- ной коммутатор, элемент И и триггер S-вход которого является входом повторного пуска преобразователя, вход установки которого соединен с первым R-входом триггера, инверсный выход которого соединен с входом сброса счетчика, счетный вход которого соединен с первым выходом генератора импульсов, второй и третий выходы которого соединены соответственно с первым и вторым информационными входами выходного коммутатора,

598

первый и второй выходы которого являются соответственно первым и вторым информационными выходами преобразователя, вход пуска которого соединен с первым входом элемента И, отличающийся тем, что, с целью упрощения преобразователя и повьппе- ния быстродействия, в него введены 0 сдвиговый регистр, первый и второй формирователи импульсов, триггер выполнен в виде 1-К-триггера, выходной коммутатор выполнен в виде , двухразрядного селектора, управляю- 5 щий вход которого соединен с выходом сдвигового регистра и информационным входом сдвигового регистра, разрядные входы которого являются информационными входами преоб- 10 разователя, вход пуска которого соединен с Т-входом триггера и через первый формирователь импульсов с синхро- входом триггера и первым синхровхо- дом сдвигового регистра, второй 25 синхровход которого соединен с вторым выходом генератора импульсов, управляющий вход которого соединен с прямым выходом триггера, второй R- вход которого соединен с выходом 30 переполнения счетчика и с входом второго формирователя импульсов, выход которого является управляющим выходом преобразователя, вход логического нуля которого соединен с К- ,35 входом триггера, инверсный выход которого соединен с вторым входом элемента И, выход которого соединен с управляющим входом сдвигового регистра.

Фиг,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1987 |

|

SU1444814A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Преобразователь последовательного кода в параллельный | 1987 |

|

SU1418911A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1989 |

|

SU1709526A1 |

| ПРЕОБРАЗОВАТЕЛЬ КОДА | 2004 |

|

RU2259009C1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к вычислительной технике и может быть использовано в устройствах межмашинного обмена и обмена с периферийными модулями. Целью изобретения является упрощение преобразователя и повышение его быстродействия. Поставленная цель достигается тем, что в преобразователь, содержащий счет- Чик 3, генератор 4 импульсов, выходной коммутатор 5, элемент И 6, дополнительно введены два формирователя импульсов 8 и 9, сдвиговый регистр 2, причем триггер 1 выполнен в виде 1-К-триггера на выходной коммутатор в виде двухразрядного селектора. 2 ил.

Редактор Н.Гунько

Составитель М.Аршавский

Техред М.Ходанич

Заказ 7301/55

Тираж 879

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

----.------ -.,- -,,-. - - «. - - -. --- - - - -. - - - -.--- - - - - - - -- - - - --, - Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М.Максимишинец

Подписное

| Преобразователь параллельного кода в последовательный | 1985 |

|

SU1282337A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Преобразователь параллельного кода в последовательный | 1984 |

|

SU1243097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-01-23—Публикация

1987-04-20—Подача