кГ,П

vi со VI о

О О

Изобретение относится к электротехнике и предназначено для использования при реализации вторичных источников электропитания, в частности в регуляторах и стабилизаторах постоянного напряжения.

Известен способ управления многоячейковым преобразователем постоянного напряжения, силовая часть которого выполнена на преобразовательных модулях с раз- личными выходными напряжениями, заключающийся в формировании сигналов управления на включение каждого преобразовательного модуля в течение заданного промежутка времени.

Недостатком известного способа является низкая надежность преобразователя, обусловленная сложностью резервирования преобразовательных модулей. Кроме того, способ обладает узкими функциональными возможностями по регулированию выходного напряжения.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является способ регулирования выходного напряжения преобразователя постоянного напряжения, выполненного на N идентичных ячейках, управление которыми выполняют со взаимным фазовым сдвигом по времени Т и периодом NT, формируя на выходе каждой ячейки напряжение длительностью М, затем суммируют выходные напряжения ячеек и подают на выходные выводы преобразователя.

Использование данного способа расширяет возможности регулирования выходного напряжения и повышает надежность преобразователя. Однако возрастают его габариты и масса, обусловленные установкой мощного выходного фильтра, необходимого для сглаживания пульсаций выходного напряжения.

Цель изобретения -уменьшение массы и габаритов преобразователя.

Поставленная цель достигается тем, что в способе регулирования выходного напряжения преобразователя постоянного напряжения, выполненного на N идентичных ячейках, управление которыми выполняют со взаимным фазовым сдвигом по времени Т и периодом NT, формируя на выходе каждой ячейки напряжение длительностью М, затем суммируют выходные напряжения ячеек и подают на выходные выводы преобразователя, указанную длительность М выбирают кратной Т в диапазоне от Т до T(N-1).

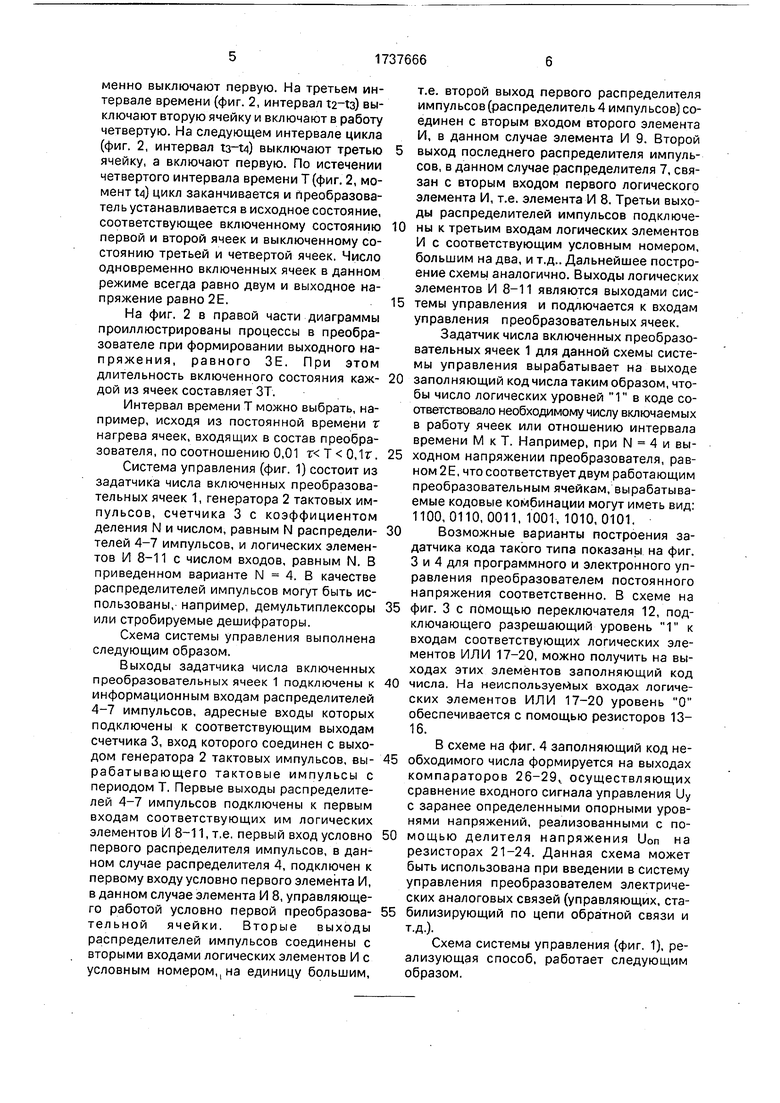

На фиг. 1 представлена функциональная схема одного из вариантов системы управления многоячейковым преобразователем постоянного напряжения, реализующим предлагаемый способ; на фиг. 2 - временные диаграммы сигналов в системе управления; на фиг. 3 и 4 - варианты построения задатчиков кода включенного

5 состояния ячеек преобразователя.

Способ реализуется следующим образом.

В преобразователе постоянного напряжения, состоящем из N идентичных ячеек,

0 которые соединяются между собой по входу параллельно,а по входу - последовательно, управление ячейками осуществляют со взаимным фазовым сдвигом по времени Т и периодом NT. При этом длительность управ5 ля ющего сигнала, а соответствен но и выходного напряжения ячеек выполняют равной М, причем длительность М выбирают кратной Т в диапазоне от Т до T(N-1). Для фор- мирования выходного напряжения

0 преобразователя суммируют выходные напряжения всех ячеек.

Пример. Преобразователь постоянного напряжения состоит из четырех ячеек, соединенных по входу параллельно, а по

5 выходу - последовательно, и выполняет функции регулятора постоянного напряжения. Следовательно, выходное напряжение преобразователя может принимать значения в диапазоне 0-4Е, где Е - выходное

0 напряжение одной ячейки. Предположим, что выходное напряжение преобразователя должно быть 2Е. Такого состояния можно достичь несколькими путями. Во-первых, можно включить в работу все четыре ячейки

5 одновременно и, управляя ими в широтно- модулированном режиме, обеспечить на выходе среднее значение выходного напряжения, равное 2Е. Это требует установки на выходе ячеек значительных фильт0 ров, что увеличивает габариты и массу преобразователя. Во-вторых, можно включить на постоянную работу две ячейки преобразователя, отключив остальные. Это также обеспечит на выходе напряжение 2Е.

5 При этом следует учитывать, что все ячейки должны выполняться на максимальную мощность, что также ведет к увеличению габаритов и массы преобразователя.

В соответствии с предлагаемым спосо0 бом управление ячейками осуществляют со сдвигом по времени Т и периодом NT, формируя на выходе каждой ячейки напряжение длительностью М. Затем аналогичным образом суммируют напряжение всех ячеек.

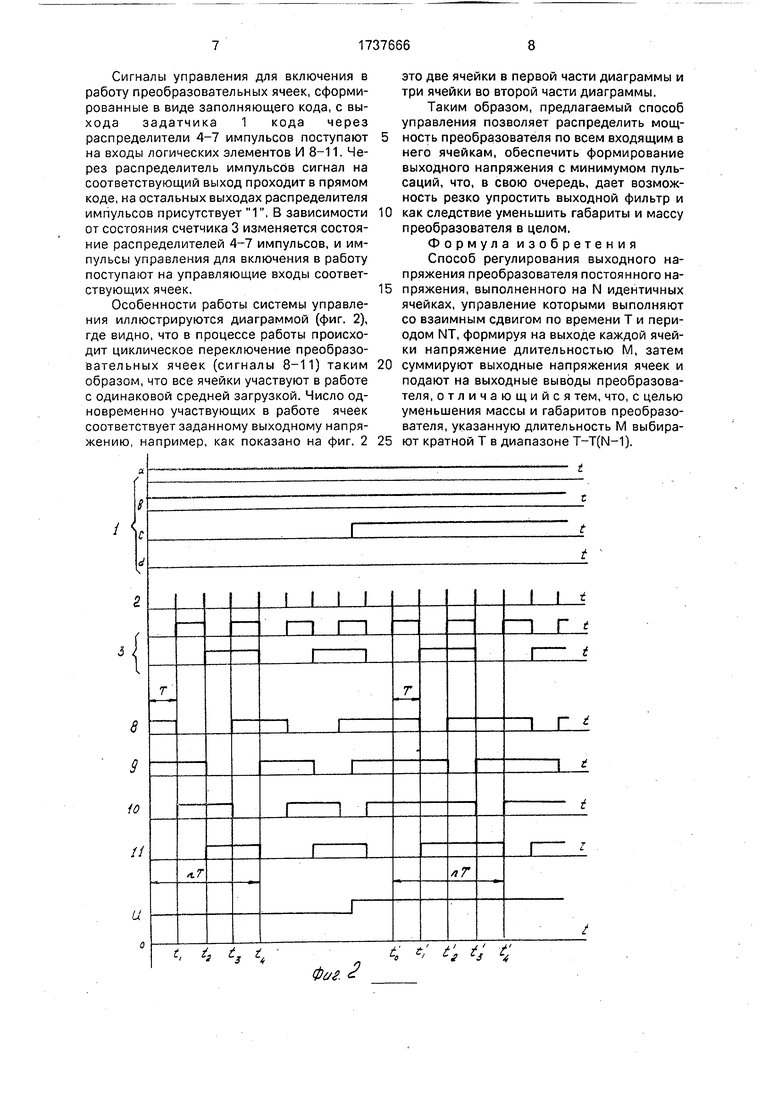

5 Например, в данном конкретном случае в течение определенного промежутка времени Т включают в работу первую и вторую ячейку (фиг. 2, интервал ). На втором интервале времени Т (фиг. 2, интервал )

в работу включают третью ячейку и одновременно выключают первую. На третьем интервале времени (фиг. 2, интервал t2-ta) выключают вторую ячейку и включают в работу четвертую. На следующем интервале цикла (фиг. 2, интервал t3-t4) выключают третью ячейку, а включают первую. По истечении четвертого интервала времени Т (фиг. 2, момент) цикл заканчивается и преобразователь устанавливается в исходное состояние, соответствующее включенному состоянию первой и второй ячеек и выключенному состоянию третьей и четвертой ячеек. Число одновременно включенных ячеек в данном режиме всегда равно двум и выходное напряжение равно 2Е.

На фиг. 2 в правой части диаграммы проиллюстрированы процессы в преобразователе при формировании выходного на- пряжения, равного ЗЕ. При этом длительность включенного состояния каж- дои из ячеек составляет ЗТ.

Интервал времени Т можно выбрать, например, исходя из постоянной времени т нагрева ячеек, входящих в состав преобразователя, по соотношению 0,01 ,1г.

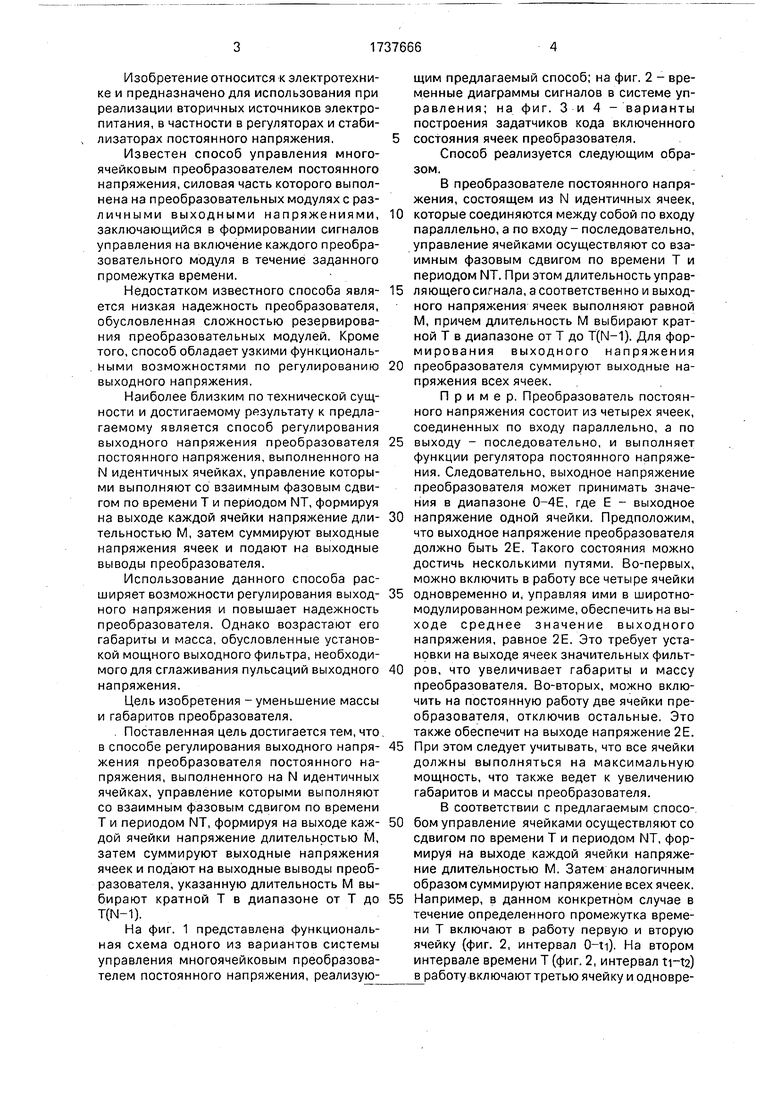

Система управления (фиг. 1) состоит из задатчика числа включенных преобразовательных ячеек 1, генератора 2 тактовых импульсов, счетчика 3 с коэффициентом деления N и числом, равным N распредели- телей 4-7 импульсов, и логических элементов И 8-11 с числом входов, равным N. В приведенном варианте N 4. В качестве распределителей импульсов могут быть использованы, например, демультиплексоры или стробируемые дешифраторы.

Схема системы управления выполнена следующим образом.

Выходы задатчика числа включенных преобразовательных ячеек 1 подключены к информационным входам распределителей 4-7 импульсов, адресные входы которых подключены к соответствующим выходам счетчика 3, вход которого соединен с выходом генератора 2 тактовых импульсов, вы- рабатывающего тактовые импульсы с периодом Т. Первые выходы распределителей 4-7 импульсов подключены к первым входам соответствующих им логических элементов И 8-11, т.е. первый вход условно первого распределителя импульсов, в данном случае распределителя 4, подключен к первому входу условно первого элемента И, в данном случае элемента И 8, управляющего работой условно первой преобразова- тельной ячейки. Вторые выходы распределителей импульсов соединены с вторыми входами логических элементов И с условным номером,, на единицу большим,

т.е. второй выход первого распределителя импульсов (распределитель 4 импульсов) соединен с вторым входом второго элемента И, в данном случае элемента И 9. Второй выход последнего распределителя импульсов, в данном случае распределителя 7, связан с вторым входом первого логического элемента И, т.е. элемента И 8. Третьи выходы распределителей импульсов подключены к третьим входам логических элементов И с соответствующим условным номером, большим на два, и т.д.. Дальнейшее построение схемы аналогично. Выходы логических элементов И 8-11 являются выходами системы управления и подлючается к входам управления преобразовательных ячеек.

Задатчик числа включенных преобразовательных ячеек 1 для данной схемы системы управления вырабатывает на выходе заполняющий код числа таким образом, чтобы число логических уровней 1 в коде соответствовало необходимому числу включаемых в работу ячеек или отношению интервала времени М к Т. Например, при N 4 и выходном напряжении преобразователя, равном 2Е, что соответствует двум работающим преобразовательным ячейкам, вырабатываемые кодовые комбинации могут иметь вид: 1100, 0110, 0011, 1001. 1010, 0101.

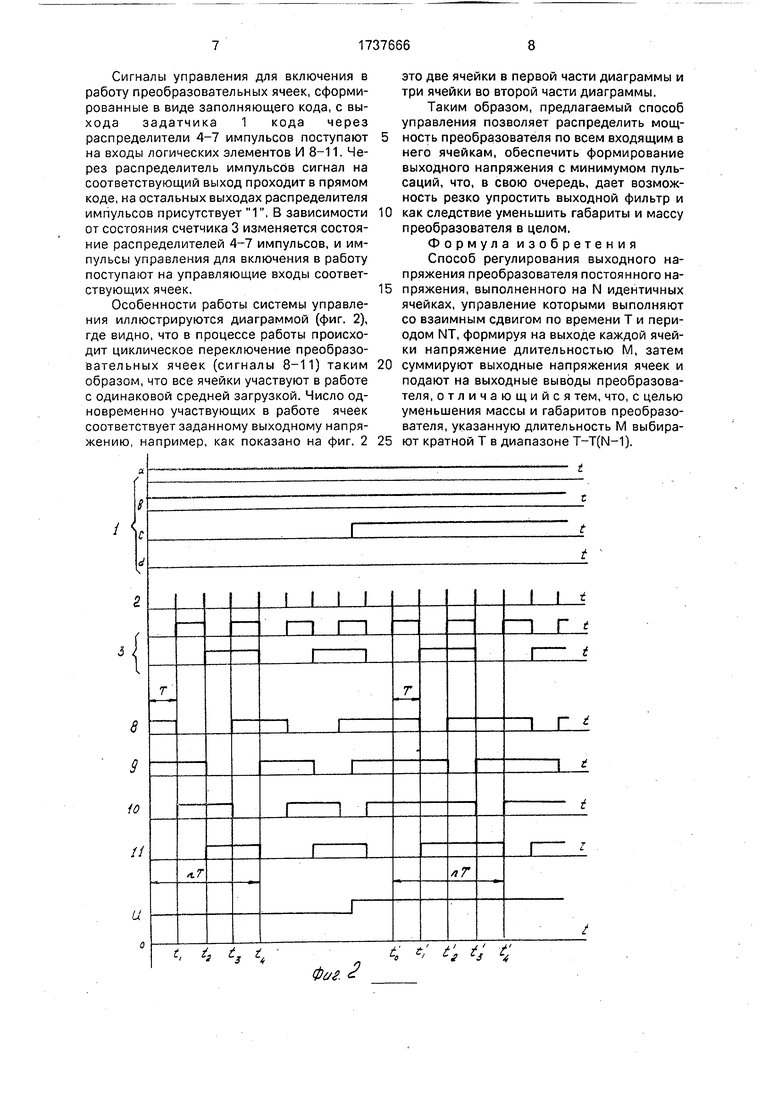

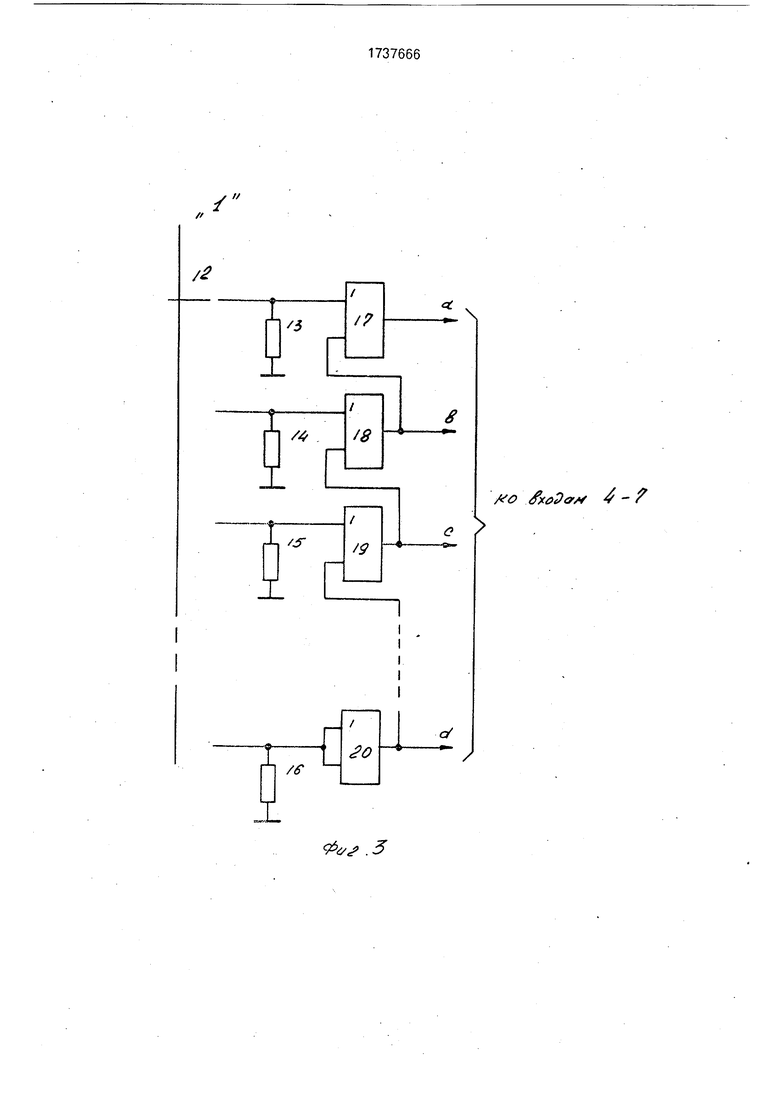

Возможные варианты построения задатчика кода такого типа показаны на фиг. 3 и 4 для программного и электронного управления преобразователем постоянного напряжения соответственно. В схеме на фиг. 3 с помощью переключателя 12, подключающего разрешающий уровень 1 к входам соответствующих логических элементов ИЛИ 17-20, можно получить на выходах этих элементов заполняющий код числа. На неиспользуемых входах логических элементов ИЛИ 17-20 уровень О обеспечивается с помощью резисторов 13- 16.

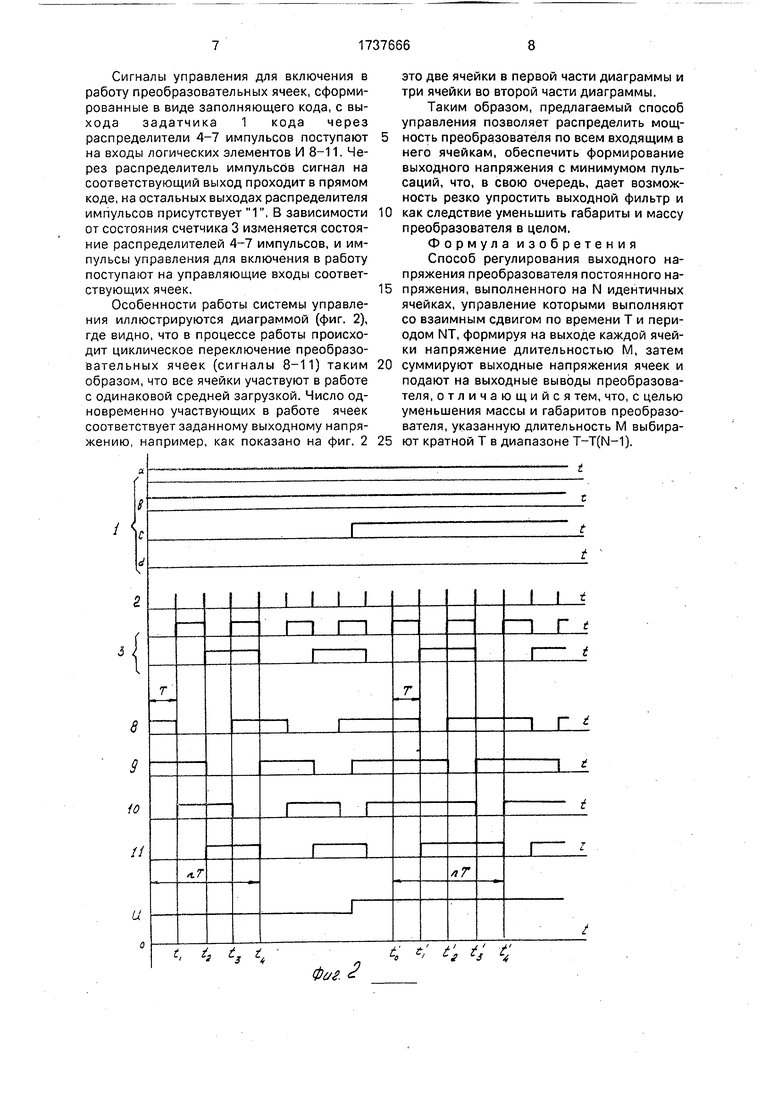

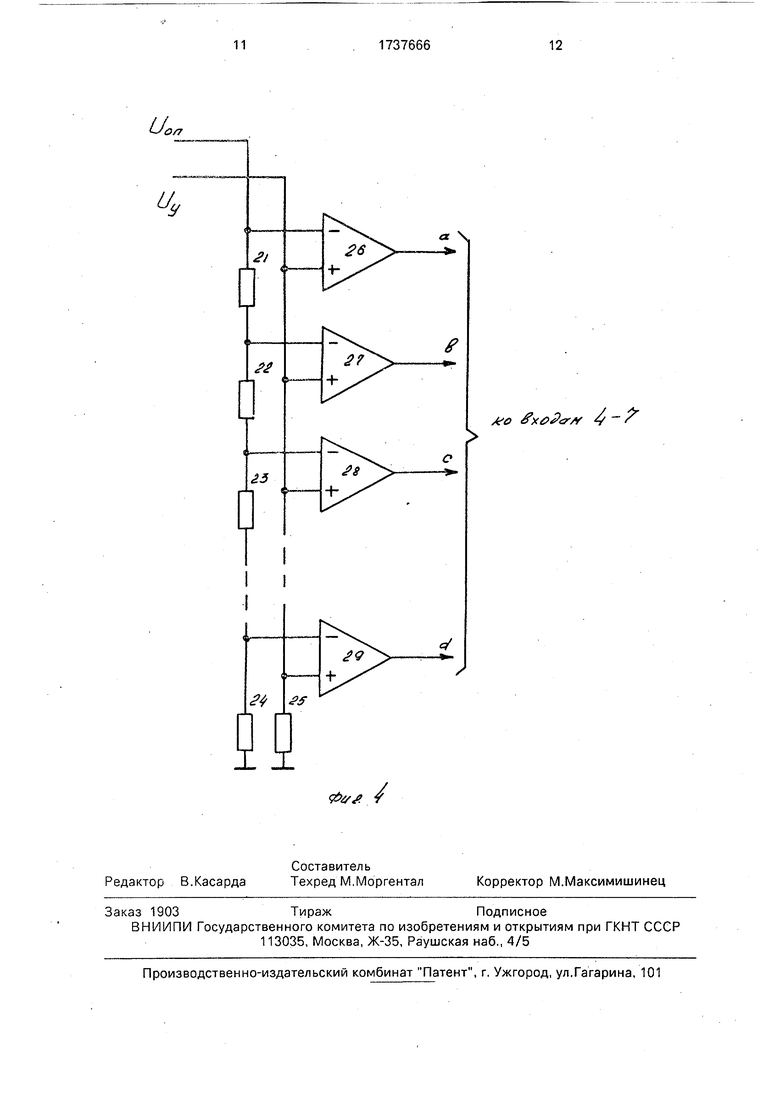

В схеме на фиг. 4 заполняющий код необходимого числа формируется на выходах компараторов 26-29, осуществляющих сравнение входного сигнала управления Uy с заранее определенными опорными уровнями напряжений, реализованными с помощью делителя напряжения Uon на резисторах 21-24. Данная схема может быть использована при введении в систему управления преобразователем электрических аналоговых связей (управляющих, стабилизирующий по цепи обратной связи и т.д.).

Схема системы управления (фиг. 1), реализующая способ, работает следующим образом.

Сигналы управления для включения в работу преобразовательных ячеек, сформированные в виде заполняющего кода, с выхода задатчика 1 кода через распределители 4-7 импульсов поступают на входы логических элементов И 8-11. Через распределитель импульсов сигнал на соответствующий выход проходит в прямом коде, на остальных выходах распределителя импульсов присутствует 1. В зависимости от состояния счетчика 3 изменяется состояние распределителей 4-7 импульсов, и импульсы управления для включения в работу поступают на управляющие входы соответствующих ячеек.

Особенности работы системы управления иллюстрируются диаграммой (фиг. 2), где видно, что в процессе работы происходит циклическое переключение преобразовательных ячеек (сигналы 8-11) таким образом, что все ячейки участвуют в работе с одинаковой средней загрузкой. Число одновременно участвующих в работе ячеек соответствует заданному выходному напряжению, например, как показано на фиг. 2

это две ячейки в первой части диаграммы и три ячейки во второй части диаграммы.

Таким образом, предлагаемый способ управления позволяет распределить мощность преобразователя по всем входящим в него ячейкам, обеспечить формирование выходного напряжения с минимумом пульсаций, что, в свою очередь, дает возможность резко упростить выходной фильтр и как следствие уменьшить габариты и массу преобразователя в целом.

Формула изобретения Способ регулирования выходного напряжения преобразователя постоянного напряжения, выполненного на N идентичных ячейках, управление которыми выполняют со взаимным сдвигом по времени Т и периодом NT, формируя на выходе каждой ячейки напряжение длительностью М, затем суммируют выходные напряжения ячеек и подают на выходные выводы преобразователя, отличающийся тем, что, с целью уменьшения массы и габаритов преобразователя, указанную длительность М выбирают кратной Т в диапазоне T-T(N-1).

/хйЭа 4 -

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| Многофазный параметрический стабилизатор постоянного напряжения | 1989 |

|

SU1658130A1 |

| Преобразователь постоянного напряжения в трехфазное | 1985 |

|

SU1292143A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1988 |

|

SU1561068A1 |

| Однотактный преобразователь переменного напряжения | 1987 |

|

SU1467705A1 |

| Устройство для управления многоячейковым преобразователем напряжения | 1982 |

|

SU1072238A1 |

| Многофазный импульсный стабилизаторпОСТОяННОгО НАпРяжЕНия | 1979 |

|

SU824161A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное переменное | 1987 |

|

SU1511833A1 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Устройство для управления преобразователем постоянного напряжения в трехфазное | 1988 |

|

SU1644331A1 |

Использование: преобразование и регулирование постоянного напряжения для систем вторичного электропитания повышенной надежности. Сущность изобретения: преобразователь выполнен на N одинаковых ячейках, соединенных по входу параллельно, а по выходу- последовательно. Ячейки управляются с периодом NT и взаимным сдвигом на время Т с помощью задатчика 2 тактовых импульсов, счетчика 3 импульсов с коэффициентом деления N и распределителя импульсов на элементах 4- 7. С помощью задатчика 1 числа включенных ячеек изменяется режим работы преобразователя, т.е. дискретно изменяется длительность выходного напряжения кратно Т в диапазоне от Т до T(N - 1). При этом изменяется число одновременно работающих ячеек и ступенчато-уровень выходного напряжения преобразователя, причем пульсации выходного напряжения минимальны. 4 ил. (Л С

W .3

flfl

#o 4

| Миловзоров В.П., Мусолин А.К | |||

| Дискретные стабилизаторы и формирователи напряжения | |||

| М.: Энергоатомиздат, 1986, с | |||

| Приспособление к тростильной машине для прекращения намотки шпули | 1923 |

|

SU202A1 |

| Преобразователь напряжения | 1979 |

|

SU890530A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1992-05-30—Публикация

1989-03-09—Подача