Изобретение может быть использовано в радиолокации, радионавигации, системах передачи информации для обнаружения дискретных сигналов с временным кодированием.

Известно устройство декодирования сигналов с временным кодированием [1] . Устройство содержит многоотводную линию задержки, вход которой соединен с входной шиной, решающий блок, выход которого соединен с выходной шиной, измерители, вход каждого из которых соединен с одним из выходов многоотводной линии задержки, а выход подключен к соответствующему входу решающего блока. Линия задержки предназначена для совмещения отсчетов сигнала во времени. После этого значения отсчетов измеряются в измерителях и поступают на решающий блок, который по априорной информации принимает решение о наличии или отсутствии сигнала.

К недостаткам этого устройства относится его большая сложность из-за наличия большого количества измерителей и большого объема памяти решающего блока, что ограничивает возможность применения устройства.

Прототипом изобретения является селектирующее устройство декодирования [2] , содержащее блок преобразования, блок задержки и решающий блок, причем вход блока преобразования является входом устройства, а выход блока преобразования соединен с информационным входом блока задержки, выходы которого сгруппированы в N групп и подключены к соответствующим группам входов решающего блока, а тактовые входы блока преобразования, блока задержки и решающего блока объединены и являются тактовым входом устройства. Каждая из N групп соответствует одному из N импульсов ИВС и содержит К отводов. Сигналы, снимаемые со всей совокупности N групп рассматриваются как некоторое "кодовое слово". В реальной ситуации эти "кодовые слова" образуют конечное множество, из-за конечности динамического диапазона блока преобразования. Для каждого элемента этого множества, которым является одно "кодовое слово", исходя из априорно заданной сигнально-помеховой обстановки (СПО), определяется, какое решение ("есть ИВС" или "нет ИВС") должен выносить оптимальный декодер. Решению "есть ИВС" ставится в соответствие "1", а решению "нет ИВС" - "0".

В результате каждому "кодовому слову" априори ставится в соответствие один бит, причем само "кодовое слово" рассматривается, как адрес этого бита в постоянном запоминающем устройстве (ПЗУ).

В результате решающий блок данного устройства представляет из себя ПЗУ, объем которого равен числу элементов множества "кодовых слов", которое вычисляется по формуле

N * K

V1 = 2 (1)

Основным недостатком этого устройства является большой объем памяти ПЗУ в связи с сильно избыточным способом хранения информации. Эта избыточность возникает из-за хранения решения для каждого "кодового слова", хотя для принятия решения нам достаточно знать граничные значения "кодовых слов" для каждого из решений. Это приводит к необходимости применения большого количества элементов памяти, что ограничивает область применения устройства.

Техническим результатом является расширение области использования устройства за счет увеличения количества декодируемых сигналов и их разрядности, путем уменьшения избыточности хранимой в ПЗУ информации и, следовательно, уменьшения удельных затрат памяти.

Указанный результат достигается тем, что в селектирующее устройство декодирования, содержащее решающий блок (ПЗУ), блок преобразования, выход которого соединен со входом блока задержки, выходы которого сгруппированы в N групп (N - число сигнальных позиций), тактовые входы блока преобразования и блока задержки объединены, информационный вход блока преобразования является входом устройства, введены блок загрузки, блок сравнения, счетчик импульсов, блок формирования шага, сумматор, регистр памяти и блок управления, первая группа выходов блока задержки соединена с первым информационным входом блока сравнения, 2-я-N-я группы выходов блока задержки соединены с соответствующими информационными входами блока загрузки, выход управления блока загрузки соединен со входом управления выходом решающего блока, выходы младших разрядов которого соединены со входами управления блока сравнения и блока управления, первый тактовый выход которого соединен с тактовыми входами блока преобразования и блока загрузки, информационный выход которого и выходы старших разрядов решающего блока соединены со вторым информационным входом блока сравнения и информационным входом блока формирования шага, выход "загрузка" блока загрузки соединен с одноименным входом блока управления, выход "величина" которого соединен с одноименными входами блока загрузки и блока формирования шага, выходы которого соединены с первым информационным входом сумматора, выходы которого соединены с информационным входом регистра памяти, выход "смена информации" блока управления соединен с одноименным входом блока формирования шага и с тактовым входом регистра памяти, информационный выход и выход знакового разряда которого соединены соответственно со вторым информационным входом сумматора и со входом "текущий знак" блока управления, выход "перенос" которого соединен с одноименным входом сумматора, выход "знак" блока управления соединен с одноименными входами блока формирования шага и блока сравнения и со входом направления счета счетчика импульсов, выход которого соединен с адресным входом решающего блока, второй тактовый выход блока управления соединен с тактовыми входами счетчика импульсов и блока сравнения, выход которого является выходом устройства.

Сущность изобретения состоит в уменьшении избыточности информации и введении дополнительных устройств, осуществляющих ее выбор. Рассмотрим сначала способ формирования информации ПЗУ. Первоначально, как и в прототипе, на основе априорных данных о СПО определяются решения для всех возможных состояний N групп выходов блока задержки и на их основе формируется множество решений, причем каждому его элементу будет соответствовать свой номер в виде N разрядного числа, каждый разряд которого будет равен значению соответствующей группы. Упорядочим это множество решений в порядке возрастания его элементов, а затем разделим на равные подмножества так, чтобы в пределах подмножества менялись, принимая все возможные значения, величина первой группы выходов блока задержки, которая соответствует младшим разрядом номера элемента, а остальные группы (со второй до N) постоянны в пределах подмножества, образуя его номер. Причем число таких подмножеств определяется как

K * (N - 1)

M = 2 (2)

Затем в пределах подмножества найдем значения первой группы выходов блока задержки блока задержки, при которых происходит смена решения о наличии или отсутствии ИВС на противоположное. Эти значения будут являться порогами по отношению к первой группе выходов блока задержки и несут ту же информацию о решении, что и все подмножество, при условии задания решения хотя бы в одной точке подмножества. Заменим каждое из подмножеств, соответствующим ему набором порогов, которые запишем в ПЗУ, начиная с третьего разряда, а для обозначения начала каждого подмножества пометим первый его порог единицей во втором разряде. В записи этого же порога укажем и решение, принимаемое устройством при значении первой группы выходов блока задержки меньшего первого порога в младшем разряде ПЗУ. Для всех последующих порогов подмножества в оба младших разряда запишем нули.

Если принять среднее количество порогов на подмножестве равным Кп, то число порогов на всем множестве будет равно

K * (N - 1)

P = Kп * М = Кп * 2, (3) а объем памяти ПЗУ будет определяться как

К * (N - 1)

V = P * (log K + 2) = Кп(log K + 2) * 2 (4)

На практике выяснилось, что достаточно часто встречаются случаи, когда несколько соседних подмножеств имеют одинаковые пороги. В связи с этим в устройстве была предусмотрена возможность записывать набор порогов лишь для первого из одинаковых подмножеств, а затем указывать их число (повторитель), которое помечается кодом 01 в младших разрядах данных ПЗУ. При этом количество порогов, записываемых в ПЗУ уменьшится и будет равно

K * (N - 1)

P2 = Кп * Ку * М = Кп * Ку * 2, (5) а объем памяти ПЗУ

К * (N - 1)

V2 = Кп * Ку * (log K + 2) * 2, (6) где Ку - коэффициент уменьшения количества порогов за счет введения повторителя.

В соответствии с (1) и (6) выигрыш в объеме памяти по сравнению с прототипом будет равен

К

V1/V2 = Кп * Ку * (log K + 2)/2 (7)

После всех этих операций в ПЗУ содержатся последовательные наборы порогов для всех возможных комбинаций значений групп выходов блока задержки.

Теперь для вынесения решения на основе полученных значений N групп выходов блока задержки необходимо:

1. Найти в ПЗУ набор порогов для комбинации групп выходов блока задержки со второй по N-ю.

2. Сравнить значение первой группы выходов блока задержки с порогами и выдать решение.

Для решения первой задачи группы выходов блока задержки со второй по N-ю переписываются с помощью блока загрузки в блок формирования шага, который формирует номер набора порогов в виде шага. В результате в регистре памяти с помощью сумматора формируется разность значений номеров старого (в момент включения равного нулю) и нового набора порогов. Затем начинается приближение этой разности к нулю за счет просмотра ПЗУ с помощью счетчика импульсов. Управление работой устройства осуществляется блоком управления.

Вторая задача решается блоком сравнения.

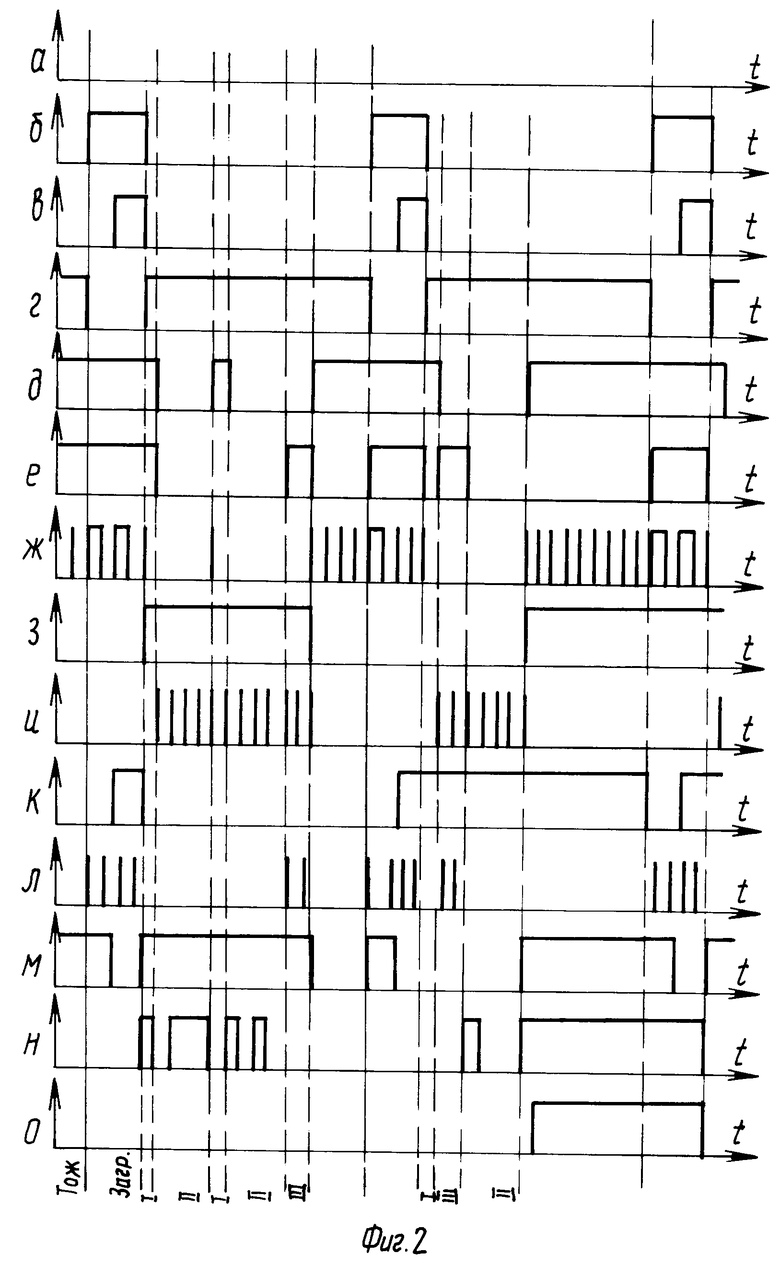

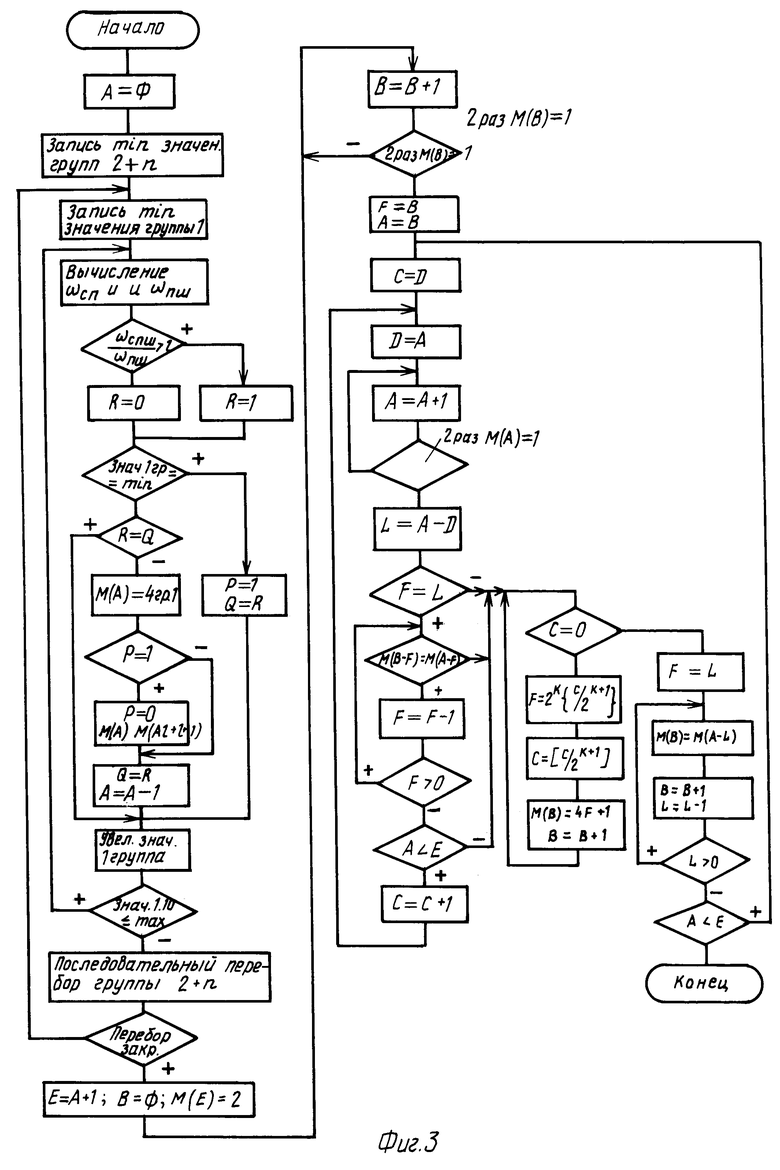

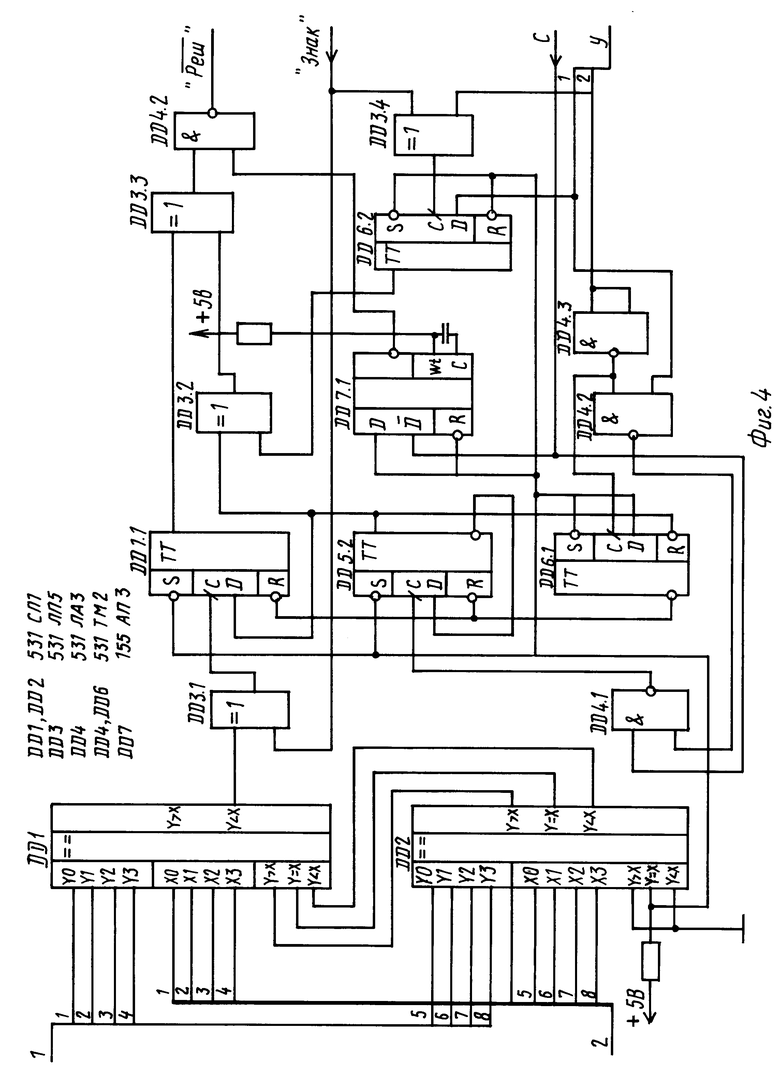

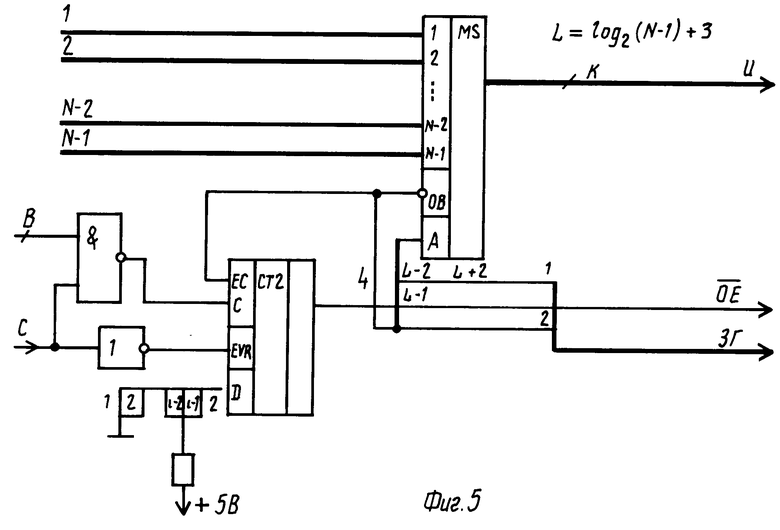

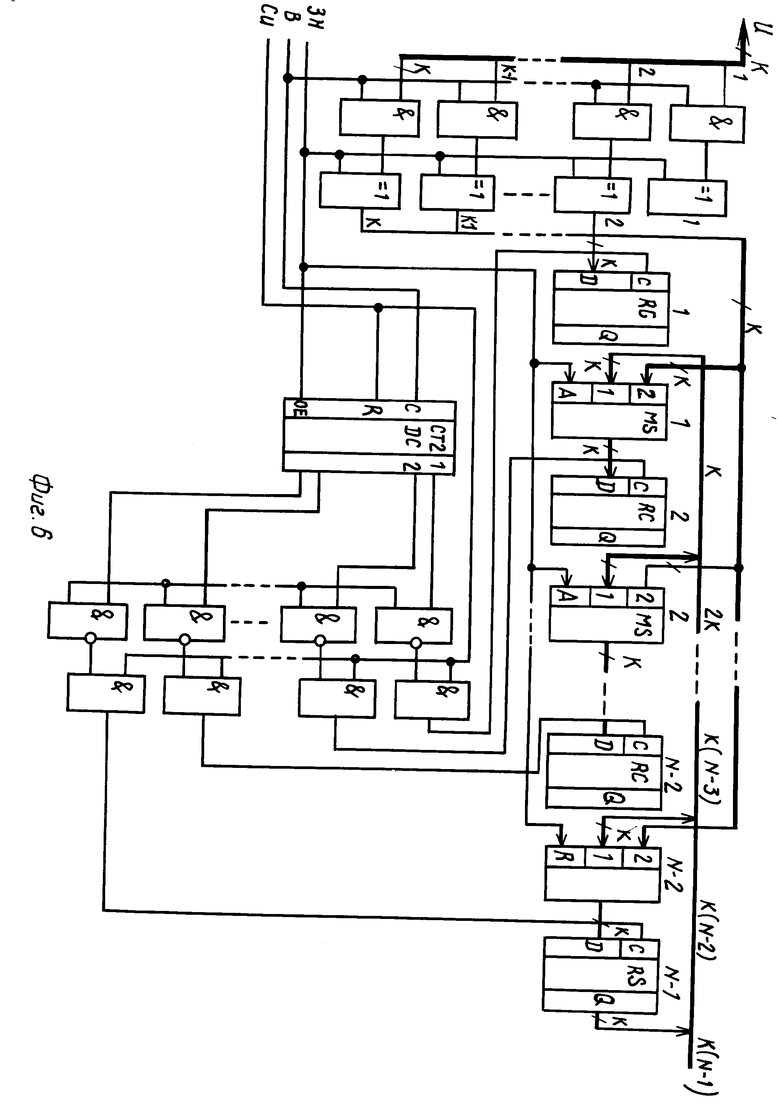

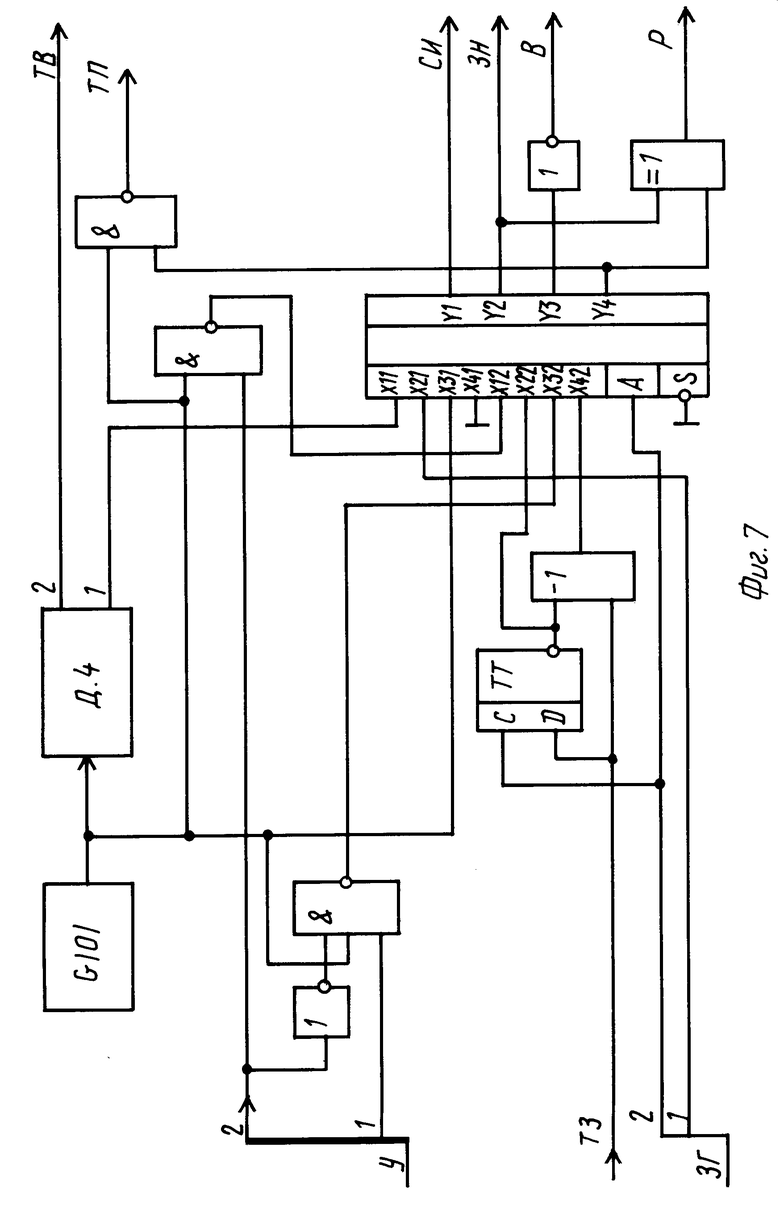

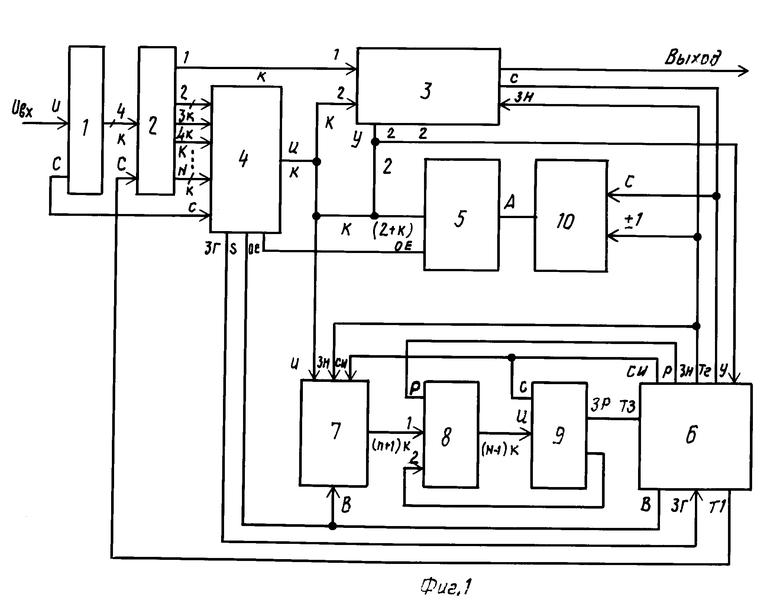

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - временные диаграммы работы устройства; на фиг.3 - алгоритм программирования решающего блока; на фиг.4 - принципиальная схема блока сравнения; на фиг.5 - функциональная схема блока загрузки; на фиг.6 - функциональная схема блока формирования шага; на фиг.7 - функциональная схема блока управления.

Вход устройства (фиг.1) соединен с информационным входом блока преобразования 1, выход которого соединен с информационным входом блока задержки 2, выходы которого сгруппированы в N групп, первая из которых соединена с первым информационным входом блока сравнения 3. 2-я-N-я группы выходов блока задержки 2 соединены с соответствующими информационными входами блока загрузки 4. Выход управления блока загрузки 4 соединен со входом управления выходом решающего блока 5, выходы младших разрядов которого соединены со входами управления блока сравнения 3 и блока управления 6, первый тактовый выход которого соединен с тактовыми входами блока преобразования 1, блока задержки 2 и блока загрузки 4, информационный выход которого и выходы старших разрядов решающего блока 5 соединены со вторым информационным входом блока сравнения 3 и информационным входом блока формирования шага 7, выход "загрузка" блока загрузки 4 соединен с одноименным входом блока управления 6, выход "величина" которого соединен с одноименными входами блока загрузки 4 и блока формирования шага 7, выходы которого соединены с первым информационным входом сумматора 8, выходы которого соединены с информационным входом регистра памяти 9, выход "смена информации" блока управления 6 соединен с одноименным входом блока формирования шага 7 и с тактовым входом регистра памяти 9, информационный выход и выход знакового разряда которого соединены соответственно со вторым информационным входом сумматора 8 и со входом "текущий знак" блока управления 6, выход "перенос" которого соединен с одноименным входом сумматора 8, выход "знак" блока управления соединен с одноименными входами блока формирования шага 7 и блока сравнения 3 и со входом направления счета счетчика импульсов 10, выход которого соединен с адресным входом решающего блока 5. Второй тактовый выход блока управления 6 соединен с тактовыми входами счетчика импульсов 10 и блока сравнения 3, выход которого является выходом устройства.

Устройство, согласно временным диаграммам (фиг.2) работает следующим образом. После включения питания устройство автоматически переходит в состояние ожидания импульса с первого тактового выхода блока управления 6. В этом состоянии информация на всех элементах устройства, кроме сигнала "смена информации" (фиг.2, ж), по которому поступают синхроимпульсы всегда, когда второй разряд решающего блока 5 равен "1", неизменна. Затем каждый импульс с первого тактового выхода блока управления 6 (фиг.2, а) приводит к повторению одного и того же цикла.

Импульсы с первого тактового выхода блока управления 6 (фиг.2, а), период которых определяет время между двумя соседними отсчетами, поступают на блок преобразования 1, который выдает на блок задержки 2 отсчет сигнала. Блок задержки 2 формирует на выходе значения групп отсчетов, а блок загрузки 4 - положительный импульс на выходе управления (фиг.2, б), запирающий выходной буфер решающего блока 5, что позволяет осуществить передачу значений групп со второй по N-ю в блок формирования шага 7. Одновременно по шине "Загрузка" с блока загрузки 4 на блок управления 6 подаются два разряда (фиг. 2, в и 2, г), на основе которых блок управления 6 формирует импульсы "величина" (фиг.2, л) на блок загрузки 4 и блок формирования шага 7 и сигнал "знак" (фиг.2, к) на блок формирования шага 7. Положительные импульсы "величина" приводят к формированию шага, равного значению, поступающему на информационный вход блока формирования шага 7 (если импульсов "величина" нет, то шаг равен "1"), а сигнал "знак" определяет знак шага. Значение шага суммируется в сумматоре 8 с предшествующим значением регистра памяти 9 (после включения равного нулю) и записывается в регистр памяти 9 импульсом "смена информации" (фиг.2, ж), который также записывает в блок формирования шага 7 шаг, равный "1".

В результате в регистре памяти 9 к моменту окончания загрузки формируется значение разности новых и старых (после включения равных нулю) значений групп отсчетов со второй по N-ю. После этого блок загрузки 4 переходит в исходное состояние, а блок управления 6 записывает во внутренний триггер знак числа в регистре 9 (фиг.2, з) и выдает состояние триггера на выход "знак" (фиг.2, к). Сигнал переноса (фиг.2, м) выдается на сумматор 8 для формирования шага, равного "+ 1" и дополнительного кода шага при работе с его отрицательными значениями блоком управления 6. Одновременно на втором тактовом выходе блока управления 6 формируются импульсы (фиг.2, и). Эти импульсы поступают на блок сравнения 3 и счетчик импульсов 10, который выдает адрес ячейки решающего блока 5 (после включения питания равный нулю), по которому осуществляется выборка данных.

Младшие разряды решающего блока 5 (первый разряд (фиг.2, е) и второй разряд (фиг. 2, д) поступают на блок сравнения 3 и блок управления 6. В соответствии с их значениями блок управления 6 и блок cравнения 3 переходят в один из трех режимов работы.

1) Режим считывания первого порога.

В этом режиме блок управления 6 формирует импульс "смена информации" (фиг. 2, ж), по которому происходит запись нового приближения в регистр памяти 9. Если знак числа в регистре 9 изменился (фиг.2, з), что указывает на выбор нужного набора порогов, то блок управления 6 переводит устройство в состояние ожидания, и прекращает выдачу импульсов по второму тактовому выходу (фиг.2, и), разрешая выдачу сигнала решения (фиг.2, о) блоком сравнения 3.

Блок сравнения 3 в этом режиме производит перезапись решения, соответствующего гипотезе, что значение первой группы выходов блока задержки 2 меньше первого порога, по заднему фронту импульса на втором разряде младшего выхода данных решающего блока 5, если сигнал "знак" равен "1", и по переднему фронту, если сигнал "знак" равен нулю, с первого разряда младшего выхода данных решающего блока 5 во внутренний триггер решения блока сравнения 3 (фиг.2, н). Если эта гипотеза подтверждается, то сравнение прекращается. В противном случае внутренний триггер решения перебрасывается в противоположное состояние (фиг. 2, н) по заднему фронту сигнала с второго тактового выхода блока управления 6 (фиг.2, и). При отсутствии тактовых импульсов состояние внутреннего триггера решения передается на выход решения устройства без изменения (фиг.2, о).

2) Режим считывания второго и последующих порогов.

В этом случае блок управления 6 продолжает выдавать импульсы по второму тактовому выходу (фиг.2, и), не меняя значения информации на других выходах. Блок сравнения 3 производит сравнение первой группы выходов блока задержки 2 с поступающими с решающего блока 5 порогами до тех пор, пока значение первой группы входов не будет больше значения порога, если сигнал "знак" равен "1", или меньше значения порога, если сигнал "знак" равен "0", и если оно не было прекращено в режиме 1. Пока производится сравнение каждый импульс со второго тактового выхода блока управления 6 приводит к перебрасыванию внутреннего триггера решения (фиг.2, н).

3) Режим считывания повторителя.

В этом режиме работа блока сравнения 3 блокируется, а блок управления 6 формирует импульсы "величина" (фиг. 2, л) на блок формирования шага 7 и обеспечивает формирование шага, равного значению повторителя из решающего блока 5.

Устройство работает в этих режимах до перехода в состояние ожидания, в котором оно затем остается до формирования очередного импульса на первом тактовом выходе блока управления 6, который приводит к повторению рабочего цикла с начала.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ЭЛЕКТРОПРИВОД ПОСТОЯННОГО ТОКА С ДВОЙНОЙ ШИРОТНО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1992 |

|

RU2037263C1 |

| ДАТЧИК ЧАСТОТЫ ВРАЩЕНИЯ РОТОРА МАШИНЫ ПЕРЕМЕННОГО ТОКА | 1994 |

|

RU2085953C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ДВОИЧНЫХ КОДОВ ХЕММИНГА | 1999 |

|

RU2161369C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ АРИТМИИ | 1993 |

|

RU2077863C1 |

| Устройство для моделирования поглощающих цепей Маркова | 1989 |

|

SU1810888A1 |

| Генератор случайных чисел | 1990 |

|

SU1817094A1 |

| МОДУЛЬ ДЛЯ РЕТРАНСЛЯЦИИ СООБЩЕНИЙ В КОММУТАЦИОННОЙ СТРУКТУРЕ | 2002 |

|

RU2222044C2 |

| Генератор псевдослучайных чисел | 1990 |

|

SU1805465A1 |

| МОДУЛЬ МУЛЬТИМИКРОПРОГРАММНОЙ СИСТЕМЫ | 1997 |

|

RU2116665C1 |

| МОДУЛЬ СИСТЕМЫ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1999 |

|

RU2152071C1 |

Изобретение может быть использовано в радиолокации, радионавигации, системах передачи информации для обнаружения дискретных сигналов с временным кодированием. Изобретение расширяет область использования устройства за счет увеличения количества декодируемых сигналов и их разрядности путем уменьшения избыточности хранимой в ПЗУ информации и, следовательно, уменьшения удельных затрат памяти. Устройство включает в себя блок преобразования 1, блок задержки 2, блок сравнения 3, блок загрузки 4, решающий блок 5, блок управления 6, блок формирования шага 7, сумматор 8, регистр памяти 9, счетчик импульсов 10. Переход в данном устройстве от хранения решения обнаружителя для всего динамического диапазона к хранению значений порогов с их последовательным выбором позволило резко уменьшить объем памяти решающего блока путем уменьшения избыточности информации, хранимой в нем, и расширить область использования устройства за счет увеличения количества декодируемых сигналов и их разрядности. 3 з.п.ф-лы, 7 ил.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Селектирующее устройство декодирования | 1985 |

|

SU1305867A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-02-09—Публикация

1990-02-08—Подача