Изобретение относится к автоматике и вычислительной технике и может быть использовано в составе специализированных вычислительных машин для LV-декомпозиции матриц,

Цель изобретения - расширение функциональнУх возможностей за счет LV-дёкомпозиции исходной матрицы.

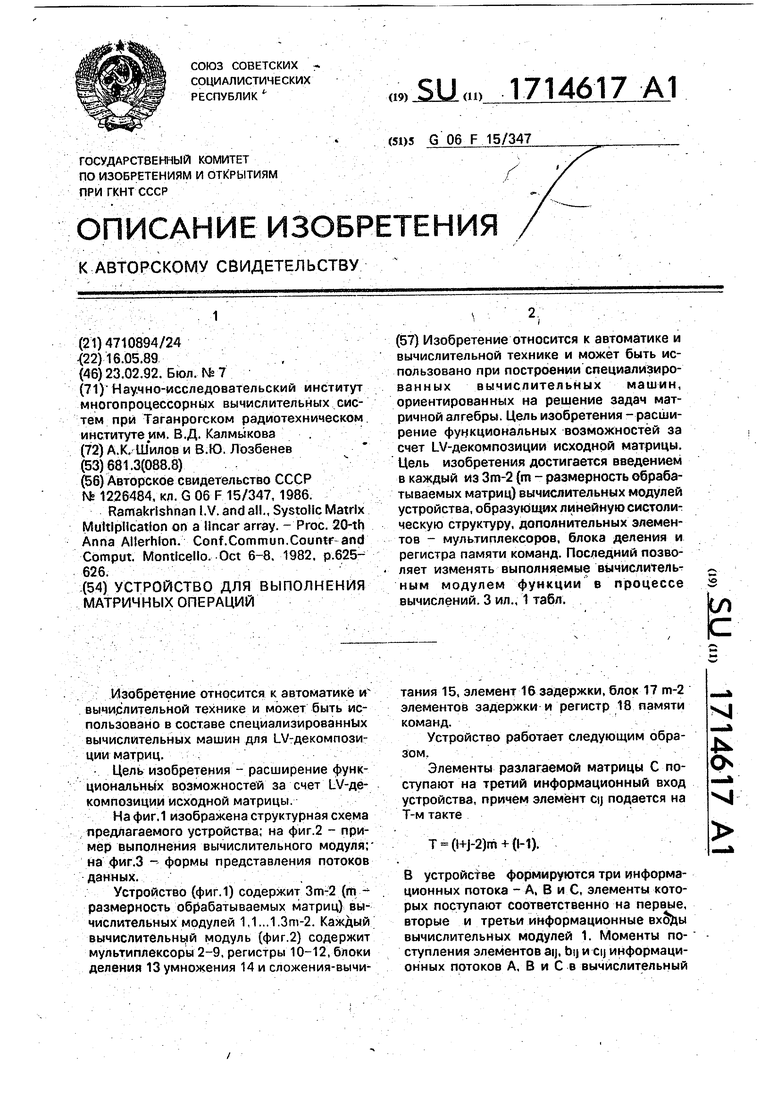

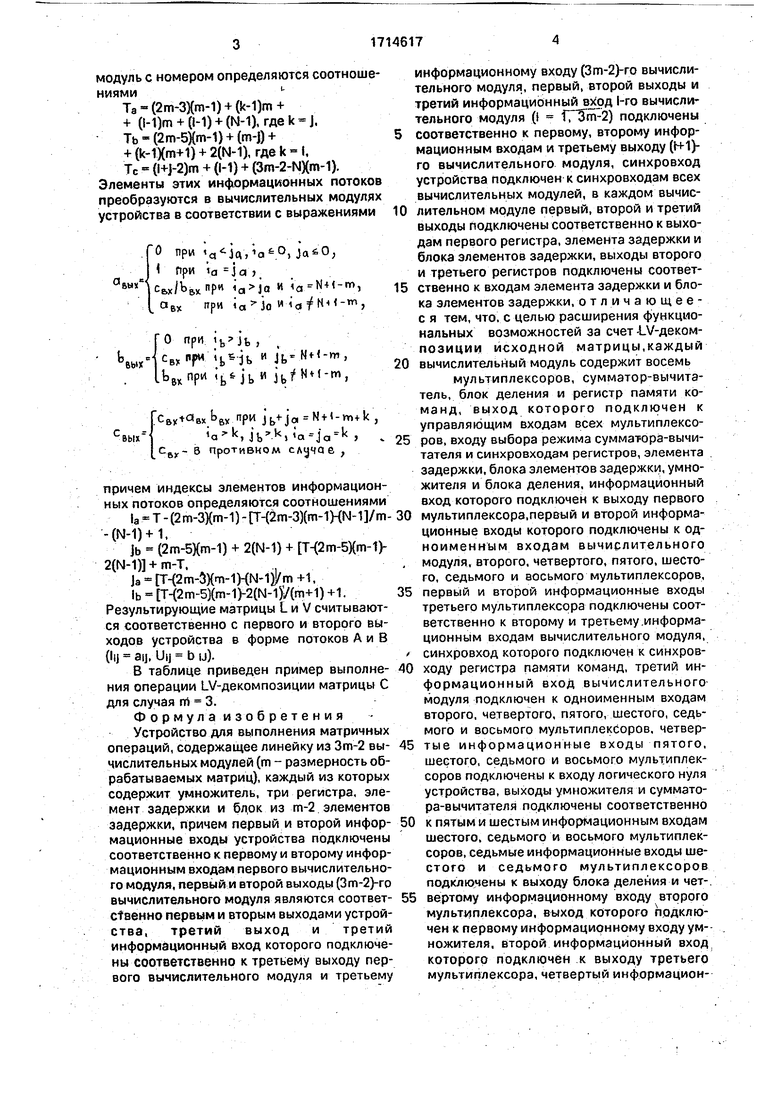

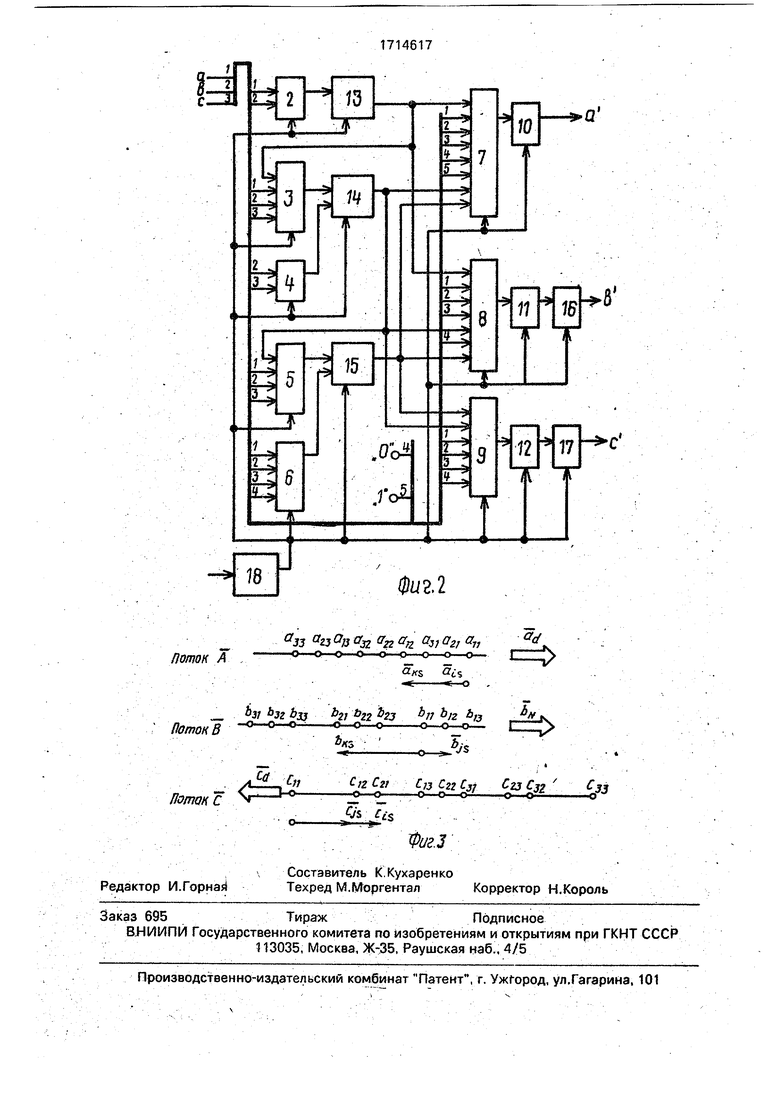

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг.2 - пример выполнения вычислительного модуля; на фиг.З - формы представления потоков данных.

Устройство (фиг. 1) содержит Зт-2 (т размерность обрабатываемых матриц) вычислительных модулей 1,1...1.3т-2. Каждый вычислительнь)й модуль (фиг.2) содержит мультиплексоры 2-9. регистры 10-12. блоки деления 13 умножения 14 и сложения-вычитания 15. элемент 16 задержки, блок 17 т-2 элементов задержки и регистр 18 памяти команд..

Устройство работает следующим образом,

Элементы разлагаемой матрицы С поступают на третий информационный вход устройства, причем элемент cij подается на Т-м такте

Т 0+j-2)m + (1-1),

В устройстве формируются три информационных потока - А. В и С, элементы которых поступают соответственно на первые, вторые и третьи информационные вычислительных модулей 1. Моменты поступления элементов aij. bij и cij информационных потоков А. В и С в вычислительный

модуль с номером определяются соотношениями Та - (2m-3Xm-1) + (k-1)m + + (i-1)m + (1-1) + (N-1), где k J. Tb-(2m-5Xm-1) + (m-) + + (k-1Xm+1)-(-2(N-1), гдеК 1, Тс {l+j-2)m -I- (1-1) + {3m-2-NXm-1). Элементы этих информационных потоков преобразуются в вычислительных модулях устройства в соответствии с выражениями

О при ,iafeO, ,

При ia ja j.

СЬХ/ЬЬХ.ПРИ « ia )

бык

. OBX ри и ,

0 прЧ , . Ч-Jb

BWX . ЬЧЬИ ibf NH-m,

Сву+Овх ЬВУ ри Jb- joi N-t--m+k,

a-k, Jt,:k,

ых

Jb

В Противном случае ,

причем индексы элементов информационных потоков определяются соотношениями

1а Т - (2m-3Xm-1) - T-(2m-3Xm-lHN-1 /m-(N-1)+1.

Jb (2m-5Xm-1) + 2(N-1) + T-(2m-5Xm-1)2(I-1)+m-T.

Ja T-{2m-3Xm-1)-{N-1)/m +1,

Ib T-{2m-5)(m-1)-2(N-l)/(m+1)+1. Результирующие матрицы L и V считываются соответственно с первого и второго выходов устройства в форме потоков А и В (lij aij, Uij b и).

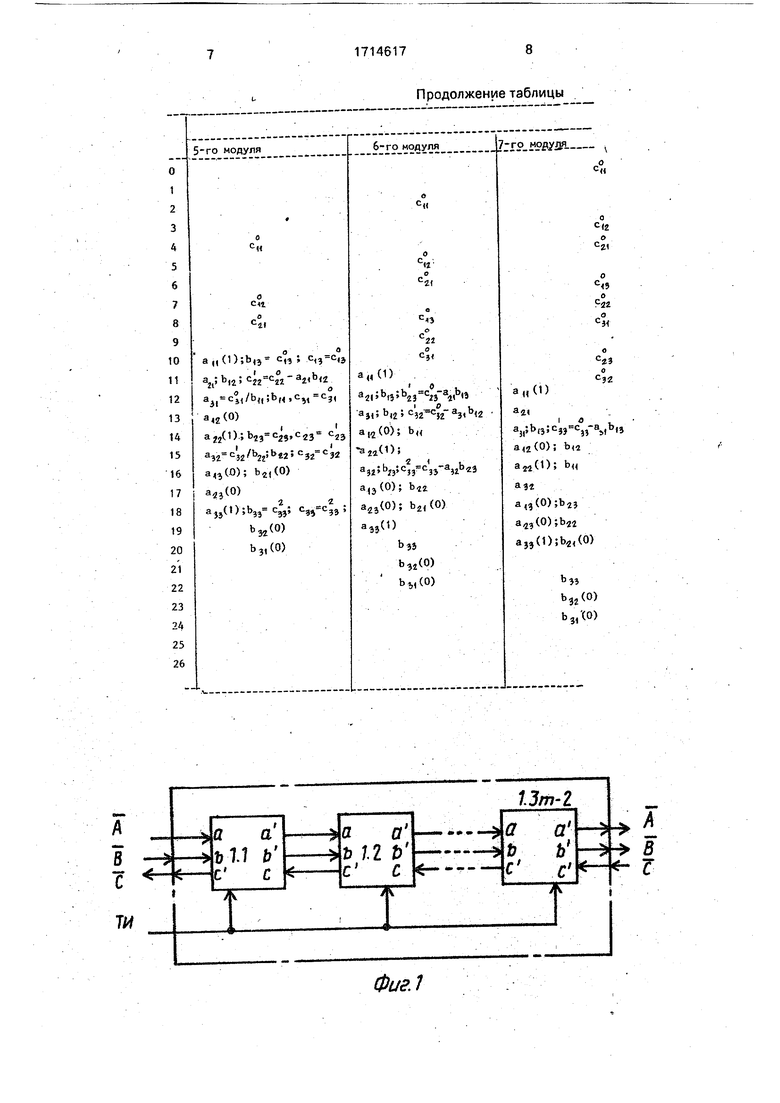

В таблице приведен пример выполнения операции LV-декомпозиции матрицы С для случая rrt 3.

Формул а и 3о бретения

Устройство для выполнения матричных операций, содержащее линейку из Згп-2 вычислительных модулей (т - размерность обрабатываемых матриц), каждый из которых содержит умножитель, три регистра, элемент задержки и бдок из т-2 элементов задержки, причем первый и второй информационные входы устройства подключены соответственно к первому и второму информационным входам первого вычислительного модуля, первый и второй выходы (Зт-2)-го вычислительного модуля являются соответcf венно первь1м и вторым выходами устройства, третий выход и третий информационней вход которого подключены соответственно к третьему выходу первого вычислительного модуля и третьему

информационному входу (Зт-2)-го вычислительного модуля, первый, второй выходы и третий информационный 1-го вычисли тельного модуля (f f77m-2) подключены

соответственно к первому, второму информационным входам и третьему выходу (Н-1)го вычислительного модуля, синхровход устройства подключен к синхровходам всех вычислительных модулей, в каждом вычислительном модуле первый, второй и третий выходы подключены соответственно к выходам первого регистра, элемента задержки и блока элементов задержки, выходы второго и третьего регистров подключены соответственно к входам элемента задержки и блока элементов задержки, отличающееся тем, что. с целью расширения функциональных возможностей за счет -LV-декомпозиции исходной матрицы,каждый

0 вычислительный модуль содержит восемь

мул ьтиплексоров, сумматор-вычитатель, блок деления и регистр памяти команд, вь1ход которого подключен к управляющим входам всех мультиплексоров, входу выбора режима сумматора-вычитателя и синхровходам регистров, элемента задержки, блока элементов задержки, умножителя и блока деления, информационный вход которого подключен к выходу первого

0 мультиплексора,первый и второй информационные входы которого подключены к одноименным входам вычислительного , модуля, второго, четвертого, пятого, шестого, седьмого и восьмого мультиплексоров,

5 первый и второй информационные входы третьего мультиплексора подключены соответственно к второму и третьему .информационным входам вычислительного модуля, / синхровход которого подключен к синхров0 ходу регистра памяти команд, третий информационный вход вычислительного модуля подключен к одноименным входам второго, четвертого, пятого, шестого, седьмого и восьмого мультиплексоров, четвертые информационные входы пятого, шестого, седьмого и восьмого мультиплексоров подключены к входу логического нуля устройства, выходы умножителя и сумматора-вычитателя подключены соответственно

0 к пятым и шестым информационным входам шестого, седьмого и восьмого мультиплексоров, седьмые информационные входы шестого и седьмого мультиплексоров подключены к выходу блока деления и чет-.

5 вертому информационному входу второго мульт1 плексора, выход которого подключен к первому информационному входу ум-ножителя, второй информационный вход которого подключен к выходу третьего мультиплексора, четвертый информационный вход четвертого мультиплексора объединен с пятым информационным входом шестого мультиплексора, восьмой информационный вход которого подключен к входу логической единицы устройства, первый 5 и второй информационные входы сумматора-вычитателя подключены к выходам соответственно четвертого и пятого мультиплексоров,выходы шестого, седьмого и восьмого мультиплексоров подключены соответственно к информационным входам первого, второго и третьего регистров.

Продолжение таблицы

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1994 |

|

RU2116667C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОГО ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1994 |

|

RU2049351C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ТРЕХ МАТРИЦ | 1990 |

|

RU2024933C1 |

| УСТРОЙСТВО ДЛЯ РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 1991 |

|

RU2012049C1 |

| Модулярное устройство вычисления систем линейных алгебраических уравнений | 2015 |

|

RU2611963C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при постр(}ении специализированных вычислительных машин, ориентированных на решение задач матричной алгебры. Цель изобретения - расширение функциональных возможностей за счет LV-декомпозиции исходной матрицы. Цель изобретения достигается введением в каждый из Зт-2 (т - размерность обрабатываемых матриц) вычислительных модулей устройства, образующих линейную систолическую структуру, дополнительных элементов - мультиплексоров, блока деления и регистра памяти команд. Последний позволяет изменять выполняемые вычислитель^ ным модулем функции в процессе вычислений. 3 ил,. 1 табл.

А

С

7И

В

ФигЛ

J5 а Огг к -777

-о. I о-о о о-43 О о

Поток А

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| and all., Systolic Matrix Muitiplicatton on a linear array | |||

| - Proc | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| Conf,Common.Countf-and Comput, Monticello | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| ТАНК-ПАРОВОЗ | 1923 |

|

SU625A1 |

Авторы

Даты

1992-02-23—Публикация

1989-05-16—Подача