Изобретение относится к вычислительной технике и может быть использовано при разработке и конструировании устройства управления вычислительными системами.

Целью изобретения является упрощение устройства за счет сокращения количества оборудования.

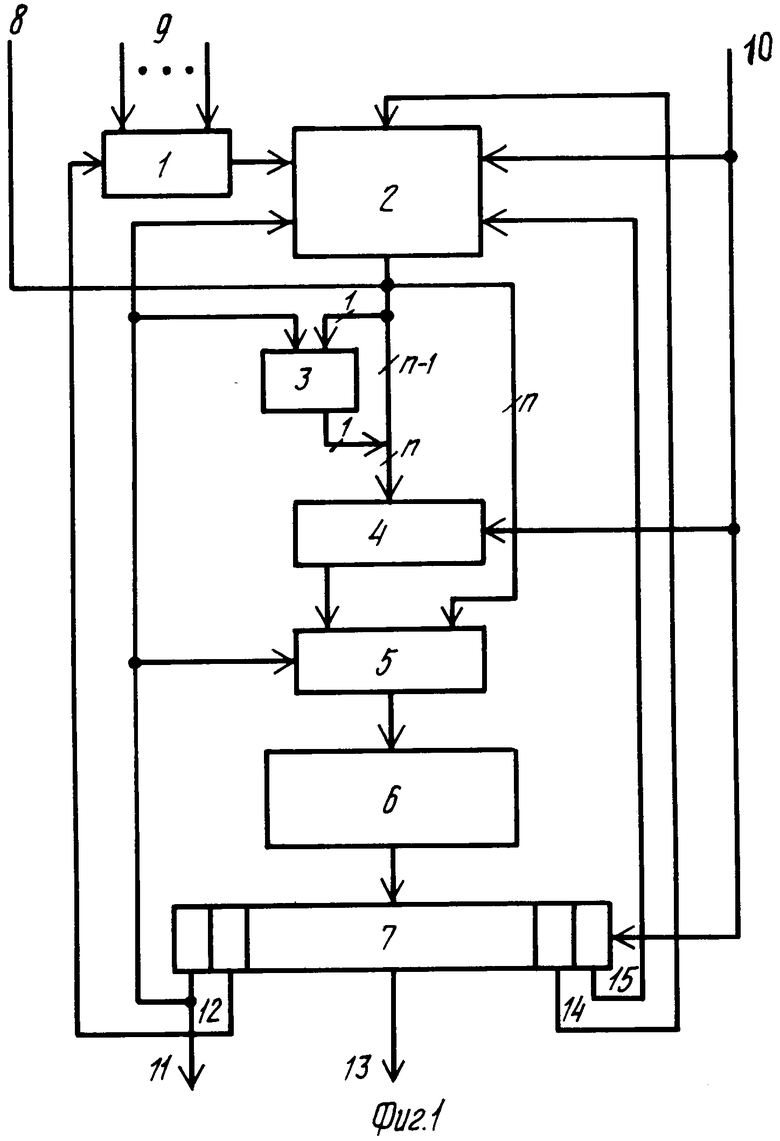

На фиг. 1 представлена структурная схема устройства микропрограммного управления; на фиг.2 - пример граф-схемы алгоритма гипотетической микропрограммы; на фиг.3 - граф-схема микропрограммы, соответствующая гипотетическому алгоритму и выполняемая предлагаемым устройством микропрограммного управления; на фиг.4 - временные диаграммы работы устройства.

Устройство (фиг.1) содержит коммутатор 1 условий, формирователь 2 адреса микрокоманд, элемент ИЛИ 3, регистр 4 адреса, коммутатор 5 результирующего адреса, блок 6 памяти микрокоманд, регистр 7 микрокоманд, вход 8 адреса, входы 9 условий, вход 10 синхронизации, выходы 11-15 регистра микрокоманд.

Вход 8 служит для загрузки начального адреса микрокоманд.

Коммутатор 1 условий служит для приема условий по входам 9 при выполнении микропрограмм условных переходов.

Формирователь 2 адреса микрокоманд предназначен для формирования адреса (i+2)-й микрокоманды под действием управляющего кода из регистра 7 микрокоманд, поступающего по входу 15. Подробно структура формирователя 2 адреса микрокоманд описана в [1].

Элемент ИЛИ 3 служит для формирования адреса (i+1)-й микрокоманды при разгоне конвейера микрокоманд под действием управляющего сигнала, поступающего с выхода 11 регистра микрокоманд 7.

Регистр 4 адреса служит для хранения адреса (i+1)-й микрокоманды.

Коммутатор 5 результирующего адреса коммутирует адрес микрокоманды либо из регистра 4 адреса, либо с входа 8 устройства.

Блок 6 памяти микрокоманд предназначен для хранения микропрограмм выполнения операций.

Регистр 7 микрокоманд служит для хранения i-й микрокоманды.

Вход 10 синхронизации используется для синхронизации работы устройства.

Выход 11 является выходом признака конца микропрограммы и используется для управления третьим состоянием источника начального адреса, поступающего на информационный вход 8 устройства.

Второй выход 12 регистра 7 микрокоманд управляет выбором анализируемого условия.

Выход 13 регистра 7 микрокоманд является информационным выходом устройства.

Выход 14 регистра 7 микрокоманд является выходом поля адреса перехода микрокоманды.

Выход 15 регистра 7 микрокоманд является выходом поля инструкции для формирования адреса микрокоманд.

Работу устройства рассмотрим на примере выполнения гипотетической микропрограммы, граф-схема алгоритма которой приведена на фиг.2. В вершинах алгоритма содержит мнемоника микрокоманд: IP - безусловный переход по адресу из регистра микрокоманд; CONT - продолжить; CIP - условный переход по адресу из регистра микрокоманд; IZ - безусловный переход на нулевой адрес.

Для того, чтобы реализовать данный алгоритм на рассматриваемом устройстве, его необходимо привести к виду, представленному на фиг.3. Это связано с тем обстоятельством, что все переходы в устройстве реализуются с использованием метода отложенного ветвления. При отложенном ветвлении выбирается и выполняется еще одна микрокоманда, прежде чем произойдет фактическое ветвление.

Изображенные на фиг.2 и 3 операторные вершины, которые выполняют одинаковые функции (кроме функции формирования адреса), имеют одинаковые номера, стоящие рядом с мнемокодом инструкции формирователя адреса. Рядом с каждой вершиной обеих граф-схем микропрограмм приведен адрес микрокоманды, соответствующей этой вершине. Для того, чтобы операторная вершина CONТ 31 не изменяла логику алгоритма, приведенного на фиг.2, она является микрокомандой типа "Нет операции" и ее функция заключается только в формировании адреса. Появление "лишней" микрокоманды не приводит к увеличению времени выполнения микропрограммы на заявляемом устройстве, так как в прототипе при выполнении условных переходов следует увеличить длительность такта синхронизации в два раза, чтобы сформировать адрес перехода и выбрать из памяти микрокоманду по этому адресу.

Работа устройства поясняется временными диаграммами (фиг.4), где используются следующие сокращения: ПНА - преобразователь начального адреса (источник начального адреса), БФА - формирователь адреса микрокоманд, РгА - регистр адреса, БПМ - блок памяти микрокоманд. РгМк - регистр микрокоманд. В устройстве за один такт происходит выполнение i-й микрокоманды, код которой находится в регистре 7 микрокоманд, чтение (i+1)-й микрокоманды из блока 6 памяти микропрограмм по адресу, находящемуся в регистре 4 адреса и формирование адреса (i+2)-й микрокоманды в формирователе 2 адреса.

Первоначально по шине 8 в устройство загружается начальный адрес (НА) микропрограммы. Начальные адреса всех микропрограмм должны быть четные (младший разряд адреса всегда нулевой). Это позволяет инкрементировать этот адрес на схеме ИЛИ 3. Данное условие практически не вызывает никаких неудобств для разработчиков, потому что каждая вторая ячейка памяти является четной. В этот момент признак КМП имеет уровень логической "1", который снимает третье состояние с выхода ПНА, устанавливает третье состояние на выходе формирователя 2 адреса и разрешает прохождение начального адреса на вход блока 6 памяти микропрограмм через второй вход коммутатора 5. Одновременно логическая "1", поступая на первый вход элемента ИЛИ 3, вызывает инкрементирование начального адреса. По положительному фронту тактового импульса в конце первого такта в регистр 7 микрокоманд считывается i-я микрокоманда с адресом НА, а в регистр 4 адреса записывается адрес НА + 1 (i+1)-й микрокоманды.

В такте 2 признак КМП исчезает (логический уровень на выходе 11 - нулевой) и снимает третье состояние с выхода формирователя 2 адреса, подключает к выходу коммутатора 5 адреса его первый информационный вход, разрешает прохождение младшего разряда с выхода формирователя адреса без изменения через элемент ИЛИ 3 и устанавливает третье состояние на выходе источника начального адреса. В регистре 7 микрокоманд выполняется i-я микрокоманда (с адресом НА), из блока 6 памяти считывается (i+1)-я микрокоманда по адресу, находящемуся в регистре 4 адреса (адрес НА+1), и в формирователе адреса осуществляется формирование адреса (НА+2) (i+1)-й микрокоманды в результате выполнения инструкции безусловного перехода IPI на адрес НА+2. Таким образом осуществляется разгон конвейера микрокоманд в начале каждой микропрограммы.

В такте 3 выполняется i-я микрокоманда с адресом НА+1, из блока 6 памяти выбирается (i-1)-я микрокоманда с адресом НА-2, который хранится в регистре 4 адреса, в формирователе 2 адреса под действием инструкции CONT формируется адрес (i+2)-й микрокоманды НА+3.

В такте 4 выполняется микрокоманда условного перехода с адресом НА+2 (условие перехода не выполняется). В соответствии с этим в формирователе 2 адреса под действием инструкции CIP3 формируется адрес НА+4, из блока 6 памяти считывается микрокоманда с адресом НА+3.

В такте 5 в регистре 7 микрокоманд находится микрокоманда CONТ 31 с адресом НА+3. Эта микрокоманда не выполняет какие-либо действия в операционном устройстве. Функция этой микрокоманды заключается только в наращивании адреса в формирователе 2. В этом такте с помощью инструкции CONT 31 формируется адрес НА+5 и из блока 6 памяти считывается микрокоманда с адресом НА+4.

В такте 6 выполняется микрокоманда безусловного перехода на адрес НА+2. При этом в формирователе 2 адреса микрокоманд под действием инструкции IP 4 формируется адрес НА+2, а из блока 6 памяти считывается микрокоманда с адресом НА+5.

В такте 7 выполняется микрокоманда с адресом НА+5. При этом в формирователе 2 адреса под действием инструкции CONT 5 формируется адрес НА+3, а из блоков памяти считывается микрокоманда условного перехода с адресом НА+2.

В такте 8 выполняется микрокоманда условного перехода IP3 с адресом НА+2. В этом такте условие выполняется и в формирователе 2 адреса под действием инструкции CIP 3 формируется адрес НА+6 (адрес перехода). Из блока 6 памяти считывается микрокоманда с адресом НА+3.

В такте 9 в регистре 7 микрокоманд находится микрокоманда CONT 31, в функции которой входит только формирование адреса (i+2)-й микрокоманды. При этом в формирователе 2 адреса формируется адрес НА+7, а из блока 6 памяти выбирается последняя для этой микропрограммы микрокоманда с адресом НА+6.

В такте 10 выполняется микрокоманда с адресом НА+6. Код инструкции этой микрокоманды может быть произвольный, так как в такте 11 начнется выполнение новой (i+1)-й микропрограммы. Для определенности код инструкции - IZ 6. В этом такте в регистре 7 микрокоманд на выходе 11 появляется единичный сигнал признака КМП, который снимает третье состояние с выхода ПНА, устанавливает третье состояние на выходе формирователя 2 адреса и разрешает прохождение начального адреса на вход блока 6 памяти микропрограммы через второй вход коммутатора 5. Одновременно эта единица, поступая на первый вход элемента ИЛИ 3, вызывает инкрементирование начального адреса. Таким образом, микропрограммное устройство переходит к выполнению (i+1)-й микропрограммы.

Реализацию предлагаемого изобретения можно осуществить на микросхемах серий К1804, К1531, К556. Коммутатор 5 результирующего адреса реализуется на микросхемах К1531, КП11, коммутатор условий - на микросхемах К1531, КП15, регистр 4 адреса микрокоманд и регистр 7 микрокоманд - на микросхемах К1531, ТМ9, блок памяти микрокоманд - на микросхемах К556Р17, формирователь 2 адреса микрокоманд - на микросхемах К1804ВУ1 и К1804ВУ3, элемент ИЛИ на микросхеме К1531ЛЛ1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования карты местности перед транспортным средством | 1989 |

|

SU1689971A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| Микропрограммное устройство управления | 1989 |

|

SU1636845A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Устройство для распаковки команд | 1990 |

|

SU1702367A1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЕННОЙ ПАМЯТИ | 2001 |

|

RU2210804C2 |

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления вычислительных систем. Целью изобретения является упрощение устройства. Для этого устройство содержит коммутатор условий, формирователь адреса микрокоманд, элемент ИЛИ, регистр адреса, коммутатор результирующего адреса, блок памяти микрокоманд и регистр микрокоманд. 4 ил.

УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ, содержащее формирователь адреса микрокоманд, регистр адреса, коммутатор результирующего адреса, блок памяти микрокоманд, регистр микрокоманд и коммутатор условий, информационные входы которого являются входами условий устройства, выход коммутатора условий соединен с первым управляющим входом формирователя адреса микрокоманд, управляющий вход коммутатора условий соединен с выходом поля анализа условий регистра микрокоманд, выходы поля адреса управления модификацией адреса которого соединены соответственно с информационным и вторым управляющим входами формирователя адреса микрокоманд, выход которого подключен к второму информационному входу коммутатора результирующего адреса, первый информационный вход которого соединен с выходом регистра адреса, выход коммутатора результирующего адреса соединен с адресным входом блока памяти микрокоманд, выход которого подключен к информационному входу регистра микрокоманд, выход поля микроопераций которого соединен с информационным выходом устройства, вход синхронизации регистра микрокоманд соединен с входами синхронизации регистра адреса, формирователя адреса микрокоманд и входом синхронизации устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит элемент ИЛИ, первый вход которого соединен с третьим управляющим входом формирователя адреса микрокоманд, управляющим входом коммутатора результирующего адреса и выходом признака конца микрокоманды регистра микрокоманд, второй вход элемента ИЛИ подключен к выходу младшего разряда формирователя адреса микрокоманд, выход элемента ИЛИ подключен к младшему разряду информационного входа регистра адреса, старшие разряды информационного входа которого соединены с выходами старших разрядов формирователя адреса микрокоманд, к выходам которого подключен также вход адреса устройства, выход признака конца микропрограммы которого соединен с выходом поля конца микропрограммы регистра микрокоманд.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Проектирование цифровых систем на комплектах микропрограммируемых БИС/ | |||

| Под ред | |||

| В.Г.Колесникова | |||

| М.: Радио и связь, 1984, с.203-207. | |||

Авторы

Даты

1994-09-30—Публикация

1991-01-21—Подача