Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах.

Известно устройство для суммирования нескольких последовательно поступающих чисел, содержащее два регистра, счетчик, оперативное запоминающее устройство, вы- читатель, накапливающий сумматор и формирователь импульсов, в котором производится накопление результата суммирования.

Недостатком устройства является его сложность и отсутствие логических операций.

Известно арифметическое устройство, содержащее регистры операндов, вспомогательные регистры, основной и байтовый сумматоры, коммутаторы и регистры сумматоров.

Недостатком данного АУ является его сложность и отсутствие операций накопления при суммировании нескольких чисел.

Наиболее близким к предлагаемому является вычислительное устройство, содержащее регистры первого и второго операндов, регистр состояния, сметчик циклов, блок регистров общего назначения, регистр информации, регистр данных, арифметико-логический блок, сдвигатель, входной коммутатор второго операнда, коммутаторы первого и второго операндов, блок микропрограммного управления, две схемы сравнения с нулем, схему сравнения, дешифратор разрядов множителя, коммутатор данных и коммутатор информации, коммутатор признаков, регистр признаков и схему сравнения с константой, причем выходы коммутаторов первого и второго операндов соединены с соответствующими информационными входами арифметико- логического блока, выход результата которого соединен с входом первой схемы сравнения с нулем, выход которого соеди2

о© ы

ней с первым входом условия перехода блока микропрограммного управления, вход начального адреса и тактовый вход которого соединены соответственно с входом запуска и тактовым входом устройства, информационная шина которого соединена с первым информационным входом входного коммутатора второго операнда и с выходом регистра информации, выходы регистра состояния и регистра первого операнда соединены соответственно с первым и вторым информационными входами сдви- гателя, выход входного коммутатора второго операнда соединен с информационным входом регистра второго операнда, выход которого соединен с информационным входом коммутатора второго операнда, выход регистра первого операнда соединен с информационным входом коммутатора первого операнда, выходы двух младших разрядов регистра данных соединены соответственно с входами разрядов дешифратора разрядов множителя, выход счетчика циклов соединен с входом второй схемы сравнения с нулем, выход которой соединен с входом условия перехода блока микропрограммного управления, третий вход условия перехода которого соединен с выходом схемы сравнения, первый вход которой соединен с четвертым входом условия перехода блока микропрограммного управления и с выходом старшего разряда регистра второго операнда, выход коммутатора данных соединен с информационным входом регистра данных, выходы с первого по тридцатый блока микропрограммного управления соединены соответственно с входом разрешения приема регистра состояния, с входом разрешения приема, адресными входами с первого по четвертый и с входом разрешения чтения блока регистров общего назначения, с входами разрешения приема и чтения регистра информации, с управляющим входом входного коммутатора второго операнда, с входом разрешения приема регистра первого операнда, с входом разрешения приема регистра второго операнда, с управляющим входом коммутатора первого операнда, с управляющим входом коммутатора второго операнда, с первым и вторым входами управления функциями сдвигателя, с входами разрешения чтения сдвигателя и арифметико-логического блока, с входами с первого по пятый вида операции арифметико-логического блока, с управляющим входом разрешения приема дешифратора разрядов множителя, с входом разрешения приема регистра данных, с первым и вторым управляющими входами коммутатора информации, с входом разрешения приема, суммирующим и вычитающим входами счетчика циклов, выходы блока регистров общего назначения, регистра информации и коммутатора информации

объединены и соединены с информационным входом регистра первого операнда, с третьим информационным входом сдвигателя, выход регистра информации соединен с вторым информационным входом входного коммутатора второго операнда, информационная шина устройства соединена с первым информационным входом регистра информации, выход сдвигателя и выход результата арифметико-логического блока

объединены и соединены с информационными входами регистра состояния, блока регистров общего назначения и счетчика циклов, с вторым информационным входом регистра информации, с первыми информационными входами коммутатора данных соединен с вторыми информационными входами коммутатора данных и коммутатора информации, третий информационный вход которого соединен с выходом первой схемы

сравнения с нулем, выходы дешифратора разрядов множителя и схемы сравнения с константой соединены соответственно с пятым и шестым входами условия перехода блока микропрограммного управления,

седьмой вход условия перехода которого соединен с вторым входом схемы сравнения, с первым входом схемы сравнения с константой, с первым информационным входом коммутатора признаков и с выходом

младшего разряда регистра данных, выход первой схемы сравнения с нулем соединен с вторым информационным входом коммутатора признаков, выход которого соединен с информационным входом регистра признаков, выход которого соединен с восьмым входом условия перехода блока микропрограммного управления, выходы второго и третьего разрядов регистра признаков соединены с вторым входом схемы сравнения

с константой, третий вход которой соединен с выходом старшего-разряда регистра второго операнда, выход переноса арифметико-логического блока соединен с третьим информационным входом коммутатора данных и с третьим информационным входом коммутатора признаков, четвертый, пятый и шестой информационные входы которого соединены соответственно с выходами младшего и двух старших разрядов регистра первого операнда, выходы с тридцать первого по тридцать шестой блока микропрограммного управления соединены соответственно с входом начальной установки регистра признаков, с первым и вторым управляющими входами коммутатора признаков, с входами разрешения приема нулевого, первого, второго и третьего разрядов регистра признаков.

Целью изобретения является сокращение аппаратурных затрат.

Поставленная цель достигается тем, что в устройство для обработки данных, содержащее регистр первого операнда, регистр второго операнда, входной коммутатор, коммутатор операндов, промежуточный регистр, арифметико-логический блок, первый и второй коммутаторы результата, счетчик, первый регистр сдвига, коммутатор переноса, триггер признака и дешифратор команд, причем входы первого и второго операндов устройства соединены соответственно с первым и вторым информационными входами входного коммутатора, выход которого соединен с информационным входом регистра второго операнда, выход которого соединен с первым информационным входом коммутатора операндов, вход задания вида операции устройства соединен с первым информационным входом дешифратора команд, тактовый вход устройства соединен с входами разрешения записи регистра первого операнда, регистра второго операнда, первого регистра сдвига, триггера признака, промежуточного регистра и с тактовым входом дешифратора команд, выход результата арифметико-логического блока соединен с первым информационным входом первого коммутатора результата, выход регистра первого операнда соединен с первым информационным входом второго коммутатора результата, с первого по девятый выходы дешифратора команд соединены соответственно со входами разрешения записи и разрешения счета счетчика, с управляющими входами входного коммутатора и коммутатора операндов, с входом задания вида операции арифметико-логического блока, с управляющими входами первого коммутатора результата, второго коммутатора результата и коммутатора переноса, с входом задания режима первого регистра сдвига, введены второй регистр сдвига и выходной коммутатор, причем вход второго операнда устройства соединен с вторым информационным входом коммутатора операндов, третий информационный вход которого соединен с выходом регистра первого операнда и с информационным входом счетчика, выход которого соединен с вторым информационным входом второго коммутатора результата, выход которого соединен с параллельным информационным входом второго регистра сдвига, выходы младшего и старшего разрядов которого соединены соответственно с первым и вторым

информационными входами коммутатора переноса, третий информационный вход и выход которого соединены соответственно с входом переноса устройства и с входом 5 переноса арифметико-логического блока, выход знака которого соединен с вторым информационным входом дешифратора команд и с информационным входом триггера признака, выход которого является выходом

0 признака устройства, выход результата которого соединен с выходом выходного коммутатора, первый информационный вход которого соединен с выходом первого регистра сдвига, параллельный информацион5 ный вход которого соединен с выходом первого коммутатора результата, второй информационный вход которого соединен с первым информационным входом арифметико-логического блока, с четвертым инфор0 мационным входом коммутатора операндов и с выходом промежуточного регистра, информационный вход которого соединен с выходом коммутатора операндов, пятый информационный вход которого соединен с

5 выходом результата арифметико-логического блока, второй информационный вход которого соединен с третьим информационным входом первого коммутатора результата и с «ыходом регистра второго операнда, выход

0 переноса арифметико-логического блока соединен с счетным входом счетчика, с последовательным информационным входом второго регистра сдвига и является выходом переноса устройства, выходы разрядов второго

5 регистра сдвига соединены с соответствующими разрядами второго информационного входа выходного коммутатора, выход входного коммутатора соединен с информационным входом регистра первого операнда,

0 выход младшего разряда второго регистра сдвига соединен с последовательным информационным входом первого регистра сдвига, тактовый вход устройства соединен с тактовым входом второго регистра сдвига,

5 с десятого по тринадцатый выходы дешифратора команд соединены соответственно со входом установки в О регистра второго операнда, с входом обнуления счетчика, с управляющим входом выходного коммута0 тора и с входом задания режима второго регистра сдвига.

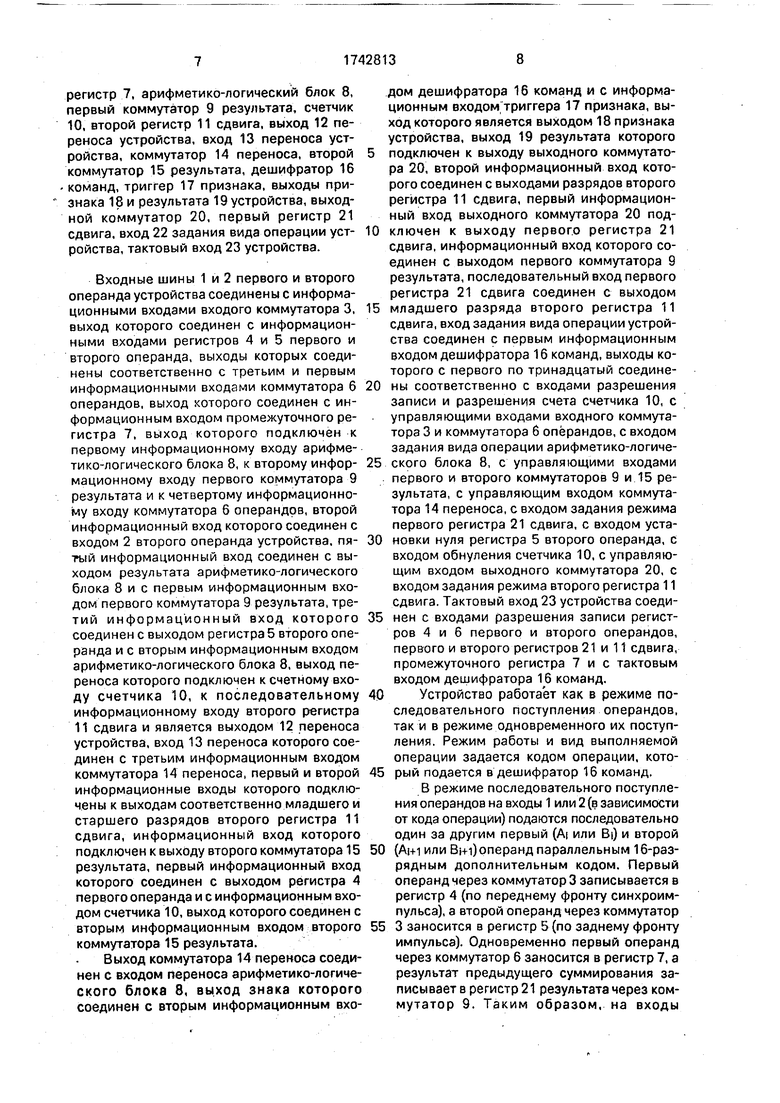

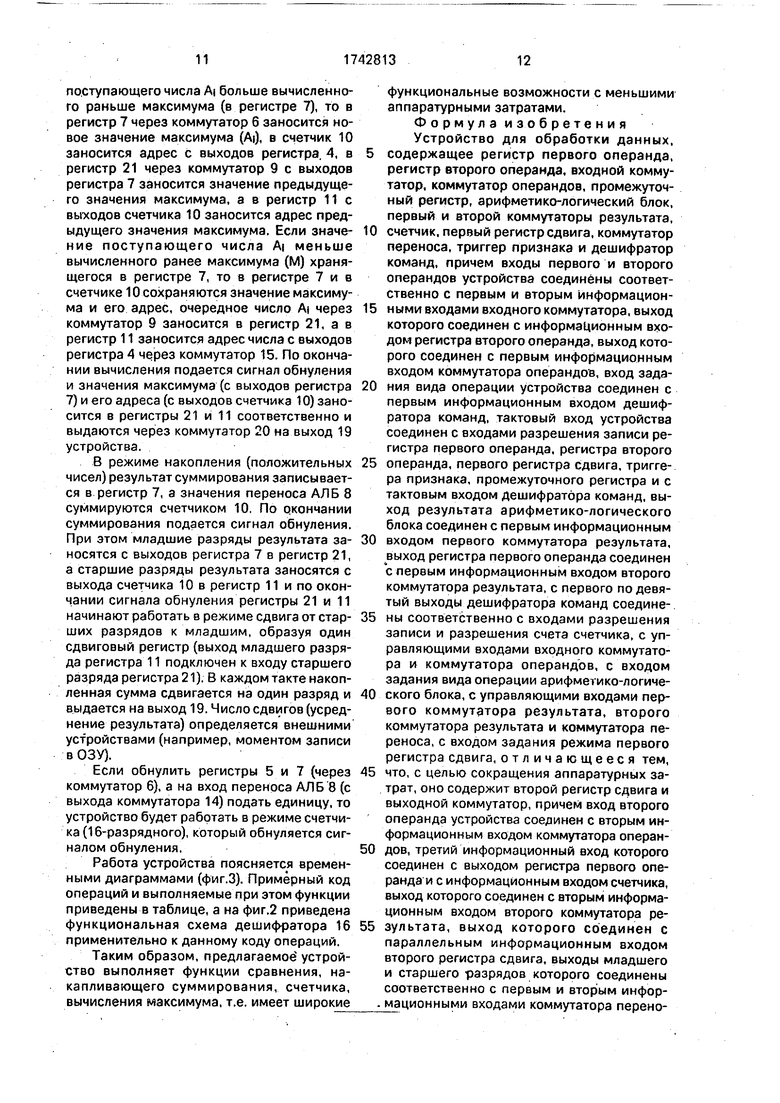

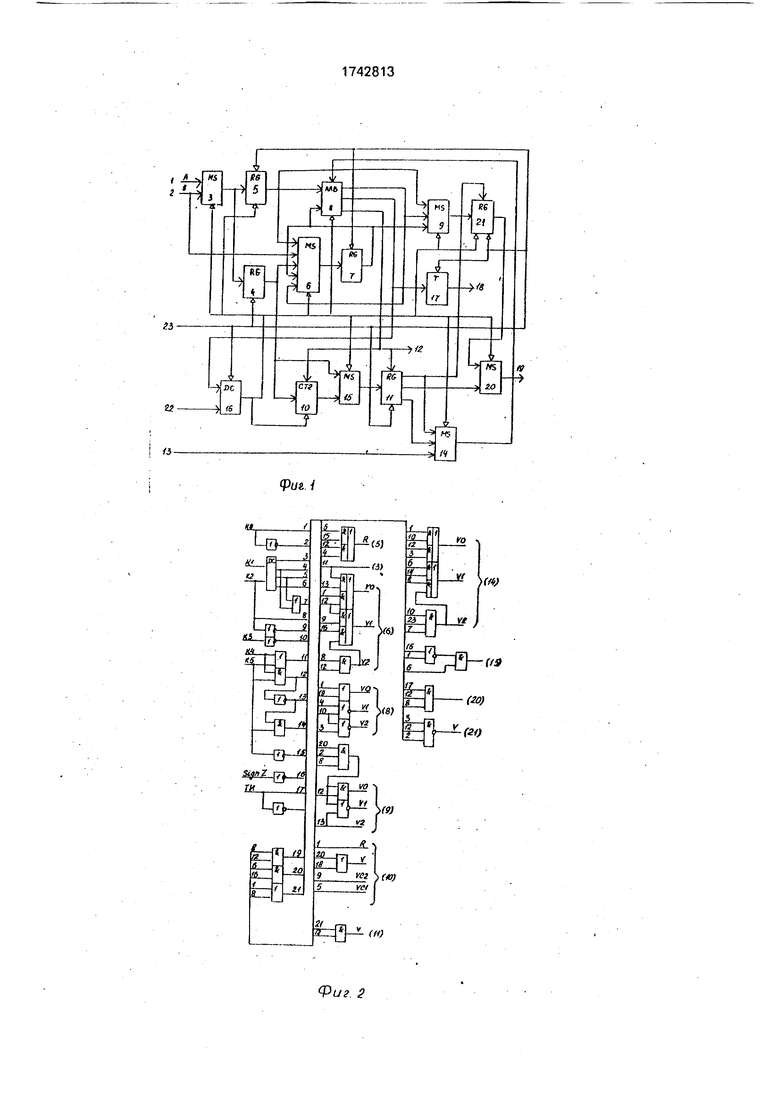

На фиг.1 приведена структурная схема АУ; на фиг.2 - функциональная схема дешифратора команд; на фиг.З - временные

5 диаграммы работы устройства.

Устройство для обработки данных содержит входные шины 1 и 2 первого и второго операндов, входной коммутатор 3, регистры 4 и 5 первого и второго операндов, коммутатор 6 операндов, промежуточный

егистр 7, арифметико-логический блок 8, ервый коммутатор 9 результата, счетчик 10, второй регистр 11 сдвига, выход 12 переноса устройства, вход 13 переноса устройства, коммутатор 14 переноса, второй коммутатор 15 результата, дешифратор 16 команд, триггер 17 признака, выходы принака 18 и результата 19 устройства, выходной коммутатор 20, первый регистр 21 сдвига, вход 22 задания вида операции устройства, тактовый вход 23 устройства.

Входные шины 1 и 2 первого и второго операнда устройства соединены с информационными входами входого коммутатора 3, выход которого соединен с информационными входами регистров 4 и 5 первого и второго операнда, выходы которых соединены соответственно с третьим и первым информационными входами коммутатора 6 операндов, выход которого соединен с информационным входом промежуточного регистра 7, выход которого подключен к первому информационному входу арифметико-логического блока 8, к второму информационному входу первого коммутатора 9 результата и к четвертому информационному входу коммутатора 6 операндов, второй информационный вход которого соединен с входом 2 второго операнда устройства, пятый информационный вход соединен с выходом результата арифметико-логического блока 8 и с первым информационным входом первого коммутатора 9 результата, третий информационный вход которого соединен с выходом регистра 5 второго операнда и с вторым информационным входом арифметико-логического блока 8, выход переноса которого подключен к счетному входу счетчика 10, к последовательному информационному входу второго регистра 11 сдвига и является выходом 12 переноса устройства, вход 13 переноса которого соединен с третьим информационным входом коммутатора 14 переноса, первый и второй информационные входы которого подключены к выходам соответственно младшего и старшего разрядов второго регистра 11 сдвига, информационный вход которого подключен к выходу второго коммутатора 15 результата, первый информационный вход которого соединен с выходом регистра 4 первого операнда и с информационным входом счетчика 10, выход которого соединен с вторым информационным входом второго коммутатора 15 результата.

Выход коммутатора 14 переноса соединен с входом переноса арифметико-логического блока 8, выход знака которого соединен с вторым информационным входом дешифратора 16 команд и с информационным входом триггера 17 признака, выход которого является выходом 18 признака устройства, выход 19 результата которого

подключен к выходу выходного коммутатора 20, второй информационный вход которого соединен с выходами разрядов второго регистра 11 сдвига, первый информационный вход выходного коммутатора 20 под0 ключей к выходу первого регистра 21 сдвига, информационный вход которого соединен с выходом первого коммутатора 9 результата, последовательный вход первого регистра 21 сдвига соединен с выходом

5 младшего разряда второго регистра 11 сдвига, вход задания вида операции устройства соединен с первым информационным входом дешифратора 16 команд, выходы которого с первого по тринадцатый соедине0 ны соответственно с входами разрешения записи и разрешения счета счетчика 10, с управляющими входами входного коммутатора 3 и коммутатора б операндов, с входом задания вида операции арифметико-логиче5 ского блока 8, с управляющими входами первого и второго коммутаторов 9 и 15 результата, с управляющим входом коммутатора 14 переноса, с входом задания режима первого регистра 21 сдвига, с входом уста0 новки нуля регистра 5 второго операнда, с входом обнуления счетчика 10, с управляющим входом выходного коммутатора 20, с входом задания режима второго регистра 11 сдвига. Тактовый вход 23 устройства соеди5 нен с входами разрешения записи регистров 4 и 6 первого и второго операндов, первого и второго регистров 21 и 11 сдвига, промежуточного регистра 7 и с тактовым входом дешифратора 16 команд.

0 Устройство работает как в режиме последовательного поступления операндов, так и в режиме одновременного их поступления. Режим работы и вид выполняемой операции задается кодом операции, кото5 рый подается в дешифратор 16 команд.

В режиме последовательного поступления операндов на входы 1 или 2 (в зависимости от кода операции) подаются последовательно один за другим первый (А| или В|) и второй

0 (Ai+ч или Bi-ц)операнд параллельным 16-разрядным дополнительным кодом. Первый операнд через коммутатор 3 записывается в регистр 4 (по переднему фронту синхроимпульса), а второй операнд через коммутатор

5 3 заносится в регистр 5 (по заднему фронту импульса). Одновременно первый операнд через коммутатор 6 заносится в регистр 7, а результат предыдущего суммирования записывает в регистр 21 результата через коммутатор 9. Таким образом, на входы

арифметико-логического блока (АЛБ) 8 одновременно подаются два операнда.

АЛБ 8 выполняет операции арифметического сложения и логические операции И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ и др. Операция вычитания выполняется путем подачи на первый вход АЛБ 8 инверсного значения первого операнда (А| или Bi) через коммутатор б, а на вход переноса АЛБ 8 подается единица с выхода коммутатора 14, т.е. прибавляется единица к последнему разряду сумматора, что обеспечивает выполнение операции в дополнительном коде.

Результат операции АЛБ 8 записывается в регистр 21 через коммутатор 9 и выдается на выход 19 устройства через коммутатор 20. АЛ Б 8 имеет схемы ускоренного и групповых переносов, а перенос записывается в регистр 11, который работает в режиме сдвига. Хранение переноса в регистре 11 позволяет строить конвейерный сумматор для 32-разрядных чисел. В первом цикле суммируются младшие 16 разрядов двух операндов. Результат выдается на выход 19, а перенес задерживается на один такт в регистре 11 (в старшем разряде регистра). Во втором цикле суммируются старшие 16 разрядов операндов и перенос от предыдущего цикла, который с выхода старшего разряда регистра 11 через коммутатор 14 подается на вход переноса АЛБ 8.

При суммировании (вычитании) массива 32-разрядных чисел (по 16 пар чисел) в регистре 11 запоминается 16 значений переносов (от суммирования каждой пары операндов) и, начиная с 17 цикла (по 32), они выдаются через коммутатор 14 с младшего разряда регистра 11 на вход переноса АЛ Б 8.

При подаче на вход установки нуля регистра 5 единичного потенциала (с одного из выходов дешифратора 16 команд) сумматор выдает положительное (А| + 0) или отрицательное (А| плюс 1) значения первого (или второго) операнда в дополнительном коде.

Логические операции выполняются АЛБ 8 в зависимости от кода операции, который поступает в АЛБ 8 с выходов дешифратора 16 команд:

А|фАн-1, А ЛА|+Т, Ai vAi-M при AJ;

А|фАц-1, AivAi-ц, A,v АТй при AI;

AI при обнулении регистра 5.

При получении модуля операнда коммутатор 9 выдает нулевое значение старшего (знакового) разряда и мантиссу числа в зависимости от знака входного операнда при обнулении регистра 5):

А при А О,

А плюс 1 при А 0.

При работе в режиме преобразования из прямого кода в дополнительный знаковый разряд отрицательного числа также инвертируется коммутатором 6, а при преобразовании из дополнительного кода в прямой знаковый разряд числа передается

без изменений. Все арифметические и логические операции могут быть получены и при одновременной подаче двух операндов. При этом в регистр 7 заносится второй операнд (В) с входа 2 через коммутатор 6 (пря0 мой или инверсный код), а в регистр 5 заносится первый операнд (А) с входа 1 через коммутатор 3.

Устройство выполняет также некоторые специальные арифметические операции

5 (сравнения, выделения максимального числа из нескольких чисел с их признаками, накапливающее суммирование) и может работать в режиме счетчика. Все эти операции начинаются с обнуления регистра 7 и счет0 чика 10 сигналом обнуления (R) от дешифратора 16 команд. Регистр 7 обнуляется за счет подачи нулевого значения операнда с выходов коммутатора б.

В режиме сравнения сумматор выпол5 няет операцию вычитания (Ан-1-Ai). В каждом цикле сравнения в регистр 21 через коммутатор 9 заносится значение второго операнда (Ai+i) с выходов регистра 5, а в триггер 17 признака - значение старшего

0 разряда АЛБ 8 (знак результата). Значения признака выдаются на выход 13 устройства в каждом цикле. Счетчик 10 работает в режиме счета (на счетный вход подается единица) и выдает в регистр 11 через коммутатор 15

5 порядовый номер пары сравнительных чисел. На выход 19 через коммутатор 20 выдаются в полуцикле значения второго операнда (с выходов регистра 21) и порядкового номера (с выходов регистра 11). По при0 знаку сравнения ( 0 или 0) во внешнем устройстве (например, ОЗУ) происходит запись тех значений операндов (и их адреса в массиве), которые больше (или меньше) какого-то порога (первый операнд).

5При выделении максимального числа из

массива чисел в регистр 5 подается очередное число, а в регистр 4 заносится его адрес в массиве. При подаче сигнала обнуления в регистр 7 и в счетчик 10 заносится нулевой

0 потенциал. Коммутацию записи информации в регистры 7 и 21, а также в счетчик 10 осуществляет сигнал сравнения с выхода ста ршего (знакового) разряда АЛБ 8, который подается в дешифратор 16. В первом

5 цикле сравнения в счетчик 10 заносится адрес операнда с выходов регистра 4, а в регистр 7 заносится значение первого числа (Ai-M 0, где М - значение вычисляемого максимума, которое хранится в регистре 7 и в первом цикле равно нулю). Если значение

поступающего числа AI больше вычисленного раньше максимума (в регистре 7), то в регистр 7 через коммутатор 6 заносится новое значение максимума (А|), в счетчик 10 заносится адрес с выходов регистра. 4, в регистр 21 через коммутатор 9 с выходов регистра 7 заносится значение предыдущего значения максимума, а в регистр 11с выходов счетчика 10 заносится адрес предыдущего значения максимума. Если значение поступающего числа AI меньше вычисленного ранее максимума (М) хранящегося в регистре 7, то в регистре 7 и в счетчике 10 сохраняются значение максимума и его адрес, очередное число At через коммутатор 9 заносится в регистр 21, а в регистр 11 заносится адрес числа с выходов регистра 4 через коммутатор 15. По окончании вычисления подается сигнал обнуления и значения максимума (с выходов регистра 7) и его адреса (с выходов счетчика 10) заносится в регистры 21 и 11 соответственно и выдаются через коммутатор 20 на выход 19 устройства.

В режиме накопления (положительных чисел) результат суммирования записывается в регистр 7, а значения переноса АЛ Б 8 суммируются счетчиком 10. По окончании суммирования подается сигнал обнуления. При этом младшие разряды результата заносятся с выходов регистра 7 в регистр 21, а старшие разряды результата заносятся с выхода счетчика 10 в регистр 11 и по окончании сигнала обнуления регистры 21 и 11 начинают работать в режиме сдвига от старших разрядов к младшим, образуя один сдвиговый регистр (выход младшего разряда регистра 11 подключен к входу старшего разряда регистра 21). В каждом такте накопленная сумма сдвигается на один разряд и выдается на выход 19. Число сдвигов (усреднение результата) определяется внешними устройствами (например, моментом записи в ОЗУ).

Если обнулить регистры 5 и 7 (через коммутатор 6), а на вход переноса АЛ Б 8 (с выхода коммутатора 14) подать единицу, то устройство будет работать в режиме счетчика (16-разрядного), который обнуляется сигналом обнуления.

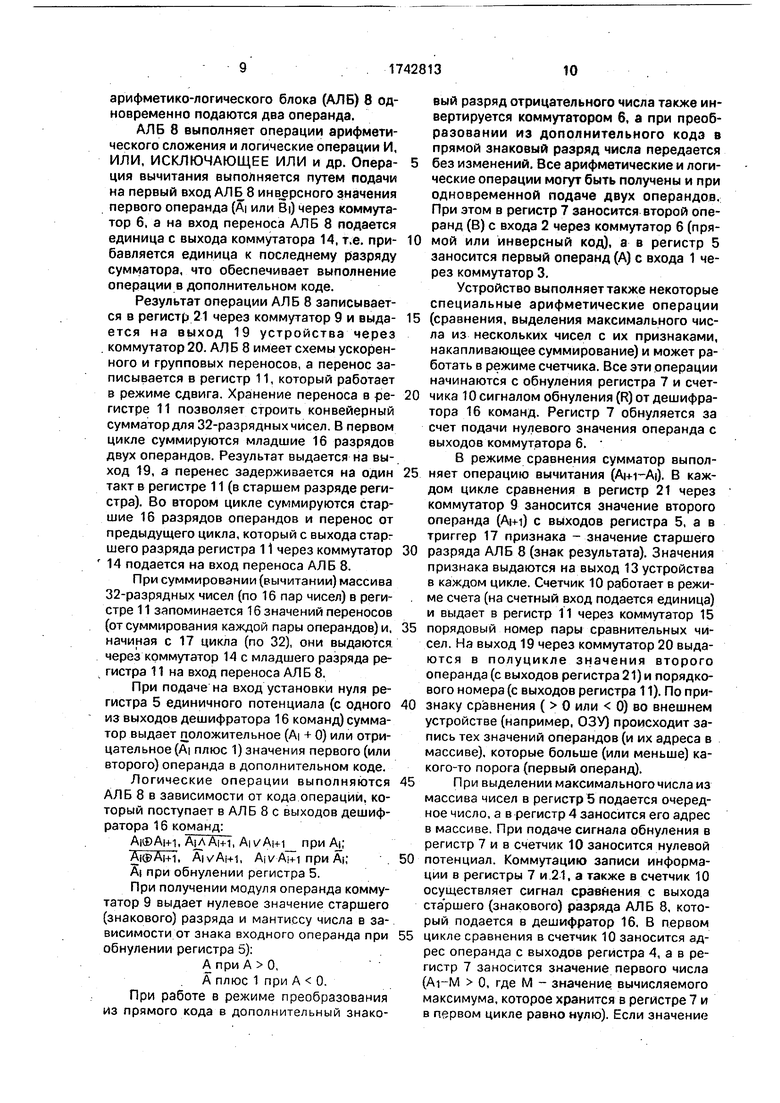

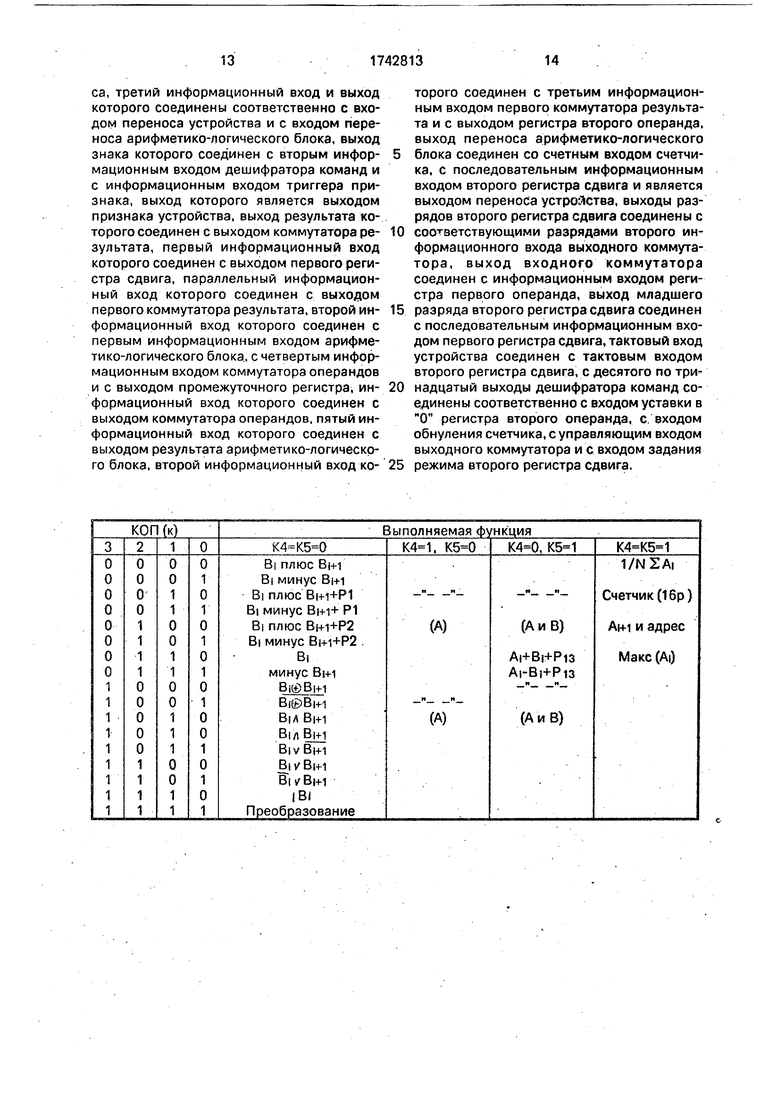

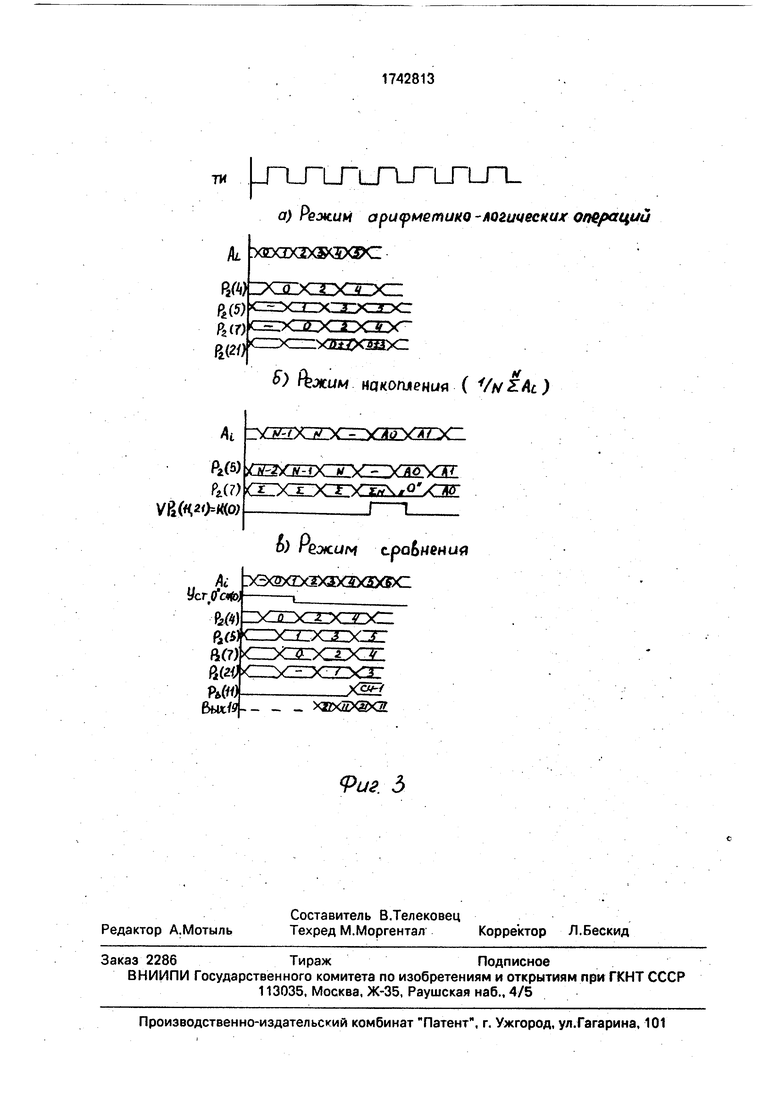

Работа устройства поясняется временными диаграммами (фиг.З). Примерный код операций и выполняемые при этом функции приведены в таблице, а на фиг.2 приведена функциональная схема дешифратора 16 применительно к данному коду операций.

Таким образом, предлагаемое устройство выполняет функции сравнения, накапливающего суммирования, счетчика, вычисления максимума, т.е. имеет широкие

функциональные возможности с меньшими аппаратурными затратами.

Формула изобретения Устройство для обработки данных,

содержащее регистр первого операнда, регистр второго операнда, входной коммутатор, коммутатор операндов, промежуточный регистр, арифметико-логический блок, первый и второй коммутаторы результата,

0 счетчик, первый регистр сдвига, коммутатор переноса, триггер признака и дешифратор команд, причем входы первого и второго операндов устройства соединены соответственно с первым и вторым информацион5 ными входами входного коммутатора, выход которого соединен с информационным входом регистра второго операнда, выход которого соединен с первым информационным входом коммутатора операндов, вход зада0 ния вида операции устройства соединен с первым информационным входом дешифратора команд, тактовый вход устройства соединен с входами разрешения записи регистра первого операнда, регистра второго

5 операнда, первого регистра сдвига, триггера признака, промежуточного регистра и с тактовым входом дешифратора команд, выход результата арифметико-логического блока соединен с первым информационным

0 входом первого коммутатора результата, выход регистра первого операнда соединен с первым информационным входом второго коммутатора результата, с первого по девятый выходы дешифратора команд соедине5 ны соответственно с входами разрешения записи и разрешения счета счетчика, с управляющими входами входного коммутатора и коммутатора операндов, с входом задания вида операции арифмешко-логиче0 ского блока, с управляющими входами первого коммутатора результата, второго коммутатора результата и коммутатора переноса, с входом задания режима первого регистра сдвига, отличающееся тем,

5 что, с целью сокращения аппаратурных затрат, оно содержит второй регистр сдвига и выходной коммутатор, причем вход второго операнда устройства соединен с вторым информационным входом коммутатора операн0 дов, третий информационный вход которого соединен с выходом регистра первого операнда и с информационным входом счетчика, выход которого соединен с вторым информационным входом второго коммутатора ре5 зультата, выход которого соединен с параллельным информационным входом второго регистра сдвига, выходы младшего и старшего разрядов которого соединены соответственно с первым и вторым инфор- . мационными входами коммутатора переноса, третий информационный вход и выход которого соединены соответственно с входом переноса устройства и с входом переноса арифметико-логического блока, выход знака которого соединен с вторым инфор- мационным входом дешифратора команд и с информационным входом триггера признака, выход которого является выходом признака устройства, выход результата которого соединен с выходом коммутатора ре- зультата, первый информационный вход которого соединен с выходом первого регистра сдвига, параллельный информационный вход которого соединен с выходом первого коммутатора результата, второй ин- формационный вход которого соединен с первым информационным входом арифметико-логического блока, с четвертым информационным входом коммутатора операндов и с выходом промежуточного регистра, ин- формационный вход которого соединен с выходом коммутатора операндов, пятый информационный вход которого соединен с выходом результата арифметико-логического блока, второй информационный вход ко-

торого соединен с третьим информационным входом первого коммутатора результата и с выходом регистра второго операнда, выход переноса арифметико-логического блока соединен со счетным входом счетчика, с последовательным информационным входом второго регистра сдвига и является выходом переноса устройства, выходы разрядов второго регистра сдвига соединены с соответствующими разрядами второго информационного входа выходного коммутатора, выход входного коммутатора соединен с информационным входом регистра первого операнда, выход младшего разряда второго регистра сдвига соединен с последовательным информационным входом первого регистра сдвига, тактовый вход устройства соединен с тактовым входом второго регистра сдвига, с десятого по тринадцатый выходы дешифратора команд соединены соответственно с входом уставки в О регистра второго операнда, с входом обнуления счетчика, с управляющим входом выходного коммутатора и с входом задания режима второго регистра сдвига.

«.

EZQ-S-W

(го

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения полей | 1987 |

|

SU1479927A1 |

| Устройство для сопряжения | 1980 |

|

SU877520A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для обработки нечеткой информации | 1989 |

|

SU1674145A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Арифметико-логическая секция | 1987 |

|

SU1499333A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных устройствах и системах. Целью изобретения является сокращение аппаратурных затрат. Устройство для обработки данных содержит регистр первого операнда, регистр второго операнда, входной коммутатор, коммутатор операндов, промежуточный регистр, арифметико-логический блок, первый и второй коммутаторы результата, счетчик, первый и второй регистры сдвига, коммутатор переноса, триггер признака, дешифратор команд и выходной коммутатор. 3 ил., 1 табл.

Фиг 2

ТИ

а) Режим арифметика -логических операций

k

ЖХ1Х2ХЗ ЗХРС

ра)реюсгхзэс:

Рг(5) РгЮ №)

С ЭС2ЭСХХЗОГ

шххддрсшхг

Ј) гЪким накопления ( /NZAt.)

Ai Рг(5)

Pi()

Vfcft f i«o;

W гелси/vf срабмения

Лс bOOXCXlXIX2X2X C Усг/сф,

ftcsj сгзспхзэсг: в()

Ј(2{J CZ ЈZDCZ3 X P4(ffj -x

Выс/э--

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Вычислительное устройство | 1984 |

|

SU1280611A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-06-23—Публикация

1990-01-10—Подача