Изобретение относится к области вычислительной техники и предназначено для построения коммутационных сетей вычислительных систем.

Известно коммутационное устройство для вычислительной системы (авт. св. N 746492, ОИПОТЗ N 25 1980), содержащее матричный коммутатор, дешифратор (присутствуют в заявляемом техническом решении), блок управления и матрицу управления коммутацией.

Однако, известное устройство обладает следующим недостатком: нет возможности обеспечения высокой надежности систем и устройств, использующих данный коммутатор путем резервирования каналов передачи информации. Причиной данного недостатка является отсутствие аппаратных средств реализации режима резервирования.

Известен матричный коммутатор (Р.С.Кильметов и др. Матричный коммутатор с внутренним контролем информации, 2-я Крымская конференция, СВЧ - техника и спутниковый прием. Материалы конференции. Севастополь, 8-10 октября 1992, с. 448-453), содержащий матрицу элементов коммутации, входные и выходные буферы, регистры кода адреса (присутствуют в заявляемом техническом решении), блок контроля и устройство управления. Устройство обеспечивает соединение каждого выхода с любым из входов. Система встроенного контроля осуществляет оперативный контроль передаваемой информации в выбранном канале коммутации путем сравнения сигналов на входе и выходе коммутатора. Устранение неисправности достигается путем реконфигурации соединений или подключения резервных элементов коммутации.

К недостаткам устройства следует отнести невозможность повышения надежности систем при использовании данного коммутатора, связанную с отсутствием режимов резервирования каналов передачи и исправления информации.

Причиной указанных недостатков является отсутствие схем мажорирования информации.

Наиболее близким к заявляемому является программируемый коммутатор IMS COO4 (Transputer databook. Second Edition 1989).

Коммутатор содержит 32 мультиплексора 32x1, адресные регистры и выходные буферные каскады.

К недостаткам известного устройства следует отнести ограниченные функциональные возможности и низкую надежность в связи с отсутствием режимов резервирования.

Цель изобретения - повышение надежности и расширение функциональных возможностей коммутатора.

Технический результат, достигаемый при осуществлении изобретения, состоит во введении режимов резервирования каналов, регистрации ошибок в каналах, исправлении одиночных ошибок при мажорировании.

Для достижения технического результата в матричный коммутатор, содержащий M коммутационных каналов, каждый из которых включает четыре адресных регистра, выходы каждого из которых, начиная с четвертого разряда, подключены к адресным входам соответствующих мультиплексоров, введен элемент ИЛИ, а в каждый коммутационный канал введены блок резервирования информационных каналов и четыре приемо-передатчика, информационные входы-выходы которых являются соответствующими информационными входами-выходами коммутатора, а управляющие входы приемо-передатчиков подключены к выходам первого разряда соответствующих адресных регистров, каждый из которых соединен выходом второго разряда с соответствующим входом первой группы управляющих входов блока резервирования информационных каналов, а выходом третьего разряда - с соответствующим входом второй группы управляющих входов блока резервирования информационных каналов, подключенного управляющими выходами к информационным входам третьего разряда соответствующих адресных регистров, информационными входами первой группы - к выходам соответствующих мультиплексоров, информационными входами второй группы - к выходам соответствующих приемо-передатчиков, информационными выходами - к информационным входам соответствующих приемо-передатчиков, а выходом сигнала отказа - к соответствующему входу элемента ИЛИ, выход которого является сигнальным выходом коммутатора, информационные входы адресных регистров являются управляющим входом коммутатора, информационные входы мультиплексоров являются информационным входом коммутатора, причем, блок резервирования информационных каналов содержит дешифратор режима, дешифратор отказа, дешифратор ошибок, шесть схем сравнения, четыре управляемых инвертора, селектор, первые информационные входы которого являются первой группой информационных входов блока и подключены к первым информационным входам соответствующих управляемых инверторов, вторые информационные входы селектора являются второй группой информационных входов блока, а управляющий вход селектора соединен с первым выходом дешифратора режима, подключенного вторым выходом к первому входу дешифратора ошибок, связанного вторым входом с выходом первой схемы сравнения и с первым входом дешифратора отказа, третьим, четвертым, пятым и шестым входами - с выходами соответственно второй, третьей, четвертой и пятой схем сравнения, а седьмым входом - с выходом шестой схемы сравнения и со вторым входом дешифратора отказа, подключенного первой группой входов к группе выходов дешифратора режима, соединенного третьим выходом с управляющими входами первого, второго, третьего и четвертого управляемых инверторов, подключенных вторыми информационными входами соответственно к первому, второму, третьему и четвертому выходам дешифратора ошибок, первый выход селектора соединен с первыми входами первой, второй и третьей схем сравнения, второй выход селектора подключен ко второму входу первой схемы сравнения и к первым входам четвертой и пятой схем сравнения, третий выход селектора связан со вторыми входами второй и четвертой схем сравнения и с первым входом шестой схемы сравнения, четвертый выход селектора подключен ко вторым входам третьей, пятой и шестой схем сравнения, группа входов дешифратора режимов является второй группой управляющих входов блока, вторая группа входов и группа выходов дешифратора отказа является соответственно первой группой управляющих входов блока, выходы управляемых инверторов являются информационными выходами блока, выход дешифратора отказа является выходом сигнала отказа блока.

Наличие причинно-следственной связи между совокупностью существенных признаков заявляемого объекта и достигнутым техническим результатом доказывается на основании нижеследующих выводов.

Расширение функциональных возможностей достигается за счет введения режимов резервирования: дублирования, троирования, квадрирования информационных каналов. Кроме того, осуществляется регистрация ошибки в регистрах адреса и при контрольной выгрузке их содержимого можно диагностировать какой канал и в каком из режимов отказал. А введение режимов резервирования с исправлением одиночных ошибок позволяет повысить надежность коммутации.

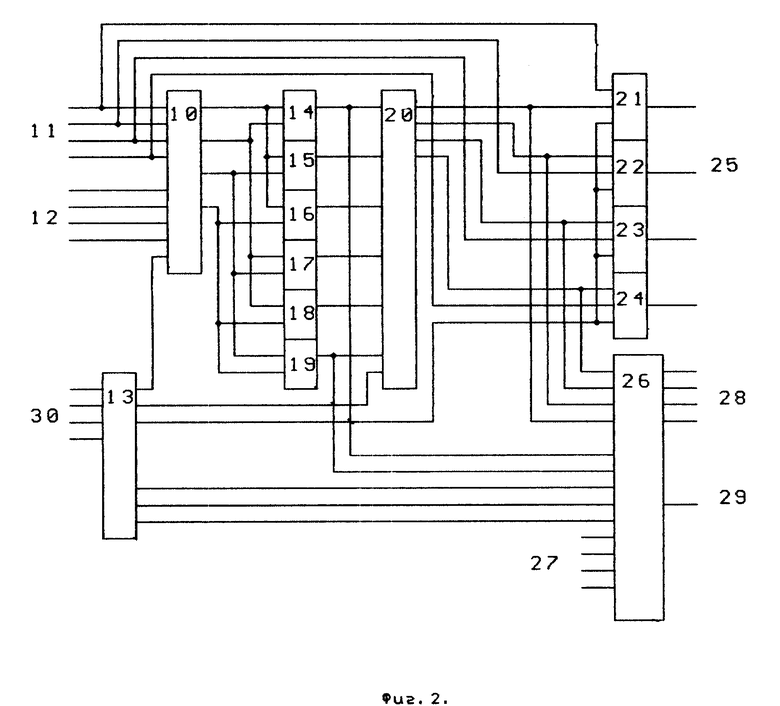

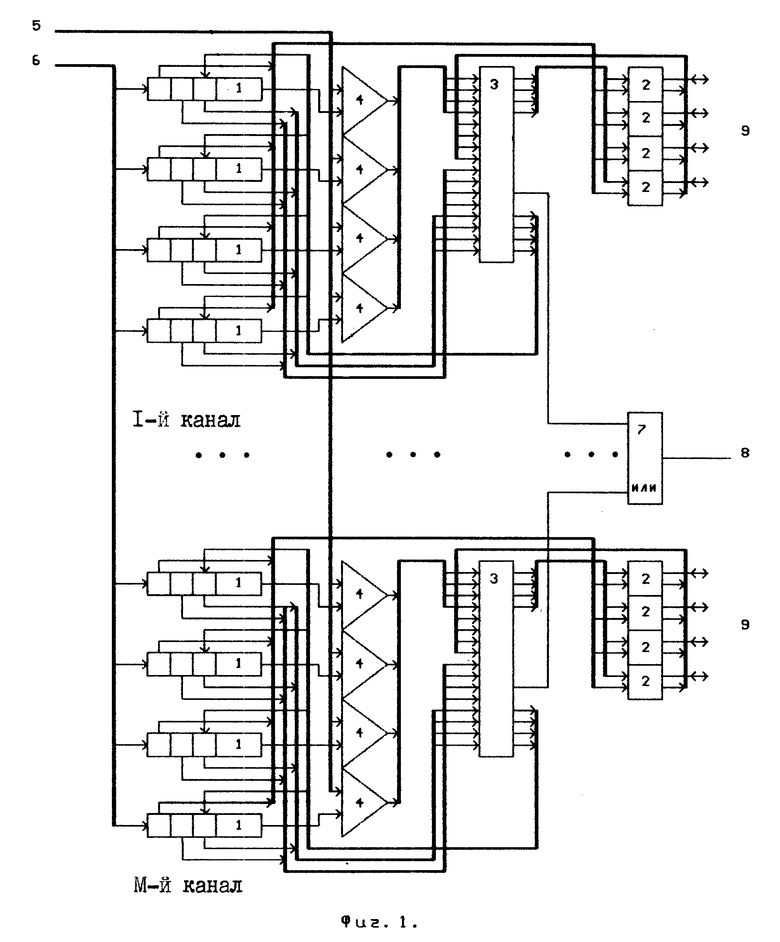

На фиг. 1 приведена структурная схема матричного коммутатора; на фиг. 2 - схема блока резервирования каналов.

Устройство содержит M коммутационных каналов, каждый из которых включает четыре адресных регистра 1 (фиг. 1), четыре приемо-передатчика 2, блок резервирования информационных каналов 3, четыре мультиплексора 4, информационные входы 5. управляющие входы 6, элемент ИЛИ 7, сигнальный выход 8 и информационные входы-выходы 9.

При этом выходы каждого адресного регистра 1, начиная с четвертого разряда, подключены к адресным входам мультиплексоров 4. выходы первого разряда подключены к управляющим входам приемо-передатчика 2, выходы второго и третьего разрядов - к первой и второй группам управляющих входов блока резервирования 3. Информационные входы мультиплексоров 4 соединены с информационными входами 5 коммутатора. Управляющие входы 6 коммутатора соединены с информационными входами регистров 1. Выходы мультиплексоров 4 соединены с первой группой информационных входов блока резервирования 3, вторая группа входов которого соединена с выходами приемо-передатчиков 2. Информационные выходы блока 3 соединены с информационными входами приемо-передатчиков 2, управляющие выходы блока 3 подключены к информационным входам третьего разряда регистров 1, а выход сигнала отказа - к соответствующему входу элемента ИЛИ 7, выход которого соединен с сигнальным выходом 8 коммутатора. Входы-выходы приемо-передатчиков 2 соединены с информационными входами-выходами 9 коммутатора.

Блок резервирования каналов (фиг.2) содержит селектор 10, первую 11 и вторую 12 группу информационных входов, дешифратор режима 13, шесть схем сравнения 14, 15, 16, 17, 18, 19, дешифратор ошибок 20, четыре управляемых инвертора 21, 22, 23, 24, информационные выходы 25, дешифратор отказа 26, первую группу управляющих входов 27, группу управляющих выходов 28, управляющий выход отказа 29 и вторую группу управляющих входов 30.

При этом входы селектора 10 соединены с первой и второй группам и входов 11, 12 и первым выходом дешифратора 13. Входы схем сравнения 14-19 попарно соединены с выходами селектора 10. Входы дешифратора 20 соединены с выходами схем сравнения 14-19 и вторым выходом дешифратора 13. Информационные входы инверторов 21-24 соединены с информационными входами 11 и выходами дешифратора 20, управляющие входы - с третьим выходом дешифратора 13, а выходы инвертора - с информационными выходами 25. С первого по шестой входы дешифратора 26 соединены с выходами схем сравнения 14, 19 и с выходами дешифратора 20. Первая группа входов дешифратора 26 соединена с группой выходов дешифратора 13. а вторая группа входов - с первой группой управляющих входов 27. Группа выходов дешифратора 20 соединена с управляющими выходами 28, а выход отказа - с выходом сигнала отказа 29. Группа входов дешифратора 13 соединена со второй группой управляющих входов 30.

Устройство работает следующим образом.

Предварительно в адресные регистры 1 через управляющие входы 6 записываются данные. Содержимое разрядов регистра 1, начиная с четвертого разряда, определяет внутреннюю коммутацию соответствующего мультиплексора. Значение первого управляющего разряда регистра 1 определяет направление движения информации в приемо-передатчике. Если приемо-передатчик находится в режиме выхода, то информация с мультиплексоров через блок резервирования и приемо-передатчик поступает на вход-выход 9 коммутатора.

Если приемо-передатчик находится в режиме входа, то информация через вход-выход 9 коммутатора поступает на вход блока резервирования 3.

По значению второго разряда регистров 1 в блоке резервирования дешифрируется один из режимов работы коммутатора:

без резервирования;

дублирование в верхней паре мультиплексоров;

дублирование в нижней паре мультиплексоров;

дублирование в верхней и нижней паре;

квадрирование без исправления ошибок;

квадрирование с исправлением ошибок;

троирование без исправления ошибок;

троирование с исправлением ошибок.

В третьем разряде регистра 1 записывается ошибка соответствующего канала.

После записи данных в адресные регистры информация с информационных входов 5 через мультиплексоры 4, блок резервирования каналов 3 и приемо-передатчики 2 поступает на информационные выходы 9 коммутатора.

В случае работы с резервированием в блоке резервирования осуществляется поразрядное сравнение информации в каналах в соответствии с заданным режимом регистрируется ошибка, а если необходимо, то происходит ее исправление. Ошибка фиксируется в третьем разряде регистра 1 и выдается через элемент ИЛИ 7 на сигнальный выход 8 коммутатора.

В режиме резервирования без исправления информация в блок резервирования каналов 3 поступает с выхода приемо-передатчика 2. А в режиме резервирования с исправлением информация в блок резервирования 3 поступает с выхода мультиплексора 4. Эта коммутация осуществляется селектором 10 по управляющему сигналу с дешифратора 13. На схемах сравнения 14-19 выполняется попарное сравнение информации первого и второго, первого и третьего, первого и четвертого, второго и третьего, второго и четвертого, третьего и четвертого информационных каналов и вырабатывается соответствующий сигнал неравнозначности F12, F13, F14, F23, F24, F34.

В дешифраторе ошибок 20 определяется: в каком из каналов ошибка:

F1 = F12•F13•(F14 + T);

F2 = F12•F23•(F24 + T);

F3 = F13•F23•(F34 + T);

F4 = F14•F24•F34•T,

где

T - признак режима троирования, вырабатывается схемой дешифратора 13.

В случае возникновения в одном из каналов одиночной ошибки и для случая задания режима резервирования с исправлением управляемые инверторы 21-24 соответствующего канала осуществляют инверсию ошибочного разряда перед выдачей его на выходные шины 25.В дешифраторе отказа 26 в соответствии с заданным режимом резервирования происходит диагностика и выдача сигнала отказа соответствующего канала для записи в соответствующий адресный регистр 1.

В режиме дублирования при обнаружении несовпадения информации ошибка фиксируется в адресных регистрах 1 обоих каналов.

При режимах троирования и квадрирования одиночная ошибка фиксируется в соответствующем канале, если не задан признак исправления одиночных ошибок. Двойная ошибка Fдв при квадрировании фиксируется во всех четырех каналах одновременно. После первого фиксирования ошибки последующие ошибки игнорируются, а на выходе 8 матричного коммутатора появляется признак отказа F. Приведенный алгоритм фиксирования ошибок реализуется в дешифраторе 26 и описывается следующими выражениями: где

Д1, Д2 - признак дублирования в верхней и нижней паре мультиплексоров;

Fдв= F12•F34 + F13•F24 + F23•F14;

KV - признак режима квадрирования;

IS - признак режима резервирования с исправлением ошибок;

Qi - признак ошибки, фиксируется в третьем разряде i-го адресного регистра.

Конструктивно для построения селектора используются четыре элемента И-ИЛИ с двумя группами по два входа. Дешифраторы отказа и ошибок строятся на элементах И и ИЛИ по описанным выше алгоритмам. Для дешифратора режима можно использовать схему стандартного дешифратора на 4 входа, соответствующим образом закодировав режимы резервирования во втором управляющем разряде адресных регистров.

Алгоритм функционирования 1-го управляемого инвертора имеет вид:

Yi=(Xi≠(Fi•IS)),

где

Xi - первый информационный вход i-го инвертора.

Предлагаемый матричный коммутатор по сравнению с известным позволяет расширить функциональные возможности за счет введения режимов резервирования каналов, а также повысит надежность коммутации информации за счет осуществления контроля, диагностики и исправления одиночных ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| МАКРОПРОЦЕССОР | 2001 |

|

RU2210808C2 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| МУЛЬТИКОНТРОЛЛЕР РАСПРЕДЕЛЕННОЙ ПАМЯТИ | 2001 |

|

RU2210804C2 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ НЕЙРОНА | 1991 |

|

RU2029368C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 1993 |

|

RU2069009C1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2020559C1 |

| Устройство для моделирования нейрона | 1989 |

|

SU1709356A1 |

Относится к области вычислительной техники и предназначен для построения коммутационных сетей вычислительных систем.

Технический результат, достигаемый при использовании изобретения, заключается во введении режимов резервирования каналов, регистрации ошибок в каналах, исправлении одиночных ошибок при мажорировании.

Для достижения технического результата в матричный коммутатор, содержащий M коммутационных каналов, каждый из которых включает четыре адресных регистра, выходы каждого из которых, начиная с четвертого разряда, подключены к адресным входам соответствующих мультиплексоров, введен элемент ИЛИ, а в каждый коммутационный канал введены блок резервирования информационных каналов и четыре приемо-передатчика, информационные входы-выходы которых являются соответствующими информационными входами-выходами коммутатора, а управляющие входы приемо-передатчиков подключены к выходам первого разряда соответствующих адресных регистров, каждый из которых соединен выходом второго разряда с соответствующим входом первой группы управляющих входов блока резервирования информационных каналов, а выходом третьего разряда - с соответствующим входом второй группы управляющих входов блока резервирования информационных каналов, подключенного управляющими выходами к информационным входам третьего разряда соответствующих адресных регистров, информационными входами первой группы - к выходам соответствующих мультиплексоров, информационными входами второй группы - к выходам соответствующих приемо-передатчиков, информационными выходами - к информационным входам соответствующих приемо-передатчиков, а выходом сигнала отказа - к соответствующему входу элемента ИЛИ, выход которого является сигнальным выходом коммутатора, информационные входы адресных регистров являются управляющим входом коммутатора, информационные входы мультиплексоров являются информационным входом коммутатора. 1 з.п.ф-лы, 2 ил.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| СПОСОБ ПОЛУЧЕНИЯ ХЛОРИСТОГО БАРИЯ ИЗ ТЯЖЕЛОГО ШПАТА | 1923 |

|

SU480A1 |

Авторы

Даты

1998-01-27—Публикация

1994-08-05—Подача