Изобретение относится к вычислительной технике и может быть использовано для построения устройств передачи и обработки информации.

Известны устройства для кодирования и декодирования информации [1-3], недостатком которых являются ограниченные функциональные возможности.

Наиболее близким к изобретению является устройство для кодирования и декодирования информации, содержащее первый счетчик импульсов, установочные входы которого являются первой группой информационных входов устройства, второй счетчик импульсов, блок элементов И, третий счетчик импульсов, выходы которого подключены к адресным входам блока кодирования [4].

Недостатками этого устройства являются невозможность обработки информации с изменяющимися за счет помех характеристиками и невысокая надежность.

Для преодоления этих недостатков в устройство для кодирования и декодирования информации, содержащее первый счетчик импульсов, установочные входы которого являются первой группой информационных входов устройства, второй счетчик импульсов, блок элементов И, третий счетчик импульсов, выходы которого подключены к адресным входам блока кодирования, введены четвертый-шестой счетчики, блок элементов памяти и элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, при этом счетный вход первого счетчика импульсов является тактовым входом устройства, входы обнуления первого и четвертого счетчиков импульсов объединены и являются входом обнуления устройства, выход первого счетчика импульсов соединен со счетными входами второго, четвертого, пятого и шестого счетчиков импульсов, первым входом блока элементов памяти и является тактовым выходом устройства, первый выход блока элементов И подключен к входам разрешения счета четвертого и пятого счетчиков импульсов и к входу обнуления второго счетчика импульсов, выход k-го разряда которого (К < n, n + K + 1 - длительность элемента кода, измеренная в тактовых интервалах), соединен с первым входом блока элементов И, а выход n-го разряда подключен к вторым входам блока элементов памяти и блока элементов И, второй вход которого соединен с входом разрешения счета второго счетчика импульсов и с третьим входом блока элементов памяти, первый выход которого подключен к третьему входу блока элементов И, третий и четвертый выходы которого соединены соответственно с четвертым входом блока элементов памяти и входом разрешения счета первого счетчика импульсов, выходы четвертого и пятого счетчиков импульсов подключены соответственно к четвертому и пятому входам блока элементов И, информационные входы блока кодирования являются второй группой информационных входов устройства, первый выход блока кодирования соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с шестым входом бока элементов И и является информационным выходом устройства, седьмой вход блока элементов И является управляющим входом устройства, второй выход блока кодирования подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с пятым входом блока элементов памяти, второй выход которого подключен к входам обнуления четвертого и пятого счетчиков импульсов, к счетному входу третьего счетчика импульсов и к восьмому входу блока элементов И, третий выход блока элементов памяти соединен с входом обнуления третьего счетчика импульсов и девятым входом блока элементов И, четвертый и пятый выходы блока элементов памяти подключены соответственно к десятому и одиннадцатому входам блока элементов И, выход шестого счетчика импульсов соединен с входом разрешения счета шестого счетчика импульсов, с двенадцатым входом блока элементов И и является управляющим выходом устройства, шестой выход блока элементов памяти является выходом индикации конца кодового элемента, выходы третьего счетчика импульсов являются контрольными выходами устройства.

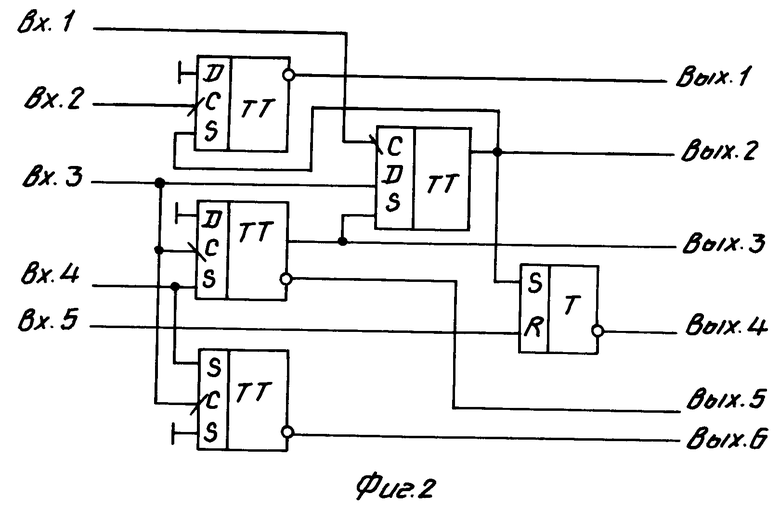

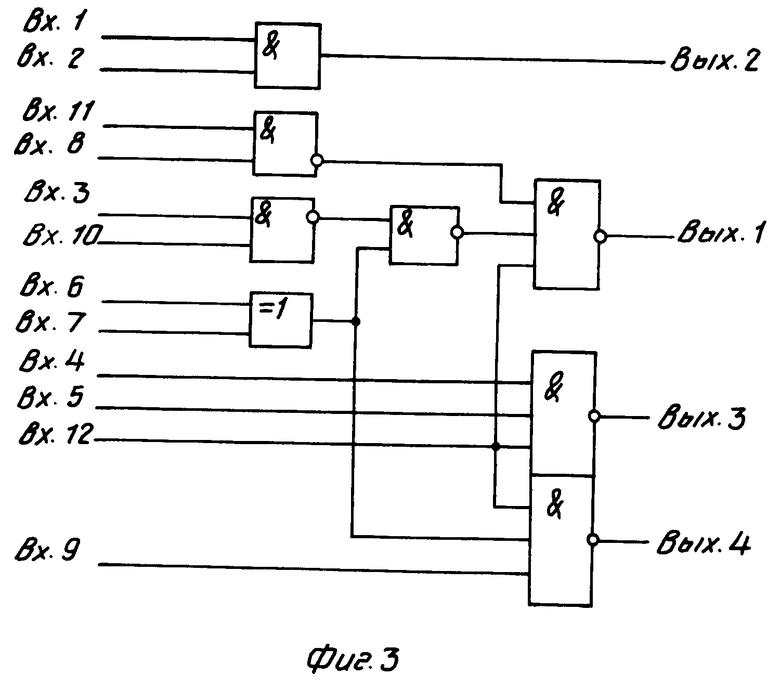

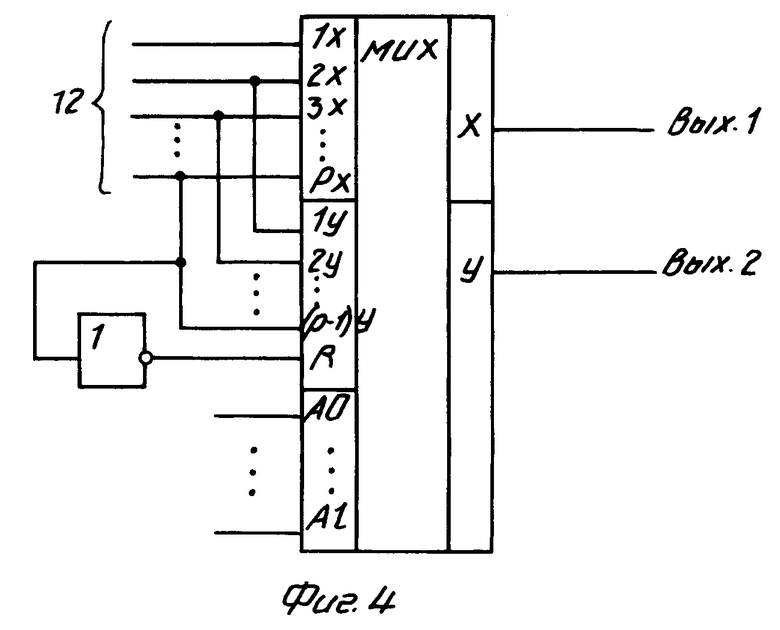

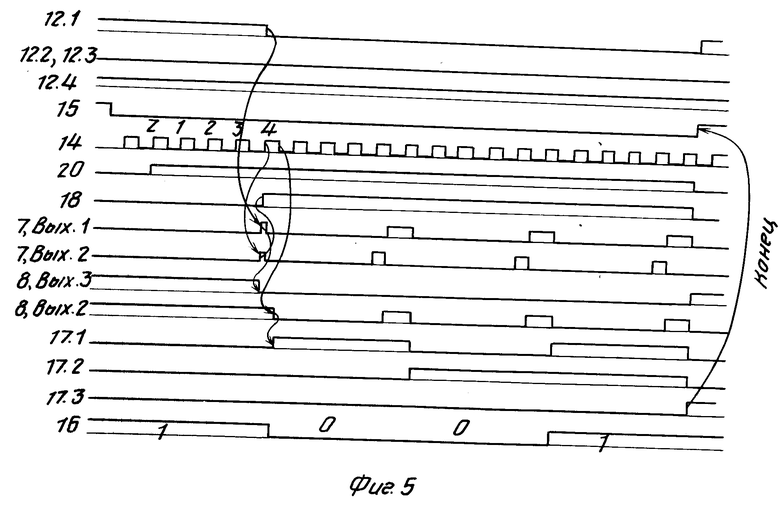

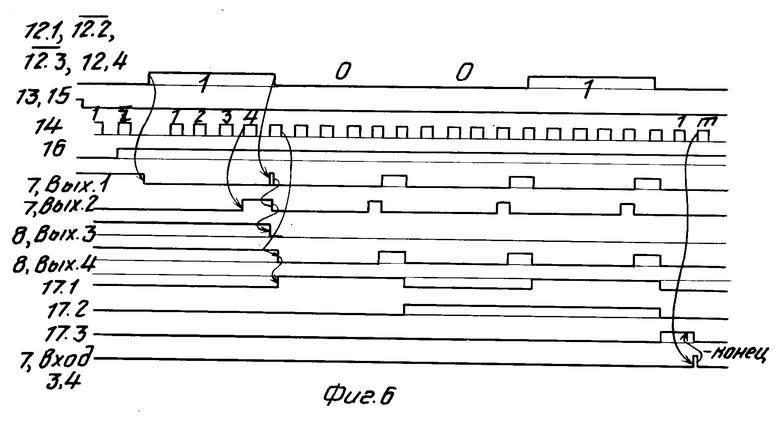

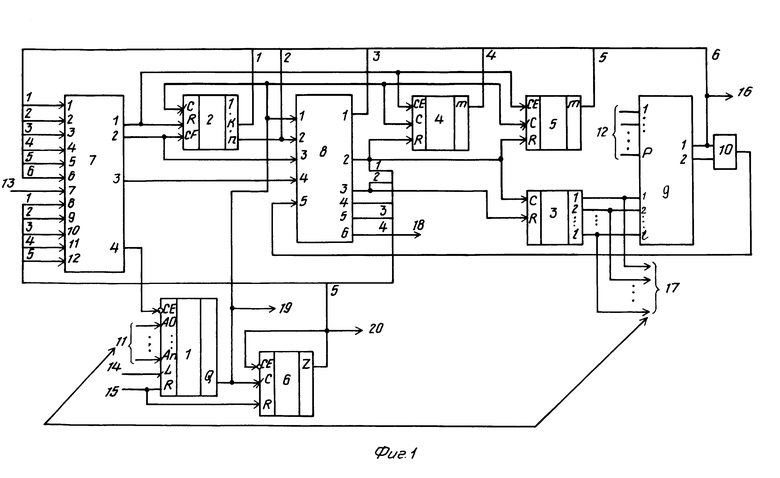

На фиг. 1 приведена функциональная схема устройства; на фиг. 2, 3 и 4 представлены функциональные схемы соответственно блока элементов памяти, блока элементов И и блока кодирования; на фиг. 5 и 6 - временные диаграммы для режимов соответственно кодирования и декодирования сигнала из четырех элементов кода 1001.

Устройство содержит первый-шестой счетчики 1-6 импульсов, блок 7 элементов И, блок 8 элементов памяти, блок 9 кодирования и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и имеет первую и вторую группы 11 и 12 информационных входов, управляющий вход 13, тактовый вход 14, вход 15 обнуления, информационный выход 16, контрольные выходы 17, выход 18 индикации конца кодового элемента, тактовый выход 19 и управляющий выход 20.

Устройство функционирует следующим образом.

В режиме кодирования выход 16 соединяют внешними элементами с входом 13 так, чтобы в конце первого элемента кода на входе 13 появится короткий импульс противоположной полярности относительно сигнала на выходе 16, используя для этого сигнал, появляющийся на выходе 18. Кодируемая информация в виде двоичных или частотных элементов кода подается на входы 12 в параллельном коде на время кодирования, а внешние тактовые импульсы - на вход 14.

Началом кодирования является снятие потенциала обнуления с входа 15, под действием которого устройство удерживалось в исходном состоянии. Счетчик 1 начинает формировать тактовые импульсы, под действием которых счетчик 6 в режиме однократного счета формирует паузу перед началом кодирования, необходимую для подготовки передатчика к режиму передачи. После паузы блок 7 элементов И снимает обнуляющий потенциал со счетчика 2. Счетчик 2 подсчитывает тактовые импульсы до состояния n+K, после чего через внешние элементы между выходом 16 и входом 13 счетчик 2 обнуляется, что позволяет блоку 8 по третьему выходу снять обнуляющий потенциал со счетчика 3, а затем по второму выходу снять такой же потенциал со счетчиков 4 и 5. При этом счетчик 3 увеличивает свое состояние на единицу, а блок 9 кодирования подключает второй вход группы 12 к выходу 16. При наличии физической или функциональной связи между выходами 17 и входами 11 счетчика 1 изменяется период его тактовых импульсов.

По окончании импульса обнуления счетчика 2 он вновь досчитывает тактовые импульсы до состояния n+K (счетчикам 4, 5 по входам СЕ счет запрещен) и через блоки 7 и 8 обнуляется, а счетчик 3 увеличивает свое состояние еще на единицу, подключая тем самым в блоке 9 третий вход группы 12 к выходу 16. Далее процесс переключения следующих входов группы 12 к выходу 16 повторяется аналогично описанному для второго входа. Таким образом, в блоке 9 кодирования информация из параллельного кода преобразуется в последовательный, приобретая временные признак, и считывается с выхода 16. Окончание кодирования формируется внешними элементами по достижении заданного состояния счетчиком 3.

В режиме декодирования поступающая информация подается на группу 12 входов в последовательном коде в виде двоичных элементов кода. Порядок подключения входов в группе 12 соответствует порядку декодирования элементов кода: первый вход группы 12 - первому элементу кода, второй вход группы 12 - второму элементу кода и т.д. С помощью внешнего элемента НЕ подаваемая информация разделяется: входы группы 12, предназначенные для кодирования единичных элементов кода, подключаются к входу внешнего элемента НЕ, а предназначенные для декодирования нулевых элементов кода, - к выходу этого элемента НЕ. Вход 13 может использоваться при необходимости для инвертирования информации.

С момента включения питания декодирующее устройство фиксируется в исходном состоянии подачей внешнего кратковременного импульса на вход 15. Формируемая счетчиком 6 пауза используется для исключения декодирования на время подготовительных операций для приема информации. После этой паузы с помощью блока 7 прекращается формирование тактовых импульсов счетчиком 1.

С приходом первого элемента кода сигнал с первого входа группы 12 через первый канал блока 9 поступает на шестой вход блока 7, который по своему первому выходу снимает обнуляющий сигнал с R-входа счетчика 2, в по четвертому выходу снимает запрещающий сигнал со счетчика 1. Последний начинает формировать тактовые импульсы, которые подсчитываются в счетчике 2 до числа n+K. При досчете до этого состояния блок 7 по сигналам на своих первом и втором входах останавливает счетчик 1 по входу СЕ и удерживает его в этом состоянии до конца первого элемента кода. По окончании первого элемента кода счетчик 2 обнуляется, блок 8 по своему третьему входу запоминает это состояние, снимает на своем третьем выходе обнуление со счетчика 3 и блокирует передачу запрещающего счет сигнала на счетчик 1 через девятый вход блока 7. Следующим тактом по первому входу блока 7 с его второго выхода снимается обнуление со счетчиков 4 и 5, а счетчик 3 увеличивает свое состояние на единицу, открывая тем самым второй канал в блоке 9. На выходах 17 при этом появляется информация о декодировании первого элемента кода. При необходимости между выходами 17 и входами 11 организуется внешняя связь, как в кодирующем устройстве на передающей стороне.

При декодировании второго элемента кода счетчик 2 считает тактовые импульсы до состояния n. Если помехой является часть декодируемого элемента, то счетчик 2 обнуляется, а счетчик 4 и 5 начинает счет. Если декодируемый элемент продолжает отсутствовать, то счетчики 4 и 5, досчитав до своего конечного состояния, через четвертый и пятый входы блока 7 и далее через четвертый вход блока 8 обнуляют блок 8, который, в свою очередь, обнуляет счетчик 3-5 и тем самым снова включает первый канал блока 9. Устройство возвращается в режим ожидания первого элемента кода.

Если второй элемент кода отсутствует кратковременно, то с его появлением счетчики 4 и 5 останавливаются, а счетчик 2 вновь считает тактовые импульсы от 0 до n. При досчете до n на первом выходе блока 8 появляется сигнал, воздействующий на третий вход блока 7. Дальнейшая работа счетчика 2 зависит от состояния элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10.

Если третий элемент кода совпадает по уровню с вторым элементом кода, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 остается нулевой сигнал и на десятом входе блока 7 (с четвертого выхода блока 8) сохраняется нулевой уровень. При этом состояние первого выхода блока 7 зависит только от наличия сигнала на втором входе группы 12. Если этот сигнал пропадает, то счетчик 2 достигает до n+К и блок 7 выдает по второму выходу сигнал на обнуление счетчиков 4 и 5 и увеличение на единицу состояния счетчика 3. Это вызывает открывание третьего канала блока 9 кодирования.

Если третий элемент кода не совпадает по уровню с вторым элементом кода, то сигнал на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ вызывает появление сигнала на четвертом выходе блока 8. В этом случае состояние первого выхода блока 7 не зависит от сигнала на входах 12 и счетчик 2 досчитывает до n+К, открывая третий канал блока 9, аналогично вышеописанному.

Таким образом, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 вместе с блоком 9 позволяет декодировать изменяющиеся элементы кода с учетом переходных процессов при их выделении, а повторяющиеся как непрерывные (без переходных процессов).

Декодирование последующих элементов кода аналогично декодированию его второго элемента. Декодирование заканчивается по достижении заданного состояния счетчиком 3.

Таким образом, повышается надежность работы устройства и снижается трудоемкость его изготовления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| СИСТЕМА ПОИСКА ИДЕНТИЧНЫХ ВЫБОРОК СИГНАЛОВ | 1992 |

|

RU2037191C1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО ДЛЯ СИНТЕЗА РЕЧЕВЫХ СИГНАЛОВ | 1991 |

|

RU2020608C1 |

| Устройство для регистрации подвижных объектов | 1987 |

|

SU1492356A1 |

| ОТКАЗОУСТОЙЧИВАЯ БОРТОВАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА, УСТРОЙСТВО "СЛУЖБА СТОРОЖЕВОГО ТАЙМЕРА, СПОСОБ РАБОТЫ ОТКАЗОУСТОЙЧИВОЙ БОРТОВОЙ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ" | 1998 |

|

RU2131619C1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

| Устройство для преобразования графической информации | 1982 |

|

SU1140148A1 |

| УСТРОЙСТВО ДЛЯ МНОГОКАНАЛЬНОГО ДЕКОДИРОВАНИЯ | 1990 |

|

RU2022469C1 |

| ДЕКОДЕР С ИСПРАВЛЕНИЕМ ОШИБОК | 1993 |

|

RU2054224C1 |

Изобретение относится к вычислительной технике. Его использование для построения устройств передачи и обработки информации позволяет повысить надежность работы устройства. Устройство содержит счетчики 1 - 3 импульсов, блок 7 элементов И и блок 9 кодирования. Благодаря введению счетчиков 4 - 6, блока 8 элементов памяти и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 10 в устройстве обеспечивается надежное функционирование при кодировании и декодировании элементов кода с изменяющимися за счет помех характеристиками. 6 ил.

УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ, содержащее первый счетчик импульсов, установочные входы которого являются первой группой информационных входов устройства, второй счетчик импульсов, блок элементов И, третий счетчик импульсов, выходы которого подключены к адресным входам блока кодирования, отличающееся тем, что в него введены четвертый - шестой счетчики импульсов, блок элементов памяти и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, счетный вход первого счетчика импульсов является тактовым входом устройства, входы обнуления первого и четвертого счетчиков импульсов объединены и являются входом обнуления устройства, выход первого счетчика импульсов соединен со счетными входами второго, четвертого, пятого и шестого счетчиков импульсов, первым входом блока элементов памяти и является тактовым выходом устройства, первый выход блока элементов И подключен к входам разрешения счета четвертого и пятого счетчиков импульсов и к входу обнуления второго счетчика импульсов, выход K-го разряда которого (K < n, n + K + 1 - длительность элемента кода, измеренная в тактовых интервалах) соединен с первым входом блока элементов И, а выход n-го разряда подключен к вторым входам блока элементов памяти и блока элементов И, второй выход которого соединен с входом разрешения счета второго счетчика импульсов и с третьим входом блока элементов памяти, первый выход которого подключен к третьему входу блока элементов И, третий и четвертый выходы которого соединены соответственно с четвертым входом блока элементов памяти и входом разрешения счета первого счетчика импульсов, выходы четвертого и пятого счетчиков импульсов подключены соответственно к четвертому и пятому входам блока элементов И, информационные входы блока кодирования являются второй группой информационных входов устройства, первый выход блока кодирования соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с шестым входом блока элементов И и является информационным выходом устройства, седьмой вход блока элементов И является управляющим входом устройства, второй выход блока кодирования подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с пятым входом блока элементов памяти, второй выход которого подключен к входам обнуления четвертого и пятого счетчиков импульсов, к счетному входу третьего счетчика импульсов и к восьмому входу блока элементов И, третий выход блока элементов памяти соединен с входом обнуления третьего счетчика импульсов и девятым входом блока элементов И, четвертый и пятый выходы блока элементов памяти подключены соответственно к десятому и одиннадцатому входам блока элементов И, выход шестого счетчика импульсов соединен с входом разрешения счета шестого счетчика импульсов, с двенадцатым входом блока элементов И и является управляющим выходом устройства, шестой выход блока элементов памяти является выходом индикации конца кодового элемента, выходы третьего счетчика импульсов являются контрольными выходами устройства.

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для кодирования и декодирования кода постоянного веса (его варианты) | 1983 |

|

SU1144193A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

Авторы

Даты

1995-02-20—Публикация

1990-07-03—Подача