Изобретение относится к цифровой электросвязи и предназначено для синхронизации принимаемого потока информации, тактируемого частотой сопровождения, с частотой тактового генератора в приемнике потока.

Существуют системы цифровой передачи данных, в которых необходимо обеспечивать обмен информацией, при этом передача производится последовательным способом на фиксированной частоте передатчика. При передаче информации по реальным физическим линиям происходят фазовые и временные искажения тактовой частоты, в результате чего на входе приемника данной информации последняя отличается на неопределенную величину от исходной. Если принятую информацию необходимо передавать далее в составе группового сигнала, тактируемого собственной опорной частотой, то за счет отличия принятой и опорной частот неизбежно возникают искажения в результатах обработки, причем величина этих искажений тем больше, чем сильнее принятая сопровождающая частота отличается от опорной по фазе и значению.

Известны способы совмещения указанных частот, использующие промежуточное запоминающее устройство (ЗУ), информация в которое записывается со скоростью, определяемой частотой сопровождения принимаемого сигнала, а чтение записываемой информации производится со скоростью, определяемой частотой опорного генератора приемника. Принципиально невозможно сделать объем ЗУ бесконечно большим, поэтому в реальных устройствах применяется циклический метод записи информации, при котором запись производится в ячейки памяти ЗУ, начиная с самой младшей и заканчивая старшей, после чего цикл записи повторяется. Таким образом, информация, записанная в первом цикле записи, неизбежно заменяется на новую во втором цикле, в свою очередь информация второго цикла заменяется информацией третьего цикла и т. д. Для вывода поступающей и записываемой в ячейки памяти ЗУ информации необходимо обеспечить процесс чтения таким образом, чтобы каждая ячейка ЗУ, записанная в первом цикле записи, была прочитана до второго цикла записи. Если частоты записи и чтения равны между собой, то данное требование выполняется автоматически, т. е. процессы записи и чтения синхронны. В случае различных величин этих частот, что имеет место при поступлении частоты записи из физического канала связи, возможны случаи, когда частота записи больше, меньше или равна частоте чтения и, кроме того, может отличаться фазой состояния.

Метод с использованием промежуточного ЗУ в качестве блока асинхронного сопряжения применен в аппаратуре ИКМ-120. Собственно ЗУ данной аппаратуры представляет собой набор триггеров (ячеек памяти), запись и чтение которых осуществляются под управлением сигналов, вырабатываемых распределителем записи и распределителем считывания, изменяющих номер триггера со скоростями поступления частот записи и считывания, а результат чтения через систему схем совпадения, объединенных через схему ИЛИ, фиксируется (стробируется) отдельным триггером, на выходе которого формируется считанная импульсная последовательность. Число ячеек памяти выбирается таким, чтобы момент считывания никогда не совпадал с моментом записи. Минимальное число ячеек памяти зависит от длительности цикла приема-передачи, который определяется передачей в потоке специальных синхронизирующих символов. Стандартный цикл ИКМ-канала содержит 256 тактов сопровождающей частоты, поэтому в общем случае число ячеек памяти должно быть кратным данной величине. Использование триггеров в качестве ячеек памяти в данном случае невыгодно из-за сложностей конструктивного, экономического и энергетического порядков.

Известно также устройство асинхронного сопряжения, работающее по рассмотренному принципу с использованием промежуточного ЗУ, состоящего из двух блоков памяти и дополнительного блока промежуточной памяти, в который предварительно записывается код адреса сравнения счетчика адреса записи и счетчика адреса считывания, что обеспечивает переключение блоков памяти при совпадении адресов записи и чтения, тем самым исключая одновременное обращение по записи и чтению к одной ячейке памяти.

Недостатками известного устройства являются его сложность и ограничение продолжительности сеанса связи.

Цель изобретения - упрощение устройства и устранение ограничений по продолжительности сеанса связи.

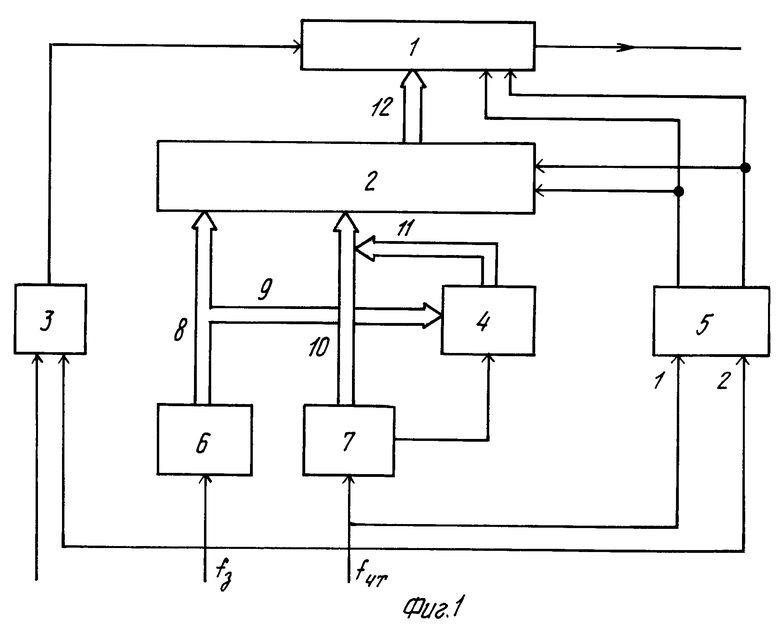

На фиг. 1 представлена структурная электрическая схема устройства приема и передачи асинхронной информации; на фиг. 2 и 3 - временные диаграммы, поясняющие его работу.

Устройство приема и передачи асинхронной информации содержит блок 1 памяти, коммутатор 2, Д-триггер 3, блок 4 коррекции адресов чтения, формирователь 5 сигнала записи "по условию", счетчик 6 адресов записи, счетчик 7 адресов чтения, шину 8 адресов записи, шину 9 старших разрядов адресов записи, шину 10 адресов чтения, шину 11 старших разрядов адресов чтения, общую адресную шину 12.

Устройство приема и передачи асинхронной информации работает следующим образом.

Оно обеспечивает сопряжение двух асинхронных частот, одна из которых, частота записи (F3), может менять величину и фазу, а другая, частота чтения (Fчт), является фиксированной стабильной частотой опорного генератора. Информационный поток, поступающий на вход устройства, тактируется частотой записи и под управлением этой частоты записывается в Д-триггер 3, где сохраняется в течение одного такта частоты записи. Частота записи управляет работой счетчика 6 адресов записи, обеспечивая по шине 8 циклическое изменение адреса с периодом изменения в один такт записи. Старшая часть адресного пространства вводится в блок 4 коррекции адресов чтения, который корректирует состояние адреса чтения под управлением производного сигнала частоты чтения по достижении счетчиком 6 адресов записи значения, совпадающего с текущим значением счетчика 7 адресов чтения.

Для исключения возможности одновременного появления сигналов разрешения чтения и записи на блоке 1 памяти и коммутаторе 2 введен формирователь 5 сигналов записи "по условию", на входы которого поступают сигналы частот записи чтения. Он обеспечивает контроль фазы частоты записи, сравнивая ее с фазой частоты чтения таким образом, чтобы в момент формирования сигнала чтения не появлялся сигнал записи.

Частота чтения (Fчт) поступает в счетчик 7 адресов чтения и обеспечивает циклическое изменение состояния шины 10 адресов чтения. Коммутатор 2 в соответствии с поступающими на его входы адресами записи или чтения управляет через общую адресную шину 12 выбором ячейки памяти блока 1 памяти. На общей адресной шине 12 попеременно появляется адрес чтения и записи в зависимости от поступления на управляющие входы коммутатора 2 сигналов чтения и записи. Этими же сигналами управляется и блок 1 памяти, в результате чего при действии сигнала чтения обеспечивается чтение заданной адресом чтения ячейки памяти и бит данных из этой ячейки появляется на выходе блока 1 памяти, а при действии сигнала записи обеспечивается запись бита данных из Д-триггера 3 в заданную адресом записи ячейку памяти блока 1 памяти через его информационный вход.

Блок 4 коррекции адресов чтения работает следующим образом.

Изменение текущего адреса чтения в пределах заданного числа производится блоком 4 по достижении счечиком 6 адресов чтения значения, равного значению счетчика 7 адресов чтения. Коррекция адреса чтения происходит под воздействием сигнала коррекции (Fчт/n) за счет изменения старших разрядов адреса чтения один раз в цикл при условии, что текущее значение данных разрядов совпадает с текущим значением аналогичных разрядов счетчика 6 адресов записи, т. е. блок 4 изменяет состояние шины 10 адресов чтения таким образом, что коррекция всегда производится на строго фиксированную величину, определяемую числом тактов (n) в цикле.

Рассмотрим диаграмму сигналов, поясняющую принцип действия блока 4 коррекции адресов чтения (фиг. 2). На фиг. 2б приведена диаграмма сигналов разрядов 2t и 2t+1 счетчика 6 адресов записи, на фиг. 2а и 2в - диаграммы сигналов разрядов 2n и 2n+1 шины 10 адресов чтения для случаев, когда частота чтения ниже и выше частоты записи. Из диаграмм видно, что изменение состояния разрядов 2n и 2n+1 производится синхронно с поступлением частоты сравнения (Fср = Fчт/n) сигнала коррекции один раз в цикл, причем это изменение происходит по закону деления на два и только в указанные на диаграммах моменты времени I, т. е. в моменты поразрядного совпадения сигналов 2n и 2t, 2n+1 и 2t+1 изменяется очередной адрес чтения, чем обеспечивается несовпадение ячеек блока 1 памяти при записи и чтении.

Формирователь 5 сигналов записи "по условию" работает следующим образом.

Как уже указывалось, он вырабатывает сигналы чтения и записи, которые являются управляющими для блока 1 памяти и коммутатора 2, исключая возможность их одновременного появления. Возможность одновременного появления сигналов чтения и записи возникает из-за того, что фазы частот записи и чтения в общем случае отличаются друг от друга и длительность периодов указанных частот разная, а это может привести к такому состоянию, когда возможно совпадение моментов передачи сигналов чтения и записи. Алгоритм работы формирователя 5 заключается в том, что в подобной ситуации обеспечивается появление на соответствующем выходе только сигнала чтения при задержке сигнала записи до полного окончания сигнала чтения. Если в пределах одного цикла чтение-запись сигнал записи по длительности действия успевает сформироваться до момента начала действия сигнала чтения, то формирователь 5 вырабатывает сигнал записи, который появляется на соответствующем выходе, в противном случае вывод сигнала записи задерживается, как это было отмечено выше. Таким образом, исключается возможность одновременного появления сигналов чтения и записи на выходах формирователя 5.

Рассмотрим диаграмму сигналов, поясняющую принцип работы формирователя 5 сигналов записи "по условию" (фиг. 3). На фиг. 3а показана последовательность адресов чтения (Ачт), на фиг. 3б - сигналы частоты чтения (Fчт), а на фиг. 3в - последовательность сигналов чтения на выходе формирователя 5.

Как видно из указанных выше диаграмм, сигнал чтения синхронен с сигналом частоты чтения Fчт и соответственно с сигналом адреса чтения Ачт, т.е. за один такт чтения (один период частоты чтения Тчт) формируется один сигнал чтения.

На фиг. 3д представлена последовательность сигналов с частотой записи F3, которая в общем случае асинхронна по отношению к частоте Fчт и отличается от нее длительностью периода (Тчт ≠ Тзп). На фиг. 3г показана последовательность адресов записи А3, а на фиг. 3е - последовательность сигналов записи на выходе формирователя 5.

Из рассмотренного выше алгоритма работы формирователя 5 и диаграмм, показанных на фиг. 3, видно, что изменение адреса записи, синхронное с частотой записи F3, вызывает появление сигнала записи только в том случае, если в этот момент не формируется сигнал чтения. Кроме того, из диаграмм видно, что сигнал записи может иметь место в пределах периода записи как до формирования сигнала чтения, так и после (позиции I и III соответственно).

Использование: в цифровой электросвязи, для синхронизации принимаемого потока информации, тактируемого частотой сопровождения, с частотой тактового генератора в приемнике потока. Сущность изобретения: устройство содержит блок 1 памяти, коммутатор 2, D - триггер 3, блок 4 коррекции адресов чтения, формирователь 5 сигнала записи "по условию", счетчик 6 адресов записи, счетчик 7 адресов чтения, шину 8 адресов записи, шину 9 старших разрядов адресов записи, шину 10 адресов чтения, шину 11 старших разрядов адресов чтения, общую адресную шину 12. Устройство обеспечивает возможность обращения к блоку памяти в режимах записи и чтения в течение одного такта чтения и применения цикловой коррекции адреса чтения относительно адреса записи. Цель - упрощение устройства и устранение ограничений по продолжительности сеанса связи. 3 ил.

УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ АСИНХРОННОЙ ИНФОРМАЦИИ, содержащее блок памяти, коммутатор, счетчик адресов чтения и счетчик адресов записи, выходы которого через шину адресов записи соединены с входами адресов записи коммутатора, к входам адресов чтения которого через шину адресов чтения подключены выходы счетчика адресов чтения, а выходы коммутатора через общую адресную шину соединены с адресными входами блока памяти, при этом входы счетчиков адресов записи и адресов чтения являются соответственно входами тактовой частоты записи и тактовой частоты чтения устройства, отличающееся тем, что в него введены блок коррекции адресов чтения, формирователь сигналов записи по условию и D-триггер, выход которого подключен к информационному входу блока памяти, к входу разрешения чтения которого и первому управляющему входу коммутатора подключен выход сигнала чтения формирователя сигналов записи по условию, выход сигнала записи которого подключен к входу разрешения записи блока памяти и второму управляющему входу коммутатора, при этом первый выход формирователя сигналов записи по условию является входом тактовой частоты устройства, входом тактовой частоты записи которого является второй вход формирователя сигналов записи по условию, соединенный с управляющим входом D-триггера, причем выходы старших разрядов счетчика адресов записи через шину старших разрядов адресов записи соединены с входами блока коррекции адресов чтения, выходы которого через шину старших разрядов адресов чтения соединены с входами старших разрядов адресов чтения коммутатора, а выход сигнала коррекции счетчика адресов чтения подключен к управляющему входу блока коррекции адресов чтения, при этом информационный вход D-триггера является информационным входом устройства, выходом которого является выход блока памяти.

| Устройство передачи асинхронной информации | 1986 |

|

SU1396287A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1995-02-27—Публикация

1992-06-02—Подача