запрета памяти.

Тактовая

коммутации (фиГоЗв) блоков

частота считывания f

тс

10

15

Изобретение относится к технике связи и может быть использовано в аппаратуре передачи данных на эталонной тактовой частоте при ограниченном времени сеанса связи

Целью изобретения является расширение функциональных возможностей путем обеспечения передачи асинхронной информации на частоте как большей, так и меньшей тактовой частоты при ограниченном времени сеанса связи с,

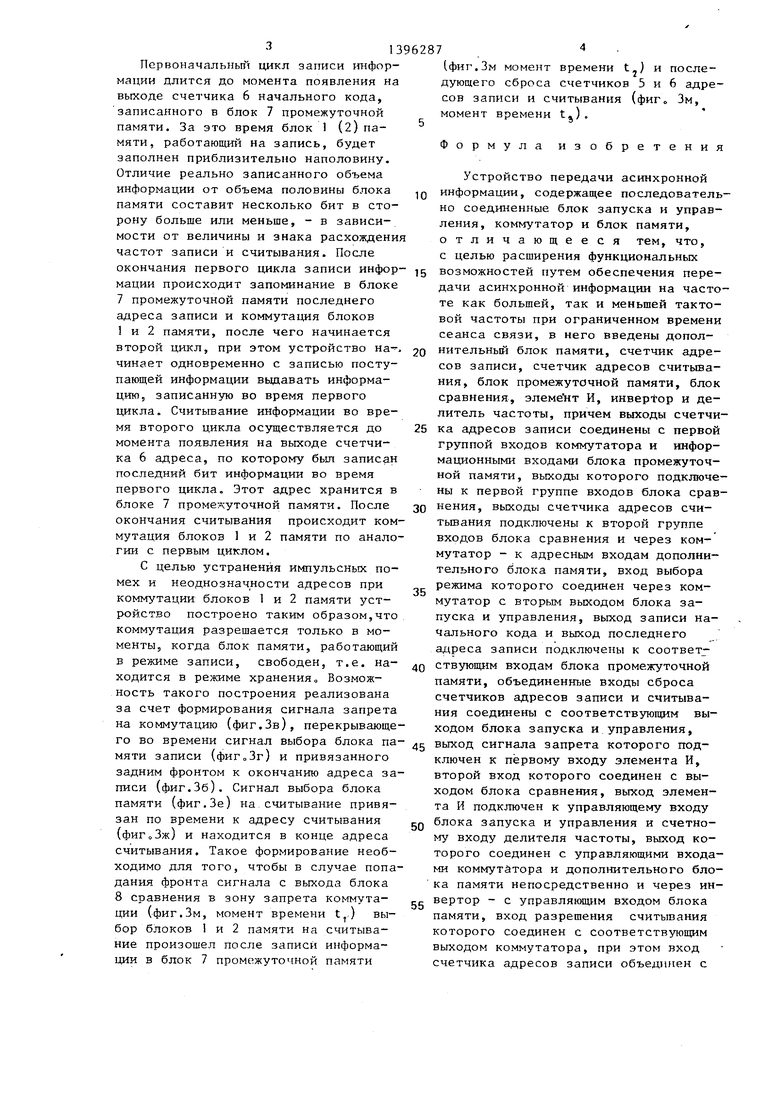

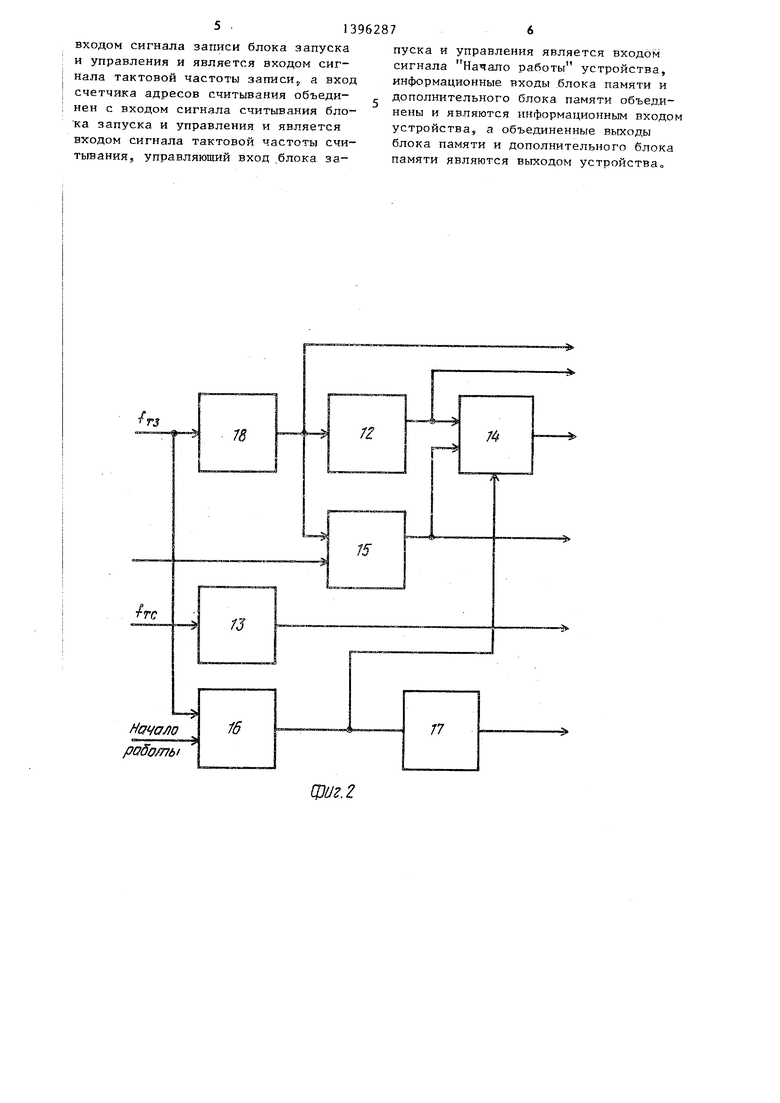

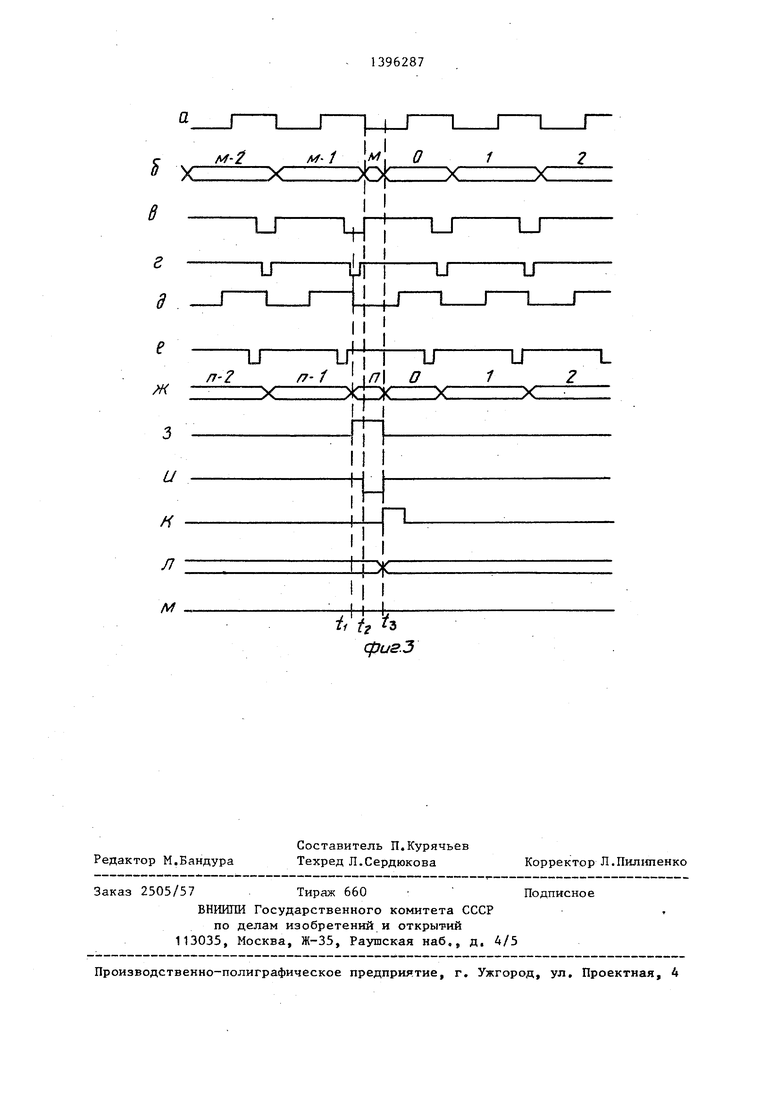

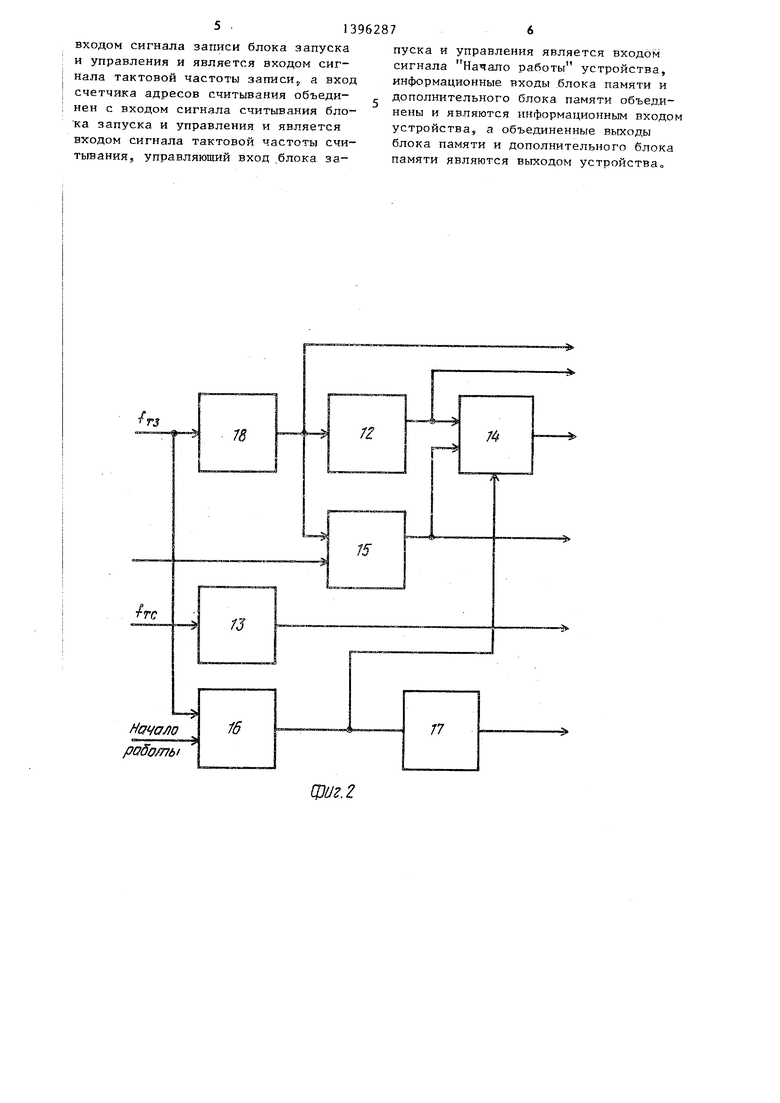

На фиг„1 приведена структурная электрическая схема устройства передачи асинхронной информации;,на фиг„2 - вариант реализации блока запуска и управления; на фиг.З - временные диаграммы, поясняющие работу устройства.

Устройство передачи асинхронной информации содержит блок I памяти, дополнительньй блок 2 памяти, блок 3 запуска и управления, коммутатор 4, счетчик 5 адресов записи, счетчик 6 адресов считывания, блок 7 промежуточной памяти, блок 8 сравнения, делитель 9 частоты, инвертор 10 и элемент И 11, причем в состав блока 3 запуска и управления входят формирователи 12 и 3 сигналов выбора блоков памяти записи и считывания соот- вественно, формирователь 14 сигнала сброса, формирователь 15 сигнала за- блок 7 промежуточной памяти и следую- писи, блок 16 привязки начала работы, 35 сигнал сброса {фиг„3к)

(фиг„3д) информации поступает на вход счетчика 6 и на вход блока 3 запуска и управления, который в ответ на этот сигнал формирует сигнал выбора . блока памяти на считывание (фиг„3е}о Сигналы выбора блоков памяти записи и считывания поступают через коммутатор 4 на выходы выбора блоков памяти, каждый из которых попеременно работает в режиме запи-- си и считывания информации, при этом работа блоков 1 и 2 памяти осуществляется в противофазео Коммутация блоков 1 и 2 памяти происходит при достижении кодом на выходе счетчика 6 адресов считьшания кода числа п (фиГоЗж), хранящегося в блоке 7 промежуточной памяти При этом происходит срабатывание блока 8 сравнения. В случае незанятости блока 1 (2), 25 памяти, работающего на запись информации, сигнал с выхода блока 8 сравнения (фиГоЗз) проходит через элемент И 11 и поступает на вход блока 3 запуска и управления, а также на счетньй вход делителя 9 частоты, В ответ на этот сигнал блок 3 запуска и управления вырабатывает сигнал переписи кода счетчика 5 числа м в

20

30

формирователь 17 сигнала записи начального кода и формирователь 18 сигнала запрета на коммутацию

Устройство передачи асинхронной информации работает следзтощим образом

Перед началом сеанса связи на вход блока 3 запуска и управления поступает сигнал Начало работы, под действием которого формируется сигнал сброса счетчиков 5 и 6 (фиГоЗк) и сигнал записи начального кода( фиг„3и) в блок 7 промежуточной памяти. Значение начального кода устанавливается равным половине объема одного из блоков памяти, при этом построение обоих блоков 1 и 2 памяти идентично

Тактовая частота записи (фиГоЗа) информации поступает на вход счетчика 5 и на вход блока 3 запуска и управления, который выраба- тьшает сигнал разрешения выбора блока памяти на запись (фиг,3г) и сигнал

счетчиков 5 и 6

(2)

40

45

50

55

В случае занятости блока 1 памяти, работающего на запись информации, прохождение сигнала с выхода блока 8 сравнения (фиг.Зз) происходит только после освобождения (перехода в режим хранения информации) блока 1 (2) памяти (фиго 3л)о При этом на втором входе элемента И 1I появляется разрешаюш;ий сигнал и делитель 9 частоты меняет свое состояние Сигнал с выхода делителя 9 частоты поступает на управляющий вход коммутатора 4 и на вход управления режимом работы дополнительного блока 2 памяти, а через инвертор 10 - на вход управления блоком 1 памяти,, Проходит коммутация блоков 1 и 2 памяти таким образом, что блок памяти, работающий на запись, начинает работать на считывание, и наоборот, блок памяти, работавший на считывание, начинает работать на запись информации

запрета памяти.

Тактовая

коммутации (фиГоЗв) блоков

частота считывания f

тс

0

5

блок 7 промежуточной памяти и следую- 5 сигнал сброса {фиг„3к)

(фиг„3д) информации поступает на вход счетчика 6 и на вход блока 3 запуска и управления, который в ответ на этот сигнал формирует сигнал выбора . блока памяти на считывание (фиг„3е}о Сигналы выбора блоков памяти записи и считывания поступают через коммутатор 4 на выходы выбора блоков памяти, каждый из которых попеременно работает в режиме запи-- си и считывания информации, при этом работа блоков 1 и 2 памяти осуществляется в противофазео Коммутация блоков 1 и 2 памяти происходит при достижении кодом на выходе счетчика 6 адресов считьшания кода числа п (фиГоЗж), хранящегося в блоке 7 промежуточной памяти При этом происходит срабатывание блока 8 сравнения. В случае незанятости блока 1 (2), 5 памяти, работающего на запись информации, сигнал с выхода блока 8 сравнения (фиГоЗз) проходит через элемент И 11 и поступает на вход блока 3 запуска и управления, а также на счетньй вход делителя 9 частоты, В ответ на этот сигнал блок 3 запуска и управления вырабатывает сигнал переписи кода счетчика 5 числа м в

0

0

блок 7 промежуто сигна

счетчиков 5 и 6

(2)

0

5

0

5

В случае занятости блока 1 памяти, работающего на запись информации, прохождение сигнала с выхода блока 8 сравнения (фиг.Зз) происходит только после освобождения (перехода в режим хранения информации) блока 1 (2) памяти (фиго 3л)о При этом на втором входе элемента И 1I появляется разрешаюш;ий сигнал и делитель 9 частоты меняет свое состояние Сигнал с выхода делителя 9 частоты поступает на управляющий вход коммутатора 4 и на вход управления режимом работы дополнительного блока 2 памяти, а через инвертор 10 - на вход управления блоком 1 памяти,, Проходит коммутация блоков 1 и 2 памяти таким образом, что блок памяти, работающий на запись, начинает работать на считывание, и наоборот, блок памяти, работавший на считывание, начинает работать на запись информации

Первоначальиьпт цикл записи гшфор- мации длится до момента появления на выходе счетчика 6 начального кода, записанного в блок 7 промежуточной памяти. За это время блок 1 (2) памяти, работающий на запись, будет заполнен приблизительно наполовину. Отличие реально записанного объема информации от объема половины блока памяти составит несколько бит в сторону больше или меньше, - в зависимости от величины и знака расхождени частот записи и считывания. После окончания первого цикла записи инфор нации происходит запоминание в блоке

7промежуточной памяти последнего адреса записи и коммутация блоков

1 и 2 памяти, после чего начинается второй цикл, при этом устройство начинает одновременно с записью поступающей информации выдавать информацию, записанную во время первого цикла. Считывание информации во время второго цикла осуществляется до момента появления на выходе счетчика 6 адреса, по которому был записан последний бит информации во время первого цикла. Этот адрес хранится в блоке 7 промежуточной памяти. После окончания считывания происходит коммутация блоков 1 и 2 памяти по аналогии с первым циклом.

С целью устранения импульсных помех и неоднозначности адресов при коммутации блоков 1 и 2 памяти устройство построено таким образом,что коммутация разрешается только в моменты, когда блок памяти, работающий в режиме записи, свободен, т.е. на- ходится в режиме хранения. Возможность такого построения реализована за счет формирования сигнала запрета на коммутацию (фиг.Зв), перекрывающего во времени сигнал выбора блока па мяти записи (фиГоЗг) и привязанного задним фронтом к окончанию адреса записи (фиг.Зб). Сигнал выбора блока памяти (фиг.Зе) на считывание привязан по времени к адресу считывания (фиГоЗж) и находится в конце адреса считывания. Такое формирование необходимо для того, чтобы в случае попадания фронта сигнала с выхода блока

8сравнения в зону запрета коммута- ции (фиг.3м, момент времени t.) выбор блоков 1 и 2 памяти на считывание произошел после записи информации в блок 7 промежуточной памяти

(фиг.3м момент времени t.) и последующего сброса счетчиков 5 и 6 адресов записи и считывания (фиг. 3м, момент времени tj).

Формула изобретения

Устройство передачи асинхронной информации, содержащее последовательно соединенные блок запуска и управления, коммутатор и блок памяти, отличающееся тем, что, с целью расширения функциональных возможностей путем обеспечения передачи асинхронной информацш на частоте как большей, так и меньшей тактовой частоты при ограниченном времени сеанса связи, в него введены дополнительный блок памяти, счетчик адресов записи, счетчик адресов считывания, блок промежуточной памяти, блок сравнения, элеме нт И, инвертор и делитель частоты, причем выходы счетчика адресов записи соединены с первой группой входов коммутатора и информационными входами блока промежуточной памяти, выходы которого подключены к первой группе входов блока сравнения, выходы счетчика адресов счи- тьшания подключены к второй группе входов блока сравнения и через коммутатор - к адресным входам дополнительного блока памяти, вход выбора режима которого соединен через коммутатор с вторым выходом блока запуска и управления, выход записи начального кода и выход последнего адреса записи подключены к соответствующим входам блока промежуточной памяти, объединенные входы сброса счетчиков адресов записи и считывания соединены с соответствующим выходом блока запуска и управления, выход сигнала запрета которого подключен к первому входу элемента И, второй вход которого соединен с выходом блока сравнения, выход элемента И подключен к управляющему входу блока запуска и управления и счетному входу делителя частоты, выход которого соединен с управляющими входами коммутатора и дополнительного блока памяти непосредственно и через инвертор - с управляющим входом блока памяти, вход разрешения считывания которого соединен с соответствующим выходом коммутатора, при этом вход счетчика адресов записи объединен с

входом сигнала записи блока запуска и управления и является входом сигнала тактовой частоты записи,, а вход счетчика адресов считывания объединен с входом сигнала считывания блока запуска и управления и является входом сигнала тактовой частоты счи- тьгаания, управляющий вход блока запуска и управления является входом сигнала Начало работы устройства, информационные входы блока памяти и дополнительного блока памяти объединены и являются информационным входом устройства, а объединенные вьпсоды блока памяти и дополнительного блока памяти являются выходом устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1984 |

|

SU1265769A1 |

| Устройство для сопряжения электронной вычислительной машины с внешними устройствами | 1983 |

|

SU1267428A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для тестового контроля цифровых блоков | 1986 |

|

SU1386999A1 |

| Устройство для сопряжения управляющего вычислительного комплекса с внешними устройствами | 1985 |

|

SU1262514A1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| Многоканальное устройство для ввода информации | 1984 |

|

SU1265783A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

Изобретение относится к технике связи и позволяет расширить функциональные возможности устр-ва путем обеспечения передачи асинхронной информации на частоте как большей, так и меньшей тактовой частоты при ограниченном времени сеанса связи Устр-во содержит блоки памяти (ВП) 1,2, блок 3 запуска и управления, коммутатор 4, счетчик 5 адресов записи, счетчик б адресов считывания, блок промежуточной памяти (ВПП) 7, блок 8 сравнения, делитель 9 частоты, инвертор 10 и злемент И Перед началом работы в БГШ 7 заносится начальный код, равный половине объема БП ,2о Блок 3 вырабатывает сигнал разрешения выбора БП на запись и сигнал запрета коммутации БП„ БП 1, 2 работают попеременно в противофа- зе в режиме записи и считьгеания ин- формации. Коммутация БП 1,2 происходит при достижении кодом счетчика 6. кода, хранящегося в БШ1 1, При этом срабатывает блок 8 сравнения, Б случае незанятости БП, работающего на запись, код счетчика 5 заносится в БПП 7, а затем счетчики 5,6 обнуляются В случае занятости БП, работающего на запись, происходит коммутация БП 1,2. При этом в БПП 7 запоминается последний адрес записи Коммутация БП разрешается только в те моменты, когда БП, работающий на запись, свободен, т.е. находится в режиме хранения, 3 ил,. I ОО со о ю 00 1ЕгЛ ibu f

po5a/r bi

фиг. 2

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

Авторы

Даты

1988-05-15—Публикация

1986-05-16—Подача