Предлагаемое репрограммируемое постоянное запоминающее устройство (РПЗУ) может быть использовано в качестве носителя программы в ЭВМ или других устройствах, в которых сохранение неизменности программы в течение длительного времени является главным показателем.

Известно РПЗУ, выполненное на элементах памяти с электрическим стиранием информации [1].

Недостатками этого РПЗУ является ограниченное время хранения информации, сложность процессов записи и стирания информации, большое энергопотребление в режиме считывания информации.

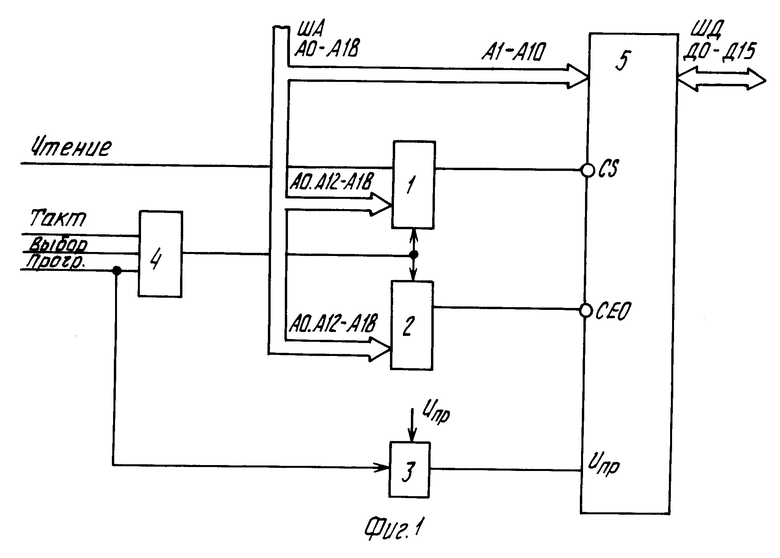

Наиболее близким к предложенному по технической сущности является запоминающее устройство [2], структурная схема которого приведена на фиг. 1.

РПЗУ состоит из дешифратора 1 сигнала выбора кристалла  , дешифратора 2 сигнала разрешения выхода

, дешифратора 2 сигнала разрешения выхода  , ключа 3 напряжения программирования Uпр, формирователя 4 сигнала записи элементов памяти 5 с ультрафиолетовым стиранием, шины адреса (ША), шины данных (ШД). Входные сигналы устройства: "Чтение"; "Такт"; "Выбор"; "Программирование".

, ключа 3 напряжения программирования Uпр, формирователя 4 сигнала записи элементов памяти 5 с ультрафиолетовым стиранием, шины адреса (ША), шины данных (ШД). Входные сигналы устройства: "Чтение"; "Такт"; "Выбор"; "Программирование".

РПЗУ может работать в режимах программирования, хранения и чтения, которые задаются входными сигналами.

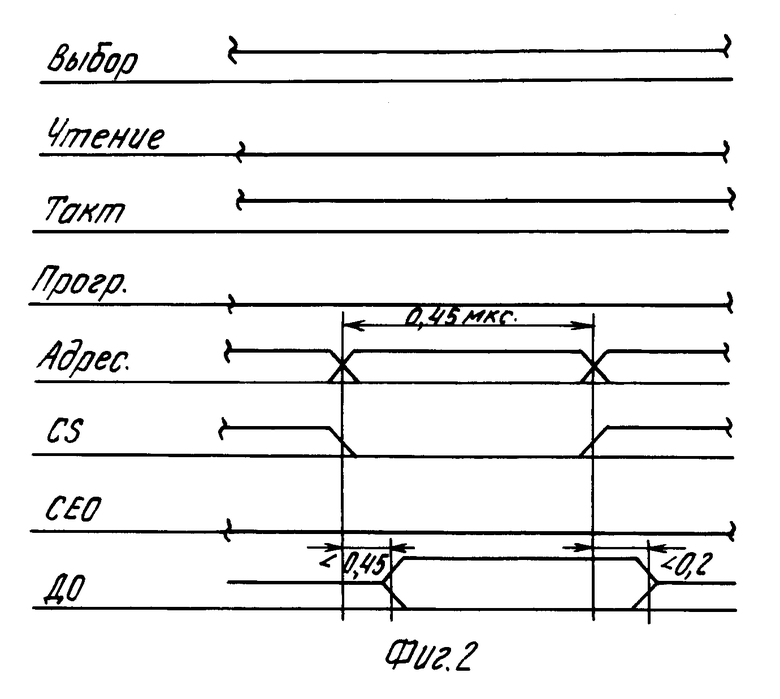

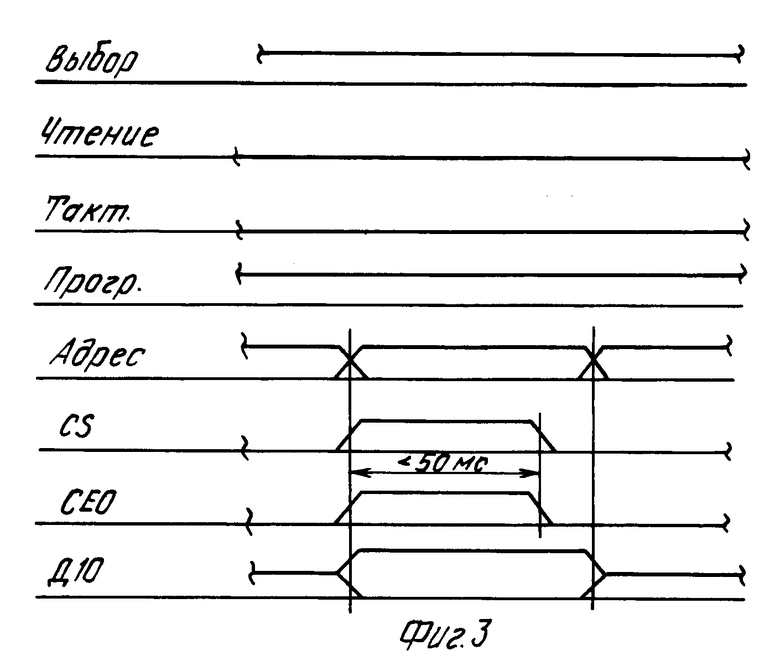

Диаграммы сигналов управления в режимах считывания и программирования показаны на фиг. 2 и 3 соответственно.

Недостатками РПЗУ этого типа являются ограниченное число циклов стирания и ограниченное время хранения информации.

Цель изобретения - увеличение времени хранения информации путем периодического восстановления уровня зарядов на элементах памяти до номинального значения, благодаря чему отпадает необходимость периодического стирания и повторной записи данных в случае, если содержимое программы не подлежит изменению.

Увеличение времени хранения информации достигается тем, что в РПЗУ, состоящее из элементов памяти с ультрафио- летовым стиранием, дешифратора сигнала выбора кристалла, дешифратора сигнала разрешения выхода, формирователя сигнала записи, ключа напряжения программирования, выход которого соединен с входом программирования блока элементов памяти, вход разрешения по выходу которого соединен с выходом дешифратора сигнала разрешения выхода, адресные входы которого объединены с адресными входами дешифратора сигнала выбора кристалла и адресными входами блока элементов памяти и являются адресными входами устройства, информационными входами/выходами которого являются информационные входы/выходы блока элементов памяти, вход выбора микросхемы которого соединен с выходом дешифратора сигнала выбора кристалла, первый управляющий вход которого и управляющий вход дешифратора сигнала разрешения выхода объединены и подключены к выходу формирователя сигнала записи, первый и второй входы которого являются соответственно тактовым входом и входом выбора устройства, третий вход формирователя сигнала записи и первый вход ключа напряжения программирования объединены и являются входом программирования устройства, входом напряжения источника программирования которого является второй вход ключа напряжения программирования, введены байтовый промежуточный регистр и инвертор, выход которого соединяется с входом разрешения выхода байтового промежуточного регистра, вход записи которого соединен с выходом дешифратора сигнала разрешения выхода, информационные входы/выходы байтового промежуточного регистра соединены с информационными входами/выходами устройства, вход инвертора соединен с выходом дешифратора выбора кристалла.

Информация на шине данных записывается из выбранного элемента памяти в промежуточный байтовый регистр, после чего элемент памяти переводится в режим записи и на шины данных поступает информация из промежуточного байтового регистра.

По истечение времени, определяемого генератором записи, проводится процесс восстановления следующего элемента памяти.

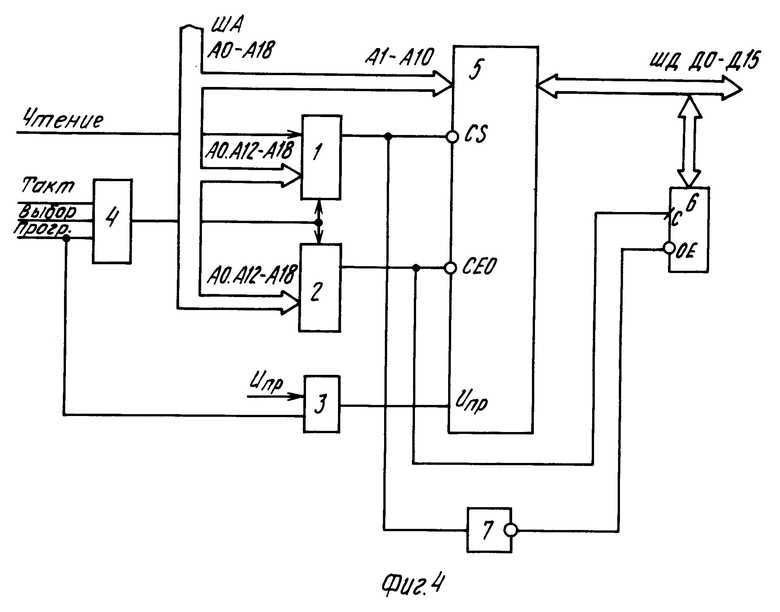

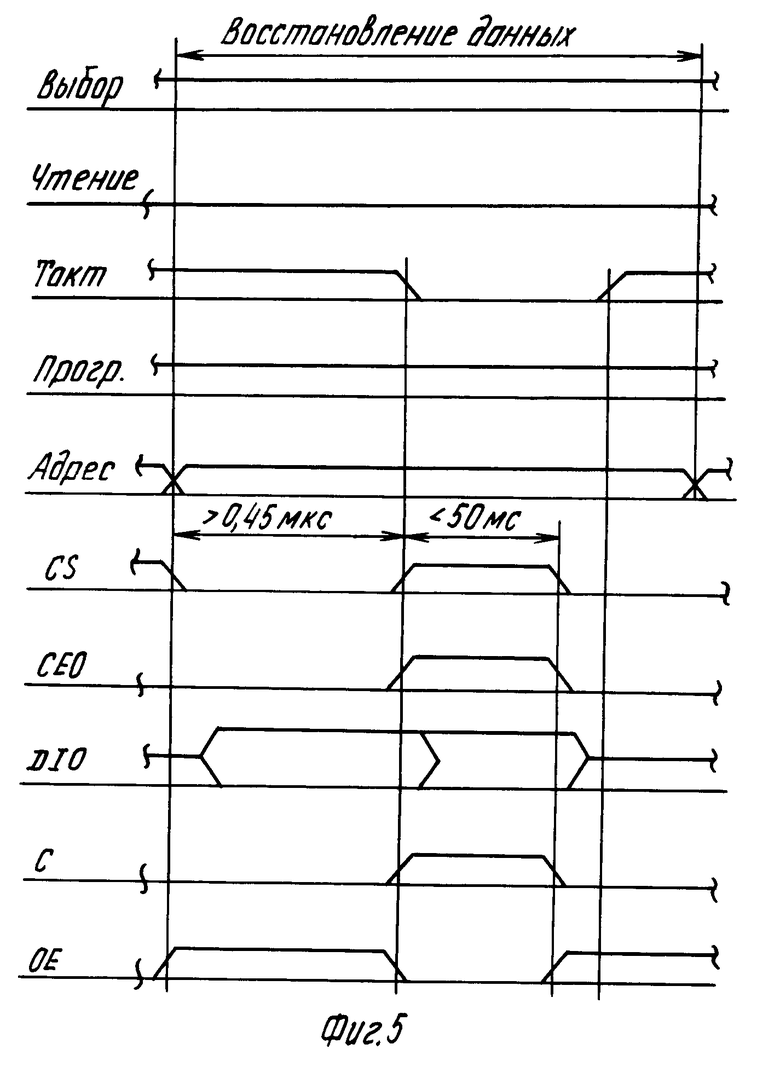

На фиг. 4 изображена структурная электрическая схема предложенного РПЗУ; на фиг. 5 - диаграммы, его работы.

РПЗУ содержит дешифратор 1 сигнала выбора кристалла  , дешифратор 2 сигнала разрешения выхода

, дешифратор 2 сигнала разрешения выхода  , ключ 3 напряжения программирования Uпр, формиро- ватель 4 сигнала записи, элементы памяти 5 с ультрафиолетовым стиранием, байтовый промежуточный регистр 6, инвертор 7, шины адреса (ША) и шины данных (ШД).

, ключ 3 напряжения программирования Uпр, формиро- ватель 4 сигнала записи, элементы памяти 5 с ультрафиолетовым стиранием, байтовый промежуточный регистр 6, инвертор 7, шины адреса (ША) и шины данных (ШД).

Входные сигналы устройства:

"Чтение";

"Такт";

"Выбор" и

"Программирование".

На фиг. 5 показаны сигналы:

"Выбор" - сигнал выбора РПЗУ;

"Чтение" - сигнал обращения к РПЗУ;

"Такт" - сигнал перевода РПЗУ из режима чтения в режим записи;

"Программирование" - сигнал программирования,

"Адрес" - сигнал адреса;

" " - сигнал выбора кристалла;

" - сигнал выбора кристалла; - сигнал разрешения выхода;

- сигнал разрешения выхода;

"DIO" - сигнал данных;

"С" - сигнал записи данного в байтовый промежуточный регистр;

"ОЕ" - сигнал разрешения выхода байтового промежуточного регистра.

В режиме хранения РПЗУ работает следующим образом.

Для выполнения режима сигнал "Выбор"=0, сигнал "Программирование"=0, в результате сигналы  ,

,  , Uпр, С и ОЕ не формируются.

, Uпр, С и ОЕ не формируются.

В режиме чтения сигнал "Выбор"=1, сигнал "Программирование"=0, сигнал "Чтение"= 0, сигнал "Такт"=1, в результате выбора адреса формируется сигнал  , и на шинах данных появляется данное, соответствующее выбранному адресу. Поскольку сигнал

, и на шинах данных появляется данное, соответствующее выбранному адресу. Поскольку сигнал  =1, разрешение выхода байтового промежуточного регистра не формируется.

=1, разрешение выхода байтового промежуточного регистра не формируется.

В режиме программирования сигнал "Выбор"=1, сигнал "Программирование"= 1, сигнал "Чтение"= 0, сигнал "Такт"=1, в результате выбора адреса формируются сигналы  и

и  , и данное, предварительно поданное на шину данных, записывается в элемент памяти. Время записи данного определяется длительностью сигнала записи.

, и данное, предварительно поданное на шину данных, записывается в элемент памяти. Время записи данного определяется длительностью сигнала записи.

В режиме восстановления сигнал "Выбор"=1, сигнал "Чтение"=0, сигнал "Программирование"= 1. В результате выбора адреса производится чтение данного по выбранному адресу.

Спустя промежуток времени не менее 0,45 мкс подается сигнал "Такт"=0 на время, определяемое уровнем восстановления данного (от 0 до 50 мс). Данное записывается в байтовый промежуточный регистр 6 сигналом С, после чего проводится восстановление данного по выбранному адресу.

Спустя промежуток времени, определяемый выдержкой формирователя 4, восстановление заканчивается.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2315372C1 |

| Запоминающее устройство | 1987 |

|

SU1425693A1 |

| Репрограммируемое постоянное запоминающее устройство | 1980 |

|

SU903984A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| УСТРОЙСТВО СБОРА И РЕГИСТРАЦИИ ПОЛЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

SU1825189A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1990 |

|

RU2047918C1 |

Изобретение относится к вычислительной и управляющей технике. Техническим результатом является увеличение времени хранения информации. Репрограммируемое постоянное запоминающее устройство содержит блок элементов памяти с ультрафиолетовым стиранием, дешифратор сигнала выбора кристалла, дешифратор сигнала разрешения выхода, формирователь сигнала записи, ключ напряжения программирования. Технический результат получается за счет введения байтового промежуточного регистра и инвертора. 5 ил.

РЕПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блок элементов памяти с ультрафиолетовым стиранием, дешифратор сигнала выбора кристалла, дешифратор сигнала разрешения выхода, формирователь сигнала записи, ключ напряжения программирования, выход которого соединен с входом программирования блока элементов памяти, вход разрешения по выходу которого соединен с выходом дешифратора сигнала разрешения выхода, адресные входы которого, адресные входы дешифратора сигнала выбора кристалла и адресные входы блока элементов памяти объединены и являются адресными входами устройства, информационными входами-выходами которого являются информационные входы-выходы блока элементов памяти, вход выбора микросхемы которого соединен с выходом дешифратора сигнала выбора кристалла, первый управляющий вход которого и управляющий вход дешифратора сигнала разрешения выхода объединены и подключены к выходу формирователя сигнала записи, первый и второй входы которого являются соответственно тактовым входом и входом выбора устройства, третий вход формирователя сигнала записи и первый вход ключа напряжения программирования объединены и являются входом программирования устройства, входом напряжения источника программирования которого является второй вход ключа напряжения программирования, отличающееся тем, что в него введены байтовый промежуточный регистр и инвертор, выход которого соединен с входом разрешения выхода байтового промежуточного регистра, вход записи которого соединен с выходом дешифратора сигнала разрешения выхода, информационные входы-выходы байтового промежуточного регистра соединены с информационными входами-выходами устройства, вход инвертора соединен с выходом дешифратора выбора кристалла.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Лебедев О.Н | |||

| Микросхемы памяти и их применение | |||

| М.: Радио и связь, 1990, с.125-141. | |||

Авторы

Даты

1995-03-27—Публикация

1992-07-16—Подача