Изобретение относится к цифровой технике, в частности к устройствам обработки и хранения информации.

Известно репрограммируемое постоянное запоминающее устройство (РПЗУ) (см. Лебедев О.Н. Микросхемы памяти и их применение. М.: Радио и связь, 1990, с.125-141.), содержащее дешифратор сигнала выбора кристалла, дешифратор сигнала разрешения выхода, ключ напряжения программирования, формирователь сигнала записи элементов памяти с ультрафиолетовым стиранием, шины адреса и шины данных.

Недостатками известного РПЗУ являются значительное время стирания информации из-за использования ультрафиолетового метода стирания информации, отсутствие санкционирования доступа к считыванию информации и сложность управления, заключающаяся в сложности процессов записи и стирания информации с использованием большого количества цепей управления.

Наиболее близким по совокупности существенных признаков к заявляемому изобретению является репрограммируемое постоянное запоминающее устройство (см. патент РФ №2032234 от 16.07.92, МПК G11C 16/00, "Репрограммируемое постоянное запоминающее устройство", Липчак И.И., опубл. 27.03.95. Бюл. №9), содержащее блок элементов памяти (блок репрограммируемой памяти) с ультрафиолетовым стиранием, дешифратор сигнала выбора кристалла (ДСВК), дешифратор сигнала разрешения выхода (ДСРВ), формирователь сигнала записи (ФСЗ), ключ напряжения программирования (КНП), байтовый промежуточный регистр (БПР) и инвертор. Выход КНП соединен с входом программирования блока элементов памяти, вход разрешения по выходу которого соединен с выходом ДСРВ, адресные входы которого, а также адресные входы ДСВК и адресные входы блока элементов памяти объединены и являются адресными входами устройства. Информационными входами - выходами РПЗУ являются информационные входы - выходы блока элементов памяти, вход выбора микросхемы которого соединен с выходом ДСВК. Первый управляющий вход ДСВК и управляющий вход ДСРВ объединены и подключены к выходу ФСЗ, первый и второй входы которого являются, соответственно, тактовым входом и входом выбора устройства. Третий вход ФСЗ и первый вход КНП объединены и являются входом программирования устройства, входом напряжения источника программирования которого является второй вход КНП. Выход инвертора соединен с входом разрешения выхода БПР, вход записи которого соединен с выходом ДСРВ. Информационные входы - выходы БПР соединены с информационными входами - выходами устройства. Вход инвертора соединен с выходом ДВК.

Недостатками известного РПЗУ являются значительное время стирания информации из-за использования ультрафиолетового метода стирания информации, отсутствие санкционирования доступа к считыванию информации и сложность управления, заключающаяся в сложности процессов записи и стирания информации с использованием большого количества цепей управления.

Задачей, на решение которой направлено предлагаемое изобретение, является создание РПЗУ, обладающего:

- малым временем стирания информации;

- возможностью санкционирования доступа к считыванию информации;

- простотой управления.

Технический результат, заключающийся в уменьшении времени стирания информации, обеспечении санкционирования доступа к ней и упрощении управления, достигается тем, что в репрограммируемое постоянное запоминающее устройство, содержащее блок репрограммируемой памяти, вход программирования которого соединен с выходом блока формирования напряжения программирования, первый вход которого является входом для подключения источника напряжения программирования устройства, введены блок связи, блок микропроцессорного управления, блок формирования сигнала сброса, блок выбора памяти и информационные вход и выход, блок формирования напряжения программирования снабжен вторым входом и третьим входом, соединенным с первым выходом блока формирования сигнала сброса, второй выход которого соединен с первым входом блока микропроцессорного управления, второй вход и первый выход которого соединены, соответственно, с первыми выходом и входом блока связи, вторые вход и выход которого являются информационными входом и выходом, соответственно, устройства, первая группа выходов блока микропроцессорного управления соединена с первой группой входов блока репрограммируемой памяти, группа входов - выходов которого соединена с группой входов - выходов блока микропроцессорного управления, вторая группа выходов которого соединена с группой входов блока выбора памяти, группа выходов которого соединена со второй группой входов блока репрограммируемой памяти, выход которого соединен со вторым входом блока формирования напряжения программирования.

Указанная совокупность признаков позволяет уменьшить время стирания информации в РПЗУ за счет использования электрического стирания информации, обеспечить санкционирование доступа к считыванию информации за счет использования микропроцессорного управления и упростить управление за счет использования стандартного последовательного протокола обмена, использующего двухпроводную линию связи (информационный вход и информационный выход).

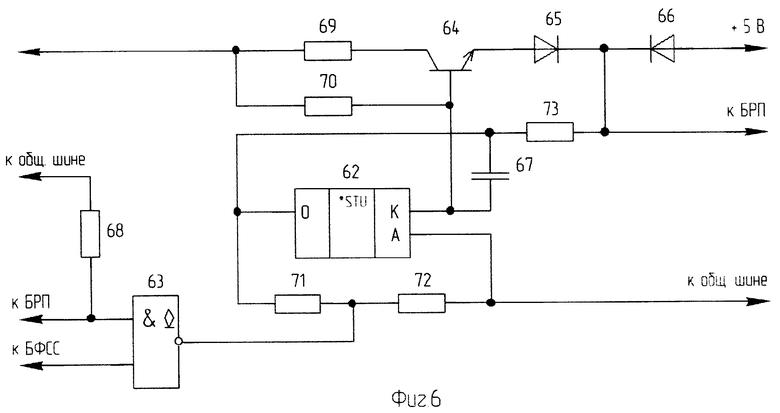

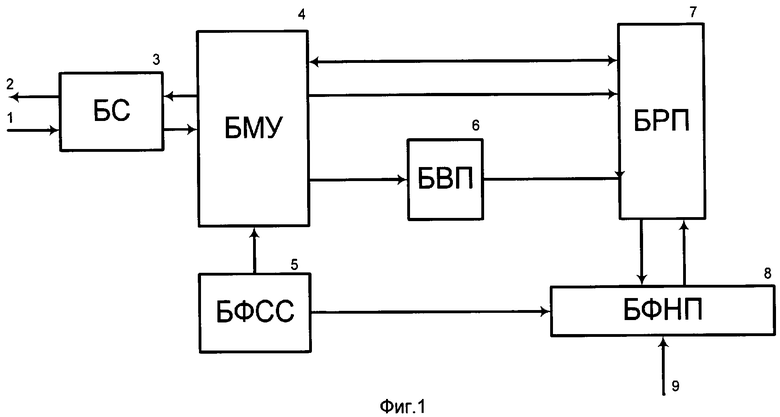

На фиг.1 представлена структурно-функциональная схема репрограммируемого постоянного запоминающего устройства, на фиг.2, фиг.3, фиг.4, фиг.5, фиг.6, фиг.7 - электрические принципиальные схемы блока связи, блока микропроцессорного управления, блока формирования сигнала сброса, блока выбора памяти, блока формирования напряжения программирования и блока репрограммируемой памяти, соответственно.

Репрограммируемое постоянное запоминающее устройство (см. фиг.1) содержит информационные вход 1 и выход 2, блок 3 связи (БС), блок 4 микропроцессорного управления (БМУ), блок 5 формирования сигнала сброса (БФСС), блок 6 выбора памяти (БВП), блок 7 репрограммируемой памяти (БРП) и блок 8 формирования напряжения программирования (БФНП). Вход программирования БРП 7 соединен с выходом БФНП 8, первый вход которого является входом 9 для подключения к источнику питания +27 В (на фиг.1 не показанному). Первый выход БФСС 5 соединен с третьим входом БФНП 8, второй выход соединен с первым входом БМУ 4, второй вход и первый выход которого соединены, соответственно, с первыми выходом и входом БС 3, вторые вход и выход которого являются информационными выходом 2 и входом 1, соответственно, устройства. Первая группа выходов БМУ 4 соединена с первой группой входов БРП 7, группа входов - выходов которого соединена с группой входов - выходов БМУ 4, вторая группа выходов которого соединена с группой входов БВП 6, группа выходов которого соединена со второй группой входов БРП 7, выход которого соединен со вторым входом БФНП 8.

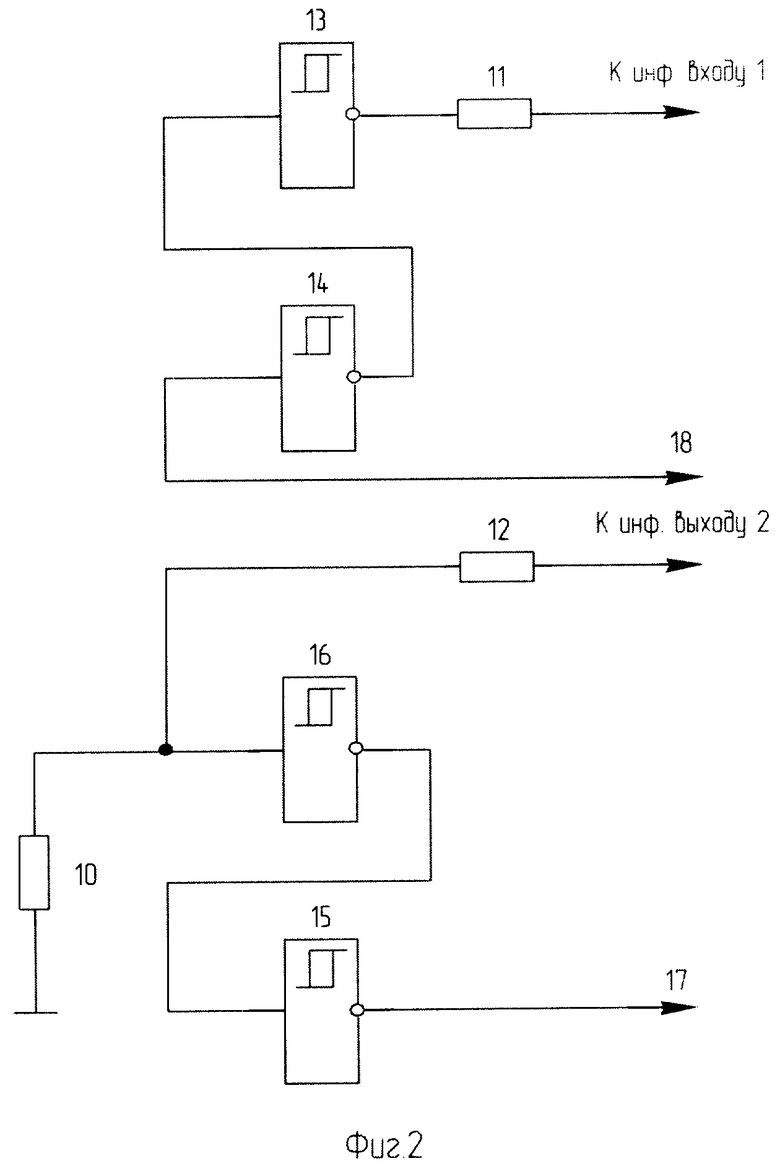

БС 3 предназначен для улучшения помехоустойчивости канала обмена данными по информационным входу 1 и выходу 2 и содержит (см. фиг.2) резисторы 10...12, триггеры Шмитта 13...16. Выход триггера Шмитта 13 соединен с первым выводом резистора 11, второй вывод которого является вторым входом БС 3. Выход триггера Шмитта 16 соединен со входом триггера Шмитта 15, выход триггера Шмитта 14 соединен со входом триггера Шмитта 13. Вход триггера Шмитта 16 соединен с первыми выводами резисторов 10 и 12, второй вывод которого является вторым выходом БС 3. Второй вывод резистора 10 соединен с общей шиной. Выход 17 триггера Шмитта 15 является первым выходом БС 3. Первый вход 18 триггера Шмитта 14 является первым входом БС 3.

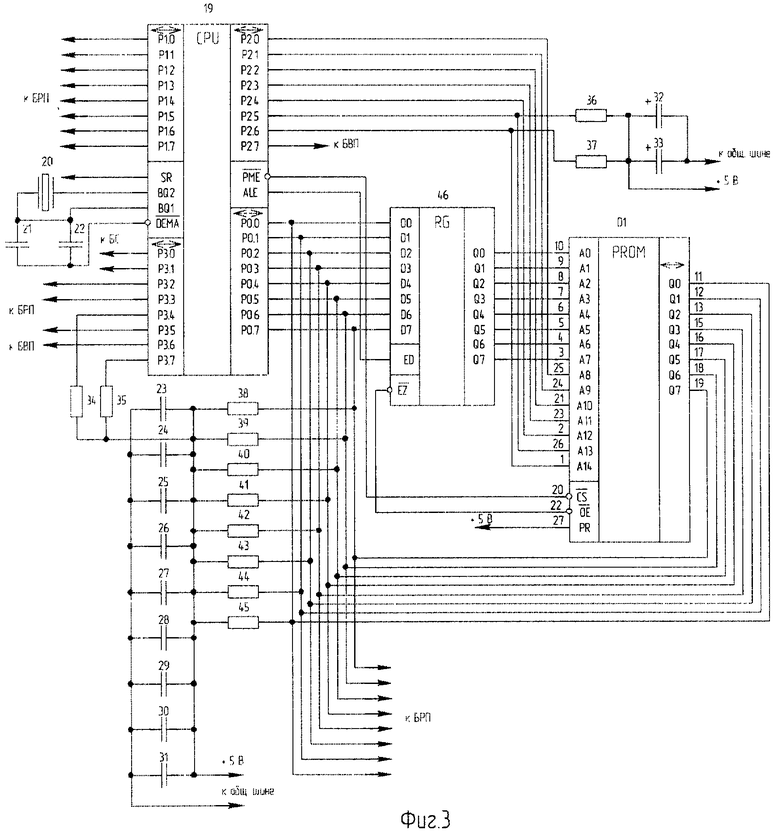

БМУ 4 предназначен для обработки, управления процессом чтения и записи информации и содержит (см. фиг.3) микропроцессор 19, кварцевый резонатор 20, конденсаторы 21...33, резисторы 34...45, регистр 46 и элемент 47 памяти. Первая группа выводов микропроцессора 19 является группой входов - выходов БМУ 4. Вход 48 микропроцессора 19 является первым входом БМУ 4. Первые выводы конденсаторов 21 и 22 соединены, соответственно, с первым и вторым выводами кварцевого резонатора 20 и, соответственно, вторым и третьим выводами микропроцессора 19. Вторые выводы конденсаторов 21, 22 и третий вход микропроцессора 19 соединены с общей шиной. Четвертый и пятый выводы микропроцессора 19 являются, соответственно, первым выходом 17 и вторым входом 18 БМУ 4. Выводы с шестого по восьмой, вторая и третья группы выводов микропроцессора 19 являются первой группой выходов БМУ 4. Первые выводы резисторов 34 и 35 соединены с шиной питания (+5 В), а вторые выводы соединены, соответственно, с двенадцатым и тринадцатым выводами микропроцессора 19. Четвертая группа выводов микропроцессора 19 является второй группой выходов БМУ 4. Девятый и десятый выводы микропроцессора 19 соединены с первыми выводами резисторов 36 и 37, соответственно, вторые выводы которых соединены с шиной питания (+5 В). Третья группа выводов микропроцессора 19 соединена с первыми выводами резисторов 38...45, вторые выводы которых соединены с шиной питания (+5 В). Первая группа выводов регистра 46 соединена с третьей группой выводов микропроцессора 19 и третьей группой выходов элемента 47 памяти. Вторая группа выходов регистра 46 соединена с первой группой входов элемента 47 памяти. Четырнадцатый вывод микропроцессора 19 соединен с первым входом элемента 47 памяти, пятнадцатый вывод микропроцессора 19 соединен с первым входом регистра 46. Третий вход элемента 47 памяти и первые выводы конденсаторов 23...33 соединены с шиной питания (+5 В), а вторые входы регистра 46 и элемента 47 памяти, вторые выводы конденсаторов 23...33 и четвертый вывод элемента 47 памяти соединены с общей шиной. Вторая группа выходов микропроцессора 19 соединена со второй группой входов элемента 47 памяти.

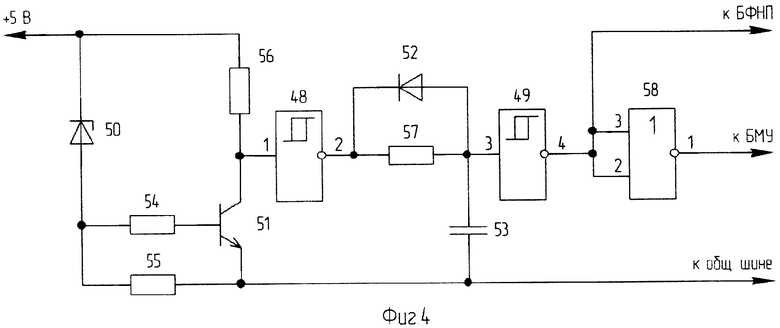

БФСС 5 предназначен для формирования сигнала сброса микропроцессора 19 и предотвращения случайного стирания информации из БРП 7 в момент включения и содержит (см. фиг.4) триггеры Шмитта 48 и 49, стабилитрон 50, транзистор 51, диод 52, конденсатор 53, резисторы 54...57, элемент ИЛИ-НЕ 58. Первые выводы стабилитрона 50 и резистора 56 соединены с шиной питания (+5 В). Первые выводы резисторов 54 и 55 соединены со вторым выводом стабилитрона 50. Второй вывод резистора 54 соединен с базой транзистора 51, эмиттер которого и второй вывод резистора 55 соединены с общей шиной. Коллектор транзистора 51 соединен со вторым выводом резистора 56 и первым входом триггера Шмитта 48, второй выход которого соединен с первыми выводами диода 52 и резистора 57, вторые выводы которых соединены, соответственно, с первым выводом конденсатора 53 и первым входом триггера Шмитта 49. Второй вывод конденсатора 53 соединен с общей шиной. Второй выход триггера Шмитта 49 соединен с первой группой входов элемента ИЛИ-НЕ 58 и является первым выходом БФСС 5. Второй выход элемента ИЛИ-НЕ 58 является вторым выходом БФСС 5.

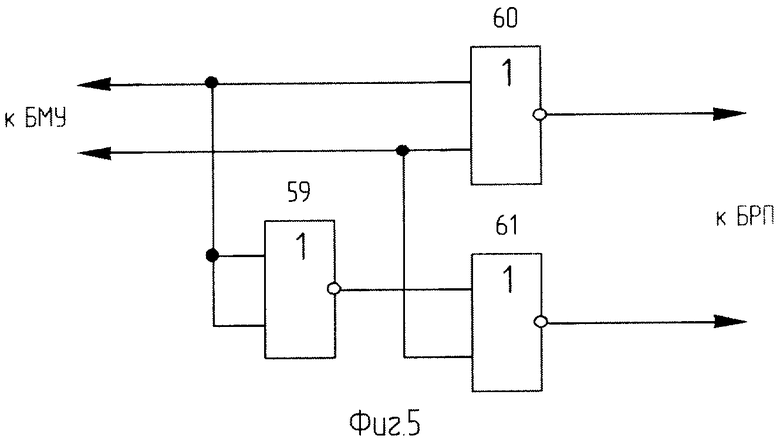

БВП 6 предназначен для формирования сигналов выборки адресных регистров 74 и 75 БРП 7 и содержит (см. фиг.5) элементы ИЛИ-НЕ 59...61. Первая группа входов элемента ИЛИ-НЕ 59 соединена с первым входом элемента ИЛИ-НЕ 60, второй вход которого соединен со вторым входом элемента ИЛИ-НЕ 61 и является группой входов БВП 6. Вторые выходы элементов ИЛИ-НЕ 60 и 61 являются группой выходов БВП 6.

БФНП 8 предназначен для формирования сигналов программирования и содержит (см. фиг.6) стабилизатор 62, элемент И-НЕ 63, транзистор 64, диоды 65 и 66, конденсатор 67, резисторы 68...73. Первые выводы резисторов 71 и 72 соединены с выходом элемента И-НЕ 63. Второй вывод резистора 68 соединен с первым входом элемента И-НЕ 63 и является вторым входом БФНП 8. Второй вход элемента И-НЕ 63 является третьим входом БФНП 8. Второй вывод резистора 72, первый вывод резистора 68 и третий вывод стабилизатора 62 соединены с общей шиной. Первый вывод резистора 69 соединен с первым выводом резистора 70 и является первым входом БФНП 8. Первые выводы стабилизатора 62, конденсатора 67 и резистора 73 соединены со вторым выводом резистора 71. Второй вывод резистора 69 соединен с коллектором транзистора 64, база которого соединена со вторыми выводами резистора 70, стабилизатора 62 и конденсатора 67. Первый вывод диода 66 соединен с шиной питания (+5 В). Эмиттер транзистора 64 соединен с первым выводом диода 65. Второй вывод резистора 73 соединен со вторыми выводами диодов 65 и 66 и является выходом БФНП 8.

БРП 7 предназначен для выбора, записи и хранения информации и содержит (см. фиг.7) адресные регистры 74 и 75 и элементы памяти 76 и 77. Группа входов адресного регистра 74, соединенная с группой входов адресного регистра 75, первые входы элементов памяти 76 и 77 и соединенные между собой вторые входы адресных регистров 74 и 75 являются группой входов БРП 7. Первые входы адресных регистров 74 и 75 являются второй группой входов БРП 7. Группа выходов адресного регистра 74 соединена с первой группой входов элементов памяти 76 и 77, а группа выходов адресного регистра 75 соединена со второй группой входов элементов памяти 76 и 77. Первый выход адресного регистра 75 соединен со вторыми входами элементов памяти 76 и 77, а второй выход адресного регистра 75 соединен с третьими входами элементов памяти 76 и 77. Третий выход адресного регистра 75 является первым выходом БРП 7. Четвертый вход элемента 76 памяти соединен с четвертым входом элемента 77 памяти и является входом программирования БРП 7. Группа выходов элемента 76 памяти соединена с группой выходов элемента 77 памяти и является группой входов - выходов БРП 7.

Репрограммируемое постоянное запоминающее устройство (см. фиг.1) работает следующим образом.

После подачи на РПЗУ напряжения питания +5 В БФСС 5 формирует сигнал сброса и подает его на БМУ 4. Одновременно БФСС 5 формирует сигнал разрешения включения БФНП 8.

Запись информации в РПЗУ осуществляется следующим образом. Управляющая команда с внешнего устройства (на фиг.1 не показана) поступает через управляющий вход 1 РПЗУ, БС 3 на БМУ 4. БМУ 4 анализирует пришедшую команду и с помощью БВП 6 выбирает в БРП 7 необходимый элемент памяти, в который требуется записать информацию, устанавливает адрес необходимой ячейки элемента памяти и необходимые данные и выдает сигнал БРП 7 на включение БФНП 8. Напряжение от источника питания +27 В поступает на БФНП 8 через вход 9. По приходу сигнала включения БФНП 8 формирует необходимое для БРП 7 напряжение программирования и подает его на вход программирования БРП 7. По окончании записи БМУ 4 снимает в обратной последовательности все сигналы управления с БВП 6, БРП 7 и БФНП 8 и выдает через БС 3 и информационный выход 2 на внешнее устройство команду о результате записи.

Считывание информации осуществляется следующим образом. Управляющая команда с внешнего устройства поступает через управляющий вход 1 РПЗУ, БС 3 на БМУ 4. БМУ 4 анализирует пришедшую команду на наличие санкционирующего признака (пароля). При неверном признаке санкционирования БМУ 4 через БС 3 и информационный выход 2 выдает на внешнее устройство команду о запрете считывания информации. При верном признаке санкционирования БМУ 4 с помощью БВП 6 выбирает в БРП 7 необходимый элемент памяти, из которого требуется считать информацию, устанавливает адрес необходимой ячейки элемента памяти и считывает необходимые данные. Считанные данные БМУ 4 через БС 3 и информационный выход 2 выдает на внешнее устройство.

Стирание информации в РПЗУ осуществляется следующим образом. Управляющая команда с внешнего устройства поступает через управляющий вход 1 РПЗУ, БС 3 на БМУ 4. БМУ 4 анализирует пришедшую команду и с помощью БВП 6 выбирает в БРП 7 необходимый элемент памяти, в котором требуется стереть информацию, и выдает сигнал БРП 7 на включение БФНП 8. Напряжение от источника питания +27 В поступает на БФНП 8 через вход 9. По приходу сигнала включения БФНП 8 формирует необходимое для БРП 7 напряжение программирования и подает его на вход программирования БРП 7. По окончании стирания информации БМУ 4 снимает в обратной последовательности все сигналы управления с БВП 6, БРП 7 и БФНП 8 и выдает через БС 3 и информационный выход 2 на внешнее устройство команду о результате стирания.

Таким образом, из описания работы видно, что РПЗУ обладает меньшим временем стирания информации за счет использования электрического стирания ее, санкционированием доступа к считыванию информации за счет использования микропроцессорного управления и простым управлением за счет использования стандартного последовательного протокола обмена, использующего двухпроводную линию связи (информационный вход и информационный выход), а также имеет общий объем памяти 16 К × 8.

Изготовлен лабораторный макет репрограммируемого постоянного запоминающего устройства, испытания которого подтвердили осуществимость и практическую ценность заявленного объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2032234C1 |

| ФОТОМЕТР УЛЬТРАФИОЛЕТОВОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2069843C1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ И СВЯЗИ | 2008 |

|

RU2400805C2 |

| Репрограммируемое постоянное запоминающее устройство | 1980 |

|

SU903984A1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ОТЛАДОЧНОЕ УСТРОЙСТВО ДЛЯ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2016 |

|

RU2634197C1 |

| УСТРОЙСТВО САНКЦИОНИРОВАНИЯ ДОСТУПА | 2004 |

|

RU2273712C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

Изобретение относится к импульсной технике. Достигаемый технический результат - малое время стирания информации, возможность санкционирования доступа к считыванию информации и простота управления. Репрограммируемое постоянное запоминающее устройство содержит информационные вход (1) и выход (2), блок (3) связи (БС), блок (4) микропроцессорного управления (БМУ), блок (5) формирования сигнала сброса (БФСС), блок (6) выбора памяти (БВП), блок (7) репрограммируемой памяти (БРП) и блок (8) формирования напряжения программирования (БФНП). Вход программирования БРП (7) соединен с выходом БФНП (8), первый вход которого является входом (9) для подключения к источнику напряжения программирования, не показанному. Первый выход БФСС (5) соединен с третьим входом БФНП (8), второй выход соединен с первым входом БМУ (4), второй вход и первый выход которого соединены, соответственно, с первыми выходом и входом БС (3), вторые вход и выход которого являются информационными выходом (2) и входом (1), соответственно, устройства. Первая группа выходов БМУ (4) соединена с первой группой входов БРП (7), группа входов - выходов которого соединена с группой входов - выходов БМУ (4), вторая группа выходов которого соединена с группой входов БВП (6), группа выходов которого соединена со второй группой входов БРП (7), выход которого соединен со вторым входом БФНП (8). 7 ил.

Репрограммируемое постоянное запоминающее устройство, содержащее блок репрограммируемой памяти, вход программирования которого соединен с выходом блока формирования напряжения программирования, первый вход которого является входом для подключения источника напряжения программирования устройства, отличающееся тем, что в него введены блок связи, блок микропроцессорного управления, блок формирования сигнала сброса, блок выбора памяти и информационные вход и выход, блок формирования напряжения программирования снабжен вторым входом и третьим входом, соединенным с первым выходом блока формирования сигнала сброса, второй выход которого соединен с первым входом блока микропроцессорного управления, второй вход и первый выход которого соединены, соответственно, с первыми выходом и входом блока связи, вторые вход и выход которого являются информационными выходом и входом соответственно устройства, первая группа выходов блока микропроцессорного управления соединена с первой группой входов блока репрограммируемой памяти, группа входов - выходов которого соединена с группой входов - выходов блока микропроцессорного управления, вторая группа выходов которого соединена с группой входов блока выбора памяти, группа выходов которого соединена со второй группой входов блока репрограммируемой памяти, выход которого соединен со вторым входом блока формирования напряжения программирования.

| РЕПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2032234C1 |

| Способ изготовления фанеры-переклейки | 1921 |

|

SU1993A1 |

| СПОСОБ ВЕДЕНИЯ ДОМЕННОЙ ПЛАВКИ | 2008 |

|

RU2395585C1 |

Авторы

Даты

2008-01-20—Публикация

2006-06-13—Подача