Изобретение относится к области цифровой вычислительной техники и может использоваться в микропроцессорных системах и микроЭВМ.

Цель изобретения - расширение функциональных возможностей устройсва за счет обеспечения режима стирания информации.

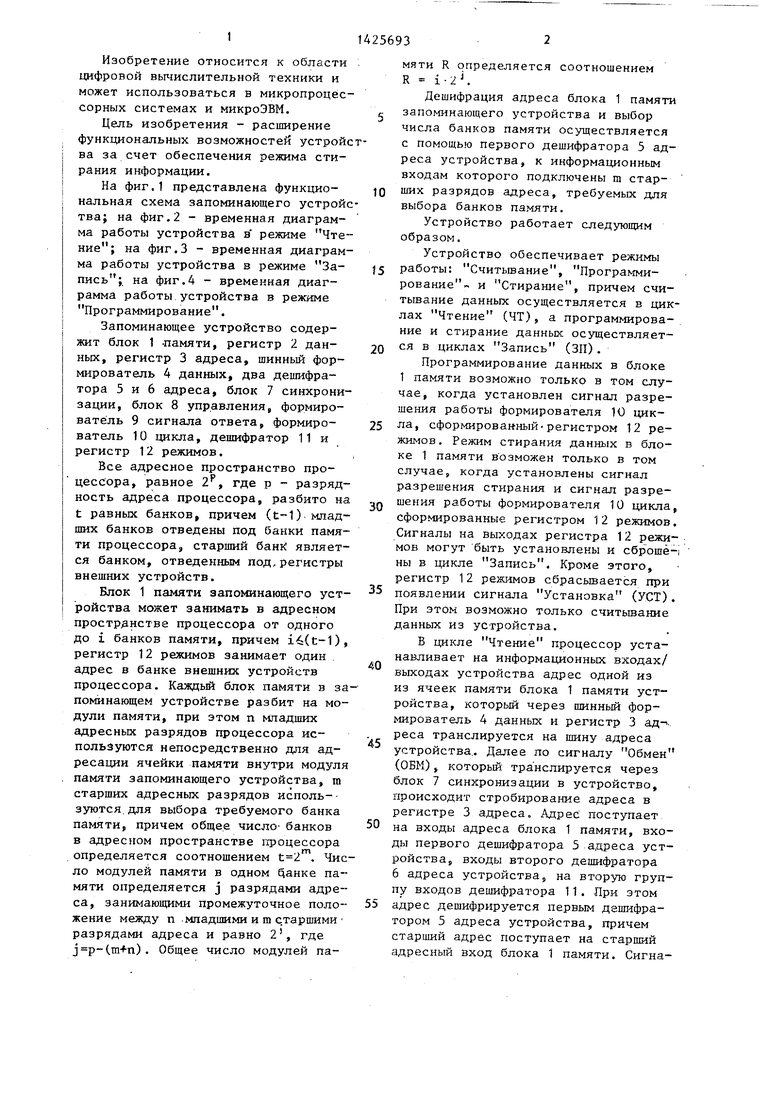

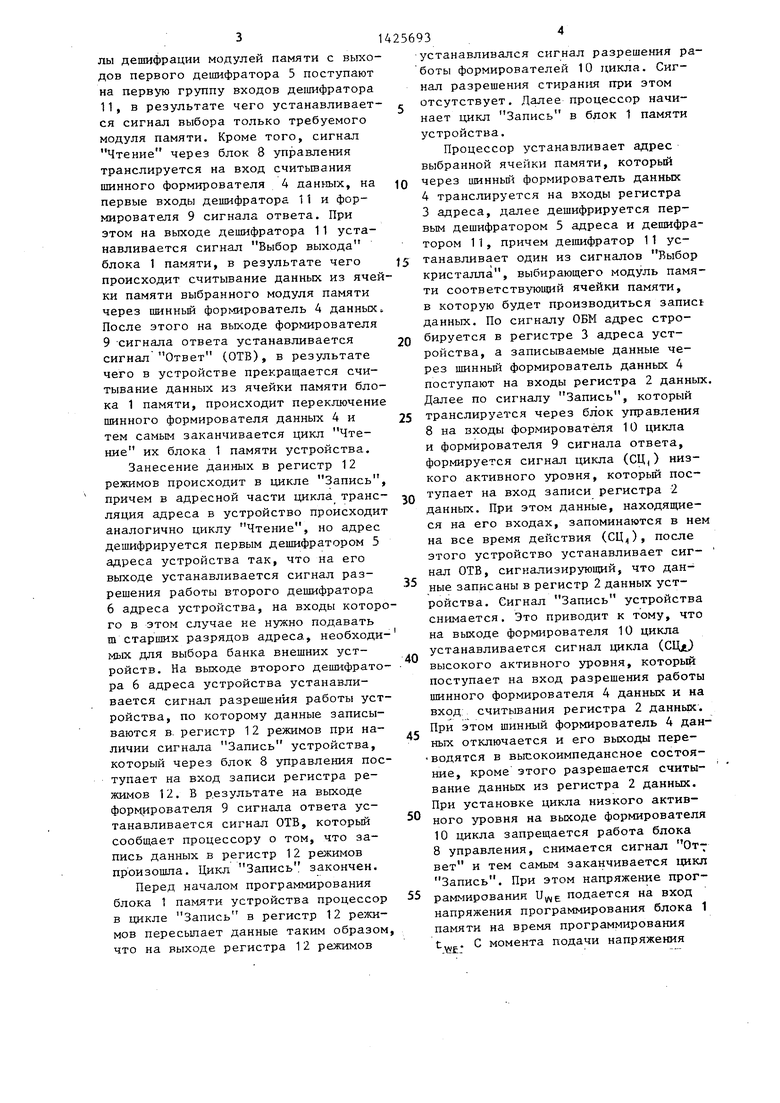

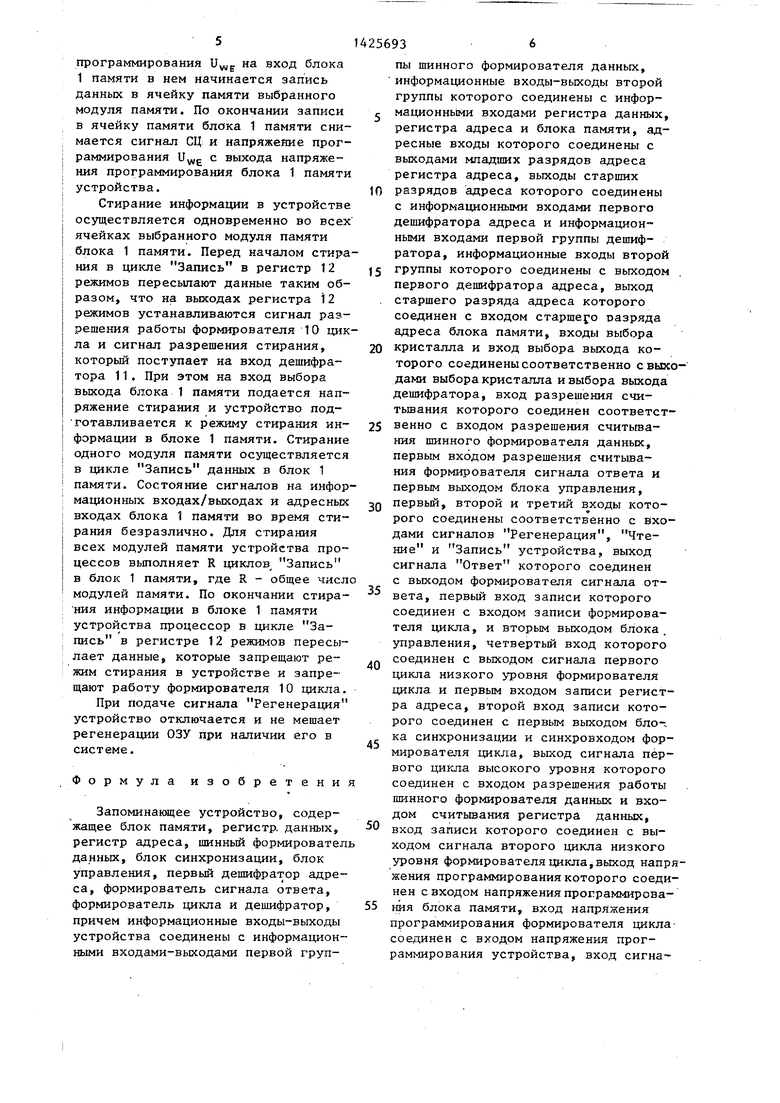

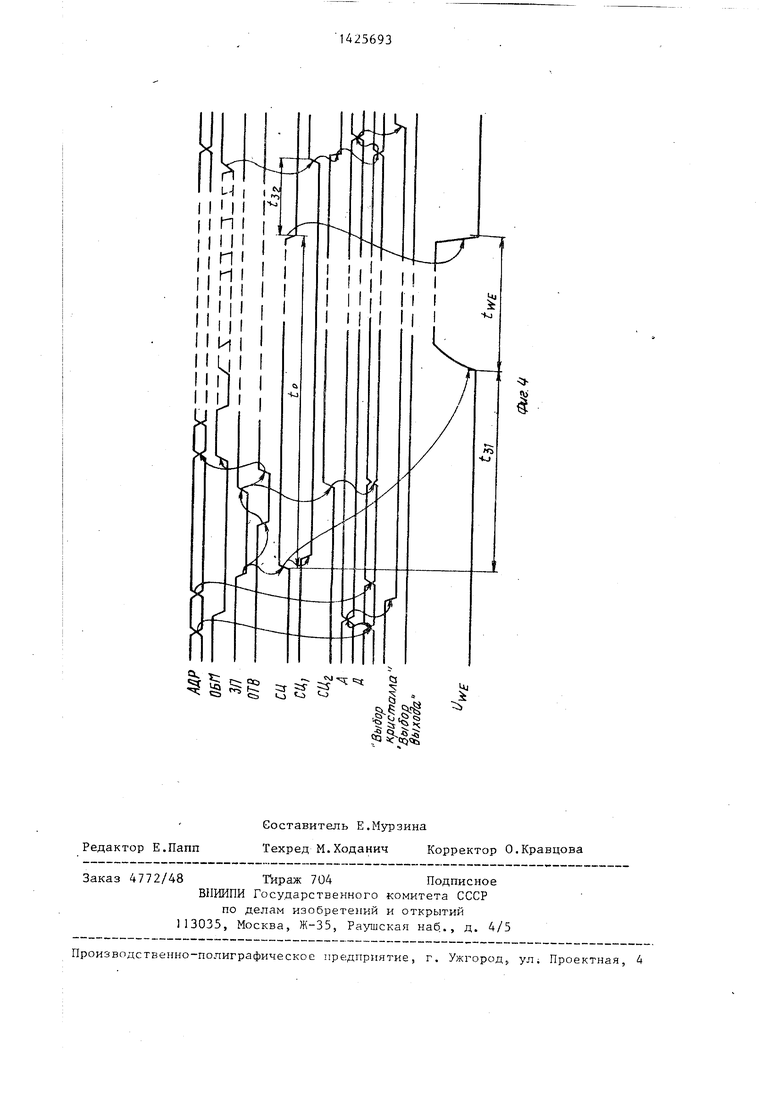

На фиг,1 представлена функциональная схема запоминающего устройства; на фиг.2 - временная диаграмма работы устройства в режиме Чтение ; на фиг.З - временная диаграмма работы устройства в режиме Запись ;, на фиг.4 - временная диаграмма работы устройства в режиме Программирование.

Запоминающее устройство содержит блок 1 -памяти, регистр 2 данных, регистр 3 адреса, шинный формирователь 4 данных, два дешифратора 5 и 6 адреса, блок 7 синхронизации, блок 8 управления, формирователь 9 сигнала ответа, формирователь 10 цикла, дешифратор 11 и регистр 12 режимов.

Все адресное пространство процессора, равное 2, где р - разрядность адреса процессора, разбито на t равных банков, причем (t-1) младших банков отведены под банки памяти процессора, старший банк является банком, отведенным под,регистры внещних устройств.

Блок 1 памяти запоминающего устройства может занимать в адресном прострднстве процессора от одного до i банков памяти, причем i6(t-1), регистр 12 режимов занимает один адрес в банке внешних устройств процессора. Каяздьй блок памяти в за пo G нaющeм устройстве разбит на модули памяти, при этом п младших адресных разрядов процессора используются непосредственно для адресации ячейки памяти внутри модуля памяти запоминающего устройства, m старших адресньк разрядов исполь-- зуются.для выбора требуемого банка памяти, причем общее число банков в адресном пространстве 1троцессора определяется соотношением . Число модулей памяти в одном анке памяти определяется j разрядами адреса, занимающими промежуточное положение между п младшими и m с.таршими разрядами адреса и равно 2, где (m+n). Общее число модулей памяти R определяется соотношением R i-2

Дешифрация адреса блока 1 памяти запоминающего устройства и выбор числа банков памяти осуществляется с помощью первого дешифратора 5 адреса устройства, к информационньм входам которого подключены m старo ших разрядов адреса, требуемых для выбора банков памяти.

Устройство работает следующим образом.

Устройство обеспечивает режимы

5 работы: Считывание, Программирование и Стирание, причем считывание данных осуществляется в циклах Чтение (ЧТ), а программирование и стирание данных осуществляет0 ся в циклах Запись (ЗП).

Программирование данных в блоке 1 памяти возможно только в том случае, когда установлен сигнал разрешения работы формирователя 10 цик5 ла, сформированный-регистром 12 режимов. Режим стирания данных в блоке 1 памяти возможен только в том случае, когда установлены сигнал разрешения стирания и сигнал разреп шения работы формирователя 10 цикла, сформированные регистром 12 режимов. Сигналы на выходах регистра 12 режимов могут быть установлены и сброшё-i ны в цикле Запись. Кроме этого, регистр 12 режимов сбрасьтается при

5 появлении сигнала Установка (УСТ). При этом возможно только считывание данных из устройства.

В цикле Чтение процессор устанавливает на информационньк входах/ выходах устройства адрес одной из из ячеек памяти блока 1 памяти устройства, который через шинный формирователь 4 данных и регистр 3 ад-i. реса транслируется на шину адреса устройства.. Далее по сигналу Обмен (ОБМ), который транслируется через блок 7 синхронизации в устройство, происходит стробирование адреса в регистре 3 адреса. Адрес: поступает.

0 на входы адреса блока 1 памяти, входы первого дешифратора 5 адреса устройства, входы второго дешифратора 6 адреса устройства, на вторую группу входов дешифратора 11. При этом

5 адрес дешифрируется первым дешифратором 5 адреса устройства, причем старший адрес поступает на старший адресный вход блока 1 памяти. Сигна0

3

лы дешифрации модулей памяти с выходов первого дешифратора 5 поступают на первую группу входов дешифратора 11, в результате чего устанавливается сигнал выбора только требуемого модуля памяти. Кроме того, сигнал Чтение через блок 8 управления транслируется на вход считьшания шинного формирователя 4 данных, на первые входы дешифратора 11 и формирователя 9 сигнала ответа. При этом на выходе дешифратора 11 устанавливается сигнал Выбор выхода блока 1 памяти, в результате чего происходит считывание данных из ячейки памяти выбранного модуля памяти через шинньй формирователь 4 данных После этого на выходе формирователя 9 сигнала ответа устанавливается сигнал Ответ (ОТВ), в результате чего в устройстве прекращается считывание данных из ячейки памяти блока 1 памяти, происходит переключение шинного формирователя данных 4 и тем самым заканчивается цикл Чтение их блока 1 памяти устройства.

Занесение данных в регистр 12 режимов происходит в цикле Запись, причем в адресной части цикла трансляция адреса в устройство происходит аналогично циклу Чтение, но адрес дешифрируется первым дешифратором 5 адреса устройства так, что на его выходе устанавливается сигнал разрешения работы второго дешифратора 6 адреса устройства, на входы которого в этом случае не нужно подавать m старших разрядов адреса, необходимых для выбора банка внешних устройств. На выходе второго дешифратора 6 адреса устройства устанавливается сигнал разрешения работы устройства, по которому данные записываются в. регистр 1 2 режимов при наличии сигнала Запись устройства, который через блок 8 управления поступает на вход записи регистра режимов 12. В результате на выходе формирователя 9 сигнала ответа устанавливается сигнал ОТВ, которьм сообщает процессору о том, что запись данных в регистр 12 режимов произошла. Цикл Запись закончен.

Перед началом программирования блока 1 памяти устройства процессор в цикле Запись в регистр 12 режимов пересьшает данные таким образом что на выходе регистра 12 режимов

25693

устанавливался сигнал разрешения работы формирователей 10 цикла. Сигнал разрешения стирания при этом отсутствует. Далее процессор начинает цикл Запись в блок 1 памяти устройства.

Процессор устанавливает адрес выбранной ячейки памяти, который

10 через шинньй формирователь данных 4 транслируется на входы регистра 3 адреса, далее дешифрируется первым дешифратором 5 адреса и дешифратором 11, причем дешифратор 11 ус15 танавливает один из сигналов Выбор кристалла, выбирающего модуль памяти соответствующий ячейки памяти, в которую будет производиться запись данных. По сигналу ОБМ адрес стро2Q бируется в регистре 3 адреса устройства, а записываемые данные через шинньй формирователь данных 4 поступают на входы регистра 2 данных. Далее по сигналу Запись, который

25 транслируется через блок управления 8 на входы формирователя 10 цикла и формирователя 9 сигнала ответа, формируется сигнал цикла (СЦ,) низкого активного уровня, который пос30

тупает на вход записи регистра 2

40

данных. При этом данные, находящиеся на его входах, запоминаются в нем на все время действия (СЦ;,), после этого устройство устанавливает сиг- нал ОТВ, сигнализирующий, что дан ные записаны в регистр 2 данных устройства. Сигнал Запись устройства снимается. Это приводит к тому, что на выходе формирователя 10 цикла устанавливается сигнал цикла (СЦ; высокого активного уровня, который поступает на вход разрешения работы шинного формирователя 4 данных и на вход считывания регистра 2 данных. При этом шинный формирователь 4 данных отключается и его выходы пере- водятся в высокоимпедансное состояние, кроме этого разрешается считывание данных из регистра 2 данных. При установке цикла низкого актив-

ного уровня на выходе формирователя 10 цикла запрещается работа блока 8 управления, снимается сигнал ОТ7 вет и тем самым заканчивается цикл Запись. При этом напряжение прог55 раммирования U,E подается на вход напряжения программирования блока 1 памяти на время программирования . С момента подачи напряжения

45

программирования 1} на вход блока 1 памяти в нем начинается запись данных в ячейку памяти выбранного модуля памяти. По окончании записи в ячейку памяти блока 1 памяти снимается сигнал СЦ и напряжение программирования и с выхода напряжения программирования блока 1 памяти устройства.

Стирание информации в устройстве осуществляется одновременно во всех ячейках выбранного модуля памяти блока 1 памяти. Перед началом стирания в цикле Запись в регистр 12 режимов пересылают данные таким образом, что на выходах регистра 12 режимов устанавливаются сигнал разрешения работы формирователя 10 цикла и сигнал разрешения стирания, который поступает на вход дешифратора 11. При этом на вход выбора выхода блока 1 памяти подается напряжение стирания и устройство под- тотавливается к режиму стирания информации в блоке 1 памяти. Стирание одного модуля памяти осуществляется в цикле Запись данных в блок 1 памяти. Состояние сигналов на информационных входах/выходах и адресных входах блока 1 памяти во время стирания безразлично. Для стирания всех модулей памяти устройства процессов выполняет R циклов Запись в блок 1 памяти, где R - общее числ модулей памяти. По окончании стира- НИЛ информации в блоке 1 памяти устройства процессор в цикле Запись в регистре 12 режимов пересылает данные, которые запрещают режим стирания в устройстве и запрещают работу формирователя 10 цикла.

При подаче сигнала Регенерация устройство отключается и не мешает регенерации ОЗУ при наличии его в системе.

Формула изобретени

Запоминающее устройство, содержащее блок памяти, регистр, данных, регистр адреса, шинный формировател данных, блок синхронизации, блок управления, первый дешифратор адреса, формирователь сигнала ответа, формирователь цикла и дешифратор, причем информационные входы-выходы устройства соединены с информационными входами-выходами первой груп

4256936

пы шинного формирователя данных, информационные входы-выходы второй группы которого соединены с инфор- г мационнь1ми входами регистра данных, регистра адреса и блока памяти, адресные входы которого соединены с выходами младших разрядов адреса регистра адреса, выходы старших

10 разрядов адреса которого соединены с информационными входами первого дешифратора адреса и информационными входами первой группы дешифратора, информационные входы второй

J5 группы которого соединены с выходом

первого дешифратора адреса, выход . старшего разряда адреса которого соединен с входом старшего разряда адреса блока памяти, входы выбора

20 кристалла и вход выбора выхода которого соединены соответственно с выходами выбора кристалла и выбора выхода дешифратора, вход разрешения счи- тьшания которого соединен соответст25 венно с входом разрешения считьгоа- ния шинного формирователя данных, первьм входом разрешения считьша- ния формирователя сигнала ответа и первым выходом блока управления,

2Q первый, второй и третий входы которого соединены соответственно с входами сигналов Регенерация, Чтение и Запись устройства., выход сигнала Ответ которого соединен с выходом формирователя сигнала от35

40

45

50

55

вета, первый вход записи которого соединен с входом записи формирователя цикла, и вторым выходом блока, управления, четвертый вход которого соединен с выходом сигнала первого цикла низкого уровня формирователя цикла и первым входом записи регистра адреса, второй вход записи которого соединен с первым выходом бло-, ка синхронизации и синхровходом формирователя цикла, выход сигнала первого цикла высокого уровня которого соединен с входом разрешения работы шинного формирователя данных и входом считьшания регистра данных, вход записи которого соединен с выходом сигнала второго цикла низкого уровня формирователя цикла,выход напряжения программирования которого соединен с входом напряжения программирования блока памяти, вход напряжения программирования формирователя цикла- соединен с входом напряжения программирования устройства, вход сигна

7

ла Обмен которого соединен с первым входом блока синхронизации, второй выход которого соединен с пятым входом блока управления, шестой вхо которого соединен с выходом соответствующего разряда первого дешифратора адреса, выходы регистра данных соединены с информационными входами блока памяти, отличаю- 1Д е е с я тем, что, с целью расширения функциональньк возможностей за счет обеспечения режима стирания информаиз1И, в него введены второй дешифратор адреса и регистр ре- жимов, выход разрешения стирания которого соединен с входом разрешения стирания дешифратора, вход записи которого соединен с шестым входом блока управления, третий вы- ход которого соединен соответственн с входами сброса регистра режимов и формирователя цикла, вход разрешения работы которого соединен с

режимов, вход записи которого соединен с четвертым выходом блока управления и вторым входом записи формирователя сигнала ответа, второй вход разрешения считывания которого соединен с пятым выходом блока управления, шестой выход которого соединен с вторым входом блока синхронизации, информационные входы регистра режимов соединены соответственно с информационными входами регистра адреса, выходы которого соединены с информационными входами второго дешифратора адреса, выход которого соединен с седьмым входом блока управления, восьмой вход которого соединен с входом Установка устройства, вход напряжения стирания которого соединен с входом напряжения стирания дешифратора, выход разрешения работы первого дешифратора адреса соединен с входом разрешения работы второго дешифратора ад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с памятью | 1988 |

|

SU1683020A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1501071A1 |

| Устройство для контроля блоков памяти | 1991 |

|

SU1833920A1 |

| Устройство для сопряжения многоблочной памяти с процессором и вводно-выводными устройствами | 1984 |

|

SU1280645A1 |

| РЕПРОГРАММИРУЕМОЕ ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1992 |

|

RU2032234C1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1988 |

|

SU1557568A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Устройство для сопряжения процессора с группой устройств памяти | 1986 |

|

SU1348843A1 |

Изобретение относится к цифровой вычислительной технике и мо,жет использоваться в микропроцессорных системах и микроЭВМ. Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения режима стирания информации. Запоминающее устройство содержит блок памяти 1, регистр данных 2, регистр адреса 3, шинный формирователь данных 4, два дешифратора адреса 5,6, блок синхронизации 7, блок управления 8, формирователь сигнала ответа 9, формирователь цикла 1U, дешифратор 1.1 и регистр режимов 12. Новым в ус тройст- ве является введение второго дешифратора адреса и регистра режимов, что дало возможность организовать в устройстве режимы электрического стирания информации и перепрограм- мирования. 4 ил. i СЛ С Фиг.1

выходом разрешения работы регистра 25

ЛДР

АЦР

У вресуГ Данные

ОВП

.J

Фив. 2

жи

h

| Авторское свид,етельство СССР № 117782U, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1984 |

|

SU1236493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-09-23—Публикация

1987-03-04—Подача