Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления универсальных вычислительных машин и микропроцессоров.

Предлагаемое устройство управления позволяет повысить сопровождаемость программ, написанных на языке ассемблера, что расширяет область его применения.

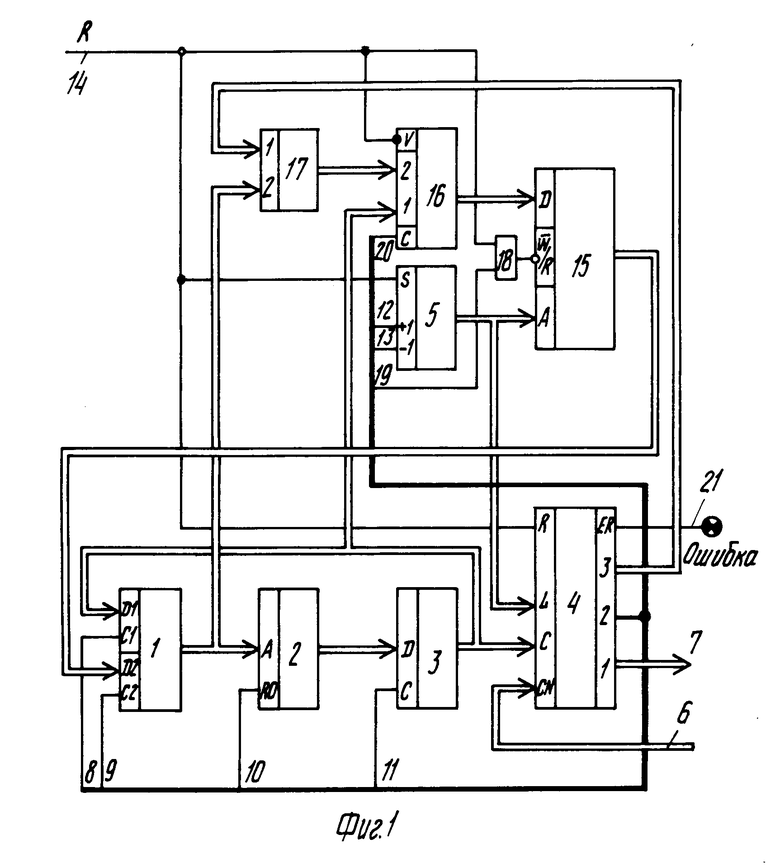

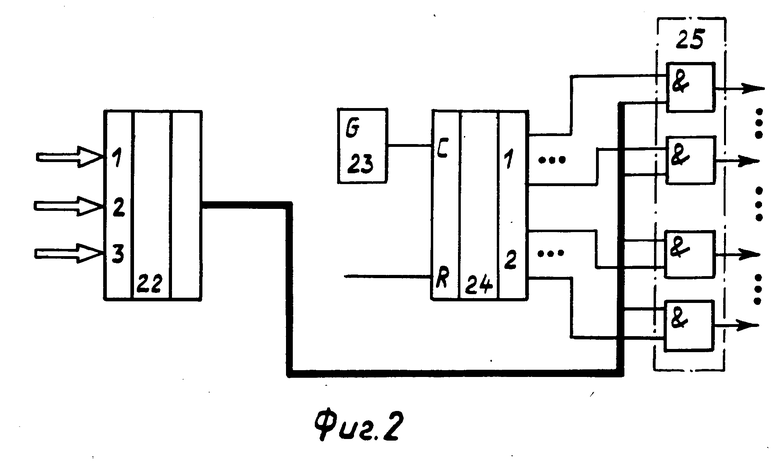

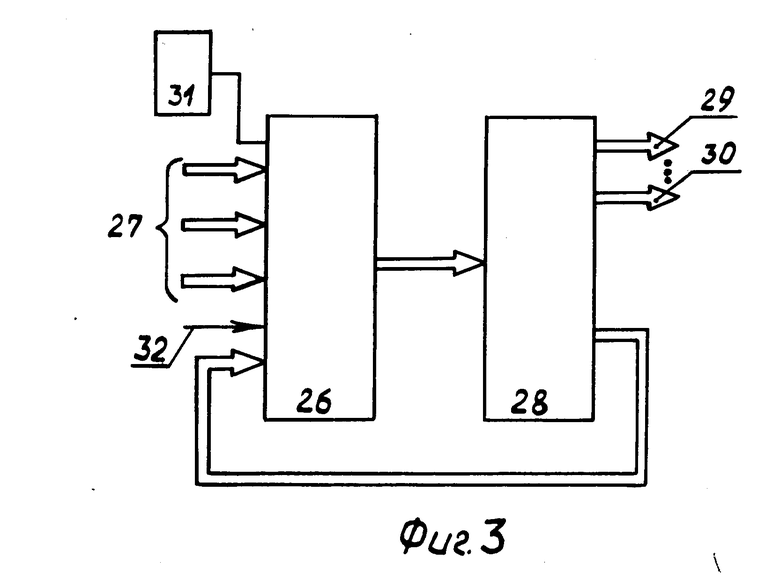

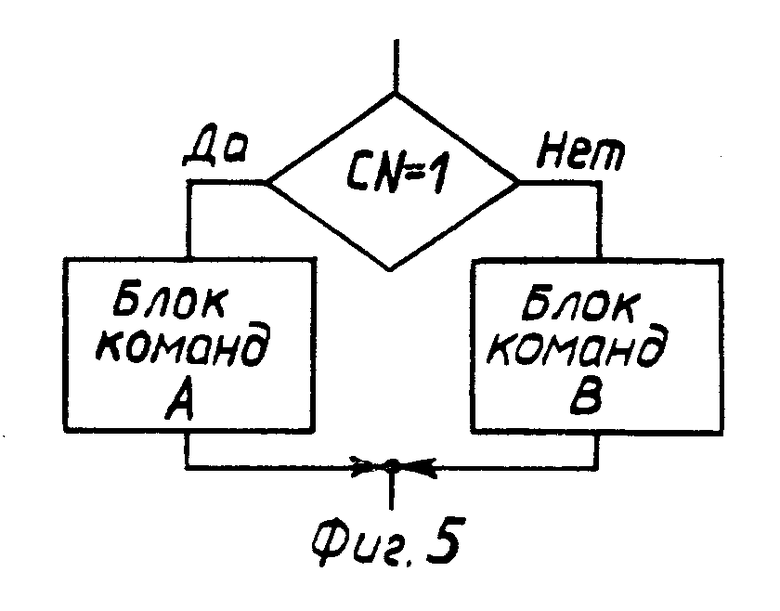

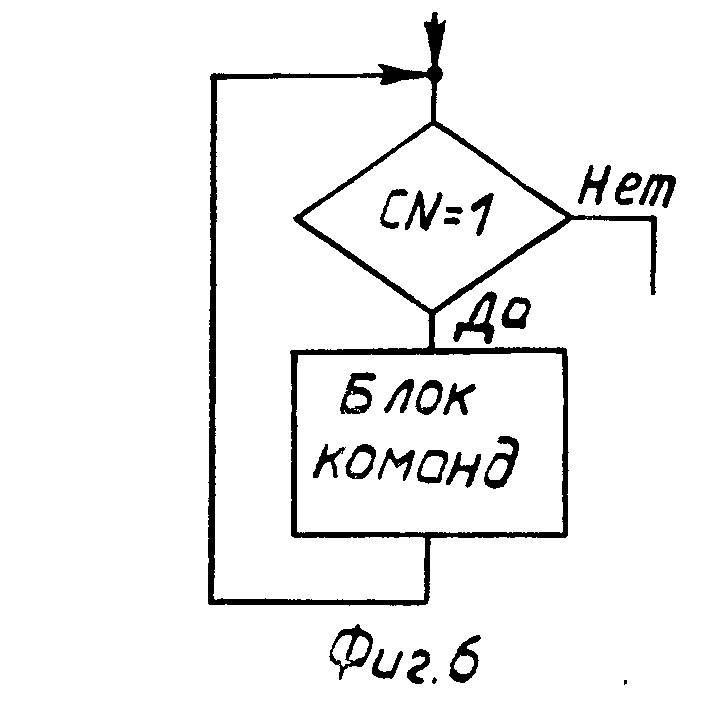

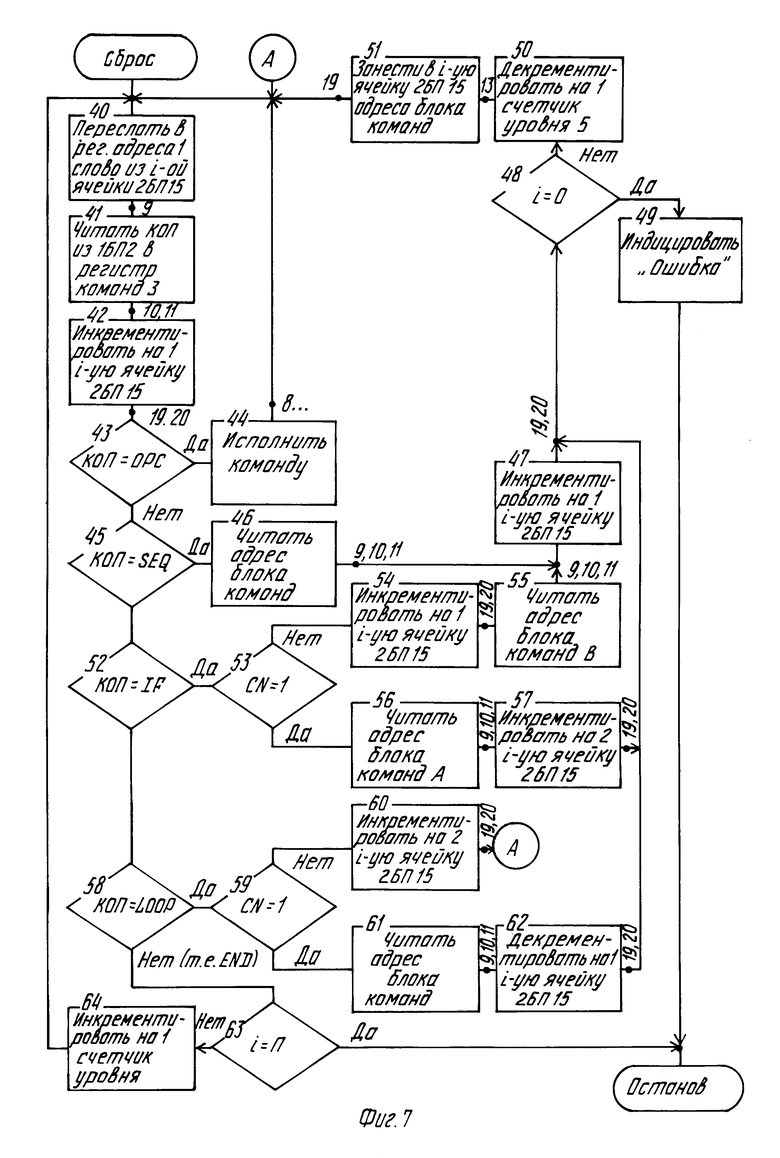

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг.2 и 3 варианты схемотехнической реализации генератора управляющих сигналов; фиг.4,5 и 6 граф-схемы реализованных конструкций структурного программирования типа "следование", "ветвление" и "цикл" соответственно; на фиг.7 граф-схема работы устройства.

Устройство управления содержит регистр адреса 1, первый блок памяти 2, регистр команд 3, генератор 4 управляющих сигналов, счетчик 5 уровня программы, причем выходы регистра команд 3 соединены с первой группой информационных входов регистра адреса 1, выход которого соединен с входом адреса первого блока памяти 2, выход которого соединен с информационным входом регистра команд 3, выход которого соединен также с входом кода операции генератора 4 управляющих сигналов, вход логических условий устройства соединен с входом логических условий генератора 4 управляющих сигналов, выход первого поля микроопераций которого является выходом микроопераций 7 устройства, с первого по шестой 8-13 выходы второго поля микроопераций которого соединены соответственно с первым и вторым входами синхронизации регистра адреса 1, с входом разрешения чтения первого блока памяти 2, входом синхронизации регистра команд 3, входами прибавления и вычитания единицы счетчика 5 уровня программы, выход которого соединен с входом уровня программы генератора 4 управляющих сигналов, вход сброса которого совместно с входом установки счетчика 5 уровня программы подключен к входу 14 начальной установки устройства. Кроме того, устройство содержит второй блок памяти 15, мультиплексор 16, сумматор 17 и элемент ИЛИ 18, выход которого соединен со входом управления записью-чтением второго блока памяти 15, выход которого соединен со второй группой информационных входов регистра адреса 1, вход адреса с выходом счетчика 5 уровня программы, а вход данных с выходом мультиплексора 16, первый информационный вход которого подключен к выходу регистра команд 3, а второй информационный вход к выходу сумматора 17, первый вход которого соединен с выходом третьего поля микроопераций генератора 4, управляющих сигналов, а второй с выходом регистра адреса 1, кроме того вход 14 начальной установки устройства соединен с входом разрешения мультиплексора 16 и первым входом элемента ИЛИ 18, второй вход которого и вход управления мультиплексора 16 соединены соответственно с седьмым 19 и восьмым 20 выходами второго поля микроопераций генератора 4 управляющих сигналов, выход "Ошибка" которого является выходом ошибки 21 устройства.

Генератор 4 управляющих сигналов (первый вариант) (фиг.2) содержит дешифратор 22, имеющий три группы входов, генератор 23 тактовых сигналов, кольцевой счетчик 24 и набор логических схем 25, выходы которых образуют первую и вторую группы выходов генератора 4 управляющих сигналов. Вход сброса кольцевого счетчика является входом сброса генератора 4 управляющих сигналов.

Генератор 4 управляющих сигналов (второй вариант) (фиг.3) содержи блок 26 микропрограммного управления, имеющий три группы входов 27, блок 28 постоянной памяти, первая 29 и вторая 30 группы выходов которого образуют соответствующие группы выходов генератора 4 управляющих сигналов, и генератор 31 тактовых сигналов. При этом вход 32 сброса генератора 4 управляющих сигналов связан с входом установки начального состояния блока 26 микропрограммного управления. Последний может быть реализован на микросхеме К589ИКО1, а блок 28 постоянной памяти на микросхемах серии К556.

Все остальные блоки предлагаемого устройства являются стандартными и легко реализуются на интегральных микросхемах, например, серии К555.

Устройство обеспечивает управление вычислительным процессом в соответствии с многоуровневой программой, размещаемой в блоке 2 памяти. Такая программа содержит блоки команд различных уровней. Команды каждого уровня могут быть операционными или управляющими. Операционной команде соответствует какая-либо арифметическая или логическая операция, а управляющей соответствует одна из возможных программных структур (фиг.4,5,6). В поле кода операции указываетcя один из пяти возможных типов команд: операционная команда ОРС, команда следование SEQ (см.фиг.4), команда ветвления IF (см.фиг.5), команда цикла LOOP (см.фиг.6), команда конца END. В поле адреса управляющих команд указывается один (SEQ и LOOP) или два (IF) адреса начала блоков на следующем, более низком, уровне.

Устройство работает в соответствии с граф-схемой (фиг.7).

После подачи сигнала "Сброс", поступающего на вход 14 установки начального состояния устройства, счетчик 5 уровня программы устанавливается в состояние n, где n количество уровней. Работа мультиплексора 16 запрещена. Кроме того, устанавливается начальное состояние генератора 4 управляющих сигналов. Фронтом сигнала "Сброс" нулевое состояние с выходов мультиплексора 16 записывается в блок памяти 15 по адресу n, (т.е. на n-уровне устанавливается нулевой адрес команды).

После снятия сигнала "Сброс" генератор 4 управляющих сигналов на линии 9 второй группы выходов формирует импульс. Благодаря этому будет выполнена микрооперация 40 "Переслать в регистр адреса 1 содержимое из i-й ячейки второго блока памяти 15", поскольку выход второго блока памяти 15 соединен со второй группой информационных входов регистра адреcа 1. Следовательно, в начальный момент в регистр адреса 1 будет записан адрес команды n-го уровня. Каждая микрооперация граф-схемы (фиг. 7) для большей наглядности помечена номерами соответствующих разрядов второй группы выходов генератора 4 управляющих сигналов. Затем генератор 4 управляющих сигналов сделает следующий шаг: 41 "Читать код операции из первого блока памяти 2 в регистр команд 3". При этом генерируются импульсы на выходах 10 и 11 генератора 4 управляющих сигналов. Первый поступает на вход разрешения чтения блока памяти 2, а второй на вход разрешения записи регистра 3 команд. Этим обеспечивается выборка кода операции (КОП) команды из блока 2 памяти и запись его в регистр 3 команд. При первом проходе после сброса в регистре 3 команд будет записан код первой команды n-го уровня.

Далее выполняется микрооперация 42 "Инкрементировать на 1 i-ю ячейку второго блока памяти 15". Это действие обеспечивается импульсами на выходах 19 и 20 генератора 4 управляющих сигналов. С помощью сумматора 17 содержимое регистра адреса 1 складывается с содержимым третьего поля микроопераций генератора 4 управляющих сигналов, где в этот момент установлен код 1, и сумма поступает на второй информационный вход мультиплексора 16, который выбирается импульсом на выходе 20 генератора 4 управляющих сигналов. По импульсу на выходе 19 генератора 4 управляющих сигналов, поступающему через элемент ИЛИ 18 на вход управления записью-чтением второго блока памяти 15, данные с выхода мультиплексора 16 записываются в i-ю ячейку второго блока памяти 15.

Дальнейшие операции зависят от типа команды. Вначале производится проверка 4к3 "Команда ОРС?". Эта проверка реализуется логикой генератора 4 управляющих сигналов путем сравнения кода операции команды, поступающего с выхода регистра команд 3 на вход кода операций генератора 4 управляющих сигналов, с известным кодом операционной команды ОРС. Если сравнение дает положительный результат, то выполняется микрооперация 44 "Исполнить команду". При этом генератор 4 управляющих сигналов генерирует сигналы первой, второй и третьей группы выходов, чем обеспечивается считывание адресной части команды, выборка из блока памяти 2 операнда адресованного командой, и выполнение команды в операционном устройстве. После этого генератор 4 управляющих сигналов обеспечивает повторение микрооперации, начиная с блока 40.

Если же код операции не совпадает с кодом операционной команды ОРС, то выполняется проверка 45 "Команда SEQ". Если результат проверки положительный, то выполняются микрооперации 46 "Читать адрес блока команд" аналогично последовательности микроопераций 40 и 41 и далее 47 "Инкрементировать на 1 i-ю ячейку второго блока памяти 15" аналогично микрооперации 42. После этого выполняется микрооперация 48 "i 0". Эта микрооперация выполняется логикой генератора 4 управляющих сигналов путем сравнения кода текущего уровня, поступающего с выходов счетчика 5 уровня программы на входы уровня программы генератора 4 управляющих сигналов, с нулевым кодом. Если результат сравнения проверки 48 поло- жительный, то выполняется микрооперация 49 "Индицировать "Ошибка", генератор 4 управляющих сигналов выставляет соответствующий уровень на выходе "Ошибка" 21 и устройство переходит в состояние "Останов". Если результат сравнения отрицательный, т.е. уровень программы не нулевой, реализуется понижение уровня программы. Это обеспечивается микрооперацией 50 "Декрементировать на 1 счетчик уровня 5". При этом генератор 4 управляющих сигналов формирует импульс на линии 13 второй группы выходов, поступающий на вход вычитания единицы счетчика 5 уровня программы. После этого выполняется микрооперация 51 "Занести в i-ю ячейку второго блока памяти адрес блока команд". Адрес блока команд, поступающий на вход данных второго блока памяти 15 из регистра команд 3 через первый информационный вход мультиплексора 16, записывается импульсом, сформированным генератором 4 управляющих сигналов на линии второй группы выходов 19, поступающий через элемент ИЛИ 18 на вход разрешения чтения-записи второго блока памяти 15. После этого генератор 4 управляющих сигналов обеспечивает повторение микроопераций, начиная с блока 40.

Если проверка 45 дала отрицательный результат, выполняется микрооперация 52 "Команда IF?". Если результат проверки положительный, то выполняется проверка условия CN ветвления 53 "CN1". Эта проверка реализуется логикой генератора 4 управляющих сигналов путем сравнения заданного кода условия CN с истинным значением, поступающим по входу 6 логических условий. Если результат сравнения положительный, то выполняются микрооперации 56, 57 аналогично выполнению микроопераций 46 и 42 соответственно, иначе микрооперации 54, 55 и 47 аналогично выполнению микроопераций 42, 46 и 42 соответственно. Далее, если нет ошибки, после выполнения микроопераций 48, 50 и 51, описанных выше, начинается очередной цикл управления.

Если проверка 52 дала отрицательный результат, выполняется микрооперация 58 "Команда LOOP?". Если результат проверки положительный, то выполняется проверка условия зацикливания 59 "CN 1?" аналогично проверке 53, описанной выше. Если результат проверки положительный, то выполняются микрооперации 61, 62 аналогично выполнению микроопераций 46 и 42 соответственно, иначе микрооперация 60 аналогична выполнению микрооперации 42. Далее после выполнения микроопераций 48, 50 и 51, описанных выше, начинается очередной цикл управления.

Если код операции не совпадает с кодами команд ОРС, SEQ, IF и LOOP (проверки 43, 45, 52, 58), значит, в регистре команд 3 зафиксирована команда END. Тогда выполняется проверка 42 "i n?". Если результат отрицательный, то это означает, что закончилась последовательность команд i-го уровня и необходимо перейти на более высокий программный уровень. В этом случае выполняется микрооперация 64 "Инкрементировать на 1 счетчик уровня 5". Генератор 4 управляющих сигналов в этом случае генерирует импульс на линии 12, который поступает на вход прибавления единицы счетчика 5 уровня программы и увеличивает его содержимое на единицу, обеспечивая переход на более высокий уровень. Если же проверка 63 дает положительный результат, то это означает, что закончена программа наивысшего уровня. В этом случае в генераторе 4 управляющих сигналов происходит блокирование всех выходных импульсов и устройство переходит в состояние "Останов".

Рассматривая циклическую граф-схему работы устройства (см.фиг.7), легко убедиться в том, что запущенная с уровня n программа в зависимости от вложенности за счет управляющих команд может последовательно понижать свой уровень, вплоть до уровня 0. На каждом уровне могут исполняться соответствующие блоки команд. По окончании очередного блока команд i-го уровня (команда END) происходит возврат к (i+1)-му программному уровню и т.д. до тех пор пока не будет обнаружена команда ЕND n-го уровня. На этом выполнение многоуровневой программы заканчивается.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления | 1986 |

|

SU1417005A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| ОПЕРАЦИОННЫЙ БЛОК | 1993 |

|

RU2034330C1 |

| Устройство для контроля микропроцессорной системы | 1989 |

|

SU1640693A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК И КОРРЕКЦИЕЙ ОДИНОЧНОЙ ОШИБКИ | 1993 |

|

RU2062512C1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПСЕВДОСЛУЧАЙНОГО СИГНАЛА | 1989 |

|

SU1692272A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1988 |

|

SU1585830A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1566332A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1481775A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств управления универсальных вычислительных машин и микропроцессоров. Для повышения сопровождаемости программ, написанных на языке ассемблера, в устройство, содержащее регистр адреса, первый блок памяти, регистр команд, генератор управляющих сигналов, счетчик уровня программы, введены второй блок памяти, мультиплексор, сумматор и элемент ИЛИ. Устройство обеспечивает управление вычислительным процессом по многоуровневой программе, написанной в соответствии с основными принципами структурного программирования. 7 ил.

УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее регистр адреса, первый блок памяти, регистр команд, генератор управляющих сигналов, счетчик уровня программы, причем выходы регистра команд соединены с первой группой информационных входов регистра адреса, выход которого соединен с входом адреса первого блока памяти, выход которого соединен с информационным входом регистра команд, выход которого соединен также с входом кода операции генератора управляющих сигналов, вход логических условий устройства соединен с входом логических условий генератора управляющих сигналов, выход первого поля микроопераций устройства, с первого по шестой выходы второго поля микроопераций генератора управляющих сигналов соединены соответственно с первым и вторым входами синхронизации регистра адреса, с входом разрешения чтения первого блока памяти, входом синхронизации регистра команд, входами прибавления и вычитания единицы счетчика уровня программы, выход которого соединен с входом уровня программы генератора управляющих сигналов, вход сброса которого совместно с входом установки счетчика уровня программы подключен к входу начальной установки устройства, отличающееся тем, что в него введены второй блок памяти, мультиплексор, сумматор и элемент ИЛИ, выход которого соединен с входом управления записью-чтением второго блока памяти, выход которого соединен с второй группой информационных входов регистра адреса, вход адреса с выходом счетчика уровня программы, а вход данных с выходом мультиплексора, первый информационный вход которого подключен к выходу регистра команд, а второй информационный вход к выходу сумматора, первый вход которого соединен с выходом третьего поля микрооперацией генератора управляющих сигналов, а второй с выходом регистра адреса, кроме того, вход начальной установки устройства соединен с входом разрешения мультиплексора и первым входом элемента ИЛИ, второй вход которого и вход управления мультиплексора соединены соответственно с седьмым и восьмым выходами второго поля микроопераций генератора управляющих сигналов, выход "Ошибка" которого является выходом ошибки устройства.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство управления | 1986 |

|

SU1417005A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-04-30—Публикация

1993-06-10—Подача