Ю

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1545221A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1536384A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1559347A1 |

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем. Устройство обеспечивает контроль микропроцессорных систем с тремя шинами Цель изобретения - расширение функциональных возможностей устройства., Устройство обеспечивает обнаружение некорректннх

О)

4 О О СО СО

обращений к различным устройствам, а также обнаружение некорректных ситуаций, связанных с ложными обращениями в пределах одного устройства, контролируемой системы, и дает возможность для контроля за нормальным функционированием мультипрограммных вычислительных систем в процессе решения всех задачо При наличии любой некорректной ситуации в контролируемой системе активизируется выход ошибки устройства, который может использоваться различным образом, наИзобретение относится к вычислительной технике ч может быть исполь- 20 зовано при построении надежных микропроцессорных систем.

Цель изобретения - расширение функциональных возможностей за счет возможности обнаружения некорректных си- 25 туаций, связанных с ложными переходами от одной задачи к другой в пределах одного устройства контролируемой системы и возможности контроля за корректным выполнением задач в мульти- 30 программной микропроцессорной системе.

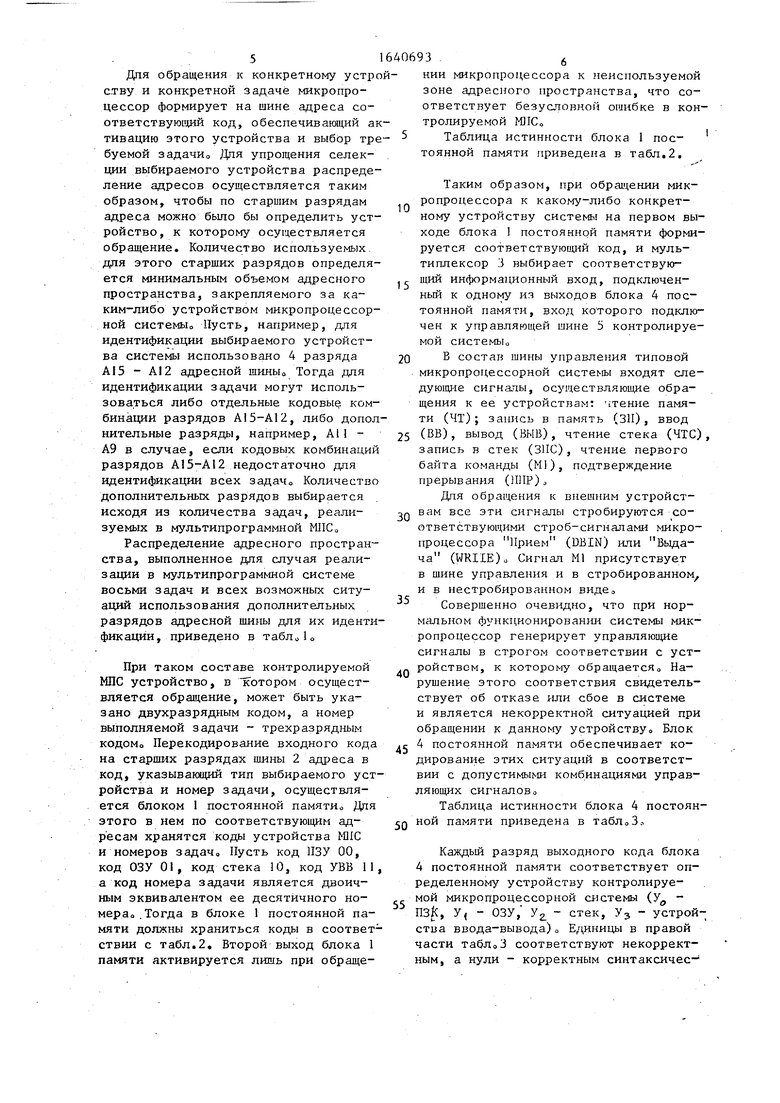

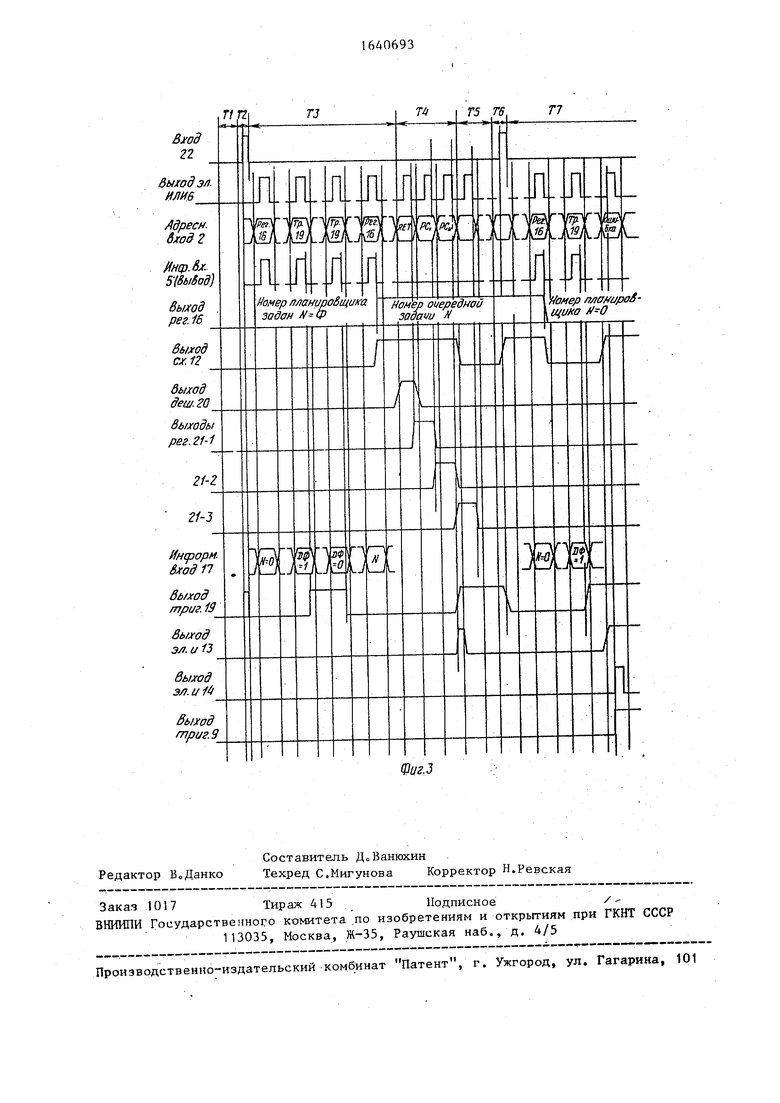

На фиго изображена структурная схема устройства; на фиг.2 - схема вычислительного процесса в мультипрограммной микропроцессорной системе и схема алгоритма планировщика задач; на фигсЗ - временные диаграммы функционирования устройства,.

Устройство для контроля микропроцессорной системы содержит первый блок 1 постоянной памяти, адресный вход 2 устройства, мультиплексор 3, второй блок 4 постоянной памяти, первый информационный вход 5 устройства, первый элемент ИЛИ 6, первый элемент И 7, второй элемент ИЛИ 8, первый триггер 9, выход 10 ошибки устройства, вход 11 сброса устройства, схему 12 сравнения, второй элемент И 13 и третий элемент И 14, третий элемент ИЛИ 15, регистр 16, второй информационный вход 17 устройства, первый дешифратор 18, второй триггер 19, вто рой дешифратор 20, регистр сдвига 21, вход 22 Прерывание текущей задачи устройства,.

пример подключаться к входу запроса прерывания процессора системы,. Это обеспечивает переход к подпрограмме обработки прерывания по ошибке с целью принятия необходимых действий„ Устройство для контроля микропроцессорных систем содержит блоки 1 и 4 постоянной памяти, мультиплексор 3, дешифраторы 18 и 20, регистр 16, регистр 21 сдвига, схему 12 сравнения, триггеры 9 и 19, элементы И 7, 13 и 14, элементы ИЛИ 6, 8 и 15. 3 ил 3 табл.

0

5 0

5

,- 5

0

Предлагаемое устройство обеспечивает контроль наиболее распространенной микропроцессорной системы (МНС) с тремя шинами: шиной адреса, шиной данных и шиной управления,, Для обеспечения контроля микропроцессорной системы вход 5 предлагаемого устройства подключается к управляющей шине, вход 17 - к шине данных контролируемой системы, вход 2 - к старшим разрядам ее адресной шины, вход 11 сброса - к цепи сброса микропроцессора, вход 22 - к выходу системного таймера или другого устройства, инициирующего прерывание текущей задачи, а выход сигнала ошибки 10 может подключаться к входу запроса прерывания микропроцессора или использоваться другим образом

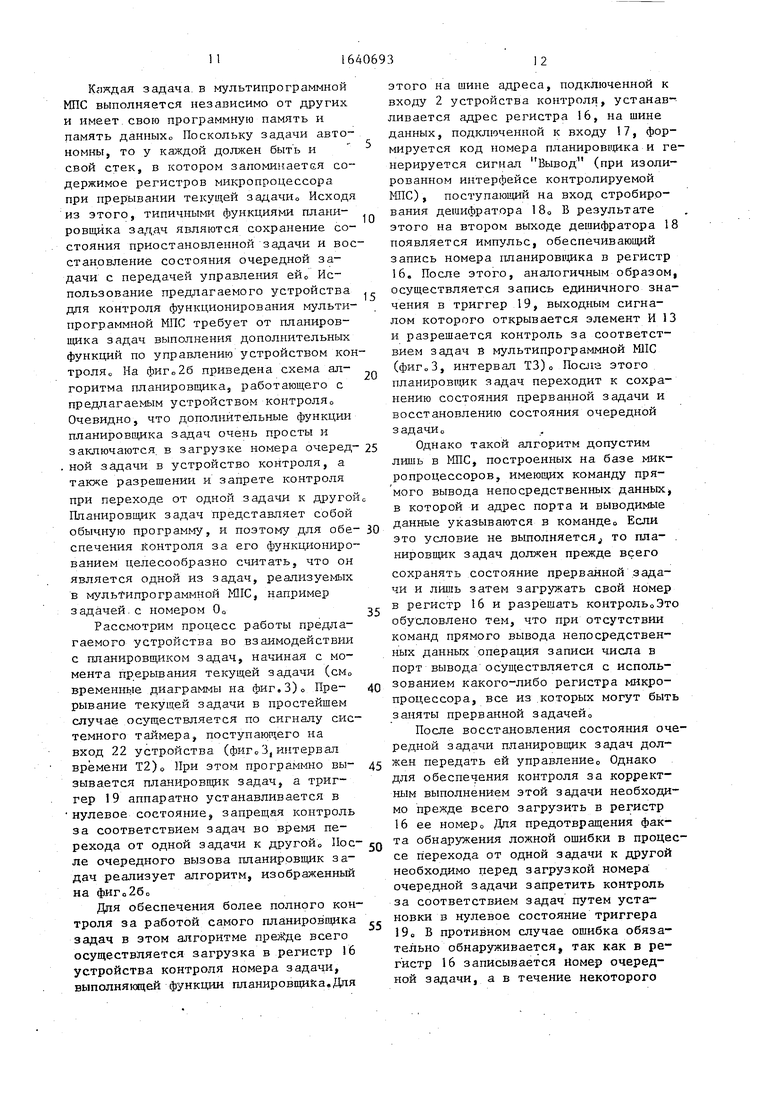

В общем случае контролируемая микропроцессорная система содержит память программ (ШТ), размещаемых чаще всего в ПЗУ, память данных (ПД) и стек, размещаемых в ОЗУ, и устройства ввода-вывода (УВВ)0 При работе микропроцессорной системы в мультипрограммном режиме каждая задача независимо от других имеет персональную память программ, память данных и стек, размещаемых в общем ПЗУ и ОЗУ, а также персональные УВВ0 На стадии программирования программист должен распределить зону адресного пространства микропроцессора и закрепить за каждым из устройств системы и каждой задачей определенную адресную зону0 При этом, как правило, часть адресного пространства остается неиспользованной о

Для обращения к конкретному устроству и конкретной задаче микропроцессор формирует на шине адреса соответствующий код, обеспечивающий активацию этого устройства и выбор требуемой задачио Для упрощения селекции выбираемого устройства распределение адресов осуществляется таким образом, чтобы по старшим разрядам адреса можно было бы определить устройство, к которому осуществляется обращение. Количество используемых для этого старших разрядов определяется минимальным объемом адресного пространства, закрепляемого за каким-либо устройством микропроцессорной системы Пусть, например, для идентификации выбираемого устройства системы использовано 4 разряда AI5 - А12 адресной шины Тогда для идентификации задачи могут использоваться либо отдельные кодовые комбинации разрядов А15-А12, либо дополнительные разряды, например, АИ - А9 в случае, если кодовых комбинаций разрядов AI5-A12 недостаточно для идентификации всех задач Количество дополнительных разрядов выбирается исходя из количества задач, реализуемых в мультипрограммной МПСа

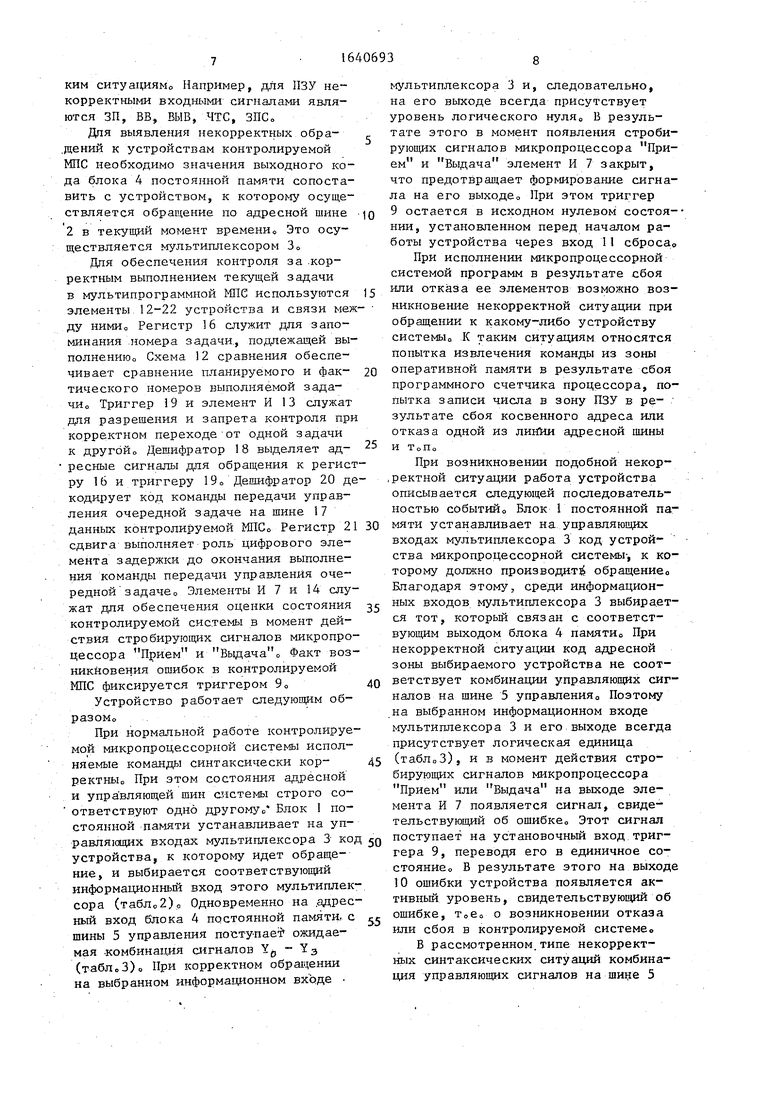

Распределение адресного пространства, выполненное для случая реализации в мультипрограммной системе восьми задач и всех возможных ситуаций использования дополнительных разрядов адресной шины для их идентификации, приведено в табл„1

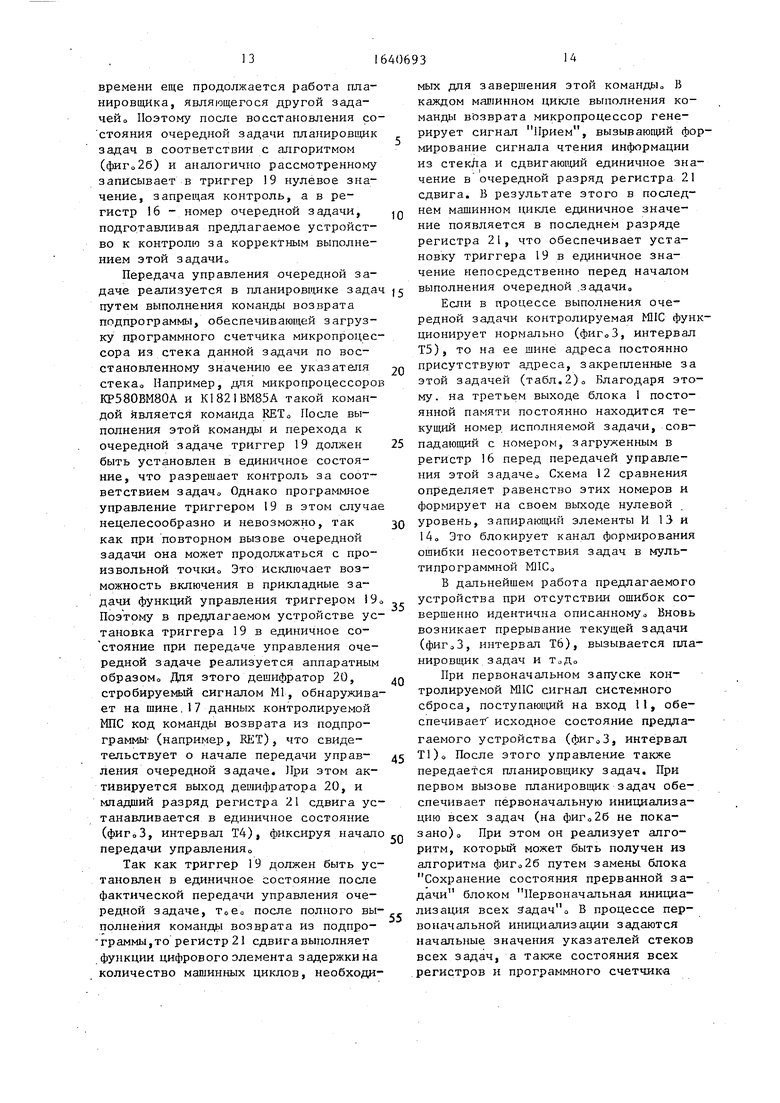

При таком составе контролируемой МПС устройство, в котором осуществляется обращение, может быть указано двухразрядным кодом, а номер выполняемой задачи - трехразрядным кодом Перекодирование входного кода на старших разрядах шины 2 адреса в код, указывающий тип выбираемого устройства и номер задачи, осуществляется блоком 1 постоянной памяти Для этого в нем по соответствующим адресам хранятся коды устройства МПС и номеров задачо Пусть код ПЗУ 00, код ОЗУ 01, код стека 10, код УВВ 11, а код номера задачи является двоичным эквивалентом ее десятичного номера .Тогда в блоке 1 постоянной памяти должны храниться коды в соответствии с табл.2. Второй выход блока 1 памяти активируется лишь при обращении микропроцессора к неиспользуемой зоне адресного пространства, что соответствует безусловной ошибке в контролируемой МПС

Таблица истинности блока 1 пос- тоянной памяти приведена в табл.2.

0

0

5

0

5

5

0

Таким образом, при обращении микропроцессора к какому-либо конкретному устройству системы на первом выходе блока 1 постоянной памяти формируется соответствующий код, и мультиплексор 3 выбирает соответствующий информационный вход, подключенный к одному из выходов блока 4 постоянной памяти, вход которого подключен к управляющей шине Ь контролируемой системы

В состав шины управления типовой микропроцессорной системы входят следующие сигнаты, осуществляющие обращения к ее устройствам: чтение памяти (ЧТ); запись в память (311), ввод 5 (ВВ), вывод (ВЫВ), чтение стека (ЧТС), запись в стек (ЗПС), чтение первого байта команды (Ml), подтверждение прерывания (ПНР)0

Для обращения к внешним устройствам все эти сигналы стробируются соответствующими строб-сигналами микропроцессора Прием (DBIN) или Выдача (WRIIE)o Сигнал Ml присутствует в шине управления и в стробированном, и в нестробированном виде

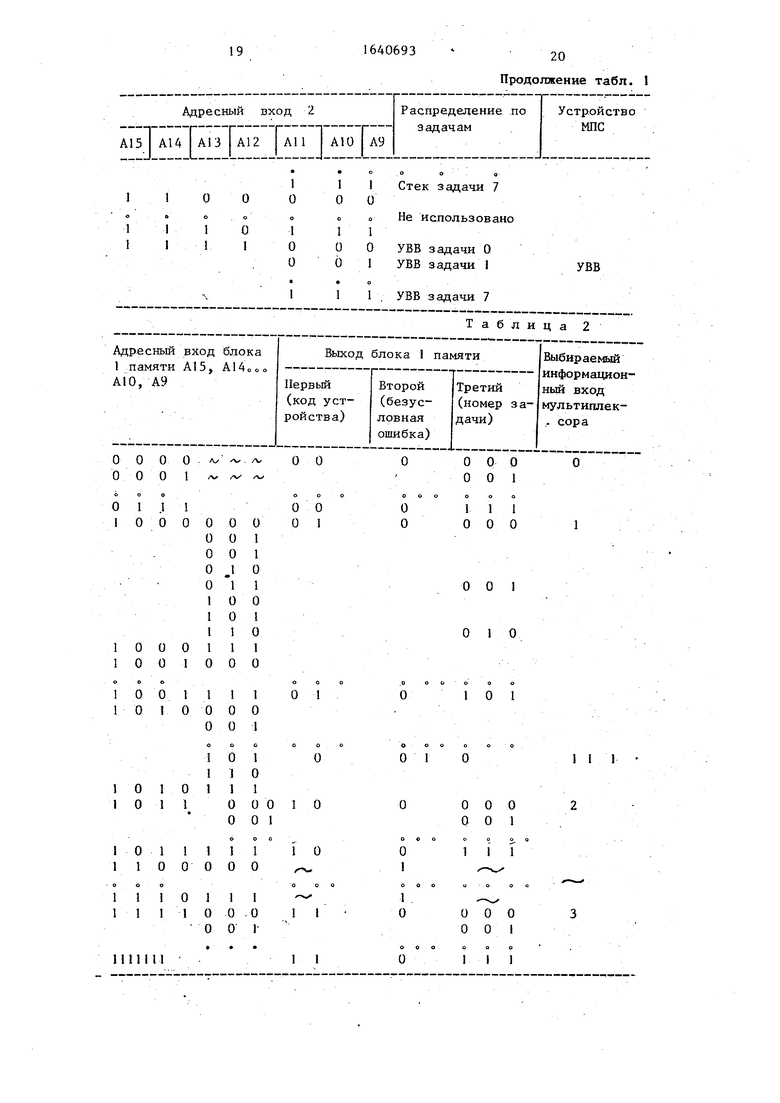

Совершенно очевидно, что при нормальном функционировании системы микропроцессор генерирует управляющие сигналы в строгом соответствии с устройством, к которому обращается Нарушение этого соответствия свидетельствует об отказе или сбое в системе и является некорректной ситуацией при обращении к данному устройству Блок 4 постоянной памяти обеспечивает кодирование этих ситуаций в соответствии с допустимыми комбинациями управляющих сигналов

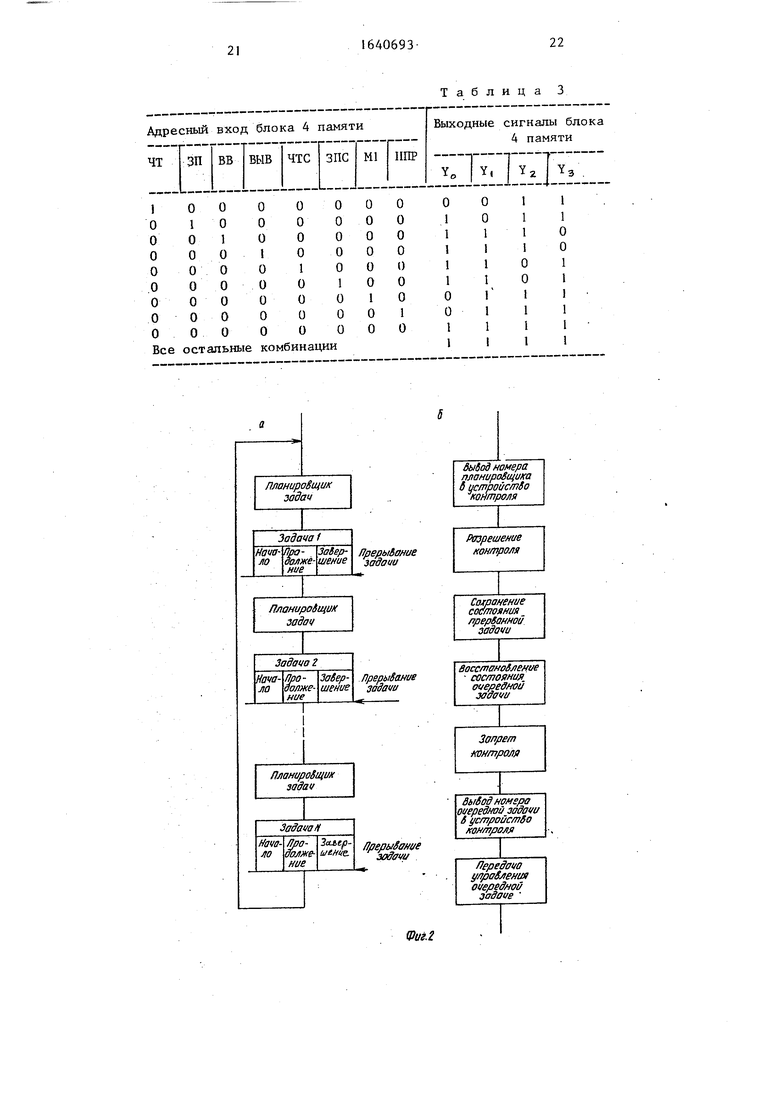

Таблица истинности блока 4 постоянной памяти приведена в

0

Каждый разряд выходного кода блока 4 постоянной памяти соответствует определенному устройству контролируемой микропроцессорной системы (У0 - ПЗК, У - ОЗУ, Уг - стек, У3 - устройства ввода-вывода) Единицы в правой части табЛоЗ соответствуют некорректным, а нули - корректным синтаксичес-1

ким ситуациямо Например, для ПЗУ некорректными входными сигналами являются ЗП, ВВ, ВЫВ, ЧТС, ЗПС„

Для выявления некорректных обраений к устройствам контролируемой ПС необходимо значения выходного коа блока 4 постоянной памяти сопоставить с устройством, к которому осуществляется обращение по адресной шине ю 2 в текущий момент времени Это осуществляется мультиплексором 3

Для обеспечения контроля за корректным выполнением текущей задачи в мультипрограммной МПС используются 15 элементы 12-22 устройства и связи между ними Регистр 16 служит для запоминания номера задачи, подлежащей выполнению 0 Схема 12 сравнения обеспечивает сравнение планируемого и фак- 20 тического номеров выполняемой задачи Триггер 19 и элемент И 13 служат для разрешения и запрета контроля при корректном переходе от одной задачи к другойо Дешифратор 18 выделяет ад- 2 ресные сигналы для обращения к регистру 16 и триггеру 190 Дешифратор 20 декодирует код команды передачи управления очередной задаче на шине 17 данных контролируемой МПС0 Регистр 21 30 сдвига выполняет роль цифрового элемента задержки до окончания выполнения команды передачи управления очередной задачео Элементы И 7 и 14 служат для обеспечения оценки состояния 35 контролируемой системы в момент действия стробирующих сигналов микропроцессора Прием и Выдача о Факт возникновения ошибок в контролируемой МПС фиксируется триггером 9о 40 Устройство работает следующим образом

При нормальной работе контролируемой микропроцессорной системы исполняемые команды синтаксически кор- 45 ректны При этом состояния адресной и управляющей шин системы строго со- ответствуют одно другому„ Блок 1 постоянной памяти устанавливает на управляющих входах мультиплексора 3 код JQ устройства, к которому идет обращение, и выбирается соответствующий информационный вход этого мультиплексора (табл02)0 Одновременно на .адресный вход блока 4 постоянной памяти, с 55 шины 5 управления поступает ожидаемая -комбинация сигналов Y0 - Y3 (табЛоЗ) При корректном обращении на выбранном информационном входе мультиплексора 3 и, следовательно, на его выходе всегда присутствует уровень логического нуля0 В результате этого в момент появления стробирующих сигналов микропроцессора Прием и Выдача элемент И 7 закрыт, что предотвращает формирование сигнала на его выходе При этом триггер

9остается в исходном нулевом состоянии, установленном перед началом работы устройства через вход 11 сброса,.

При исполнении микропроцессорной системой программ в результате сбоя или отказа ее элементов возможно возникновение некорректной ситуации при обращении к какому-либо устройству системЫо К таким ситуациям относятся попытка извлечения команды из зоны оперативной памяти в результате сбоя программного счетчика процессора, попытка записи числа в зону ПЗУ в результате сбоя косвенного адреса или отказа одной из линии адресной шины и т о п о

При возникновении подобной некор- , ректной ситуации работа устройства описывается следующей последовательностью событий Блок 1 постоянной памяти устанавливает на управляющих входах мультиплексора 3 код устройства микропроцессорной системы-, к которому должно производит обращение,) Благодаря этому, среди информационных входов мультиплексора 3 выбирается тот, который связан с соответствующим выходом блока 4 памяти При некорректной ситуации код адресной зоны выбираемого устройства не соответствует комбинации управляющих сигналов на шине 5 управления0 Поэтому на выбранном информационном входе мультиплексора 3 и его выходе всегда присутствует логическая единица (табЛоЗ), и в момент действия стробирующих сигналов микропроцессора Прием или Выдача на выходе элемента И 7 появляется сигнал, свидетельствующий об ошибке Этот сигнал поступает на установочный вход триггера 9, переводя его в единичное состояние В результате этого на выходе

10ошибки устройства появляется активный уровень, свидетельствующий об ошибке, о возникновении отказа или сбоя в контролируемой системе

В рассмотренном.типе некорректных синтаксических ситуаций комбинация управляющих сигналов на шине 5

управления является корректной, а некорректно ее сочетание с адресом на адресной шине 2 системы0 Однако кроме подобных некорректных ситуаций часто в результате отказов или сбоев возникают некорректные синтакстичес- кие ситуации, связанные с непоявлением ожидаемого управляющего сигнала, необходимого для обращения к выб- ранному устройству, что нарушает нормальное функционирование микропроцессорной системы Для обнаружения некорректных ситуаций, связанных с непоявлением ожидаемых управляющих сигна лов, в ячейку блока 4 постоянной памяти по нулевому адресу, соответствующему отсутствию сигналов управления, записаны единичные значения всех выходных сигналов Y0 - Y3 (таблаЗ)0 Б результате этого при непоявлении ожидаемого управляющего сигнала в момент действия стробирующих сигналов микропроцессора Прием или Выдача на адресном входе блока 4 па- мяти устанавливается нулевой код, что обеспечивает появление логической единицы на выходе мультиплексора 3 независимо от состояния его управляющего входа При этом на выходе эле мента И 7 появляется сигнал, переключающий триггер 9 в единичное состояние, что вызывает формирование активного уровня на выходе 10 ошибки уст- ройствао Аналогичным образом уст- ройство работает при появлении любой некорректной комбинации управляющих сигналов (табЛоЗ)о

Активньй уровень на выходе 10 ошибки устанавливается также и при обра- щении в контролируемой системе к неиспользуемой зоне адресного пространства В этом случае на втором выходе блока 1 постоянной памяти появляется уровень логической единицы (), поступающий на вход стробирования мультиплексора 30 Это запрещает работу мультиплексора 3, устанавливая на его выходе уровень логической единицы,, В результате этого элемент И 7 открывается, и стробирующий сигнал Прием или Выдача с выхода элемента ИЛИ 6 в момент очередной оценки состояния системы проходит на установочный вход триггера 9, устанавли- вая его в единичное состояниес

Рассмотренный механизм контроля обнаруживает некорректные обращения к устройствам контролируемой МПС (например, обращение к ПЗУ по шине адреса и одновременное обращение к ОЗУ п шине управления), а также отсутствие ожидаемых обращений к этим устройствам Однако в мультипрограммных МНС возможны некорректные ситуации, связанные с ложным переходом в результате сбоя или отказа элементов системы от одной задачи к другой в пределах одного устройства МПС. Например, если в результате сбоя косвенного адреса происходит ложный переход от памяти данных одной задачи к памяти данных другой задачи, то-механизм контроля не обнаруживает этот факт, так как и в том и в другом случае осуществляется корректное обращение к ОЗУ„ Для обнаружения подобных ситуаций, связанных с ложным переходом от одной задачи к другой в пределах одного устройства МПС, перед передачей управления очередной задач., ь регистр 16 загружается ее номер, а в процессе выполнения этой задачи осуществляется постоянное сравнение этого номера с номером фактически выполняемой задачи, поступающим с третьего выхода блока I постоянной памяти,

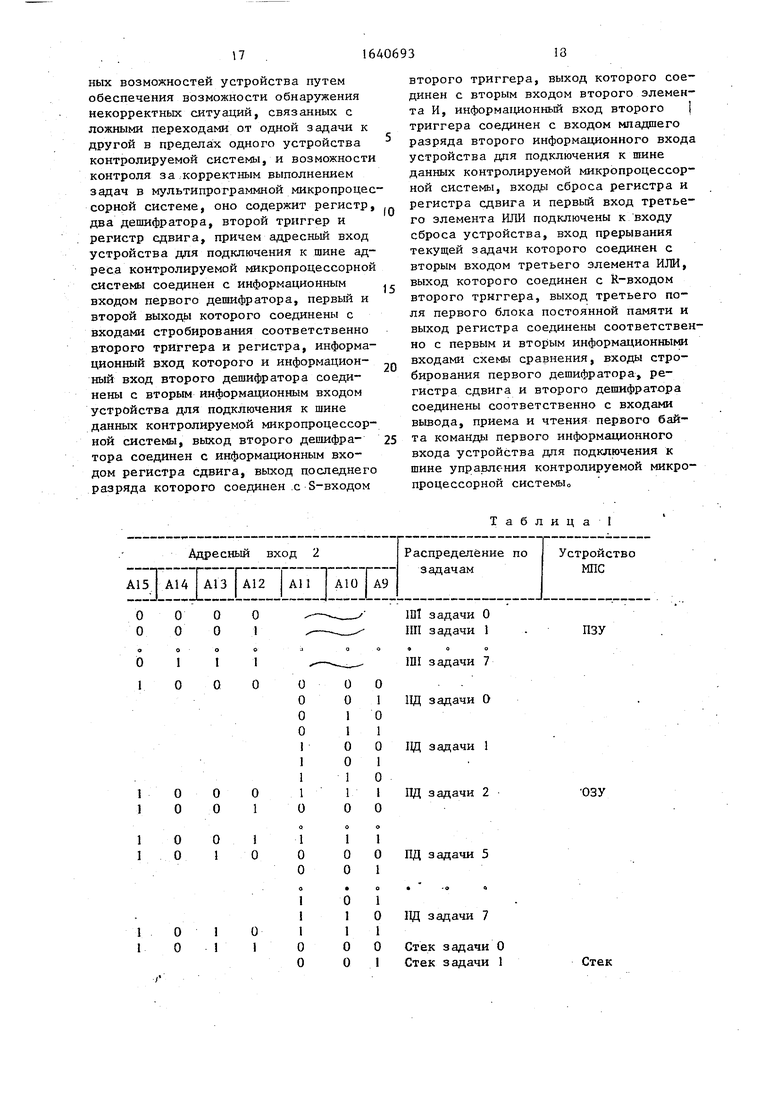

Передача управления очередной задаче в мультипрограммных МПС реализуется с помогаю планировщика задачо Последовательность выполнения задач также выбирается планировщиком задач путем реализации установленной дисциплины приоритетного обслуживания задачо При простейшем циклическом планировании время процессора предоставляется каждой задаче по очереди до достижения естественной точки приостановки В качестве такой точки часто используется окончание выделенного интервала времени для текущей задачио При этом выполнение текущей задачи прерывается по сигналу системного таймера, и управление передается планировщику задач0 Планировщик задач определяет номер очередной задачи, подлежащей выполнению, и передает ей управление,, На фиг02а приведен общий алгоритм функционирования мультипрограммной МПС,, для случая простейшего циклического планирования После обслуживания всех задач управление передается вновь первой задаче и ее решение продолжается с точки приостановки и

Каждая задача в мультипрограммной МПС выполняется независимо от других и имеет свою программную память и память данныхо Поскольку задачи автономны, то у каждой должен быть и свой стек, в котором запоминается содержимое регистров микропроцессора при прерывании текущей задачи Исходя из этого, типичными функциями планировщика задач являются сохранение состояния приостановленной задачи и восстановление состояния очередной задачи с передачей управления ей0 Использование предлагаемого устройства для контроля функционирования мультипрограммной МПС требует от планировщика задач выполнения дополнительных функций по управлению устройством контроля,, На фиго 26 приведена схема ал- горитма планировщика5 работающего с предлагаемым устройством контроля0 Очевидно, что дополнительные функции планировщика задач очень просты и заключаются в загрузке номера очеред- ной задачи в устройство контроля, а также разрешении и запрете контроля при переходе от одной задачи к другой Планировщик задач представляет собой обычную программу, и поэтому для обе- спечения контроля за его функционированием целесообразно считать, что он является одной из задач, реализуемых в мультипрограммной МПС, например задачей с номером 0Q

Рассмотрим процесс работы предлагаемого устройства во взаимодействии с планировщиком задач, начиная с момента прерывания текущей задачи (см0 временные диаграммы на фиг.З) Пре- рывание текущей задачи в простейшем случае осуществляется по сигналу сис темного таймера, поступающего на вход 22 устройства (фиг03( интервал времени Т2)0 При этом программно вы- зывается планировщик задач, а триггер 19 аппаратно устанавливается в 1 нулевое состояние, запрещая контроль за соответствием задач во время перехода от одной задачи к другой,, Hoc- ле очередного вызова планировщик задач реализует алгоритм, изображенный на фиго 26о

Для обеспечения более полного контроля за работой самого планировщика задач в этом алгоритме прежде всего осуществляется загрузка в регистр 16 устройства контроля номера задачи, выполняющей функции планировщика. Для

0

5 0 5

0 5 Q

-

этого на шине адреса, подключенной к входу 2 устройства контроля, устанавливается адрес регистра 16, на шине данных, подключенной к входу 17, формируется код номера планировщика и генерируется сигнал Вывод (при изолированном интерфейсе контролируемой МПС), поступающий на вход стробиро- вания дешифратора 180 В результате этого на втором выходе дешифратора 18 появляется импульс, обеспечивающий запись номера планировщика в регистр 16. После этого, аналогичным образом, осуществляется запись единичного значения в триггер 19, выходным сигналом которого открывается элемент И 13 и разрешается контроль за соответствием задач в мультипрограммной МПС (фиГоЗ, интервал ТЗ)„ Посла этого планировщик задач переходит к сохранению состояния прерванной задачи и восстановлению состояния очередной задачио

Однако такой алгоритм допустим лишь в МПС, построенных на базе микропроцессоров, имеющих команду пря- мого вывода непосредственных данных, в которой и адрес порта и выводимые данные указываются в команде„ Если это условие не выполняетсяt то планировщик задач должен прежде всего

сохранять состояние прерванной задачи и лишь затем загружать свой номер в регистр 16 и разрешать контроль0Это обусловлено тем, что при отсутствии команд прямого вывода непосредственных данных операция записи числа в порт вывода осуществляется с использованием какого-либо регистра микропроцессора, все из которых могут быть заняты прерванной задачей„

После восстановления состояния очередной задачи планировщик задач должен передать ей управление0 Однако для обеспечения контроля за корректным выполнением этой задачи необходимо прежде всего загрузить в регистр 16 ее номеро Для предотвращения факта обнаружения ложной ошибки в процессе перехода от одной задачи к другой необходимо перед загрузкой номера очередной задачи запретить контроль за соответствием задач путем установки в нулевое состояние триггера 190 Б противном случае ошибка обязательно обнаруживаетсяt так как в регистр 16 записывается Номер очередной задачи, а в течение некоторого

времени еще продолжается работа планировщика, являющегося другой задачей Поэтому после восстановления со- стояния очередной задачи планировщик задач в соответствии с алгоритмом (фиг02б) и аналогично рассмотренному записывает в триггер 19 нулевое значение, запрещая контроль, а в регистр 16 - номер очередной задачи, подготавливая предлагаемое устройство к контролю за корректным выполнением этой задачи

Передача управления очередной задаче реализуется в планировщике задач путем выполнения команды возврата подпрограммы, обеспечивающей загрузку программного счетчика микропроцессора из стека данной задачи по восстановленному значению ее указателя стека Например, дня микропроцессоров КР580ВМ80А и К1821ВМ85А такой командой является команда КЕТ0 После выполнения этой команды и перехода к очередной задаче триггер 19 должен быть установлен в единичное состояние, что разрешает контроль за соответствием задач Однако программное управление триггером 19 в этом случае нецелесообразно и невозможно, так как при повторном вызове очередной задачи она может продолжаться с произвольной точки Это исключает возможность включения в прикладные задачи функций управления триггером 19 Поэтому в предлагаемом устройстве установка триггера 19 в единичное со- стояние при передаче управления очередной задаче реализуется аппаратным образом Для этого дешифратор 20, стробируемый сигналом Ml, обнаруживает на шине.17 данных контролируемой МПС код команды возврата из подпрограммы- (например, RET), что свидетельствует о начале передачи управ- ления очередной задаче. При этом активируется выход дешифратора 20, и младший разряд регистра 21 сдвига устанавливается в единичное состояние (фиг03, интервал Т4), фиксируя начало передачи управления

Так как триггер 19 должен быть установлен в единичное состояние после фактической передачи управления очередной задаче, тсе0 после полного вы

полнения команды возврата из подпро- траммы,то регистр 21 сдвиг а выполняет функции цифрового элемента задержки на количество машинных циклов, необходиJQ

(5 2Q 25 30 Q 5

5

0

5

мых для завершения этой команды,, В каждом машинном цикле выполнения команды возврата микропроцессор генерирует сигнал Прием, вызывающий формирование сигнала чтения информации из стекла и сдвигающий единичное значение в очередной разряд регистра 21 сдвига. В результате этого в последнем машинном цикле единичное значение появляется в последнем разряде регистра 21, что обеспечивает установку триггера 19 в единичное значение непосредственно перед началом выполнения очередной задачи,,

Если в процессе выполнения очередной задачи контролируемая МПС функционирует нормально (фиг03, интервал Т5), то на ее шине адреса постоянно присутствуют адреса, закрепленные за этой задачей (табл.2)0 Благодаря этому, на третьем выходе блока 1 постоянной памяти постоянно находится текущий номер исполняемой задачи, совпадающий с номером, загруженным в регистр 16 перед передачей управления этой задаче Схема 12 сравнения определяет равенство этих номеров и формирует на своем выходе нулевой уровень, запирающий элементы И 13 и 14 Это блокирует канал формирования ошибки несоответствия задач в мультипрограммной МПСо

В дальнейшем работа предлагаемого устройства при отсутствии ошибок совершенно идентична описанному„ Вновь возникает прерывание текущей задачи (, интервал Тб), вызывается планировщик задач и т0д

При первоначальном запуске контролируемой МПС сигнал системного сброса, поступающий на вход 11, обеспечивает исходное состояние предлагаемого устройства (фигоЗ, интервал Т1) После этого управление также передается планировщику задач. При первом вызове планировщик задач обеспечивает первоначальную инициализацию всех задач (на фиг02б не показано) При этом он реализует алгоритм, который может быть получен из алгоритма путем замены блока Сохранение состояния прерванной задачи блоком Первоначальная инициализация всех задач В процессе первоначальной инициализации задаются начальные значения указателей стеков всех задач, а также состояния всех регистров и программного счетчика

микропроцессора0 После этого планировщик задач передает управление первой задаче и т„д, При первоначальном вызове планировщика задач предлагаемое устройство работает совершенно идентично описанному, обеспечивая контроль за функционированием мультипрограммной МПС и в этом глучае0

Если же в процессе выполнения очередной задачи в результате отказа или сбоя элементов системы осуществляется ложный переход от одной задачи к другой в пределах одного устройства контролируемой МПС, то на ее шине адреса появляется адрес, не соответствующий исполняемой задаче. При этом на третьем выходе блока 1 постоянной памяти появляется текущий номер, указывающий задачу, к которой произошло некорректное обращение. Этот номер отличается от номера, хранящегося в регистре 163 что фиксируется схемой 12 сравнения,, На ее выходе повляется единичный уровеньо При разрешенном контроле за соответствием задач это обеспечивает формирование единичного уровня на выходе элемента И 13 и отпирание элемента И 140 В момент очередной оценки состояния в контролируемой МПС стробирующий импульс с выхода элемента ИЛИ b проходит на выход элемента И 14 и через элемент ИЛИ 8 на установочный вход триггера 90 При этом триггер 9 устанавливается в единичное состояние, фиксируя ошибку в контролируемой МПС (фиг.З, интервал T7)s что обеспечивает активирование выхода ошибки 10 устройства,.

Выход 10 ошибки устройства может соединяться с входом запроса прерывания микропроцессорной системы„ В этом случае при возникновении ошибки выполнение текущей программы прерывается, и система переходит к выполнению программы обработки прерывания по ошибке. Программа обработки прерывания по ошибке может предусматривать восстановление процесса, нарушенного сбоем, может иметь диагностический характер (выявление причин ошибки) или, в простейшем случае, обеспечивать останов нарушенного процесса.

Таким образом, устройство обеспечивает обнаружение некорректных ситуаций, связанных с ложными переходами от одной задачи к другой в пределах одного устройства (ПЗУ, ОЗУ,

стека или УВВ) контролируемой системы, и возможность контроля за корректным выполнением задач в мультипрограммной МПСо Все это определяет более широкие функциональные возможности устройства и существенно расширяет возможности его применения для контроля функционирования современных вычислительных системе

5

0

5

0

5

0

5

0

5

Формула изобретения

Устройство для контроля микропроцессорной системы, содержащее два блока постоянной памяти, мультиплексор, три элемента И, три элемента ИЛИ, схему сравнения, первый триггер, причем адресный вход первого блока памяти соединен с входом адреса устройства для подключения к шине адреса контролируемой микропроцессорной системы, выход первого поля первого блока постоянной памяти соединен с адресным входом мультиплексора, информационный вход которого соединен с выходом второго блока постоянной памяти, адресный вход которого соединен с первым информационным входом устройства для подключения к шине управления контролируемой микропроцессорной системы, вход стробирования мультиплексора соединен с выходом второго поля первого блока постоянной памяти, входы первого элемента ИЛИ соединены с входами приема и выдачи первого информационного входа устройства для подключения к шине управления контролируемой микропроцессорной системы, выход первого элемента ИЛИ соединен с первым входом первого элемента И, второй вход которого соединен с выходом мультиплексора, выход первого элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен c S-вхо- дом первого триггера, выход которого является выходом ошибки устройства, R-вход первого триггера соединен с входом сброса устройства, выход схемы сравнения соединен с первым входом второго элемента И, выход которого соединен с первым входом- третьего элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, выход третьего элемента И соединен с вторым входом второго элемента ИЛИ, отлич аю щееся тем, что, с целью расширения функциональ-

ных возможностей устройства путем обеспечения возможности обнаружения некорректных ситуаций, связанных с ложными переходами от одной задачи к другой в пределах одного устройства контролируемой системы, и возможности контроля за корректным выполнением задач в мультипрограммной микропроцессорной системе, оно содержит регистр, два дешифратора, второй триггер и регистр сдвига, причем адресный вход устройства для подключения к шине адреса контролируемой микропроцессорной системы соединен с информационным входом первого дешифратора, первый и второй выходы которого соединены с входами стробирован-ия соответственно второго триггера и регистра, информационный вход которого и информационный вход второго дешифратора соединены с вторым информационным входом устройства для подключения к шине данных контролируемой микропроцессорной системы, выход второго дешифратора соединен с информационным входом регистра сдвига, выход последнего разряда которого соединен с S-входом

0

5

второго триггера, выход которого соединен с вторым входом второго элемента И, информационный вход второго триггера соединен с входом младшего разряда второго информационного входа устройства для подключения к шине данных контролируемой микропроцессорной системы, входы сброса регистра и регистра сдвига и первый вход третьего элемента ИЛИ подключены к входу сброса устройства, вход прерывания текущей задачи которого соединен с вторым входом третьего элемента ИЛИ, выход которого соединен с R-входом второго триггера, выход третьего поля первого блока постоянной памяти и выход регистра соединены соответственно с первым и вторым информационными входами схемы сравнения, входы стро- бирования первого дешифратора, регистра сдвига и второго дешифратора соединены соответственно с входами вывода, приема и чтения первого байта команды первого информационного входа устройства для подключения к шине управления контролируемой микропроцессорной системы

Таблица 1

19

ооо

1 0 1 1 1 О 0111 1000

О 0 1

ООС

1111

0000

0111

1000

О 0 1

1 О

1 О

оо о

1 1

1111111

1 1

1640693

20 Продолжение табл. 1

Оо о

О 1 О

1 1 1

О О

о о

о о

000 О 0 1

1 1 Г

000

00 1

оао

11 1

Планировщик задач

Задача 1

Начало

Продолжение

3aiep- шение

Планиродщих задач

Задача 2

Начало

Продолжение

Завершение

ПланироВщик sadav

ЗадаиаН

Начало

Продолжение

Задер- ii/tHve.

Таблица 3

Прерывание задачи

Прерыйание задам

Прерывание 3o3avu

| Устройство для синтаксического контроля программ микропроцессорной системы | 1985 |

|

SU1260960A1 |

Авторы

Даты

1991-04-07—Публикация

1989-03-20—Подача