1i/

Изобретение относится к вычислительной технике и может найти приме- . нет-те при построении устройств управления универсальных цифровых вычислительных машин и микропроцессоров.

Целью изобретения является сокращение емкости блока памяти за счет обеспечения возможности организации вложенных друг в друга подпрограмм.

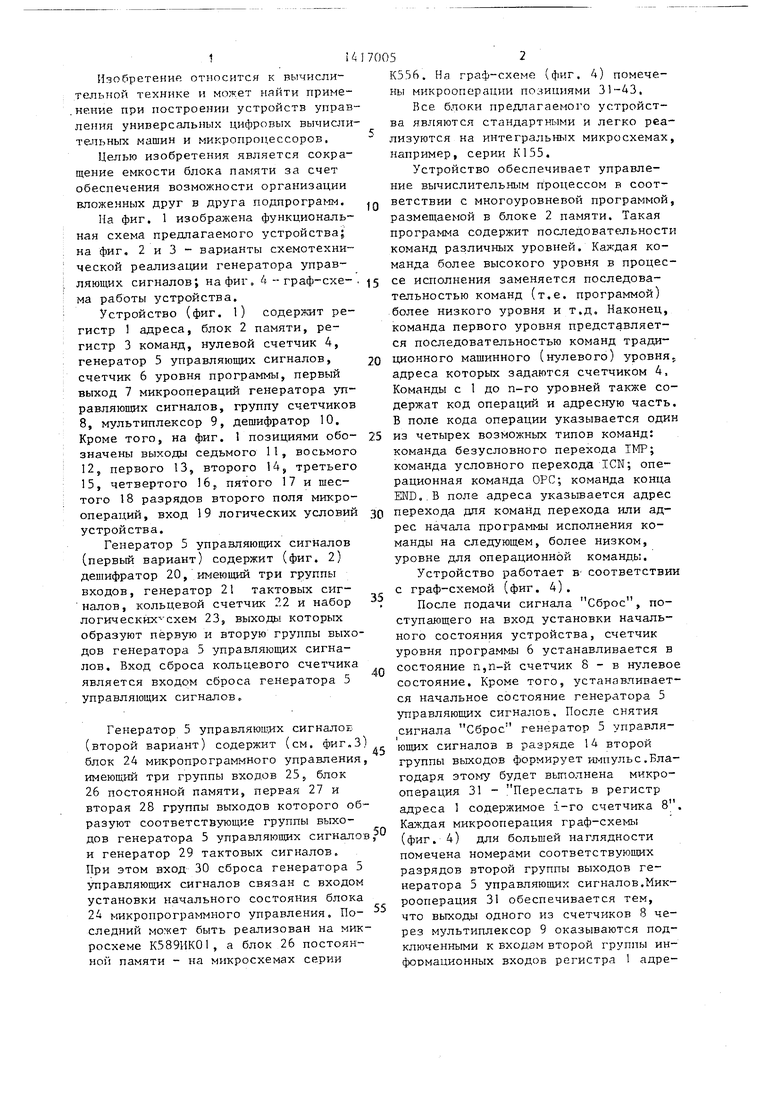

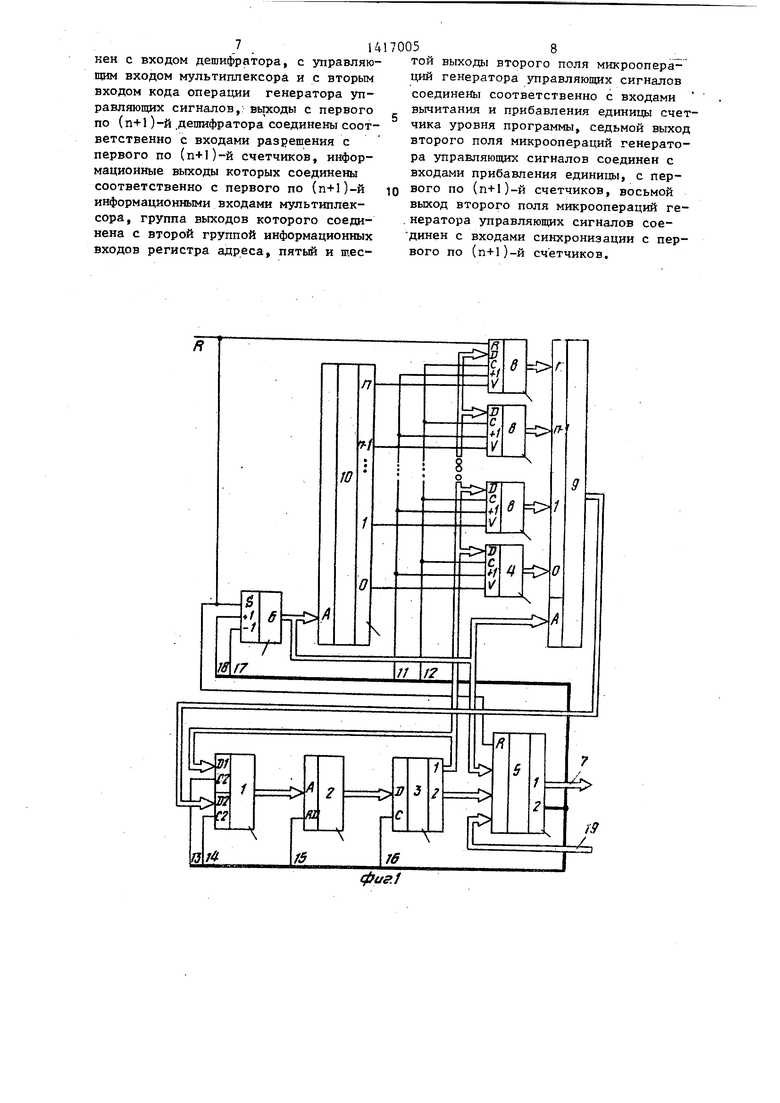

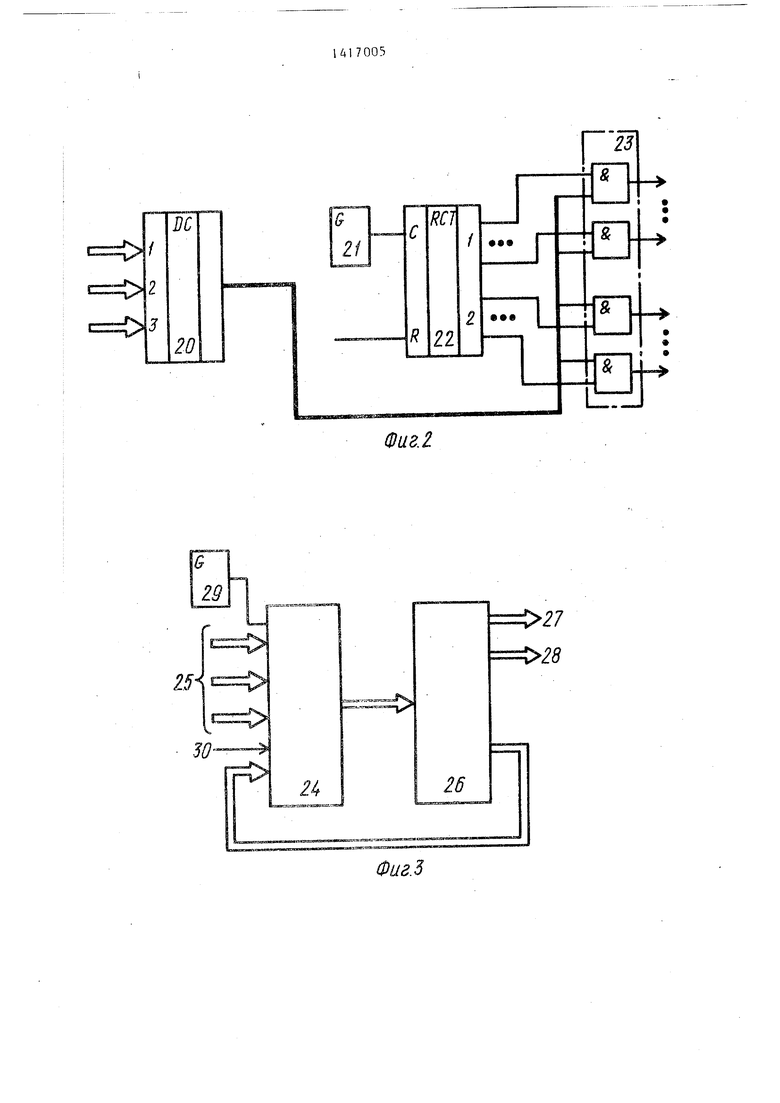

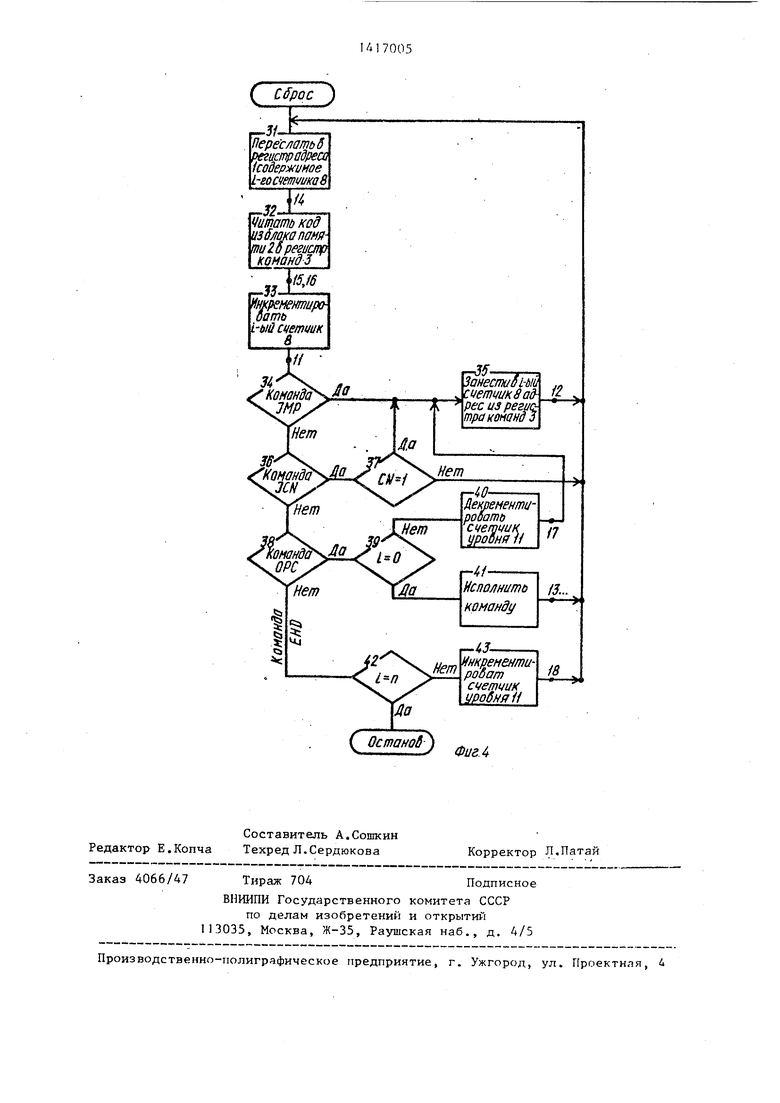

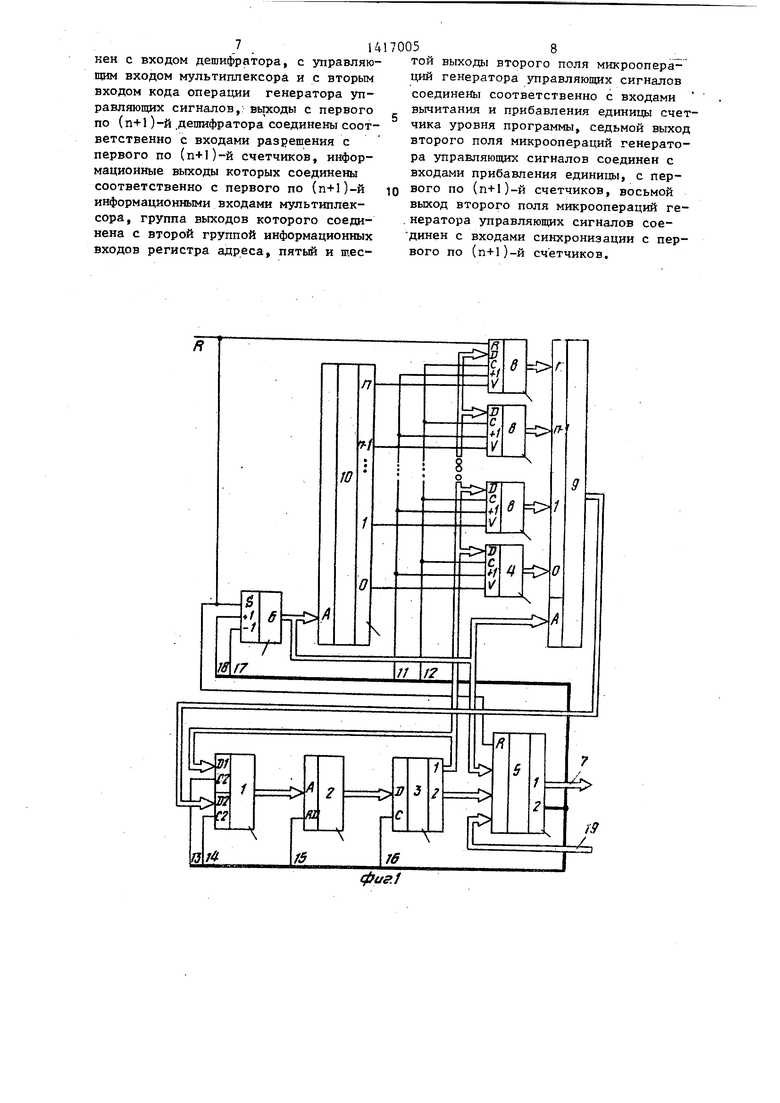

На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг, 2 и 3 - варианты схемотехнической реализации генератора управляющих сигналов; на фиг, 4 -- граф-схе- ма работы устройства.

Устройство (фиг. 1) содержит регистр 1 адреса, блок 2 памяти, регистр 3 команд, нулевой счетчик 4, генератор 5 управляющих сигналов, счетчик 6 уровня программы, первый выход 7 микроопераций генератора управляющих сигналов, группу счетчиков 8, мультиплексор 9, дешифратор 10. Кроме того, на фиг. 1 позициями обозначены выходы седьмого 11, восьмого 12, первого 13, второго Н, третьего 15, четвертого 16;, пятого 17 и шестого 18 разрядов второго поля микроопераций, вход 19 логических условий устройства.

Генератор 5 управляющих сигналов (первый вариант) содержит (фиг, 2) дешифратор 20, имеющий три группы входов, генератор 21 тактовых сиг- налов, кольцевой счетчик 22 и набор логическнх- схем 23, выходы которых образуют первую и вторую группы выходов генератора 5 управляющих сигналов. Вход сброса кольцевого счетчика является входом сброса генератора 5 управляюш;их сигналов,,

Генератор 5 управляющих сигналов (второй вариант) содержит (см, фиг.З блок 24 микропрограммного управления имеющий три группы входов 25, блок 26 постоянной памяти, первая 27 и вторая 28 группы выходов которого образуют соответствующие группы выходов генератора 5 управляющих сигнало и генератор 29 тактовых сигналов. При этом вход 30 сброса генератора 5 управляющих сигналов связан с входом установки начального состояния блока 24 микропрограммного управления. Последний может быть реализован на микросхеме К589ИК01, а блок 26 постоянной памяти - на микросхемах серии

0

5

0

5

0052

К556. На граф-схеме (фиг, 4) помечены микрооперации позициями 31-43,

Все блоки предлагаемого устройства являются стандартными и легко реализуются на интегральных микросхемах, например, серии К155,

Устройство обеспечивает управление вычислительным п роцессом в соответствии с многоуровневой программой, размещаемой в блоке 2 памяти. Такая программа содержит последовательности команд различных уровней. Каждая команда более высокого уровня в процессе исполнения заменяется последовательностью команд (т,е. программой) более низкого уровня и т,д. Наконец, команда первого уровня представляется последовательностью команд традиционного машинного (нулевого) уровняр адреса которых задаются счетчиком 4, Команды с 1 до п-го уровней также содержат код операций и адресную часть, В поле кода операции указывается один из четырех возможных типов команд: команда безусловного перехода IMP; команда условного перехода ICW; операционная команда ОРС; команда конца ЖВ..В поле адреса указывается адрес перехода для команд перехода или адрес начала программы исполнения команды на следующем, более низком, уровне для операционной команд,ы.

Устройство работает В соответствии с граф-схемой (фиг, 4),

После подачи сигнала Сброс, поступающего на вход установки начального состояния устройства, счетчик уровня программы 6 устанавливается в состояние п,п-й счетчик 8 - в нулевое состояние. Кроме того, устанавливается начальное состояние генератора 5 управляющих сигналов. После снятия сигнала Сброс генератор 5 управля- юш}1х сигналов в разряде 14 второй группы выходов формирует импульс.Благодаря этому будет выполнена микрооперация 31 - Переслать в регистр адреса 1 содержимое i-ro счетчика 8. „ Каждая микрооперация граф-схемы (фиг, 4) для большей наглядности помечена номерами соответствуюших разрядов второй группы выходов генератора 5 управляющих сигналов.Мик- г рооперация 31 обеспечивается тем,

что выходы одного из счетчиков 8 через мультиплексор 9 оказываются подключенными к входам второй группы информационных входов регистра 1 адре0

5

0

5

314

са, причем номер i счетчика 8 определяется состоянием счетчика уровня программы И. Следовательно, в начальный момент в регистр 1 адреса будет записано начальное состояние п-го счетчика 8. Затем генератор управляющих сигналов сдедает следующий шаг: 32 - Читать код из блока 2 памяти в регистр 3 команд. При этом генерируются импульсы в 15 и 16 разряды генератора 5 управляющих сигналов. Первый поступает на вход стро- бирования блока 2 памяти, а второй - на вход разрешения записи регистра 3 команд. Этим обеспечивается выборка кода команды из блока 2 памяти и запись его в регистр 3 команд. При первом проходе после сброса, в регистре команд будет записана первая команда п-го уровня. Затем выполняется микрооперация 33 - Инкрементиро- вать i-ый счетчик 8. Это действие обеспечивается импульсом в разряде 11 второй группы выходов генератора 5 управляющих сигналов, который поступает на входы инкрементирования всех счетчиков 8 и счетчика 4 команд Однако дешифратор 10 обеспечивает выборку только одного счетчика, номер которого соответствует текущему состоянию счетчика 6 уровня программы (счетчик 4 выбран при нулевом состоянии счетчика 6 уровня программы). При первом проходе после сброса выбирается п-й счетчик 8, поэтому только он будет инкрементирован. Дальнейшие операции зависят от типа команды. Вначале производится проверка 34 - Команда IMP. Эта проверка реализуется логикой генератора 5 управляющих сигналов путем сравнения кода операции команды, поступающего с второй группы выходов регистра 3 команд на вторую группу вводов генератора 5 управляющих сигналов с известным кодом команды IMP. Если сравнение дает положительный результат, то вьшолня- ется микрооперация 35 - Занести в i-й счетчик 8 адрес из регистра 3 команд. Для вьшолнения этого действия генератор 5 управляющих сигналов формирует импульс в разряде 12 второй группы выходов, которыйглоступа- ет на входы разрешения записи всех счетчиков В и счетчика 4. Однако за счет действия входов выборки, управляемых с выходов дешифратора 10, запись будет реализована только в

счетчике 8, соответствующем текущему уровгао. Этими действиями адрес перехода из адресной части команды через первую группу выходов регистра 3 команд будет передан в счетчик 8 текущего уровня, чем и обеспечивается предписанный командой безусловный переход. После этого генератор 5 управляющих сигналов обеспечивает повторение микроопераций, начиная с блока 31. Если же код операции не совпадает с кодом команды IMP, то выполняется проверка 36 - Команда ICN.

Она выполняется аналогично микрооперации 34. Если результат проверки положительный, то выполняется проверка условия 37 - . Эта проверка также реализуется логикой генератора

5 управляющих сигналов путем сравнения заданного кода условия CN с истинным значением, поступающем по входам 19 сигналов-условий. Если же ре- зультат сравнения положительный, то

вьтолняется переход (реализуется микрооперация 35), иначе, происходит повторение микроопераций, .начиная с блока 31 (т.е. выборка очередной команды).

Если код операции не совпадае с кодом команды ICN, то выполняется микрооперация 37 - Команда ОРС. Эта микрооперация выполняется аналогично 34 и 36. Если команда действительно операционная, то генератор 5 управлящих сигналов вьтолняёт микрооперацию 39 - . Эта микрооперация вьтолняется логикой генератора 5 управляющих сигналов путем сравнения

кода текущего уровня, поступающего с выходов счетчика 6 уровня программы на входы второй группы входов кода операции генератора 5 управляющих сигналов, с нулевым кодом. Если результат

сравнения отрицательный, т.е. уровень программы не нулевой, реализуется понижение уровня программы. Это беспечивается микрооперацией 40 - Декрементировать счетчик 6 уровня

рограммы. При этом генератор 5 упавляющих сигналов формирует импульс а линии 17 второй группы выходов, оступающий на вход декрементирова- ия счетчика 6 уровня программы. По

55

, еле этого выполняется описанная микрооперация 35, .благодаря которой адресная часть операционной командь заносится в программный счетчик подчиненного уровня, чем подготавливается

очередной цикл управления Если же результат сравнения положительный, т.е. , и очередная команда адресована счетчиком А команд то она подлежит выполнению. Это обеспечивается блоком 41 - Исполнить команду При этом генератор 5 управляю- nuix сигналов генерирует здесь импуль в разряде 13 второй группы выходов, чем обеспечивается запись адреса из адресной части регистра 3 команд через первую группу выходов в регистр адреса через первую группу входов.

По окончании этой последовательности происходит возврат к 1-му программному уровню, очередная команда которого вызывает следующую последовательно.сть команд нулевого уровня и т.д. до тех пор пока, не будет обнаружена команда END 1-го уровня. Здесь происходит

обращение к 2-му уровню и т.д. Процесс продолжается до тех пор, пока не будет полностью исполнена вся последовательность команд п-го уровня.

Таким образом,, предлагаемое устройство обеспечивает управление вычис

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2034329C1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для тестового диагностирования и управления | 1984 |

|

SU1256024A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1621027A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Программный управляющий модуль с контролем | 1990 |

|

SU1758634A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении устройств управления универсальных вычислительных машин и микропроцессоров. Целью изобретения является сокращение емкости блока памяти за счет обеспечения возможности организации вложенных друг в друга подпрограмм. Устройство содержит регистр адреса, блок памяти, регистр команд, группу счетчиков, генератор управляющих сиг-налов, счетчик уровня программы, дешифратор, мультиплексор. Введение мультиплексора, счетчика уровня программы, дешифратора и группы счетчиков обеспечивает достижение цели. 4 ил.

Этим подготавливается выборка из бло- 15 лительным процессом в соответствии с

ка 2 памяти операнда, адресованного командой. Кроме того, генератор 5 управляющих сигналов на первой груп пе выходов формирует серию управляющих импульсов, поступающих в операци онное устройство через линии выхода управляющих сигналов устройства. Все это обеспечивает исполнение команды нулевого уровня. Затем возобновляется очередной цикл управления Если же проверки 34, 36 и 38 дали отрица- тельный результат, значит в регистре 3 команд зафиксирована команда END Тогда выполняется проверка 42 - 1 п. Если результат отрицательный, то это означает, что закончилась последовательность команд i-ro уровня и необходимо перейти на более высокий программный уровень, В этом случае вьшолняется микрокоманда 43 - Инкрементировать счетчик 6 уровня программы. Генератор 5 управляющих сигналов в этом случае генерирует импульс в разряде 18, который поступает на вход инкрементирования счетчика 6 уровня программы и увеличивает его содержимое на единицу,, обеспечивая переход устройства на более высокий уровень. Если же проверка 42 дает положительный результат, то это означает, что закончена программа наивысшего уровня п, В этом случае в генераторе 5 управляющих сигналов происходит блокирование всех выходных импульсов и устройство переходит в состояние Останов „ Рассматривая циклическую граф-схему работы устройства (фиг, 4)5 легко убедиться в том, что запущенная с уровня п программа последовательно понижает свой gg мультиплексор, причем вход начальной

уровень, пока не дойдет до уровня О, где начнет исполняться последова- тельность команд, обеспечивающая вы полнение одной команды 1-го уровня.

установки устройства соединен с вхо- дом установки в О п-го счетчика и с входом установки в 1 счетчика уровня программы, выход которого соедиП Уровневой программой. Формула изобретения

Устройство управления, содержащее регистр адреса, блок памяти, регистр команд, генератор управляющих сигналов, причем выходы поля адреса регистра команд соединены с первой группой информационных входов регистра адреса, выход которого соединен с входом адреса блока памяти, выход которого соединен с информационным входом регистра команд, выход поля кода

операции которого соединен с первым входом кода операции генератора управляющих сигналов, вход логических условий устройства соединен с входом логических условий генератора управ- ляющих сигналов, выход первого поля микроопераций которого является выходом микроопераций устройства, выходы с первого по четвертый второго поля микроопераций генератора управляющих

сигналов соединены соответственно с первым и вторым входами синхронизации регистра адреса, с входом разращения блока памяти, с входом синхронизации регистра команд, вход начальной установки устройства соединен с входом сброса генератора управляющих сигналов, отличающееся тем, что, с целью сокращения емкости блока памяти за счет обеспечения возможности Организации п вложенных од - на в другую подпрограмм, дополнительно содержит п+1 счетчиков, где п - количество вложенных подпрограмм, счетчик уровня программы, дешифратор.

установки устройства соединен с вхо- . дом установки в О п-го счетчика и с входом установки в 1 счетчика уровня программы, выход которого соеди7i41

кен с входом дешифратора, с управляющим входом мультиплексора и с вторым входом кода операции генератора управляющих сигналов,: вьрсоды с первого по (п+1 )-й .дешифратора соединены соответственно с входами разрешения с первого по (п+1)-й счетчиков, информационные выходы которых соединены соответственно с первого по (п+1)-й информационными входами мультиплексора, группа выходов которого соединена с второй группой информационных входов регистра адреса, пятый и тес70058

той выходы второго ПОЛЯ микроопераций генератора управляющих сигналов соединены соответственно с входами вычитания и прибавления единицы счетчика уровня программы, седьмой выход второго поля микроопераций генератора управляющих сигналов соединен с входами прибавления единицы, с вого по (п+1)-й счетчиков, восьмой выход второго поля микроопераций ге- ,нератора управляющих сигналов сое- динен с входами синхронизации с первого по (п+1)-й счетчиков.

фиг.1

Г

23

&

21

RCl

R

n

2

0

Фиг. 2

Фиг.З

| Устройство управления | 1982 |

|

SU1042018A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микропроцессорные системы | |||

| М., 1981, с | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

Авторы

Даты

1988-08-15—Публикация

1986-04-22—Подача