Js V

Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля хода программ | 1988 |

|

SU1649551A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Устройство для контроля микропроцессорной системы | 1988 |

|

SU1566332A1 |

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля кода программ | 1988 |

|

SU1564632A1 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1460722A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

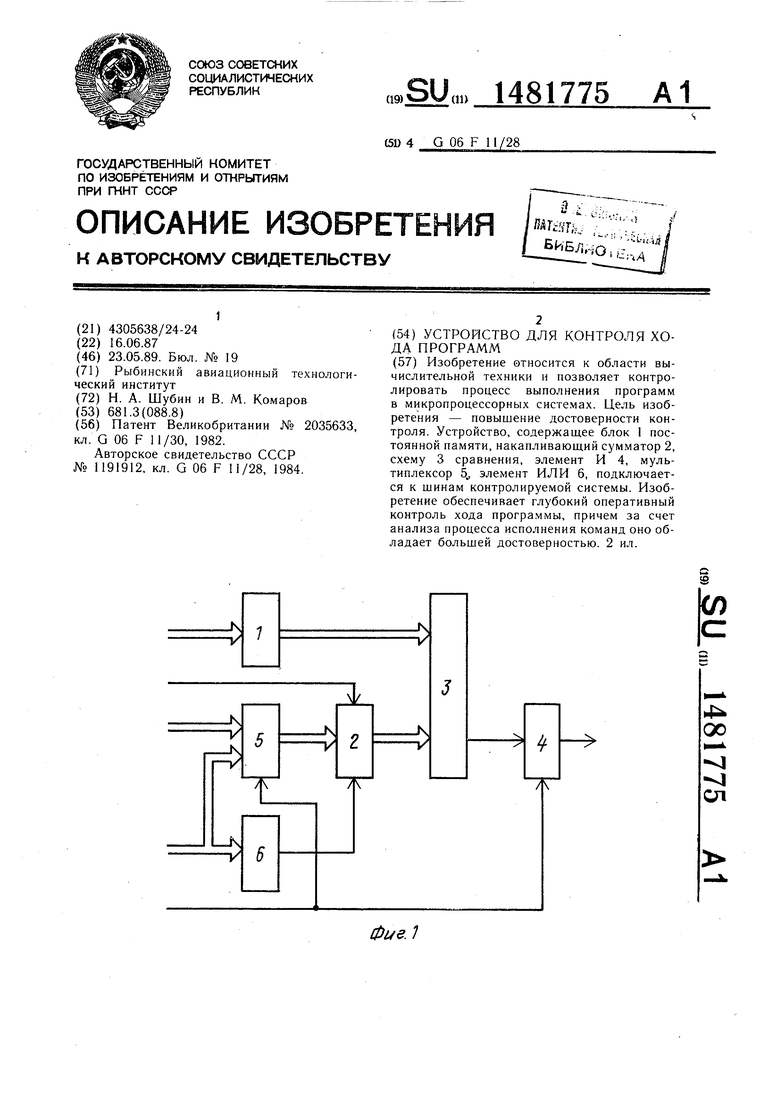

Изобретение относится к области вычислительной техники и позволяет контролировать процесс выполнения программ в микропроцессорных системах. Цель изобретения - повышение достоверности контроля. Устройство, содержащее блок 1 постоянной памяти, накапливающий сумматор 2, схему 3 сравнения, элемент И 4, мультиплексор 5, элемент ИЛИ 6, подключается к шинам контролируемой системы. Изобретение обеспечивает глубокий оперативный контроль хода программы, причем за счет анализа процесса исполнения команд оно обладает большей достоверностью. 2 ил.

Т

1

/

/

3

00

1 ел

Фиг. 7

Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных систем, нечувствительных к сбоям программы,

Цель изобретения - повышение дос- товерности контроля хода программ.

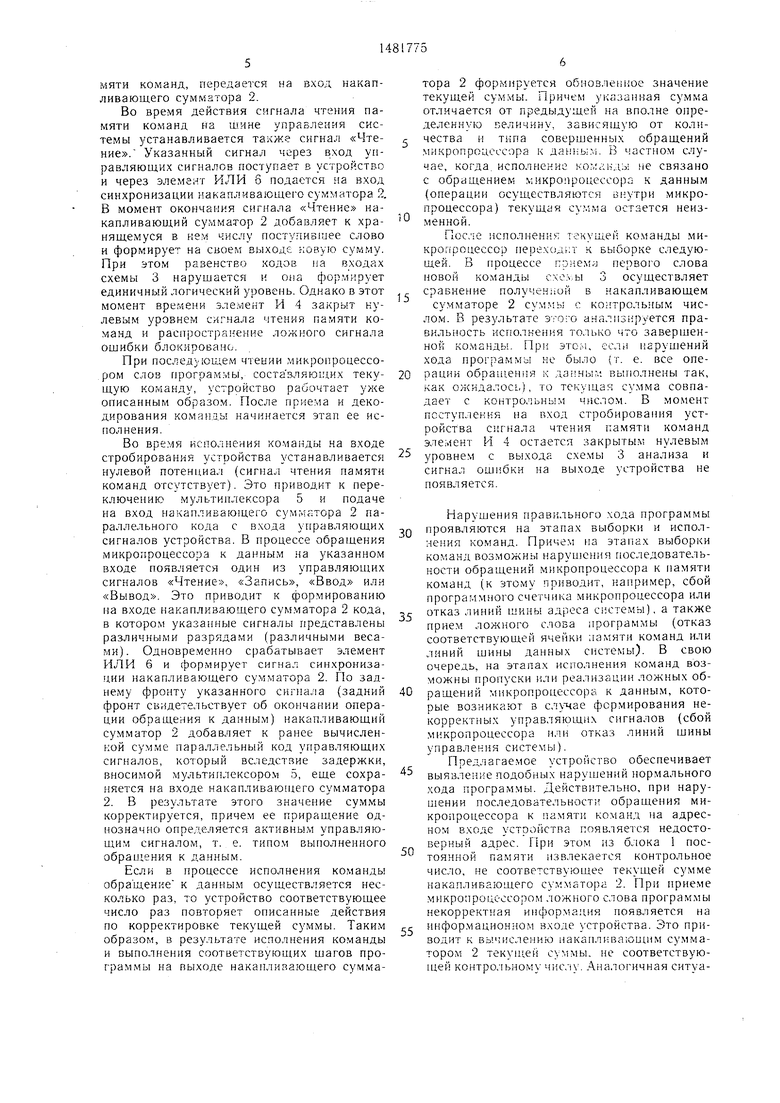

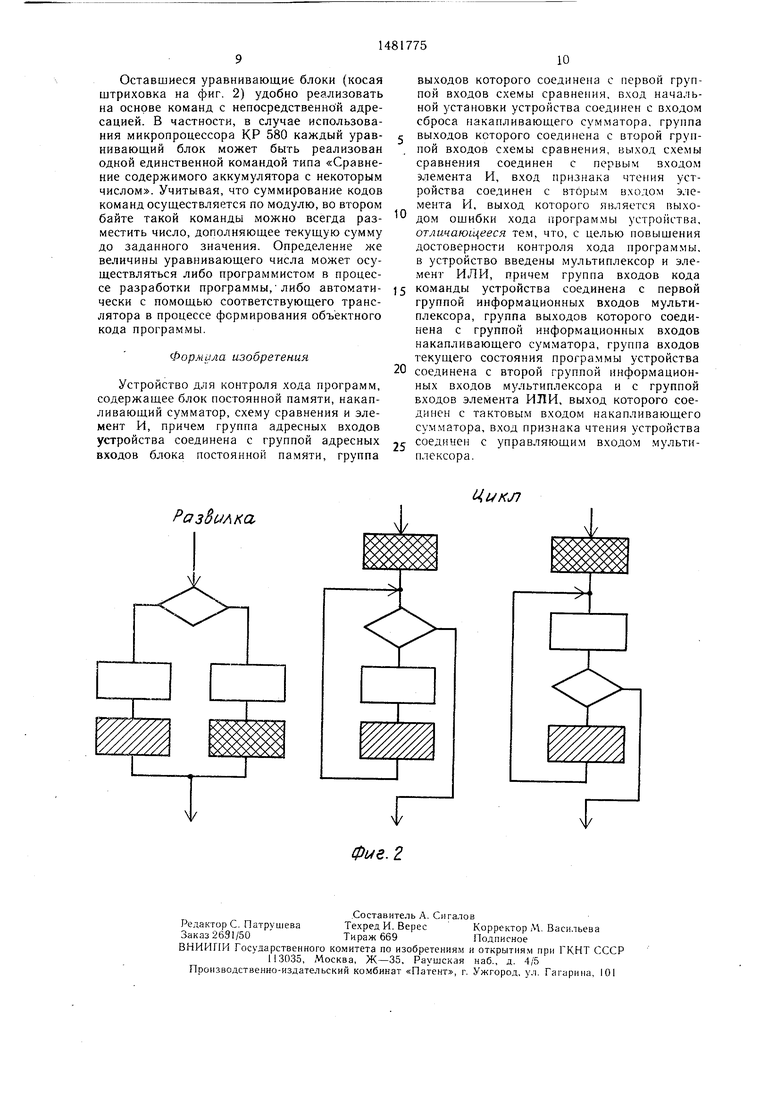

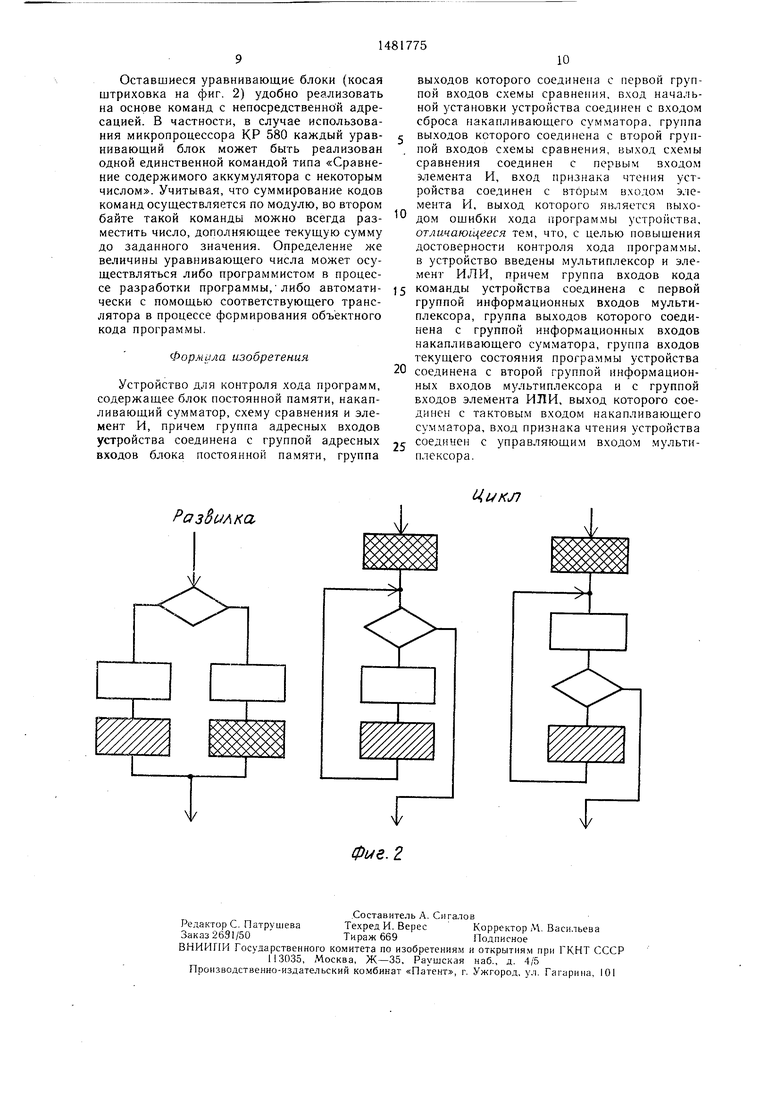

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - базовые структуры программирования контролируемой системы.

Устройство для контроля программ содержит блок 1 постоянной памяти и накапливающий сумматор 2, схему 3 сравнения и элемент И 4, мультиплексор 5 и элемент ИЛИ 6.

Устройство работает следующим образом.

Пусть необходимо контролировать ход программы некоторой микропроцессорной системы. Программа представляет собой совокупность команд и хранится в памяти команд. В качестве последней обычно выступа- ет постоянное запоминающее устройство. Каждая команда занимает от одной до нескольких соседних ячеек памяти и информационно характеризуется массивом слов (байтов)-.

Процесс воспроизведения программы заключается в последовательном (шаг за шагом) извлечения из памяти команд слов программы, их декодировании и исполнении принятых команд. При этом извлечение каждого очередного слова программы сопро- вождается тем, что на шине адреса системы устанавливается адрес указанного слова. Затем генерируется сигнал чтения памяти команд, по которому адресуемое слово поступает на шину данных системы и принимается микропроцессором. После извлечения всех слов, составляющих текущую команду, и их декодирования микропроцессор исполняет принятую команду.

В процессе исполнения команды микропроцессор может обращаться к памяти и портам ввода-вывода системы, реализуя предписанные командой операции приема или выдачи данных. При этом на шине адреса системы устанавливается соответствующий адрес данных. Затем на шине управления генерируется сигнал, однозначно идентифицирующий выполняемую операцию. Такими сигналами являются «Чтение или «Запись при обращении к памяти и «Ввод и «Вывод при обращении к портам.

Для реализации своих функций предлагаемое устройство подключается к микро- процессорной системе таким образом, что его адресный вход соединяется с шиной адреса системы, входы кода команды устройства соединены с шиной данных, входы текущего состояния программы устройства соединены с шиной управления. Нарушение хода программы фиксируется путем генерации устройством на своем выходе сигнала ошибки.

5

5

0

0

Q

Q 5

5

0

5

Для обеспечения контроля в предлагаемом устройстве каждому адресу (каждой точке) программы ставится в соответствие некоторое контрольное число. Указанное число является суммой (например, по модулю 256) всех слоя программы, извлекаемых из памяти команд системы к моменту прохождения программы через соответствующую точку, и всех кодов, появляющихся на шине управления системы в процессе исполнения команд, предшествовавших текущей. При этом контрольные числа вычисляются заранее и еще до работы устройства размещаются в блоке 1 постоянной памяти.

В процессе реализации программы на каждом ее шаге вычисляются текущие суммы, которые в определенные моменты времени сравниваются с контрольными числами. В случае корректных вычислений текущие суммы всегда совпадают с контрольными числами и ошибка не фиксируется. При нарушении же хода программы возникает несоответствие между текущими суммами и контрольными числами, что приводит- к появлению на выходе устройства сигнала ошибки.

Рассмотрим работу предлагаемого устройства в процессе реализации некоторой команды. На этапе выборки команды на адресный вход устройства и, следовательно, на вход блока 1 постоянной памяти подается адрес, по которому в микропроцессорной системе из памяти команд извлекается очередное слово программы. Это обеспечивает появление на выходе блока 1 постоянной памяти контрольного числа, соответствующего данной точке программы.

Пусть на рассматриваемый момент времени в накапливающем сумматоре 2 накопитель некоторая сумма, характеризующая работу программы за предыдущее время. Указанная сумма и контрольное число с выхода блока 1 поступают на схему 3. Схема 3 сравнивает поступившие числа и в случае их равенства формирует на своем выходе нулевой логический уровень, свидетельствующий о корректности выполняемых вычислений. С выхода схемы 3 указанный сигнал поступает на вход элемента И 4.

Оценка корректности реализуемых программой вычислений осуществляется в момент появления сигнала чтения памяти команд. При корректных вычислениях элемент И 4 в момент появления этого сигнала закрыт нулевым уровнем с выхода схемы 3 и сигнал ошибки на выходе устройства не формируется.

Одновременно с сигналом чтения памяти команд на информационный вход устройства подается текущее слово программы. Код указанного слова через мультиплексор 5, управляемый тем же сигналом чтения памяти команд, передается на вход накапливающего сумматора 2.

Во время действия сигнала чтения памяти команд на шине управления системы устанавливается также сигнал «Чтение. Указанный сигнал через вход управляющих сигналов поступает в устройство и через элемент ИЛИ 6 подается на вход синхронизации накапливающего сумматора 2. В момент окончания сигнала «Чтение накапливающий сумматор 2 добавляет к хранящемуся в кем числу поступившее слово и формируе на своем выходе сумму. При этом равенство ходов на входах схемы 3 нарушается и она формирует единичный логический уровень. Однако в этот момент времени элемент И 4 закрыт кулевым уровнем сигнала чтения памяти команд и распространение ложного сигнала ошибки блокировано.

При последующем чтении микропроцессором слов программы, составляющих текущую команду, устройство раоочтает уже описанным образом. После приема и декодирования команды начинается этап ее исполнения.

Во время исполнения команды на входе опробирования устройства устанавливается нулевой потенциал (сигнал чтения памяти команд отсутствует). Это приводит к переключению мультиплексора 5 и подаче на вход накапливающего сумматора 2 параллельного кода с входа управляющих сигналов устройства. В процессе обращения микропроцессора к данным на указанном входе появляется один из управляющих сигналов «Чтение. «Запись, «Ввод или «Вывод. Это приводит к формированию па входе накапливающего сумматора 2 кода, в котором указанные сигналы представлены различными разрядами (различными весами). Одновременно срабатывает элемент ИЛИ 6 и формирует сигнал синхронизации накапливающего сумматора 2. По заднему фронту указанного сигнала (задний фронт сБзде-ельствует об окончании операции обращения к данным) накапливающий сумматор 2 добавляет к ранее вычисленной сумме параллельный код управляющих сигналов, который вследствие задержки, вносимой мультиплексором 5, еще сохраняется на входе накапливающего сумматора 2. В результате этого значение суммы корректируется, причем ее приращение однозначно определяется активным управляющим сигналом, т. е. типом выполненного обращения к данным.

Если в процессе исполнения команды обращение к данным осуществляется несколько раз. то устройство соответствующее число раз повторяет описанные действия по корректировке текущей суммы. Таким образом, в результате исполнения команды и выполнения соответствующих шагов программы на выходе накапливающего сумма0

5

0

5

0

5

0

5

0

5

тора 2 формируется обновленное значение текущей суммы. Причем указанная сумма отличается от предыдущей на вполне определенную величину, зависящую от количества и типа совершенных обращений микропроцессора к данные. В частном случае, когда исполнение ьог.мкд.:,; не связано с обращением микропроцессора к данным (операции осуществляются внутри микропроцессора) текущая сумма остается неизменной.

После исполнен тонущей команды микропроцессор переход:.1 к выборке следующей. В процессе приема первого слова новой команды 3 осуществляет сравнение полученной в накапливающем сумматоре 2 суммы с контрольным числом. R результате эого анализируется правильность исполнения только что завершенной команды. При этс.ч, сели нарушений хода программы не было (г. е. все опе- пации обращения к данным выполнены так, как ожидалось), то теклщая сумма совпадает с контрольным числом. В момент поступления на вход стробирования устройства сигнала чтения памяти команд элемент И 4 остается закрытым нулевым уровнем с выхода схемы 3 анализа и сигнал ошибки на выходе устройства не появляется.

Нарушения правильного хода программы проявляются на этапах выборки и исполнения команд. Причем па этапах выборки команд возможны нарушения последовательности обращений микропроцессора к памяти команд (к этому приводит, например, сбой программного счетчика микропроцессора или отказ линий шины адреса системы), а также прием ложного слова программы (отказ соответствующей ячейки памяти команд или линий шины данных системы). В свою очередь, на этапах исполнения команд возможны пропуски или реализации ложных обращений микропроцессора к данным, которые возникают в случае формирования некорректных управляющих сигналов (сбой микропроцессора или отказ линий шины управления системы).

Предлагаемое устройство обеспечивает выявление подобных нарушений нормального хода программы. Действительно, при нарушении последовательности обращения микропроцессора к памяти команд на адресном входе устройства появляется недостоверный адрес. При этом из блока 1 постоянной памяти извлекается контрольное число, не соответствующее текущей сумме накапливающего сумматора 2. При приеме микропроцессором ложного слова программы некорректная информация появляется на информационном входе устройства. Это приводит к вычислению накапливающим сумматором 2 текущей . не соответствующей контрольному чнсл Аналогичная ситуация складывается и в результате пропуска или реализации ложных обращений микропроцессора к данным. При этом, несоответствие текущей суммы контрольному числу возникает вследствие поступления некорректной информации на вход управляющих сигналов устройства.

Во всех описанных случаях схема 3 фиксирует неравенство кодов и генерирует устойчивый уровень логической елиницы, который поступает на вход элемента 14. В момент чтения микропроцессором памяти команд элемент И4 открывается, в результате чего на выходе устройства формируется сигнал ошибки. Полученный сигнал может быть использован в контролируемой системе для запуска, например, по прерыванию, программы устранения ошибки. В процессе обработки прерывания микропроцессор системы обеспечивает подачу на вход сброса устройства сигнала начальной установки. Указанный сигнал поступает в накапливающий сумматор 2 и производит обнуление (очистку) текущей суммы. После того, как сигнал начальной установки снимается, устройство вновь готово к работе. При этом запускаемая программа в первой своей точке должна иметь нулевое контрольное число. Аналогичным образом происходит очистка накапливающего сумматора 2 и в процессе начального запуска (сброса контролируемой системы.

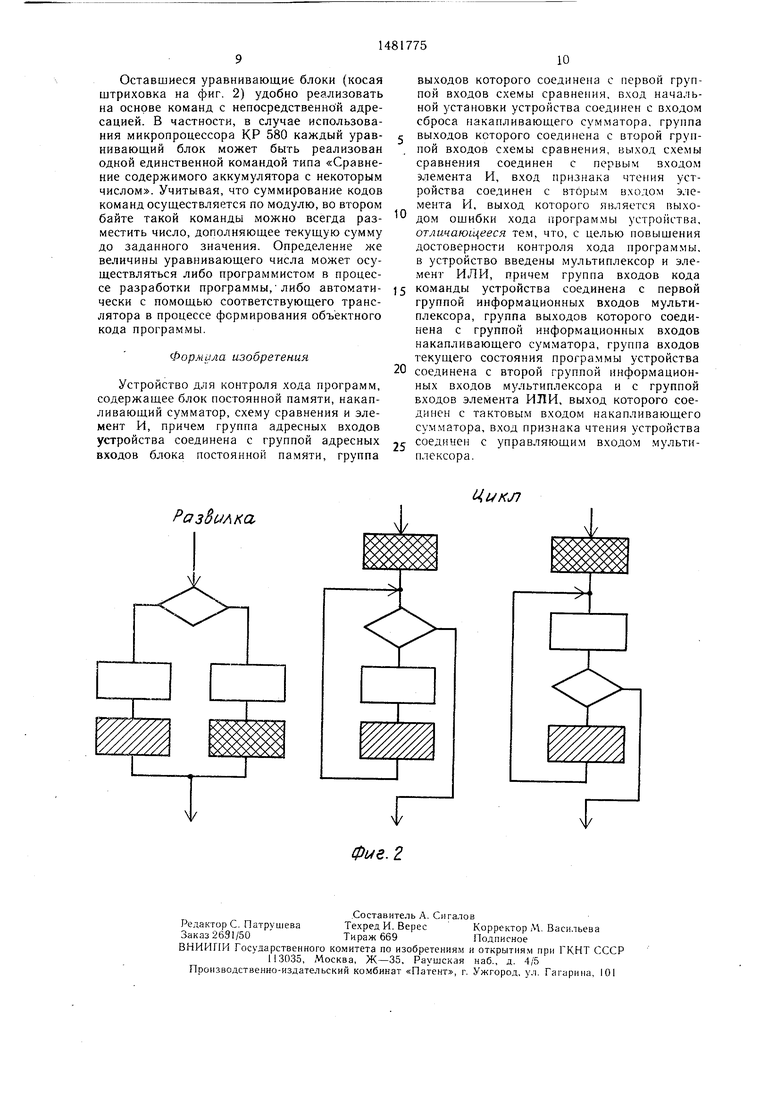

Таким образом, устройство позволяет контролировать ход программы в микропроцессорной системе с момента начального ее запуска, а также после устранения ошибок. Однако использование предлагаемого устройства налагает некоторые ограничения на программирование микропроцессорной системы. Без учета этих ограничений в предложенном устройстве обеспечивается контроль лишь линейных участков программы. Линейный участок программы при широко распространенном в настоящее время структурном подходе к программированию называется базовой структурой «Следование. Однако этой структуры недостаточно, чтобы представить даже самые простые практические программы. Теория показывает, что логическая структура любой сколь угодно сложной программы, может быть выражена комбинацией трех базовых структур: к уже упомянутой структуре «Следование добавляются структуры «Развилка и «Цикл (фиг. 2). При этом последняя может иметь две разновидности. Внутри базовых структур «Развилка и «Цикл осуществляется ветвление вычислительного процесса с последующим объединением ветвей. Объединение ветвей программы осуществляет обращение по одному и тому же адресу после прохода ветвей программы. Суммы кодов команд, находящихся в различных ветвях, в общем

случае не совпадают. В результате этого при объединении ветвей программы без принятия дополнительных мер предложенное устройство зафиксирует ошибку программы,

хотя таковой и нет. Для исключения этого являения необходимо искусственно выравнивать текущие суммы программы перед каждым объединением ветвей. Это легко обеспечивается путем размещения перед каждой точкой объединения ветвей дополнительных команд (уравнивающих блоков), не имеющих функционального значения с точки зрения процесса решения задачи, реализуемой микропроцессорной системой. Уравнивающие блоки изображены на фиг. 2 заштрихованными прямоугольниками, причем их различная штриховка подчеркивает различное значение уравнивающих чисел в различных ветвях программы

В простейшем случае уравнивание текущих сумм осуществляться до нулево® го значения. При этом вход в каждую точку слияния ветвей прогораммы происходит с нулевым значением текущей, суммы, т. е. нулевым состоянием накапливающего сумматора 2. Наиболее просто обнуление

5 текущих сумм может быть реализовано путем подачи на вход сброса устройства соответствующего сигнала в момент исполнения программой уравнивающего блока. При подключении устройства к системе, построенной на базе микропроцессора КР 580

0 такое «директивное уравнивание реализуется программным блоком, состоящим из двух команд «Запрещение прерывания и «Разрешение прерывания. В процессе исполнения этих команд на выходе INTE микропроцессора появляется импульс, кото5 рый поступает на вход сброса устройства и осуществляет обнуление текущей суммы. Использование «директивного уравнения снижает достоверность контроля предлагаемого устройства. Это связано с тем, что часть ложных переходов программы не обнаружена, поскольку в результате такого уравнивания возникающие после сбоя некорректные текущие суммы могут принимать нулевые (корректные) значения еще до момента фиксации ошибки на вы5 ходе устройства.

Для устранения указанного недостатка необходимо применять естественное уравнивание путем суммирования кодов команд уравнивающих блоков (вход сброса устройства не возбуждается). В качестве кон0 трольных сумм точек слияния ветвей программы в этом случае рационально принимать не нулевые, а такие суммы, которые получаются при естественном прохождении программой одной из сходящихся ветвей. Это дает возможность исключить из соот5 ветствующих ветвей уравнивающие блоки. В частности, из базовых структур (фиг. 2) исключаются блоки, заштрихованные крест- накрест.

0

Оставшиеся уравнивающие блоки (косая штриховка на фиг. 2) удобно реализовать на основе команд с непосредственной адресацией. В частности, в случае использования микропроцессора КР 580 каждый уравнивающий блок может быть реализован одной единственной командой типа «Сравнение содержимого аккумулятора с некоторым числом. Учитывая, что суммирование кодов команд осуществляется по модулю, во втором байте такой команды можно всегда разместить число, дополняющее текущую сумму до заданного значения. Определение же величины уравнивающего числа может осуществляться либо программистом в процессе разработки программы,1 либо автоматически с помощью соответствующего транслятора в процессе формирования объектного кода программы.

Формула изобретения

Устройство для контроля хода программ, содержащее блок постоянной памяти, накапливающий сумматор, схему сравнения и элемент И, причем группа адресных входов устройства соединена с группой адресных входов блока постоянной памяти, группа

Раз&илка

/

0

выходов которого соединена с первой группой входов схемы сравнения, вход начальной установки устройства соединен с входом сброса накапливающего сумматора, группа выходов которого соединена с второй группой входов схемы сравнения, выход схемы сравнения соединен с первым входом элемента И, вход признака чтения устройства соединен с вторым входом элемента И, выход которого является выходом ошибки хода программы устройства, отличающееся тем, что, с целью повышения достоверности контроля хода программы, в устройство введены мультиплексор и элемент ИЛИ, причем группа входов кода

5 команды устройства соединена с первой группой информационных входов мультиплексора, группа выходов которого соединена с группой информационных входов накапливающего сумматора, группа входов текущего состояния программы устройства

0 соединена с второй группой информационных входов мультиплексора и с группой входов элемента ИЛИ, выход которого соединен с тактовым входом накапливающего сумматора, вход признака чтения устройства соединен с управляющим входом мультиплексора.

5

Цикл

| ЗАКЛЕПОЧНОЕ СОЕДИНЕНИЕ | 1989 |

|

RU2035633C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-23—Публикация

1987-06-16—Подача