Изобретение относится к вычислительной технике и может найти применение при построении быстродействующих универсальных ЭВМ, работающих в двоично-десятичной системе счисления.

Известны операционные блоки [1] Двухбитный операционный блок содержит дешифратор микрокоманд, одиннадцать регистров сверхоперативного ОЗУ (СОЗУ), первый и второй мультиплексоры, арифметико-логическое устройство (АЛУ), регистр адреса памяти, регистр накопитель, первый выходной буфер, второй выходной буфер, причем входы М1 и М0, операционного блока подключены к первому информационному входу первого мультиплексора, информационный выход которого подключен к входам АЛУ, первые информационные выходы которого подключены к информационным входам регистра адреса памяти и через первый выходной буфер к выводам А1, А0 операционного блока, информационные выходы СОЗУ подключены к второму информационному входу первого мультиплексора, входы I1 и I0, К1 и К0 блока подключены соответственно к первому и третьему информационным входам второго мультиплексора, информационные выходы которого подключены к вторым информационным входам АЛУ, вторые информационные выходы которого подключены к информационным входам накапливающего регистра, информационные выходы которого подключены к третьим информационным входам первого мультиплексора, вторым информационным входам второго мультиплексора, информационным входам СОЗУ и через второй выходной буфер к выходам D1, D0 операционного блока, входы дешифратора микрокоманд соединены с входами F0-F6 операционного блока, а выходы с входами управления первого и второго мультиплексоров и адресными входами СОЗУ.

Известный операционный блок имеет невысокое быстродействие при выполнении двоично-десятичных операций, обусловленное необходимостью десятичной коррекции результата. Особенно это сказывается при реализации операций, более сложных, чем сложение, например умножения.

Из известных операционных блоков наиболее близким к заявляемому является операционный блок [2] содержащий запоминающий узел, с первого по четвертый регистры, первый и второй мультиплексоры, причем с первого по шестой входы синхронизации блока подключены соответственно к входу синхронизации первого регистра, входу синхронизации второго регистра, первому и второму входам синхронизации третьего регистра, первому и второму входам синхронизации четвертого регистра, третий информационный вход блока соединен с первым информационным входом второго мультиплексора, первый инфор- мационный вход блока соединен с информационным входом первого регистра и с вторым информационным входом четвертого регистра, выход которого соединен с вторым информационным входом второго мультиплексора, первая группа входов кода операции блока соединена с группой адресных входов запоминающего узла, первый информационный выход которого соединен с первым информационным входом третьего регистра и с информационным входом второго регистра, выход которого соединен с первым входом первого мультиплексора, вход переноса блока соединен с первым адресным входом запоминающего узла, второй информационный выход которого является выходом переноса блока, выход первого регистра соединен с вторым информационным входом первого мультиплексора, выход которого соединен с вторым адресным входом запоминающего узла, вход разрешения чтения которого соединен с входом строба блока, второй информационный вход блока соединен с вторым информационным входом третьего регистра и с первым информационным входом четвертого регистра, выход третьего регистра соединен с третьим информационным входом второго мультиплексора, выход которого соединен с третьим адресным входом запоминающего узла и с информационным выходом блока, управляющие входы первого и второго мультиплексоров объединены и подключены к второй группе входов кода операции блока.

Известный операционный блок имеет невысокое быстродействие при выполнении десятичных операций, обусловленное последовательной работой запоминающих узлов операционных блоков при выполнении операции сложения и необходимостью выборки результатов операции умножения за несколько микрокоманд.

Для повышения быстродействия в операционный блок, содержащий запоминающий узел, первый, второй мультиплексоры, первый, второй, третий, четвертый регистры, причем с первого по шестой входы синхронизации блока подключены cоответcт- венно к входам cинхронизации первого регистра, второго регистра, первому и второму входам синхронизации третьего регистра, первому и второму входам синхронизации четвертого регистра, первый информационный вход блока соединен с информационным входом первого регистра и вторым информационным входом четвертого регистра, второй информационный вход блока соединен с вторым информационным входом третьего регистра и первым информационным входом четвертого регистра, третий информационный вход блока соединен с первым информационным входом второго мультиплексора, первая группа входов кода операции блока соединена с первой группой адресных входов запоминающего узла, вторая группа входов кода операции блока подключена к входам управления первого и второго мультиплексоров, вход чтения блока соединен с входом разрешения чтения запоминающего узла, второй информационный выход которого соединен с информационным входом второго регистра, информационный выход которого подключен к первому информационному входу первого мультиплексора, информационный выход которого связан с второй группой адресных входов запоминающего узла, информационный выход первого регистра соединен с вторым информационным входом первого мультиплексора, информационный выход третьего регистра связан с третьим информационным входом второго мультиплексора, информационный выход четвертого регистра связан с вторым информационным входом второго мультиплексора, информационный выход которого является информационным выходом блока и связан с третьей группой адресных входов запоминающего узла, дополнительно введены третий мультиплексор и пятый регистр, вход синхронизации которого подключен к второму входу синхронизации блока, первый, второй, и третий, четвертый информационные выходы запоминающего узла соединены соответственно с первым и вторым информационными входами третьего мультиплексора, управляющий вход которого соединен с входом переноса операционного блока, первый информационный выход третьего мультиплексора является выходом переноса операционного блока, а второй выход связан с первым информационным входом третьего регистра, четвертый информационный выход запоминающего узла связан с информационным входом пятого регистра, информационный выход которого связан с третьим информационным входом первого мультиплексора.

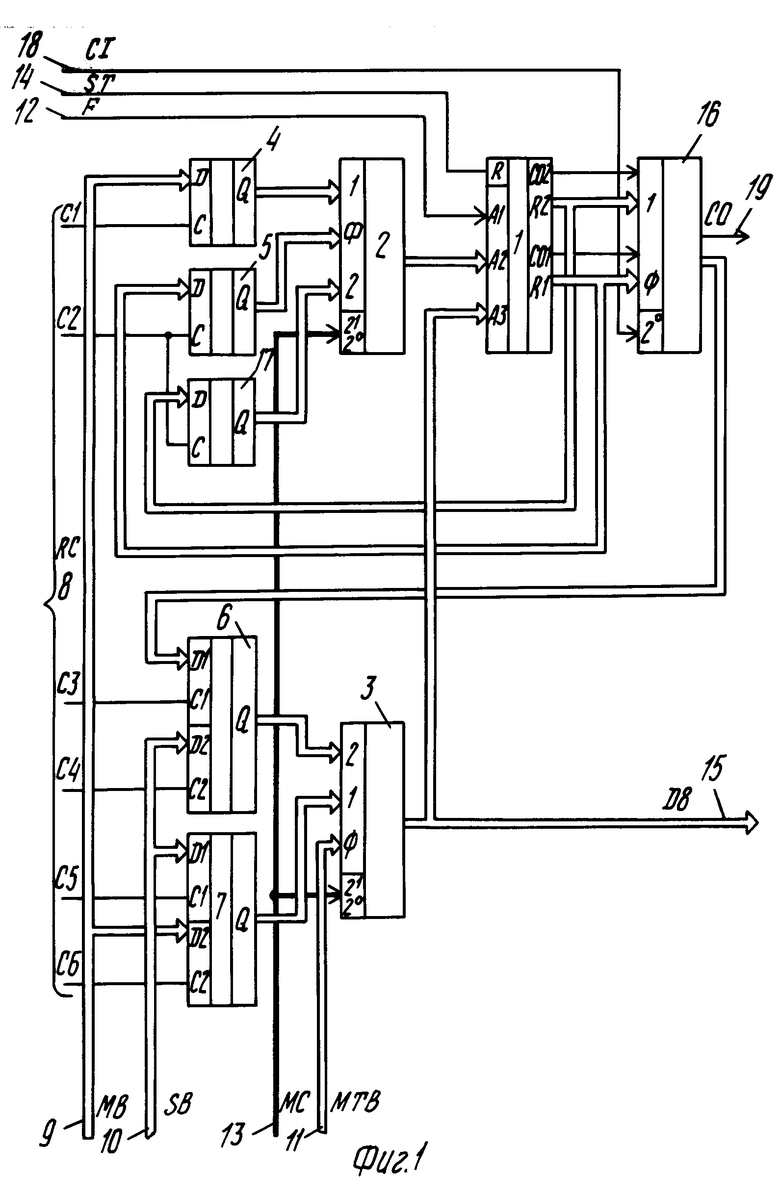

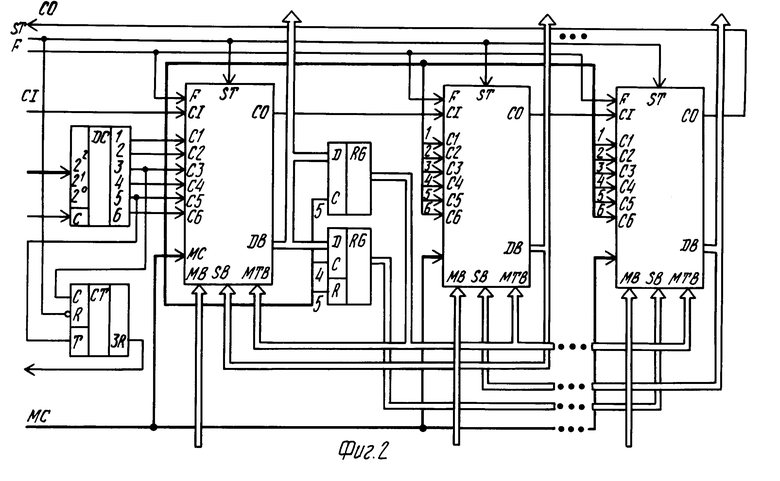

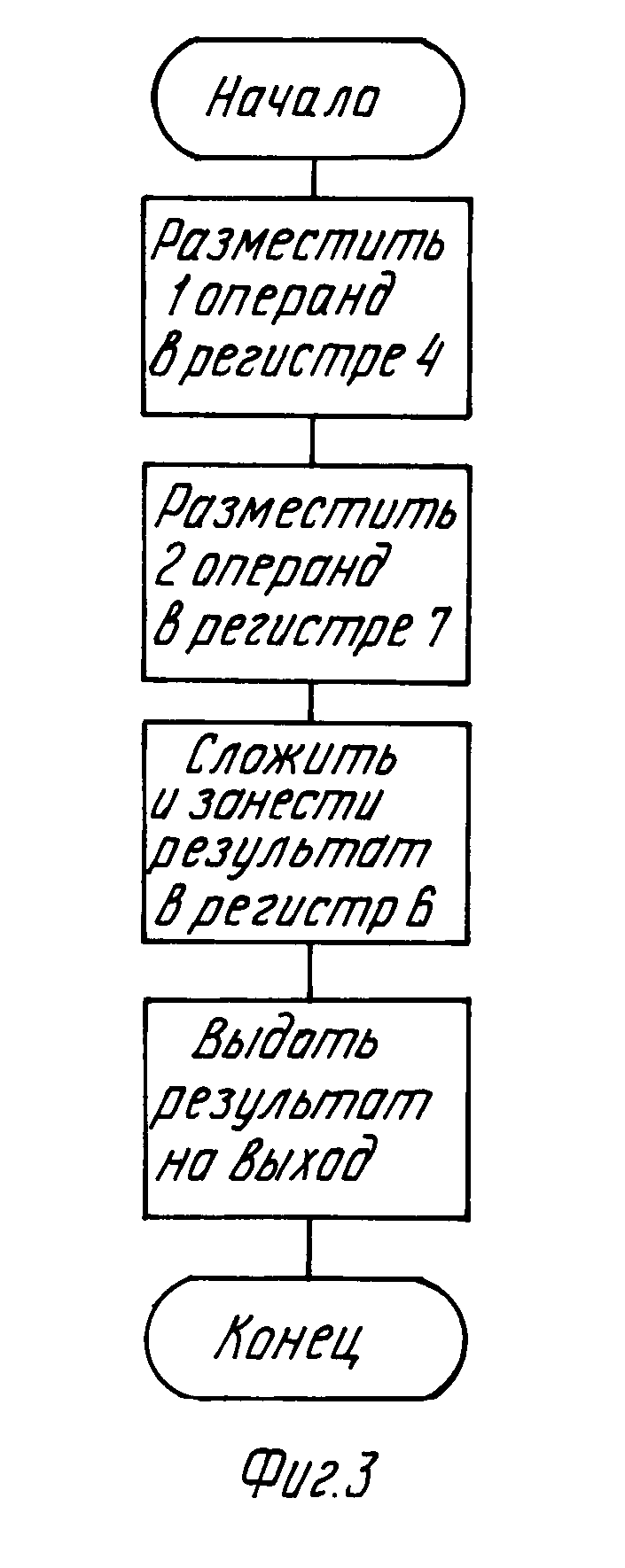

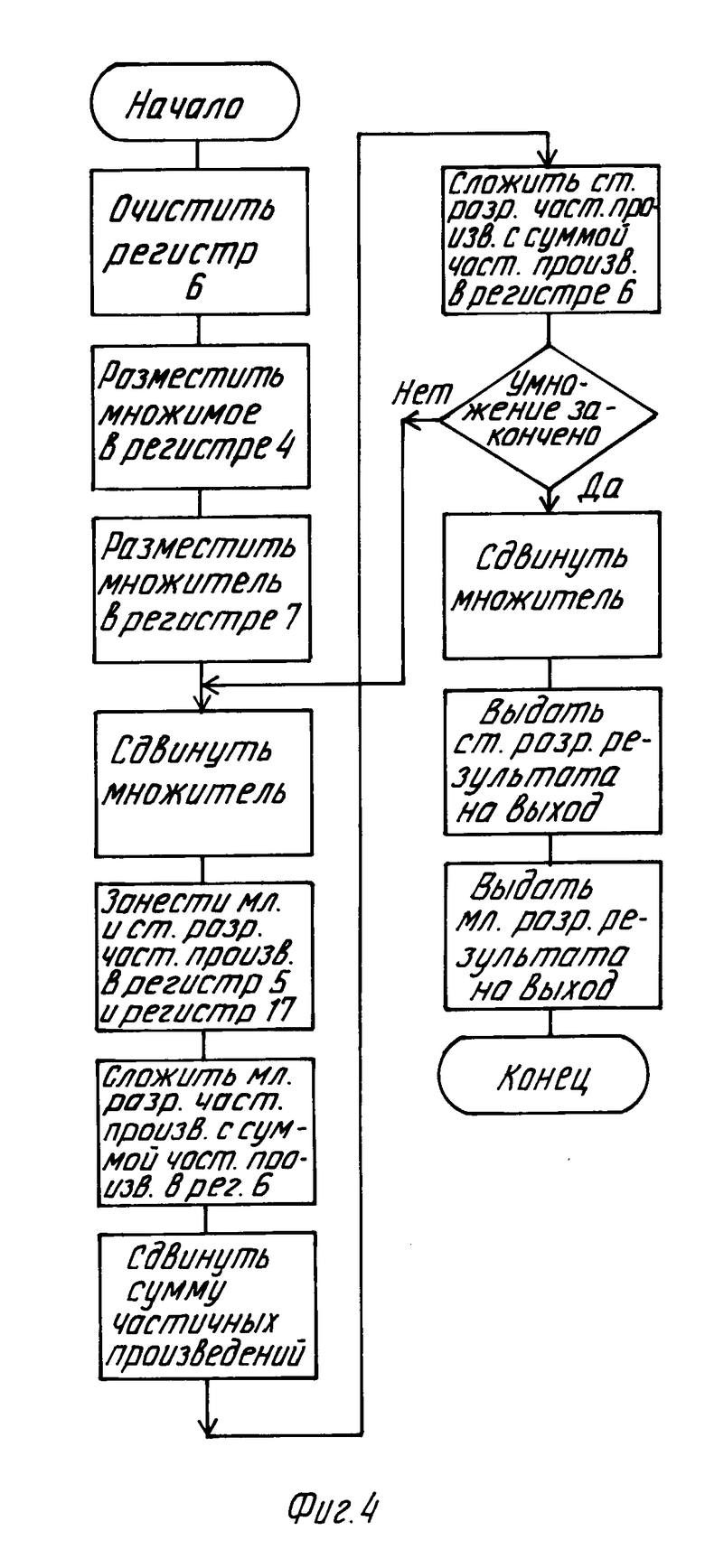

На фиг. 1 показана функциональная схема четырехбитного операционного блока; на фиг.2 схема вычислительного устройства; на фиг.3 граф-схема выполнения операции сложения; на фиг.4 граф-схема выполнения операции умножения.

Операционный блок (фиг.1) содержит запоминающий узел 1, первый 2 и второй 3 мультиплексоры, первый-четвертый регистры 4-7, входы 8 синхронизации, первый информационный вход 9, второй информационный вход 10, третий информационный вход 11, первую группу 12 входов кода операции, вторую группу 13 входов кода операции, вход чтения 14, информационный выход 15, третий мультиплексор 16, пятый регистр 17, вход 18 переноса, выход 19 переноса.

С первого по шестой входы синхронизации 8 блока подключены соответственно к входам синхронизации первого 4 регистра, второго 5 регистра, первому и второму входам синхронизации третьего 6 регистра, первому и второму входам синхронизации четвертого 7 регистра, первый информационный вход 9 блока соединен с информационным входом первого регистра 4 и вторым информационным входом четвертого регистра 7, второй информационный вход 10 блока соединен с вторым информационным входом третьего регистра 6 и первым информационным входом четвертого регистра 7, третий информационный вход 11 блока соединен с первым информационным входом второго мультиплексора 3, первая группа входов 12 кода операции блока соединена с первой группой адресных входов запоминающего узла 1, вторая группа входов 13 кода операции блока подключена к входам управления первого 2 и второго 3 мультиплексоров, вход чтения 14 блока соединен с входом разрешения чтения запоминающего узла 1, второй информационный выход которого соединен с информационным входом второго регистра 5, информационный выход которого подключен к первому информационному входу первого 2 мультиплексора, информационный выход которого связан с второй группой адресных входов запоминающего узла 1, информационный выход первого регистра 4 соединен с вторым информационным входом первого мультиплексора 2, информационный выход третьего регистра 6 связан с третьим информационным входом второго мультиплексора 3, информационный выход четвертого регистра 7 связан с вторым информационным входом второго мультиплексора 3, информационный выход которого является информационным выходом 15 блока и связан с третьей группой адресных входов запоминающего узла 1, вход синхронизации пятого регистра 17 подключен к второму входу синхронизации блока, первый, второй и третий, четвертый информационный выходы запоминающего узла 1 соединены соответственно с первым и вторым информационными входами третьего мультиплексора 16, управляющий вход которого соединен с входом переноса 18 операционного блока, первый информационный выход третьего мультиплексора 16 является выходом переноса 19 операционного блока, а второй выход связан с первым информационным входом третьего регистра 6, четвертый информационный выход запоминающего узла 1 связан с информационным входом пятого регистра 17, информационный выход которого связан с третьим информационным входом первого мультиплексора 2.

Операционный блок работает в составе вычислительного устройства, которое, например, содержит (см.фиг.2) n соединенных по цепи переноса операционных блоков, первые группы входов кода операции которых объединены и являются первой группой входов кода операции устройства, первые информационные входы операционных блоков являются информационными входами устройства, информационные выходы операционных блоков являются информационными выходами устройства, вход переноса устройства соединен с входом переноса первого операционного блока, выход переноса i-го операционного блока соединен с входом переноса (i+1)-го операционного блока (i=1,2,n-1), выход переноса n-го операционного блока является выходом переноса устройства, информационный выход (i+1)-го операционного блока соединен с вторым информационным входом i-го операционного блока, вторые группы входов кода операции операционных блоков объединены и подключены к второй группе входов кода операции устройства, третья группа входов кода операции вычислительного устройства соединена с информационными входами дешифратора, с первого по шестой выходы которого подключены соответственно к входам с первого по шестой синхронизации с первого по n-й операционных блоков, вход синхронизации устройства соединен со стробирующим входом дешифратора, кроме того, пятый выход дешифратора соединен с входом синхронизации первого регистра (регистр цифры множителя), входом сброса второго регистра (регистр младшей цифры суммы частичных произведений) и счетным входом счетчика циклов умножения, третий выход дешифратора соединен с входом синхронизации счетчика, выход переноса которого является выходом признака окончания умножения устройства, информационный выход первого операционного блока соединен с информационными входами первого и второго регистров, четвертый выход дешифратора соединен с входом синхронизации второго регистра, выход которого соединен с вторым информационным входом n-го операционного блока, выход первого регистра соединен с третьими информационными входами с первого по n-й операционных блоков, вход строба устройства соединен с входом чтения с первого по n-й операционных блоков и с входом сброса счетчика.

Реализация операций обеспечивается путем выполнения последовательности микрокоманд, генерируемых устройством управления машины, в состав которой входит вычислительное устройство с предлагаемым операционным блоком. Связь устройства управления с предлагаемым операционным блоком осуществляется через входы 8 синхронизации, первую группу 12 входов кода операции, вторую группу 13 входов кода операции, вход 14 чтения, вход 18 переноса. Код, устанавливаемый на этих входах устройством управления в каждом такте машинного времени, представляет собой микрокоманду. Предлагаемый операционный блок формирует для устройства управления и последующих операционных блоков признак переноса (выход 19 операционного блока). Операнды в предлагаемый операционный блок поступают из памяти машины через информационный вход 9 устройства, а результаты операций передаются в память и другие операционные блоки через информационные выходы 15 блока.

Операционный блок при выполнении операции сложения и умножения в двоично-десятичном коде работает следующим образом.

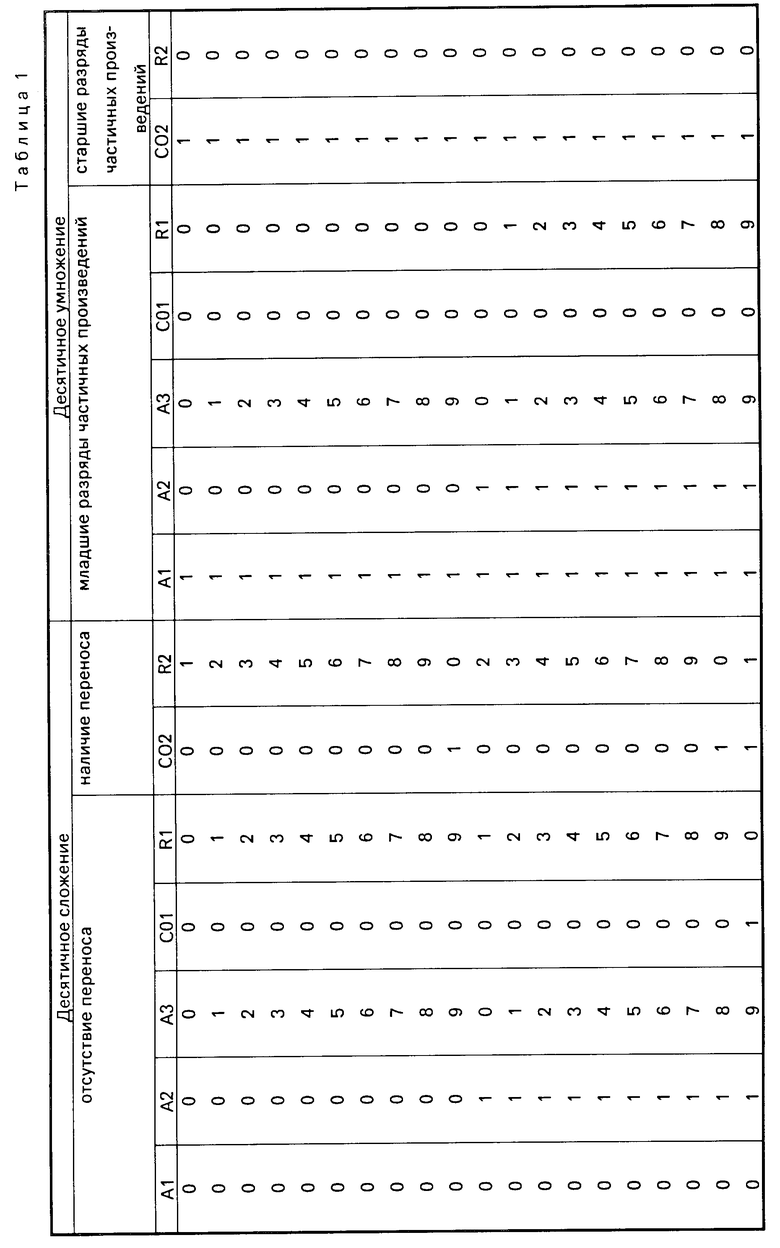

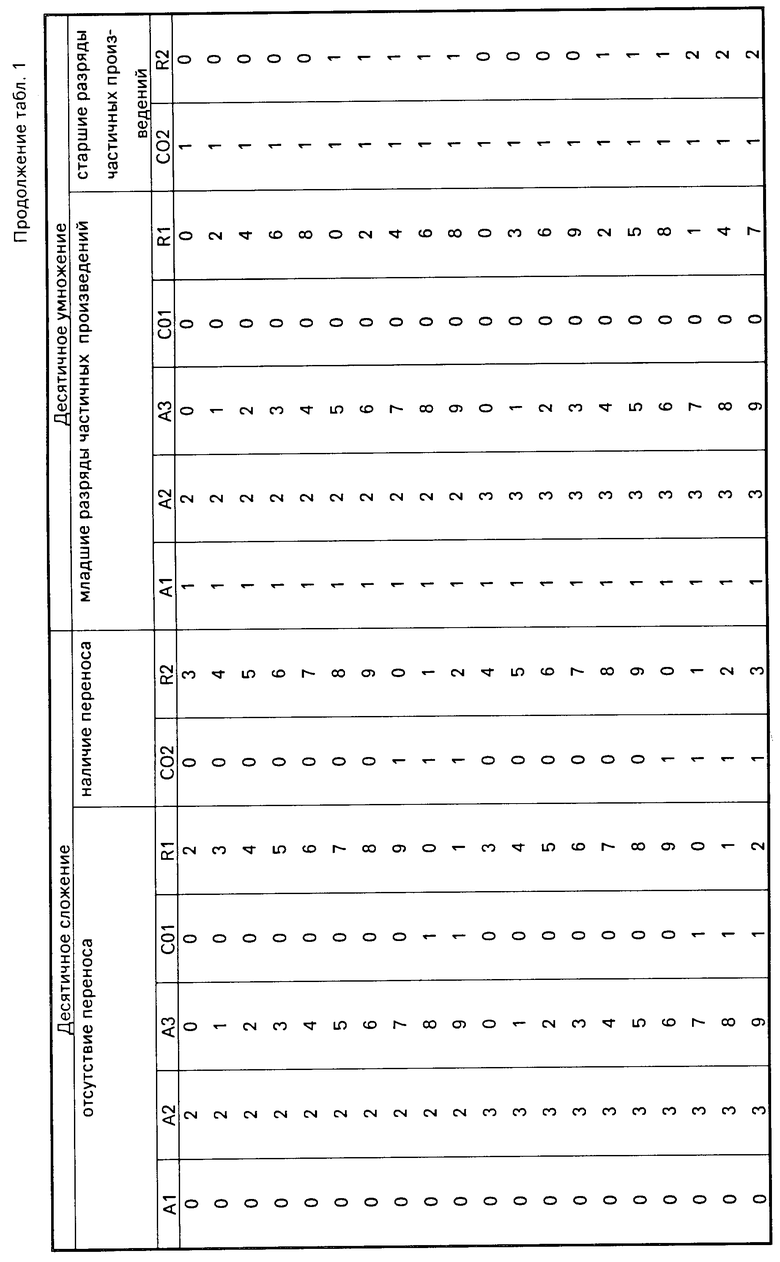

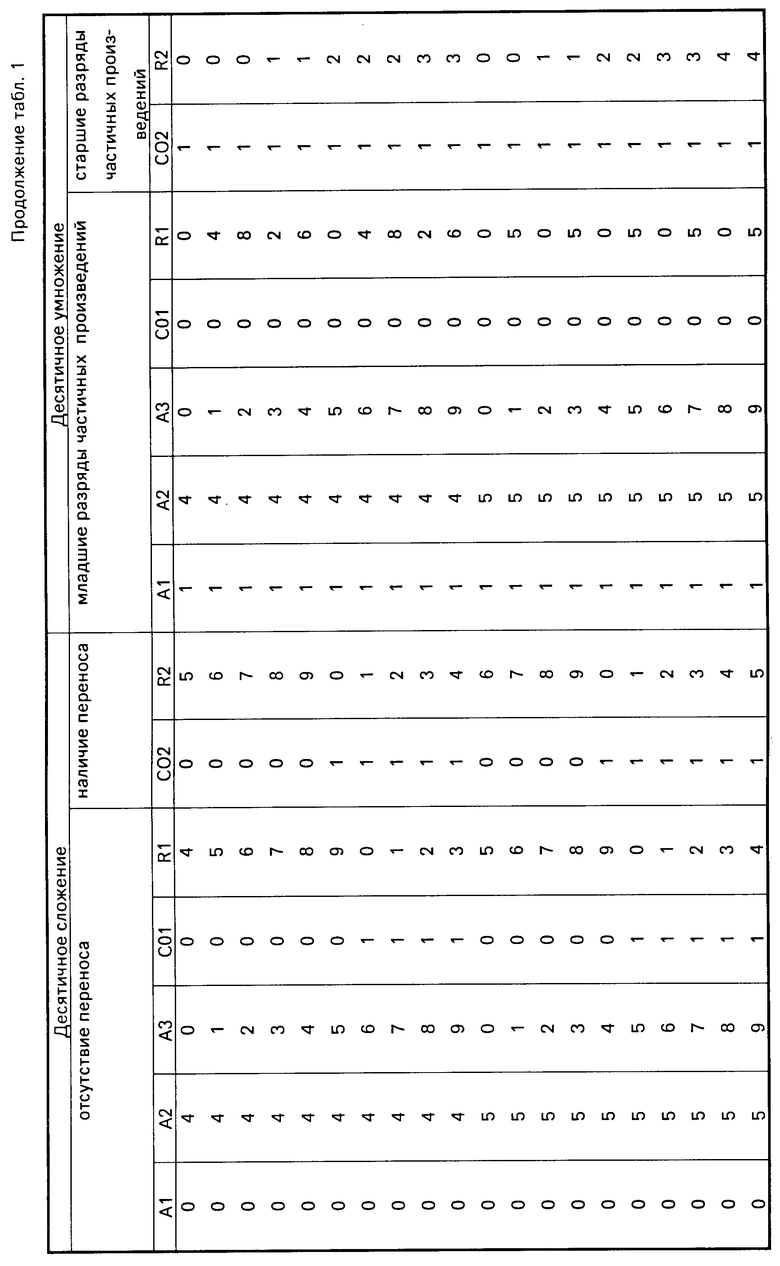

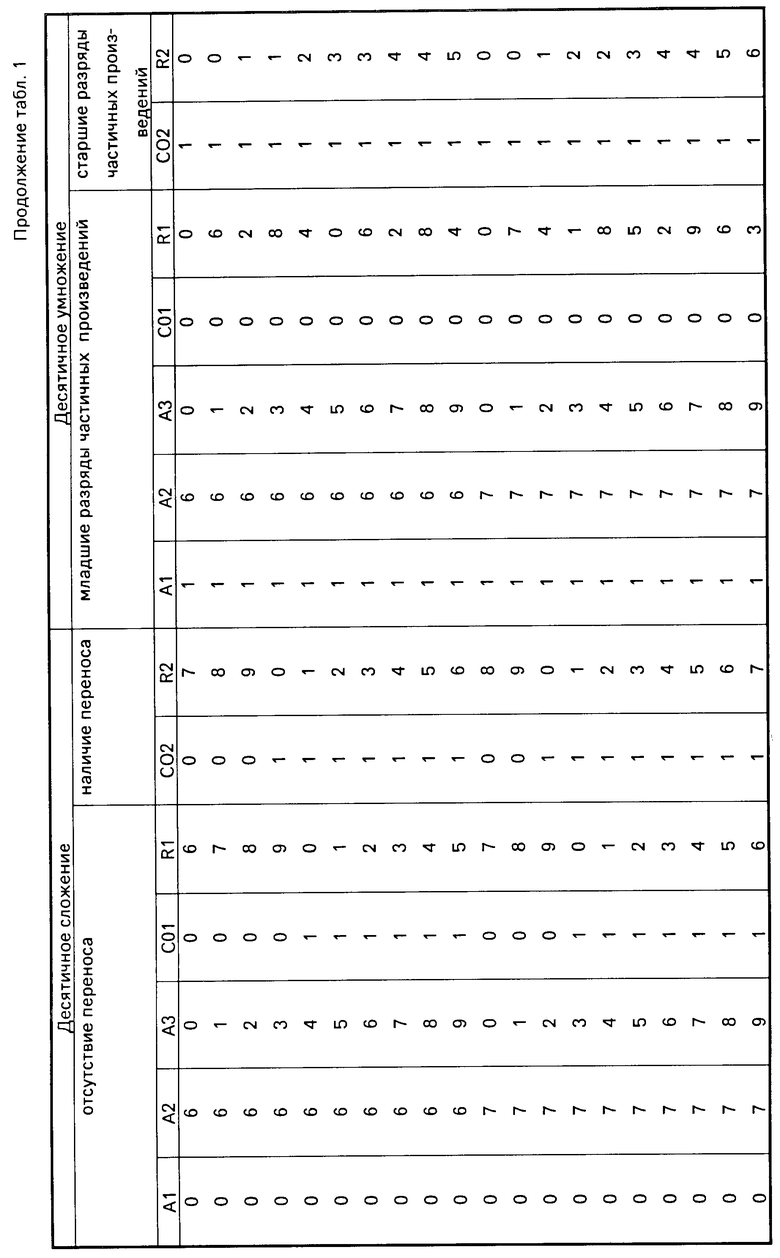

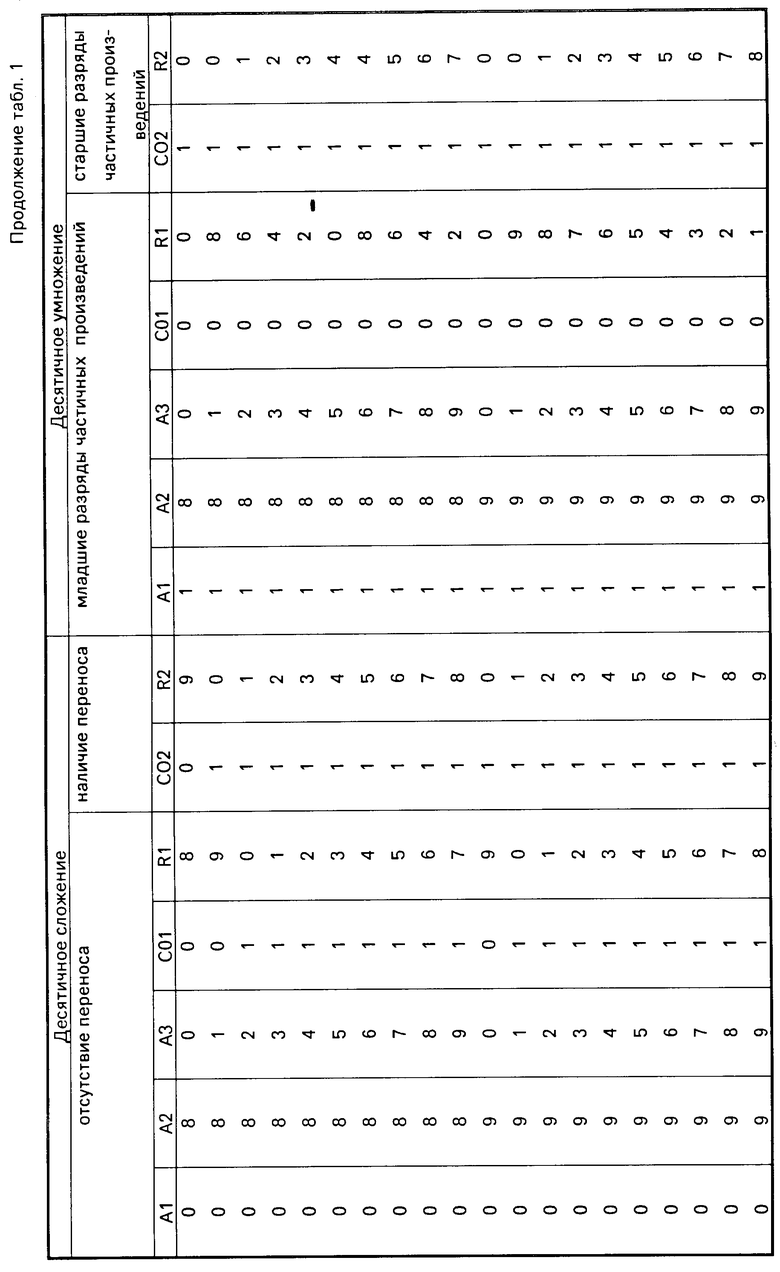

Для реализации операций сложения и умножения содержимое запоминающего узла 1 должно соответствовать данным табл.1. В табл.1 принято шестнадцатиричное кодирование по группам разрядов. Группы разрядов обозначены в табл.1 следующим образом: А1 первая группа адресных входов; А2 вторая группа адресных входов; А3 третья группа адресных входов; СО1 первый информационный выход (перенос); R1 второй информационный выход (результат); СО2 третий информационный выход (перенос); R2 четвертый информационный выход (результат).

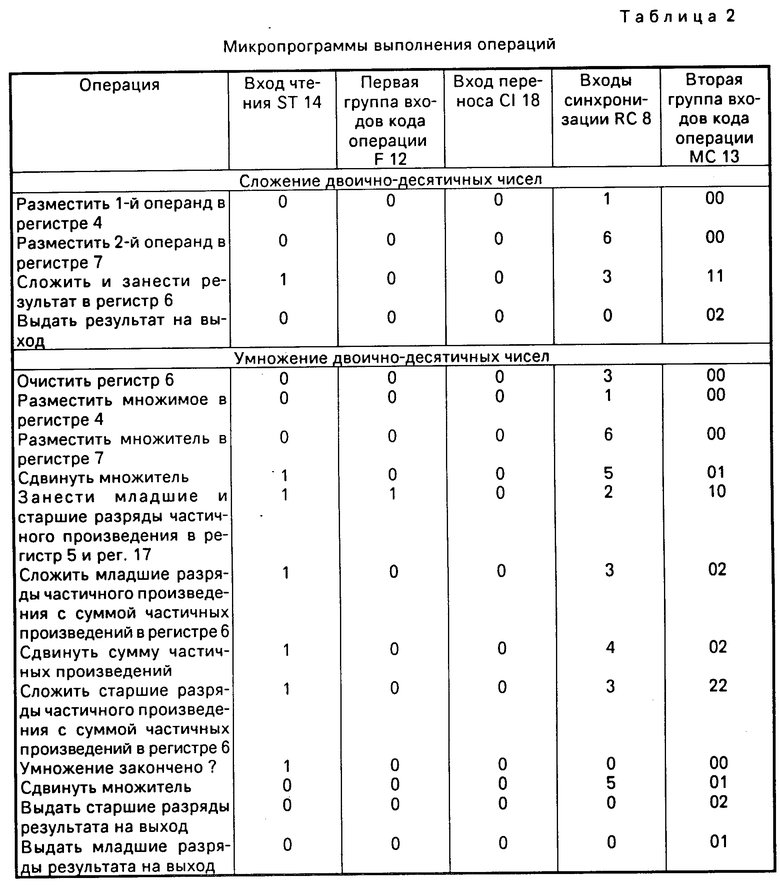

При выполнении операции двоично-десятичного сложения операционный блок работает в соответствии с микропрограммой, приведенной на фиг.3. Каждый блок этой схемы соответствует одной микрокоманде и выполняется за один такт. Коды микрокоманд приведены в табл.2. Первой выполняется команда "Разместить первый операнд в регистре 4". Код первого операнда поступает из памяти машины на информационный вход 9 блока и при выполнении микрокоманды заносится в регистр 4. Это обеспечивается тем, что на первом входе С1 входов 8 синхронизации присутствует уровень логической "1" (согласно данным табл.2). Аналогично выполняется команда "Разместить второй операнд в регистре 7". Информация с информационного входа 9 операционного блока записывается в регистр 7 благодаря наличию уровня логической "1" на входе С6 группы входов 8 синхронизации (согласно данным табл.2) При выполнении команды "Сложить и занести результат в регистр 6" первый и второй операнды в соответствии с кодом, поступающим на вторую группу 13 входов кода операции, через мультиплексоры 2 и 3 поступают на адресные входы А2 и А3 запоминающего узла 1, а на группу адресных входов А1 поступает код операции 0, что соответствует операции сложения. Благодаря активному уровню сигнала, поступающему на вход 14 операционного блока, активируются информационные выходы запоминающего узла 1 и результат сложения в соответствии с данными табл.1 формируется в виде двух результатов переноса СО1, результата R1 сложение при отсутствии переноса и переноса СО2, результата R2 сложение при наличии переноса, которые поступают на первый и второй информационные входы мультиплексора 16. В соответствии с сигналом переноса, поступающим из младшего операционного блока или устройства управления на управляющий вход мультиплексора 16, результат операции в виде переноса СО с выхода переноса операционного блока поступает на вход переноса старшего операционного блока или в устройство управления, а код результата заносится в регистр 6 благодаря уровню логической "1", формируемому на входе С3 группы входов 8 синхронизации (см.табл.2). Заключительной является операции "Выдать результат на выход", которая необходима для записи результата в память машины. При этом на управляющие входы второго мультиплексора 3 поступает код 2 (см. табл.2), благодаря чему выходы регистра 6 коммутируются на информационный выход 15 операционного блока. С этого выхода код суммы поступает для занесения в память.

Работа операционного блока при выполнении операции двоично-десятичного умножения соответствует микропрограмме, приведенной на фиг.4. Коды микрокоманд приведены в табл.2.

Вначале выполняется подготовительная операция "Очистить регистр 6". При этом на входе С3 группы входов 8 синхронизации устанавливается уровень логической "1" (см.табл.2). Поскольку на вход чтения запоминающего узла 1 через вход 14 операционного блока поступает сигнал логического нуля (см.табл. 2), на выходах запоминающего узла 1 устанавливаются нулевые уровни. В результате в регистр 6 заносится нулевой код. Затем последовательно выполняются команды "Разместить множимое в регистре 4" и "Разместить множитель в регистре 7". Эти микрокоманды выполняются аналогично микрокомандам "Разместить первый операнд в регистре 4" и "Разместить второй операнд в регистре 7". Основной цикл умножения начинается выполнением микрокоманды "Сдвинуть множитель". Для обеспечения сдвига множителя на входы управления второго мультиплексора 3 подается код 1, а на вход С5 группы входов 8 синхронизации уровень логической "1". В результате этого код цифры множителя из регистра 7 i-го операционного блока заносится в регистр 7 (i-1)-го операционного блока через вторые информационные входы 10 операционных блоков. Затем выполняется микрокоманда "Занести младшие и старшие разряды частичного произведения в регистры 5 и 17". В соответствии с кодом управления мультиплексорами на входах 13 устройства первый мультиплексор 2 подключает ко второму адресному входу А2 запоминающего узла 1 код множимого из регистра 4, а второй мультиплексор 3 к третьему адресному входу А3 запоминающего узла третий информационный вход 11, на который поступает код очередной цифры множителя. На группу адресных входов А1 (см.табл.2) поступает логическая единица, что соответствует выборке из запоминающего узла 1 младших и старших разрядов частичных произведений (см.табл.1). Выборка поддерживается активным сигналом на входе 14. На входе С2 группы входов 8 синхронизации устанавливается уровень логической "1", что обеспечивает занесение младших и старших разрядов произведения в регистры 5 и 17. Затем выполняется микрокоманда "Сложить младшие разряды частичного произведения с суммой частичных произведений в регистре 6". Сложение выполняется так же, как при выполнении команды "Сложить и занести результат в регистр 6", только в операции участвуют операнды из регистров 5 и 6, причем результат заносится в последний. После сложения выполняется микрокоманда "Сдвинуть сумму частичных произведений". Эта микрокоманда выполняется аналогично микрокоманде "Сдвинуть множитель", при этом в операции участвует сумма частичных произведений, расположенная в регистре 6, а согласно табл.2 на входе С4 группы входов 8 синхронизации устанавливается уровень логической "1".

Затем выполняется микрокоманда "Сложить старшие разряды частичного произведения с суммой частичных произведений в регистре 6 и проверить признак окончания умножения". Она выполняется аналогично микрокоманде "Сложить и занести результат в регистр 6", только в операции участвуют операнды из регистров 17 и 6. Кроме того, при выполнении этой команды управляющее устройство анализирует признак окончания умножения. Если эта ситуация еще не наступила, управляющее устройство переходит к повторению цикла умножения, начиная с микрокоманды "Сдвинуть множитель". В противном случае цикл умножения не повторяется, но дополнительно выполняется микрокоманда "Сдвинуть множитель". Необходимость в таком действии возникает для окончательной упаковки множителя в регистр. Последние микрокоманды "Выдать старшие разряды результата на выход" и "Выдать младшие разряды результата на выход" обеспечивает передачу на выход 15 устройства содержимого регистров 6 и 7 соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| Операционный модуль | 1982 |

|

SU1083198A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ ОШИБОК И КОРРЕКЦИЕЙ ОДИНОЧНОЙ ОШИБКИ | 1993 |

|

RU2062512C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2034329C1 |

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| УНИВЕРСАЛЬНЫЙ ГЕНЕРАТОР СИГНАЛОВ ПРОИЗВОЛЬНОЙ ФОРМЫ | 1994 |

|

RU2060536C1 |

| Многофункциональный модуль | 1981 |

|

SU1067497A1 |

Изобретение относится к вычислительной технике и может найти применение при построении быстродействующих универсальных ЭВМ. Цель изобретения - повышение быстродействия при выполнении двоично-десятичных операций. Операционный блок содержит запоминающий узел для хранения таблиц сложения и умножения, первый и второй мультиплексоры, первый, второй, третий, четвертый регистры, с целью повышения быстродействия, в него введены третий мультиплексор и пятый регистр. 4 ил., 2 табл.

ОПЕРАЦИОННЫЙ БЛОК, содержащий запоминающий узел, первый и второй мультиплексоры, первый четвертый регистры, с первого по шестой входы синхронизации блока подключены соответственно к входам синхронизации первого и второго регистров, первому и второму входам синхронизации третьего и четвертого регистров, первый информационный вход блока соединен с информационным входом первого регистра и вторым информационным входом четвертого регистра, второй информационный вход с вторым информационным входом третьего регистра и первым информационным входом четвертого регистра, третий информационный вход с первым информационным входом второго мультиплексора, первая группа входов кода операции блока соединена с первой группой адресных входов запоминающего узла, вторая группа входов кода операции блока подключена к входам управления первого и второго мультиплексоров, вход чтения блока соединен с входом разрешения чтения запоминающего узла, второй информационный выход которого соединен с информационным входом второго регистра, информационный выход которого подключен к первому информационному входу первого мультиплексора, информационный выход которого связан с второй группой адресных входов запоминающего узла, информационный выход первого регистра соединен с вторым информационным входом первого мультиплексора, информационный выход третьего регистра с третьим информационным входом второго мультиплексора, информационный выход четвертого регистра с вторым информационным входом второго мультиплексора, информационный выход которого является информационным выходом блока и связан с третьей группой адресных входов запоминающего узла, отличающийся тем, что в него введены третий мультиплексор и пятый регистр, вход синхронизации которого подключен к второму входу синхронизации блока, первый, второй и третий, четвертый информационные выходы запоминающего узла соединены соответственно с первым и вторым информационными входами третьего мультиплексора, управляющий вход которого соединен с входом переноса операционного блока, первый информационный выход третьего мультиплексора является выходом переноса операционного блока, а второй связан с первым информационным входом третьего регистра, четвертый информационный выход запоминающего узла связан с информационным входом пятого регистра, информационный выход которого связан с третьим информационным входом первого мультиплексора.

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1995-04-30—Публикация

1993-06-01—Подача