Изобретение относится к ВЕЛЧИСЛИтельной технике и может найти применение при построении специализирован ных и универсальных ЭВМ. Известен микропроцессорный модуль содержащий регистр-аккумулятор, четы ре группы ыин управления, входные и выходные шины данных и функционально го переноса направо и налево, а такж шину тактовых импульсов Cl1. Недостатком данного мбдуля являет ся широкое поле управления микрооперацией. Наиболее близким к предлагаемому по технической сущности является мик ропроцессорный модуль, содержащий первый и второй триггеры, входы синх ронизации которых соединены с шиной тактовых импульсов, четыре мультиплексора, первая группа шин управлени соединена с информационными входами первого мультиплексора, первый упраВ ляющий вход которого соединен с первым управляющим входом второго мультиплексора, второй управляющий вход которого соединен с входной шиной переноса и вторым управляющим входом первого мультиплексора, третий управ ляющий вход которого соединен с первой входной шиной данных и третьим управляющим входом второго мультиплексора, четвертый управляющий вход которого соединен с выходной шиной обратной связи, первой выходной шиной данных, выходом триггера нулевог разряда и четвертым управляющим входом первого мультиплексора, выход которого соединен с первой выходной шиной переноса, вторая выходная шина переноса соединена с выходом третьего мультиплексора, первый управляющий вход которого соединен с входной шиной обратной связи и первым уп равляющим входом четвертого мультиплексора, второй управляющий вход которого соединен с первой выходной шиной переноса и вторым управляющим входом третьего мультиплексора, тре- тий управляющий вход которого соединен с второй входной шиной данных и третьим управляющим входом четвертого мультиплексора, четвертый управляющий вход которого соединен с выходом первого триггера/ второй вы-г ходной шиной данных и первым управля ющим входом первого мультиплексора, информационные входы которого соединены с первой группой шин управления, информационные выходы второго и четвертого мультиплексоров соедине ны соответственно с D -входами первого и второго триггеров, первая и вторая асинхронные шины данных соединены соответственно сD-входами первого и второго триггеров 2. Недостатком известного модуля является невозможность адаптации к решаемой задаче. Цель изобретения - расширение области прик нения модуля за счет реализации им возможности адаптации к решаемой задаче и выполнения различных операций в разных разрядах. Поставленная цель достигается .тем, что в операционный модуль, содержащий первый и второй триггеры, входы синхронизации которых подключены к входу синхронизации модуля, введены первая и вторая группы элементов ЗИ-ИЛИ-НЕ по четыре элемента в каждой, элемент НЕ, первый и второй блоки памяти, группы информационных входов, первые группы адресных входов и входы разрешения записи которых соединены соответственно с группой информационных входов, с группой входов управления и с управляющим входом модуля, вторые группы адресных входов первого и второго блоков памяти подключены соответственно к выходам элементов 2И-ИЛИ-НЕ первой и второй групп, первые информационные выходы первого и второго блоков памяти соединены соответственно с первым входом первого элемента 2И-ИЛИ-НЕ второй группы и с выходом переноса модуля, второй информационный выход первого блока памяти соединен с информационным входом первого триггера и с первым асинхронным выходом данных модуля, второй информационный выход второго блока памяти соединен с информационным входом второго триггера и с вторым асинхронным выходом данных модуля, первый вход первого элемента 2И-ИЛИ-НЕ первой группы соединен с входом переноса модуля, первые входы.вторых элементов 2И-ИЛИ-НЕ первой и второй групп соединены соответственно с первым и вторым входами данных модуля, первый вход третьего элемента 2ИИЛИ-НЕ первой группы соединен с выходом первого триггера, с выходом переноса вправо модуля и с первым синхронным входом данных модуля, первый вход третьего элемента 2ИИЛИ-НЕ второй группы соединен с перовым входом четвертого элемента 2ИИЛИ-НЕ первой группы, с выходом вто,рого триггера и с вторьал синхронным выходом данных модуля, первый вход четвертого элемента 2И-ИЛИ-НЕ второй группы соединен с входом переноса вправо модуля, вторые входы первых, вторых, третьих и четвертых элементов 2И-ИЛИ-НЕ первой и второй групп соединены соответственно с первым, вторым, третьим и четвертым входами настройки модуля, третьи входы всех элементов 2И-ИЛИ-НЕ соединены с выходом элемента НЕ, вход которого соединен с четвертыми входами всех элементов 2И-ИЛИ-НЕ и с входом управления режимом модуля.

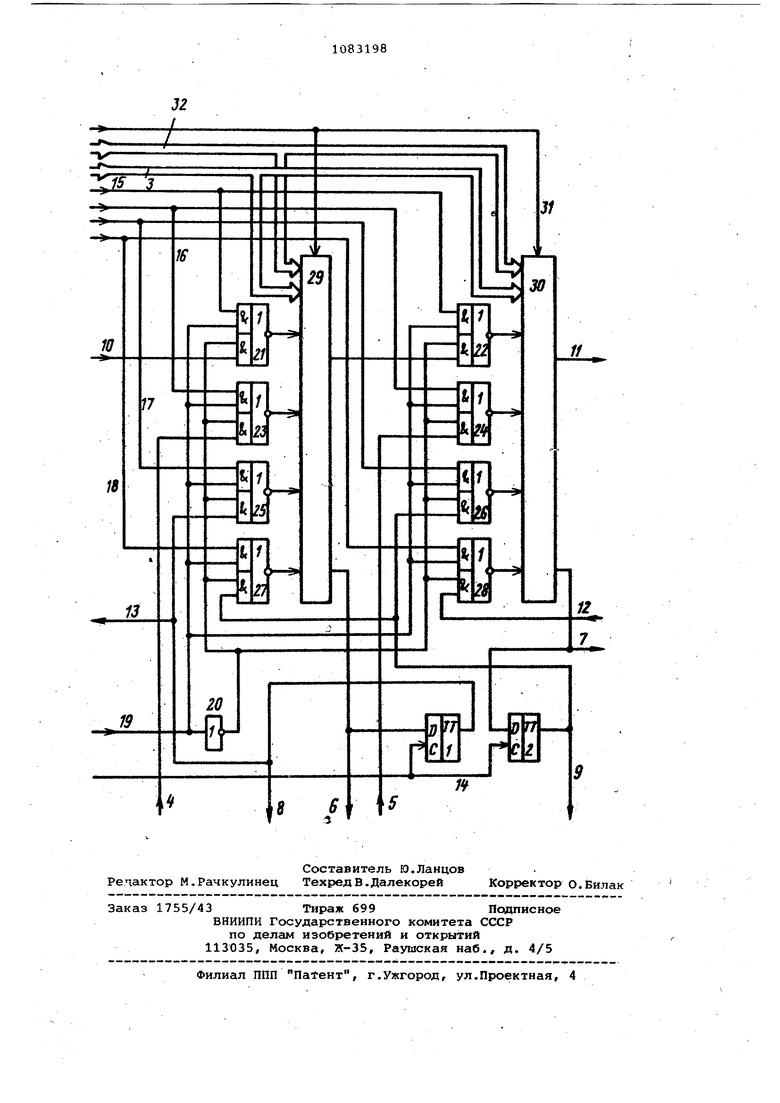

На чертеже изображена схема предлагаемого модуля.

Операционный модуль содержит первый. 1 и второй 2 триггеры, группу входов 3 управления, первый 4 и второй 5 входы данных, первый 6 и второй 7 асинхронные выходы данных, первый 8 и второй 9 синхронные выходы данных, вход 10 и выход 11 пере-. носа, вход 12 и выход 13 переноса вправо, вход 14 синхронизации, четыре входа 15-18 настройки, вход 19 управления режимом, элемент НЕ 20, восемь элементов 2И-ИЛИ-НЕ 21-28, два блока 29 и 30 памяти, вход 31 разрешения записи и группу информационных входов 32.

Операционный модуль, предназначенный для реализации арифметико-логических операций, работа;ет следующим образом.

Двоичный код, подаваемый по группе входов 3 управления, определяет вид микрооперации, реализуемой над двумя операндами, один из которых находится в триггерах 1 и 2, а другой - на входах 4 и 5 данных. Количество входов управления определяется двоичным логарифмом количества микроопераций, выбранных из всего множества возможных микроопераций для решения данной задачи. Для подготовки микропроцессорного модуля к реализации выбранного набора микр операций служит режим настройки, определяемый значением сигнала на входе 19 управления режимом. В этом режиме вторая группа адресных входо блоков 29 и 30 памяти соединяется . через элементы 2И-ИЛИ-НЕ 21,23,25, 27 и 22,24,26,28 с выходами 15,16 и 17,18 настройки соответственно.

Для настройки операционного модуля для. реализации некоторой заданно микрооперации на группе входов 3 управления устанавливается код этой микрооперации, а на входах 15-18 настройки - один из возможных наборов значений операндов, переноса и сдвига вЪраво соединяется с микрооперации. При этом на вход 15 подаеся сигнал,, представляющий собой в режиме настройки значение переноса, на вход 16 - значение разряда входного операнда, на вход 17 - значение триггеров 1 и 2, а на вход 18 значение переноса вправо. Одновремено на одной и другой парах разрядов группы информационных входов 32 устанавливаются значения результато операций в соответствующих разрядах устройства и переноса в следующие разряды. После установки всех этих данных на вход 31 разрешения записи поступает сигнал, производящий запись полученной информации в блоки 29 и 30 памяти. Аналогичнымобра зом осуществляется настройка операционного модуля при всех возможных наборах значений операндов и переносов для всего выбранного множества микроопераций.

. После настройки- операционный модуль изменением сигнала на входе 19 управления режимом переводится в режим вычисления. В этом режиме вторая группа адресных входов блоков 29 и 30 памяти соединяется .соответствующими выходами триггеров 1 и 2, входа0ми 4 и 5 данных и входами 12 и 10 переносов. При этом на вторых выходах блоков 29 и 30 памяти и на асинхронных выходах 6 и 7 данных в соответ-i ствии с заданной на группе входов 3

5 управления микрооперацией формируется результат выполнения микрооперации в срответствующем разряде, а на первых выходах - значение сигналов переноса. Значение сигнала переноса

0 с первого выхода блока 30 памяти поступает на выход 11 переноса. Таким образом, значение результата в данном разряде и перенос в следующий разряд при заданной микроопера5ции являются произвольными переключательными функциями четырех аргументов: сигнала на входе 4 или 5 данных соответствующего разряда, выходного сигнала соответствующего разряда,сиг0нала переноса,поступающего по входу 10 переноса или с первого выхода блока 29 памяти и сигнала переноса вправо,поступающего с выхода второго нли по входу 12 переноса вправо.

5

По фронту тактового импульса, поступакицего по входу 14 сияхронизации на вход синхронизации триггеров 1 и 2, происходит запись результата микрооперации с асинхронных выходов 6 и 7 данных в триггеры 1 и 2. Этот

0 результат поступает на .синхронные выходы 8 и 9 данных. Одновременно сигнал с выхода первого триггера 1 поступает на выход 13 переноса вправо. Результат, записанный в тригге5ры 1 и 2, остается неизменным до прихода фронта следующего тактового импульса.

Для реализации другого подмножества микроопераций должен быть пов0торен процеср настройки.

Таким образом, в предлагаемом модуле реализуется возможность адаптации к решаемой задаче путем проведения соответств.ующей настройки опре5деленной системы микрокоманд, а также предусмотрена возможность выполнения различных операций в разных разрядах.

Реализация таких возможностей поз0воляет расширить область применения предлагаемого модуля. Так, например, на его базе можно построить многоразрядный адаптивный процессор с изменяющимся в процессе вычислений набором реализуемых микроопераций.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорное устройство для цифрового преобразования координат | 1982 |

|

SU1104523A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Процессор для обработки массивов данных | 1982 |

|

SU1381532A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Устройство для контроля устройства микропрограммного управления | 1988 |

|

SU1608674A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Устройство для выполнения операций умножения и деления | 1986 |

|

SU1403061A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

ОПЕРАЦИОННЫЙ МОДУЛЬ, содержащий первый и второй, триггеры, входы синхронизации которых подключены к входу синхронизации модуля, отличающийся тем, что, с целью расширения области применения за счет реализации модулем возможности адаптации к решаемой задаче, в него введены первая и вторая группы элементов 2И-ИЛИ-НЕ по четыре элемента в каждой, элемент НЕ, первый и второй блоки памяти, группы информационных входов, первые группы адресных входов и входы разрешения записи которых соединены соответственно с группой информационных входов,-с группой входов управлейия и с управляющим входом модуля,вторые группы адресных входов первого и второго блоков памяти подключены соотBeTCTBieHHo к выходам элементов. 2ИИЛИ-НЕ первой и второй групп, первые информационные выходы первого и второго блоков памяти соединены соответственно с первым входом первого элемента 2И-ИЛИ-НЕ второй группы и с выходом переноса модуля, второй информационный выход первого блока памяти соединен с информационным входом первого триггера и-с-первым асинхронным выходом данных модуля, второй информационный выход второго блока памяти соединен с информационным входом вт,орого триггера и с вторым асинхронным выходом данных модуля, первый вход первого элемента 2И-ИЛИ-НЕ первой группы соединен с входом переноса модуля, первые входы вторых элементов 2К-ИЛИ-НЕ первой и второй групп соединены соответственно с первым и вторым входами данных модуля, первый вход третьего элемента 2И-1ШИ-КЕ i О) первой группы соединен с выходом первого триггера, с выходом переноса вправо модуля и с первым синхронным входом данных модуля, первый вход третьего элемента 2И-ИЛИ-НЕ второй группы соединен с первым входом четвертого элемента 2И-ИЛИ-МЕ первой группы, с выходом второго триггера и с синхронным выходом данных модуля, первый вход четвертого элемента 2И-ИЛИ-НЕ второй 00 груйпы соединен с входом переноса вправо модуля, вторые входы первых, со вторых, третьих и четвертых элементов 2И-Ш1И-НЕ первой и второй групп соединены соответственно с первым, со вторым, третьим и четвертым входами эо настройки модуля, третьи входы всех элементов 2И-ИЛИ-НЕ соединены с выходом элемента НЕ, вход которого соединен с четвертыми входами всех элементов 2И-ИЛИ-НЕ и с входом управления режимом модуля.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропроцессорная секция | 1979 |

|

SU842789A1 |

| кя | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1984-03-30—Публикация

1982-12-03—Подача