Изобретение относится к вычислительной техйике и может найти применение при построении специализированных и универсальных ЭВМ,

Известен многофункциональный модуль, содержащий регистр-аккумулятор группу управляющих входов, входы и выходы данных и функционального переноса направо и налево, тактовый вход, кроме того, содержащий восемь селекторов-мультиплексоров flj.

Недостатками известного устройст являются сложность конструкции и большое количество внешних выводов.

Наиболее близким к изобретению яв ляется многофункциональный модуль, содержащий триггеры нулевого и первого разрядов, первый и второй мулы типлексоры, информсщионные входы которых соединены с группой управляющих входов модуля, выходы первого и второго мультиплексоров подключены к информационным входам триггеров нулевого и первого разрядов соответственно, а также к асинхронным данных нулевого и первого разрядоБ модуля, первый, второй, третий и четвертый управляющие входы первого мультиплексора соединены соответственно с выходом триггера нулевого разряда, входом данных нулевого разряда модуля, входом переноса модуля выходом триггера первого разряда, . первый, второй и третий управляквдие входы второго мультиплексора подключены соответственно к выходу триггера первого разряда, входу данных первого разряда модуля и входу обрат ной связи модуля, при этом выходы триггеров нулевого и первого разрядов соединены с выходами данных нулевого и первого разрядов модуля соответственно С21. .

Недостатками данного многофункционального модуля являются сложность конструкции и большое количество Внешних выводов (44 вывода без учета выводов для питания устройства). Это значительно затрудняет микроэлектронную реализацию данного модуля, так как используемая площадь кристалла и количество внешних выводов из корпуса являются основными критериями при микроэлектронной реализации устройств и близки в данном модуле к предельным значениям. Поскольку при современном уровне развития вычислительной техники невозможность микроэлектронной реализации вычислительного узла является практически непреодолимой преградой для его широкого внедрения, то эти недостатки являются очень серьезными и данный многофункциональный модуль может иметь лишь ограниченную облаА применения.Цель изобретения - упрощение модуля и сокращение количества внешних выводов.

Поставленная цель достигается тем, что в многофункциональный модуль, содержащий триггеры нулевого и первого разрядов, первый и второй мультиплексоры, информационные входы которых соединены с группой управляющих входов модуля, выходы первого и второго мультиплексоров подключены к инфори1ационным входам триггеров нулевого и первого разрядов соответственно, а также к асинхронным выходам данных нулевого и первого разрядов модуля, первый, второй, третий и четвертый управляющие входы первого мультиплексора соединены соответственно с выходом триггера нулевого разряда, входом данных нулевого разряда модуля, входом переноса модуля и выходом триггера первого разряда, первый, второй и третий управляюйще .входы второго мультиплексора подключены соответственно к выходу триггера первого разряда, входу данных первого разряда модуля и входу обратной связи модуля, при этом выходы триггеров нулевого и первого разрядов соединены с выходами данных Нулевого и первого разрядов модуля соответственно, введены первый и второй D -триггеры и элемент И, первый и второй входы и выход которого подключены соответственно к тактовому и управляющему входам модуля и входам синхронизации триггеров нулевого и первого разрядов, информационные входы первого и второго р -триггеров соединены с выходами соответственно первого и второго мультиплексоров, входа синхронизации Э -триггеров подключены к управляющему входу модуля, а выходы первого и второго 3 -триггеров соединены соответственно с четвертым управляющим входом второго мультиплексора и выходом переноса модуля.

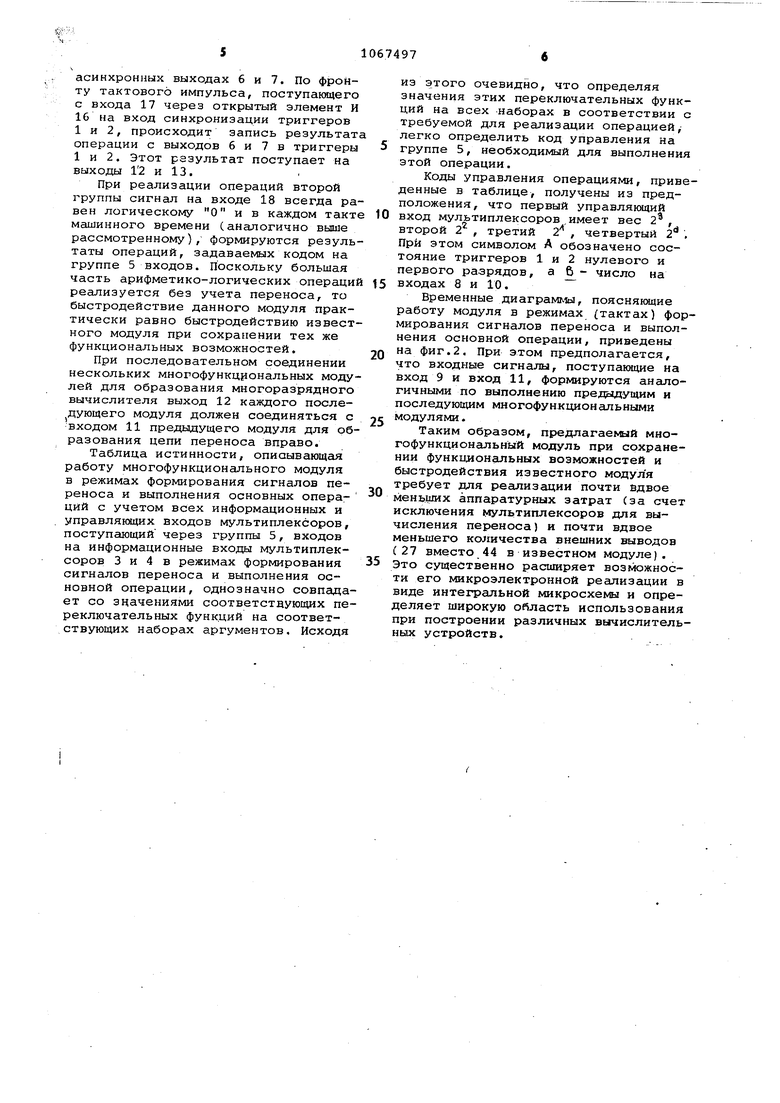

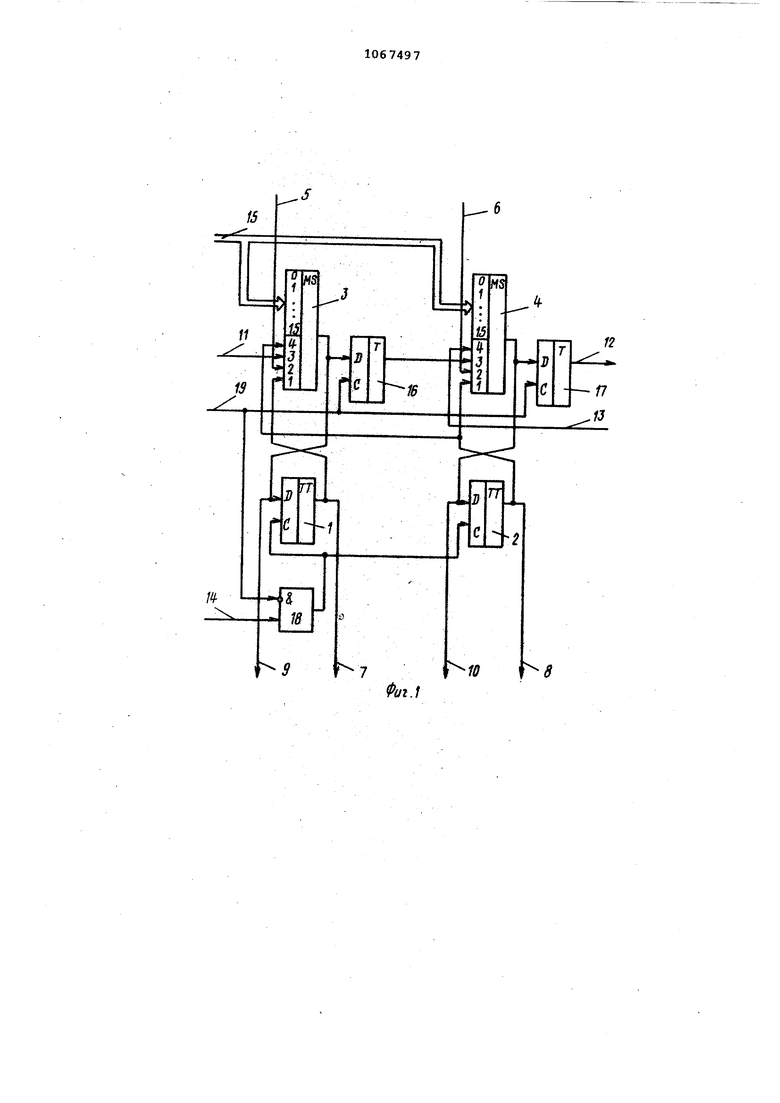

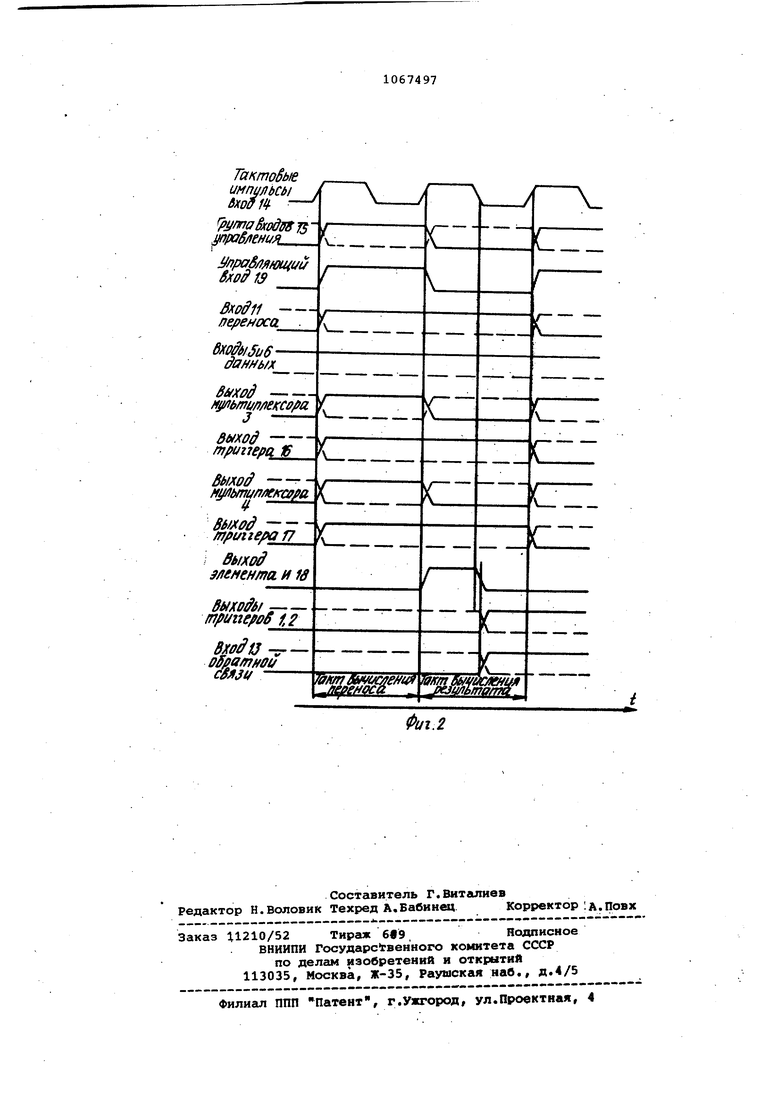

На фиг.1 изображена схема многофункционального кюдуля, на фиг.2 его временная диаграмма поясняющая работу модуля.

Многофункциональный модуль содержит триггеры 1 и 2 нулевого и первого разрядов, первый и второй мультиплексоры 3 и 4, информационные входы которых соединены с группой 5 управляющих входов модуля, выходы мультиплексоров 3 и 4 подключены к информационным входам триггеров 1 и 2 соответственно, а также к асинхронным выходам б и 7 данных нулевого и первого разрядов модуля, первый, второй, третий и четвертый управляюшие входы первого мультиплексора 3 соединены соответственно с выходом триггера 1, входом 8 данных нулевого разряда модуля, входом 9 переноса мо дуля и выходом триггера 2, первый, второй и третий управляюище входы мультиплексора 4 подключены соответственно к выходу триггера 2, входу 10 данных первого разряда модуля и входу 11 обратной связи модуля. При этом выходы триггеров 1 и 2 соединены с выходами 12 и 13 данных нулевого и первого разрядов модуля соответственно. Кроме того, модуль содержит первы и второй Ь -триггеры 14 и 15 и элемент И 16, первый и второй входы и выход которого подключены соответственно к тактовому 17 и управляющем 18 входам модуля и входам синхронизации триггеров 1 и 2, информационные входы триггеров 14 и 15 соединен с выходами соответственно мультиплек jcopoB 3 и 4, входы синхронизации С-триггеров подключены к управляющему входу 18 модуля, а выходы триггеров 14 и 15 соединены соответственно с четвертым управляющим входом мультиплексора 4 и выходом 10 перено са модуля. Многофункциональный модуль работа ет следующим образом. Все арифметико-логические операци могут быть разбиты на две группы. В первой из них результат операции в некотором разряде формируется исходя из заданного кода опергщии и значени операндов в этом разряде с учетом переносов в него справа и слева. Во второй группе результат операции в некотором разряде формируется без учета переносов в этот разряд. Поскольку алгоритм решения задачи в общем случае содержит арифметико-логические операции обеих групп, то кг1ждый разрядный фрагмент вычислительного устройства должен содержать управляекше от блока микропрограммно го управления логические схемы вычис ления переносов, которые не используются при реализации операций второй группы. Так как операции второй группы составляют большую часть операций, необходикЕлх для решения любой Зсодачи, то в результате этого практи чески в течение всего времени работы устройства существует большая аппара турная избыточность ( неиспользуемые схема вычисления переносов и их входы управления), что приводит к неоправданному усложнению многофункциональных модулей и увеличению внешних выводов из корпуса при их микроэлектронной реализсЩйи. В данном многофункциональном модуле для вычисления, переносов и результатов операции используются одни и те же мультиплексоры 3 и 4, управляемые кодом операции, поступающим на группу управляющих входов 5. При, этом арифметико-логические операции первой группы реализуются за два такта машинного времени, в первом из которых вычисляется значение переноса из каждого разряда, запоминаемое в соответствующих D -триггерах 14 и 15, а во втором - значение операции в этом разряде с учетом переноса. Двоичный код управления, подаваемый по группе 5 входов, ширина которой равна 16 бит, определяет вид операции, реализуемой в данном такте машинного времени. Разделение тактов машинного времени на такты для вычисления переносов и результатов операции осутдествляется сигнгшом, поступаквдим на вход 18. При наличии на входе 18 .сигнгша логической 1 осуществляется вычисление сигналов переноса каждого разряда. Вычисление этих сигналов осуществляется мульти лексорами 3 или 4 в соответствии с кодом операции на группе 5 входов сигналс1МИ на входах 8 и 10, сигналами с выходов триггеров 1 или 2, со входа переноса 9 или с выхода триггера 14, а также сигналами переноса вправо, поступающими с выхода триггера 2 или входа 11. В этом такте D-триггеры 14 и 15 открыты сигналом со входа 18 и запоминают значение соответствующих сигна1лов переноса. При этом сигнал со входа 18 с помощью элемента И 16 по инверсному входу блокирует сигнал синхронизации на входах триггеров 1 и 2. В результате этого их состояния в этом такте не изменятся.. При переходе к следующему такту машинного времени (такту вычисления результата операции) сигнал на входе 18 должен принимать значение, равное логическому О. Это обеспечивает запирайие D -триггеров 14 и 15, хранящих сигналы переноса, и пропускание импульсов синхронизации со входа 18 на входы триггеров 1 и 2. В этом такте машинного времени мультиплексоры 3 или 4 вычисляют значение результата операции, заданной кодом на группе 5 входов. Результат опергьции в кешдом разряде явлйется произвольной переключательной функцией четырех аргументов: сигнала на входах данных (8 или 10), выходного сигнала соответствующего триггера (1 или 2, сигнала переноса, поступанвдего с входа 9 переноса или триггера 14, и сигнсша переноса вправо, поступающего с выхода триггера 2 или входа 11. При этом сигнал с выхода триггера 15 поступает на выход 19 и участвует в образовании результатов операции в последующих модулях. Через интервал времени, равный времени переключения мультиплексоров 3 и 4, результат операции устанавливается на

асинхронных выходах 6 и 7. По фронту тактового импульса, поступакицего с входа 17 через открытый элемент И 16 на вход синхронизации триггеров 1 и 2, происходит запись результата операции с выходов б и 7 в триггеры 1 и 2. Этот результат поступает на выходы Г2 и 13.

При реализации операций второй группы сигнал на входе 18 всегда равен логическому О и в каждом такте машинного времени (аналогично выше рассмотренному), формируются результаты операций, задаваемых кодом на группе 5 входов. Поскольку большая часть арифметико-логических операций реализуется без учета переноса, то быстродействие данного модуля практически равно быстродействию известного модуля при сохранении тех же функциональных возможностей.

При последовательном соединении нескольких многофункциональных модулей для образования многоразрядного вычислителя выход 12 каждого после дуюадего модуля должен соединяться с входом 11 предыдущего модуля для образования цепи переноса вправо.

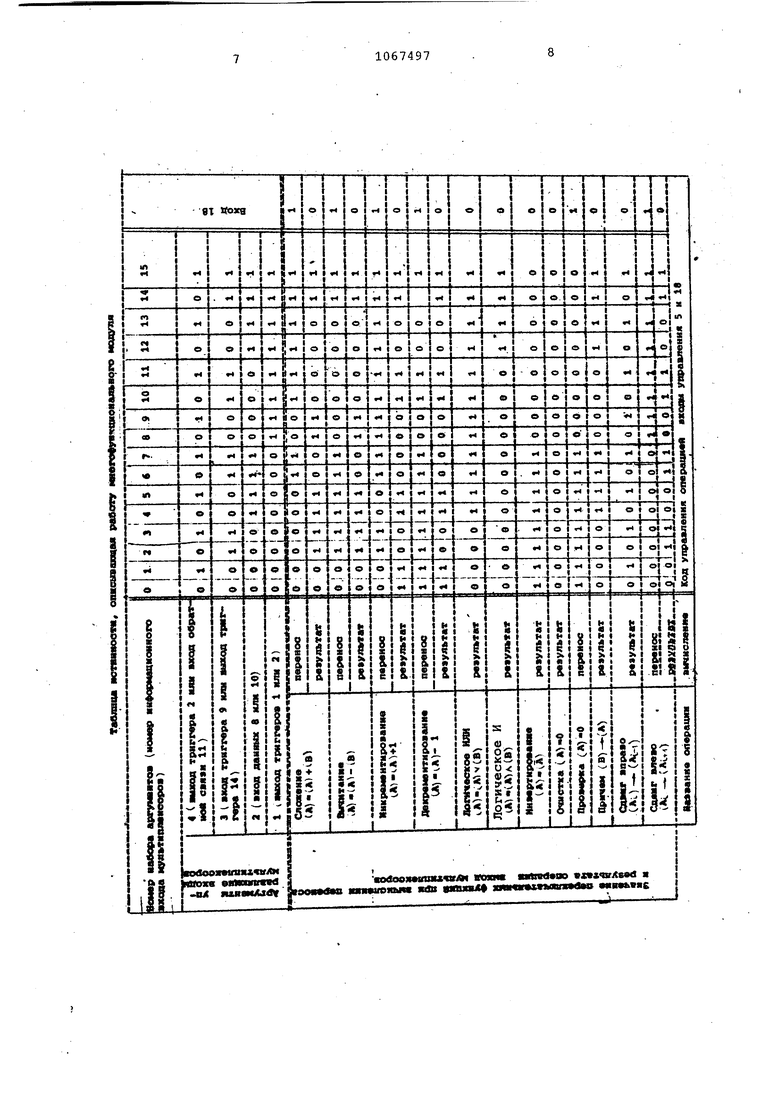

Таблица истинности, описывающая работу многофункционального модуля в режимах формирования сигналов переноса и выполнения основных операцИй с учетом всех информационных и управляющих входов мультиплексоров, поступающий через группы 5, входов на информационные входы мультиплексоров 3 и 4 в режимах формирования сигналов переноса и выполнения основной операции, однозначно совпадает со значениями соответстдующих переключательных функций на соответствующих наборах аргументов. Исходя

из этого очевидно, что определяя значения этих переключательных функций на всех наборах в соответствии с требуемой для реализации операцией, легко определить код управления на группе 5, необходимый для выполнения этой операции.

Коды управления операциями, приведенные в таблице, получены из предположения, что первый управляниций вход мультиплексоров,имеет вес 2, второй , третий 2 , четвертый 2 . При этом символом А обозначено состояние триггеров 1 и 2 нулевого и первого разрядов, число на входах 8 и 10.

Временные диаграммы, поясняннцие работу модуля в режимах (тактах) формирования сигналов переноса и выполнения основной операции, приведены на фиг.2. При этом предполагается, что входные сигналы, поступающие на вход 9 и вход 11, формируются аналогичными по выполнению предыдущим и последующим многофункциональньоми модулями.

Таким образом, предлагаегллй многофункциональный модуль при сохранении функциональных возможностей и быстродействия известного модуля требует для реализации почти вдвое меньших аппаратурных затрат (за счет исключения мультиплексоров для вычисления переноса) и почти вдвое меньшего количества внешних выводов (27 вместо 44 в известном модуле). Это существенно расширяет возможности его микроэлектронной реализации в виде интегральной микросхемы и определяет широкую область использования при построении различных вычислительных устройств.

f2

8

Фиг.1

Такто8ые импмьсы

бходп -

ипкгВмния

J npaS/} №Ufw 8x0 IS

Sxodll

оереноса

6xo 6iSu6 даннь/х

Bifxod

i bmufiflCKCofa

&шод1

триггера ff

Вшо -Hi/a m/fffleffCfffa

Вшод1

триггера Т7

Bbixod /fMCf/ma и 1в

t2

ш

Sffafffi/Bu л

ji/

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль | 1984 |

|

SU1238098A1 |

| Многофункциональное устройство | 1988 |

|

SU1520503A1 |

| Микропроцессорный модуль | 1979 |

|

SU894714A1 |

| Арифметико-логический модуль | 1980 |

|

SU962916A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1109735A1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

| Арифметико-логический модуль | 1988 |

|

SU1501032A1 |

| Ячейка однородной вычислительной среды | 1987 |

|

SU1594519A1 |

| Устройство для вычисления функций синуса и косинуса | 1986 |

|

SU1478213A1 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ МОДУЛЬ, содержащий триггеры нулевого и первого разрядов, первый и второй мультиплексоры, информационные входы которых соединены с группой управляюи их входов модуля, выхода первого и второго мультиплексоров подключены к информационным входам триггеров нулевого и первого разрядов соответственно, а также к асинхронным выходам данных нулевого и первого ра-з рядов модуля, первый, второй, третий и четвертый управляющие входы первого / мультиплексора соединены соответственно с выходом триггера нулевого разряда, входом данных нулевогоразряда модуля, входом переноса модуля и выходом триггера первого разряда, первый, второй и третий управляющие входы втррого мультиплексора подключены соответственно к выходу триггера первого разряда, входу данных первого разряда модуля и входу обратной связи модуля, при этом выходы триггеров нулевого и первого разрядов соединены с выхсщс1ми данных нулевого и первого разрядов модуля соответственно, отличающийся тем, что, с целью упрощения модуля и сокращения количества внешних выводов, он содержит нервый и второй Ь -триггеры и элемент И, первый и второй входы и выход которого подключены соответственно к тактовому и управ- .i «Л ляющему входам модуля и входам синхронизации триггеров нулевого и первого разрядов, информационные входы первого и второго И -триггеров соединены с выходги и соответственно ; первого и второго мультиплексоров, входы синхронизации 1) -триггеров пoдкJaoчeны к управляюцему входу мо- , дуля, а внкоды первого и второго . | 1)-триггеров соединены соответствено а: но с четвёртым управляшцим входом f второго мультиплексора и выходом пек реноса модуля. 4 СО |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Радиально-упорный подшипниковый узел | 2021 |

|

RU2771989C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СОЕДИНИТЕЛЬНАЯ МУФТА С РАЗОМКНУТЫМ ИНТЕРФЕРОМЕТРОМ С ДВУМЯ ПЛЕЧАМИ ДЛЯ ИЗВЕЩАТЕЛЯ ОХРАННОГО ВОЛОКОННО-ОПТИЧЕСКОГО | 2020 |

|

RU2786482C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-15—Публикация

1981-07-17—Подача