-.30

Изобретение относится к запоминающим устройствам и может быть использовано в линиях задержки цифровой информации.

Цель изобретения - повьпиение надежности устройства.

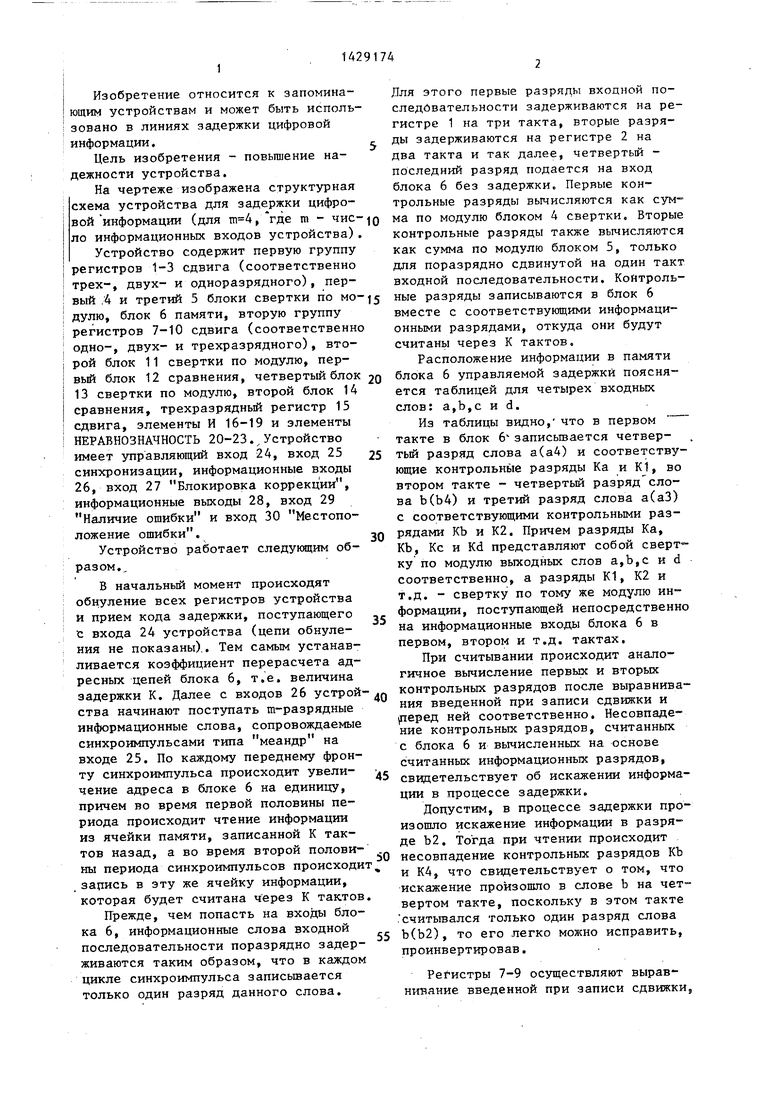

На чертеже изображена структурная схема устройства для задержки цифровой информации (для ,где m - число информационных входов устройства)

Устройство содержит первую группу регистров 1-3 сдвига (соответственно трех-, двух- и одноразрядного), первый .4 и третий 5 блоки свертки по модулю, блок б памяти, вторую группу регистров 7-10 сдвига (соответственн одно-, двух- и трехразрядного), второй блок 11 свертки по модулю, пер- вьй блок 12 сравнения, четвертый блок 13 свертки по модулю, второй блок 14 сравнения, трехразрядный регистр 15 сдвига, элементы И 16-19 и элементы НЕРАВНОЗНАЧНОСТЬ 20-23. Устройство имеет управляющий вход 24, вход 25 синхронизации, информационные входы 26, вход 27 Блокировка коррекции, информационные выходы 28, вход 29 Наличие ошибки и вход 30 Местоположение ошибки.

Устройство работает следующим образом,,

В начальный момент происходят обнуление всех регистров устройства и прием кода задержки, поступающего х: входа 24 устройства (цепи обнуления не показаны).. Тем самьм устанавливается коэффициент перерасчета адресных цепей блока 6, т.е. величина задержки К. Далее с входов 26 устройства начинают поступать т-разрядные информационные слова, сопровождаемые синхроимпульсами типа меандр на входе 25. По каждому переднему фронту синхроимпульса происходит увеличение адреса в блоке 6 на единицу, причем во время первой половины периода происходит чтение информации из ячейки памяти, записанной К тактов назад, а во время второй половины периода синхроимпульсов происходи запись в эту же ячейку информации, которая будет считана ч ерез К тактов

Прежде, чем попасть на входы блока 6, информационные слова входной последовательности поразрядно задерживаются таким образом, что в каждом цикле синхроимпульса записьюается только один разряд данного слова.

Для этого первые разрядь входной по- следйвательности задерживаются на регистре 1 на три такта, вторые разря- ды задерживаются на регистре 2 на два такта и так далее, четвертый - последний разряд подается на вход блока 6 без задержки. Первые контрольные разряды вычисляются как сум0 ма по модулю блоком 4 свертки. Вторые контрольные разряды также вьтисляются как сумма по модулю блоком 5, только для поразрядно сдвинутой на один такт входной последовательности. КоНтроль5 ные разряды записываются в блок 6 вместе с соответствующими информационными разрядами, откуда они будут считаны через К тактов.

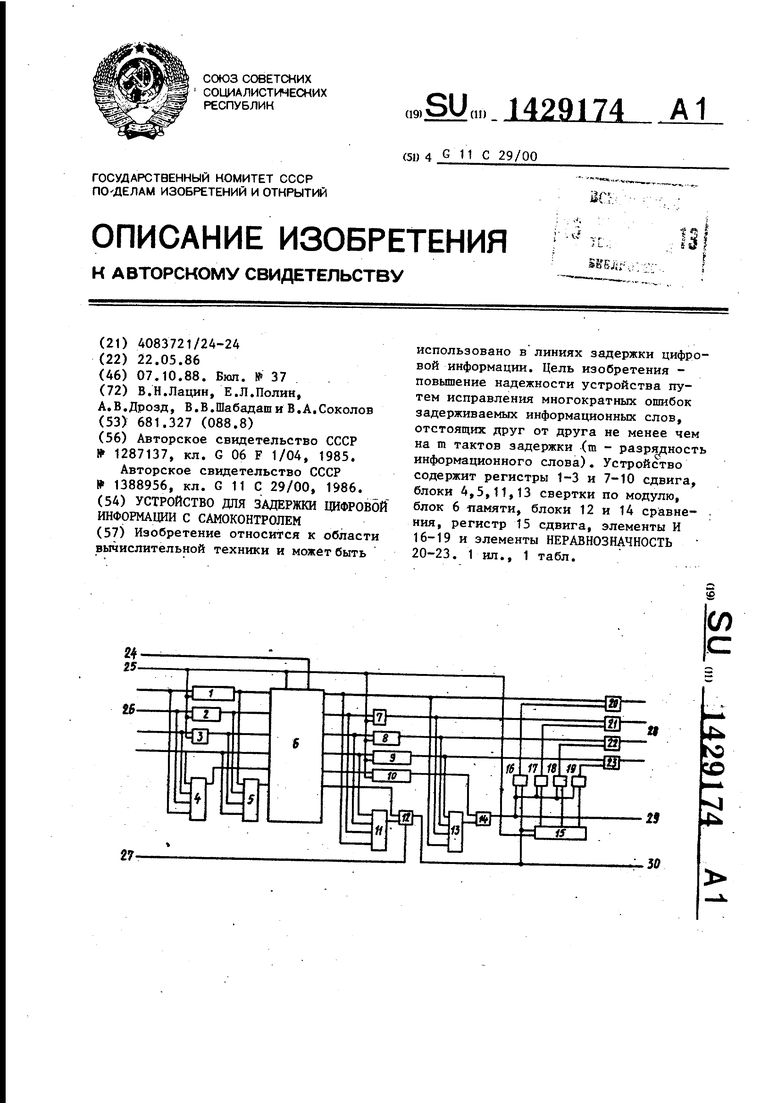

Расположение информации в памяти

0 блока 6 управляемой задержки поясняется таблицей для четырех входных слов: а,Ь,с и d.

Из таблицы видно, что в первом такте в блок 6 записьшается четвер5 тый разряд слова а(а4) и соответствующие контрольные разряды Ка и К1, во втором такте - четвертый разряд слова Ь(Ь4) и третий разряд слова а(аЗ) с соответствующими контрольными раз0 рядами Kb и К2. Причем разряды Ка, Kb, Кс и Kd представляют собой свертку по модулю выходных слов а,Ь,с и d соответственно, а разряды К1, К2 и т.д. - свертку по тому же модулю информации, поступающей непосредственно на информационные входы блока 6 в первом, втором и т.д. тактах.

При считывании происходит аналогичное вычисление первых и вторых контрольных разрядов после выравнивания введенной при записи сдвижки и ртеред ней соответственно. Несовпадение контрольных разрядов, считанных с блока 6 и вычисленных на основе считанных информационных разрядов,

5 свидетельствует об искажении информации в процессе задержки.

Додустим, в процессе задержки произошло искажение информации в разряде Ь2. Тогда при чтении происходит

0 несовпадение контрольных разрядов Kb

и К4, что сввдетельствует о том, что искажение произошло в слове b на четвертом такте, поскольку в этом такте . считывался только один разряд слова

5 Ь(Ь2), то его легко моясно исправить, проинвертировав.

Регистры 7-9 осуществляют выравнивание введенной при записи сдвижки.

5

0

регистр 10 выравнивает считанные первые контрольные разряды с соответствующими им информационными словами. Блоки 11 и 13 вычисляют свертку по модулю считанной с блока 6 и выравненной информации, определяя вторые и первые контрольные разряды соответственно. Факты несовпадения первых и вторых контрольных разрядов проявля- ются на выходах блоков 14 и 12 сравнения в виде сигналов логической единицы. Сигналы о совпадении вторых контрольных разрядов с выхода блока 12 поступают на вход регистра 15, где осуществляется их задержка на три такта. При этом, как только на выходе блока 14 появляется сигнал о несовпадении первых контрольных разрядов (логическая единица на выходе блока 14), соответствующий элемент И 16-19 переводит свой выход в состояние логической единицы переводя подключенный к его выходу элемент НЕРАВНОЗНАЧНОСТЬ в режим инвертирования. Сбойный разряд, поступающий с регистров 7-9 или первого информационного выхода блока 6, будет проинвертирован. Подавая на вход 27 устройства сигнал блокировки, можно запретить коррекцию, принудительно устанавливая на выходе блока 12 сигнал логического нуля. После того, как этот логический нуль заполнит все разряды регистра 15, выходы элементов И 16-19 удерживаются

в состоянии логического нуля, запрещая инвертирование информации. При этом на информационньш вход устройства поступает нескорректированная информация, сопровождаемая сигналами

об ошибке на входе 29 устройства.

Формула изобретения

Устройство для задержки цифровой информации с самоконтролем, содержа- щее блок памяти, первый и второй блок свертки по модулю, первьй и второй блоки сравнения, причем входы первого блока свертки по модулю являются информационными входами устройства, выход первого блока свертки по модулю подключен к входу первого контрольного разряда блока памяти, вход синхронизации и управляющий вход блока памяти являются соответственно входом синхронизации и управляющим входом устройства, первый информационный вход первого блока сравнения подключен к выходу второго контрольного

0 5 0 5 o

с

0

5 0 е

разряда блока памяти, второй информационный вход блока сравнения соединен с выходом второго блока свертки по модулю, входы которого подключены к выходам информационных разрядов блока памяти, вход последнего информационного разряда блока памяти подключен к соответствующему информационному входу устройства, отличающееся тем, что, с целью повьшения надежности устройства, в него введены первая и вторая группы регистров сдвига, третий и четвертый блоки свертки по модулю, регистр сдвига, элементы И и элементы неравнозначности, причем информационные входы регистров сдвига первой группы подключены к информационным входам устройства, кроме последнего, выходы регистров сдвига первой группы соединены с входами информационных разрядов блока памяти, кроме последнего, один из входов тре тьего блока свертки по модулю соединен с последним информационным входом устройства, другие входы третьего блока свертки по модулю подключены к выходам регистров сдвига первой группы, выходы информационных разрядов блока памяти, кроме первого информационного разряда, и выход первого контрольного разряда блока памяти подключены к информационным входам регистров сдвига группы, выход первого информационного разряда блока памяти и выходы регистров сдвига второй группы, кроме последнего регистра

сдвига, соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ, вторые входы которых подключены к выходам элементов И, выходы элементов НЕРАВНОЗНАЧНОСТЬ являются информационными выходами устройства, первый и второй входы второго блока сравнения подключены соответственно к выходам по следне- го регистра сдвига второй группы и четвертого блока свертки по модулю, выход второго блока сравнения соединено первыми входами элементов И, второй вход одного из элементов И и информационный вход регистра сдвига подключенык выходу первого блока сравнения, вторые входы других элементов И соединены с выходами разрядов регистра сдвига, входы синхронизации регистров сдвига подключены к входу синхронизации устройства, выходы второго и первого блоков сравнения являются соответственно выходом Наличие ощибки и вы5 2 6

ходом Местоположение ошибки устрой- Сравнения является входом Блокиров- ства, управляющий вход первого блока «а коррекции устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Запоминающее устройство с обнаружением ошибок | 1986 |

|

SU1425787A1 |

| Коррелометр | 1980 |

|

SU1062717A1 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

Изобретение относится к области вычислительной техники и может быть использовано в линиях задержки цифровой информации. Цель изобретения - повышение надежности устройства путем исправления многократных ошибок задерживаемых информационных слов, отстоящих друг от друга не менее чем на m тактов задержки (т - разря ность информационного слова). Устройство содержит регистры 1-3 и 7-10 сдвига, блоки 4,5,11,13 свертки по модулю, блок 6 памяти, блоки 12 и 14 сравне- . ния, регистр 15 сдвига, элементы И 16-19 и элементы НЕРАВНОЗНАЧНОСТЬ 20-23. 1 шт., 1 табл.

Разряд

ETEinnilLin

о о о

К7

с1

О О

Кб

Номер такта

a1 Ь2 сЗ

Kd

К4

О

а2

ЬЗ

с4

О О аЗ Ь4

Кс Kb

КЗ К2

О О О а4

Ка К1

| Устройство для задержки информации | 1985 |

|

SU1287137A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Блок задержки цифровой информации с самоконтролем | 1986 |

|

SU1388956A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-07—Публикация

1986-05-22—Подача