Изобретение относится к вычислительной технике и предназначено для использования в устройствах регистрации цифровой информации на магнитном носителе.

Цель изобретения - повышение достоверности счлтываемой информации при увеличении поперечной плотности записи.

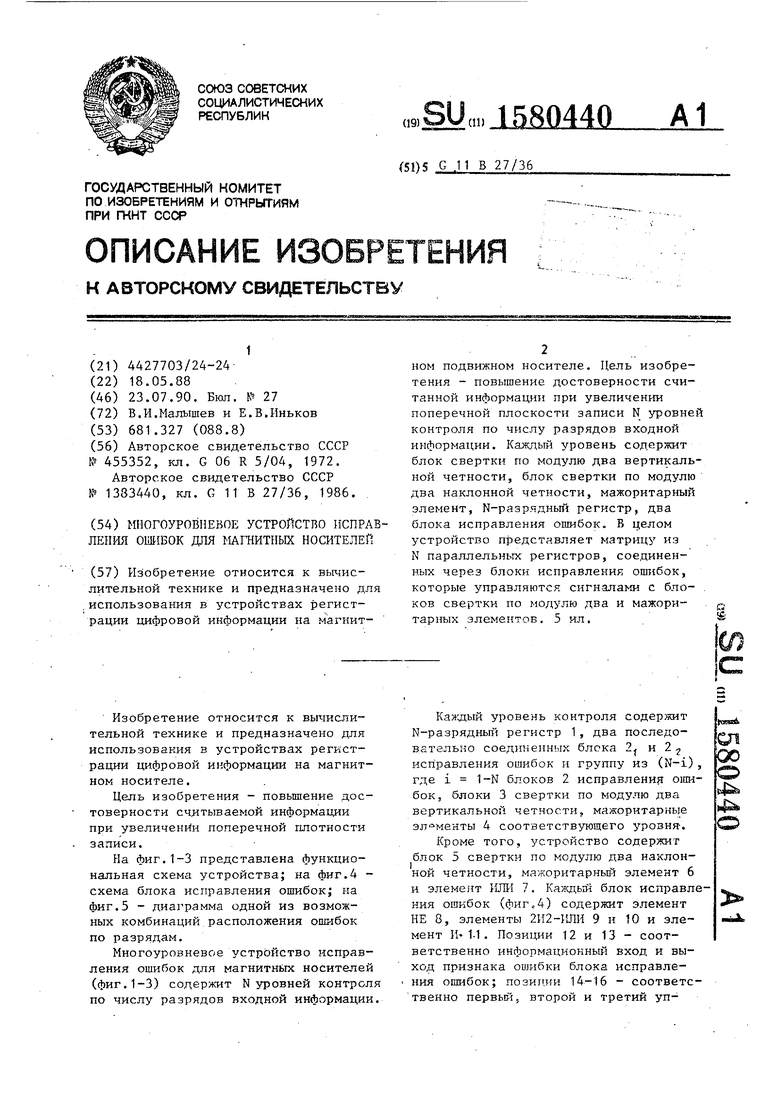

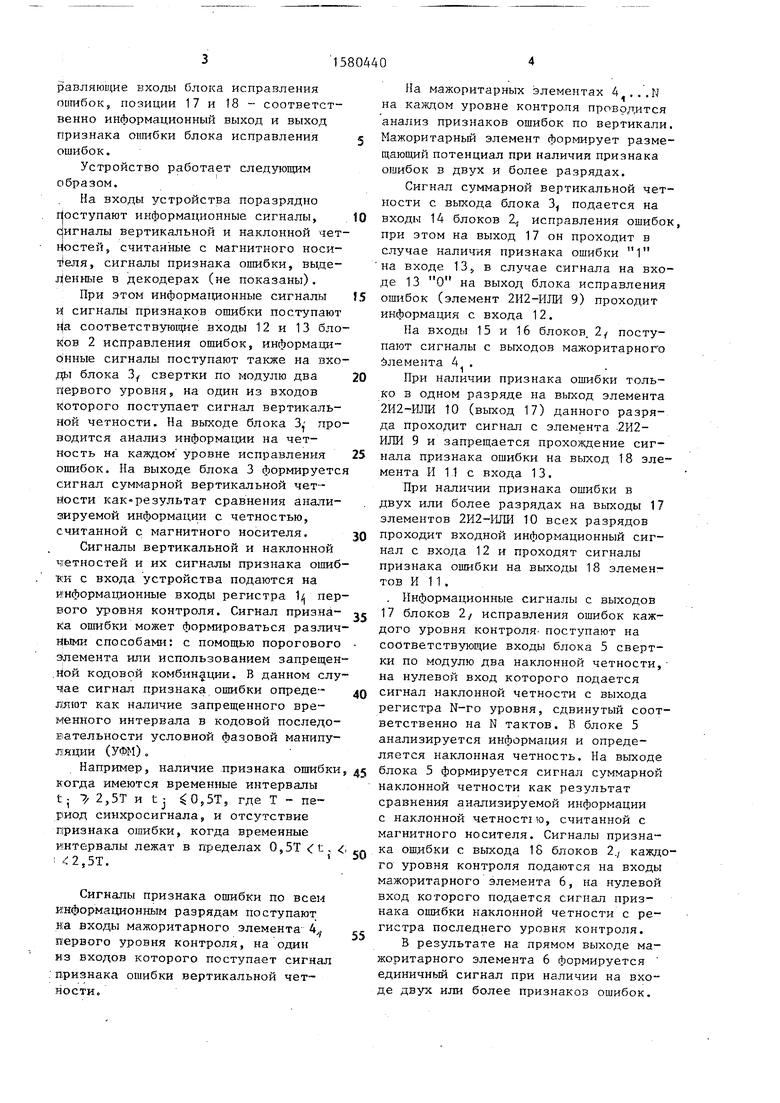

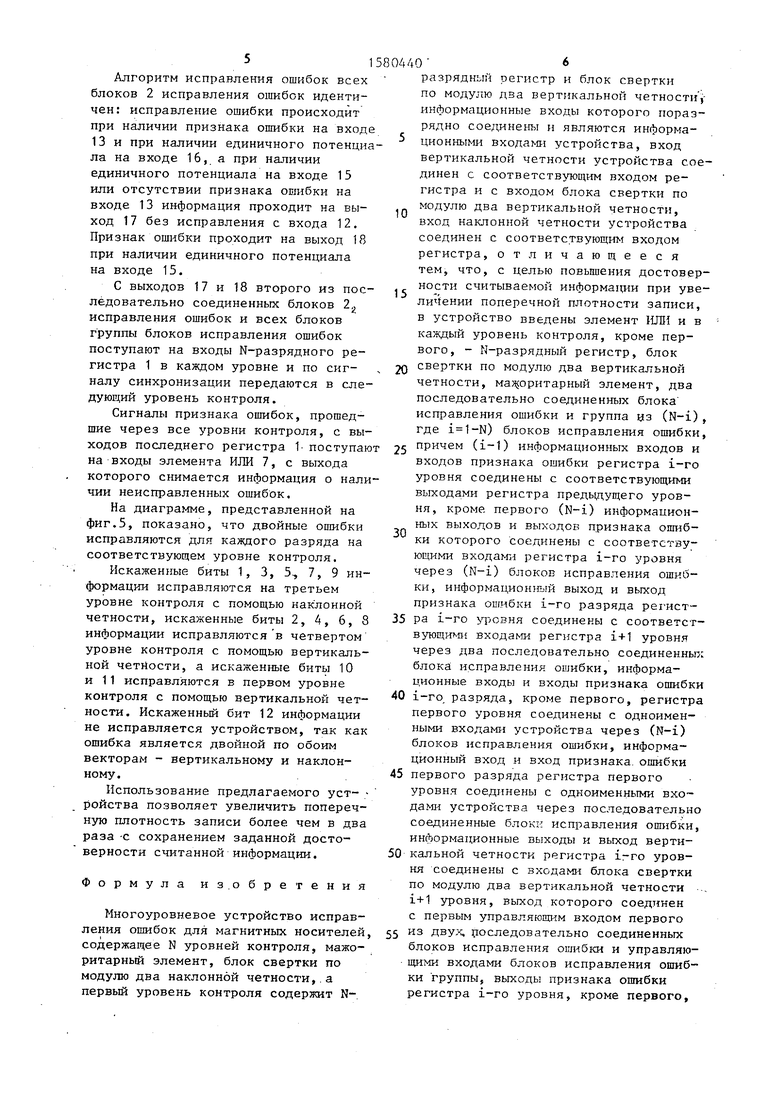

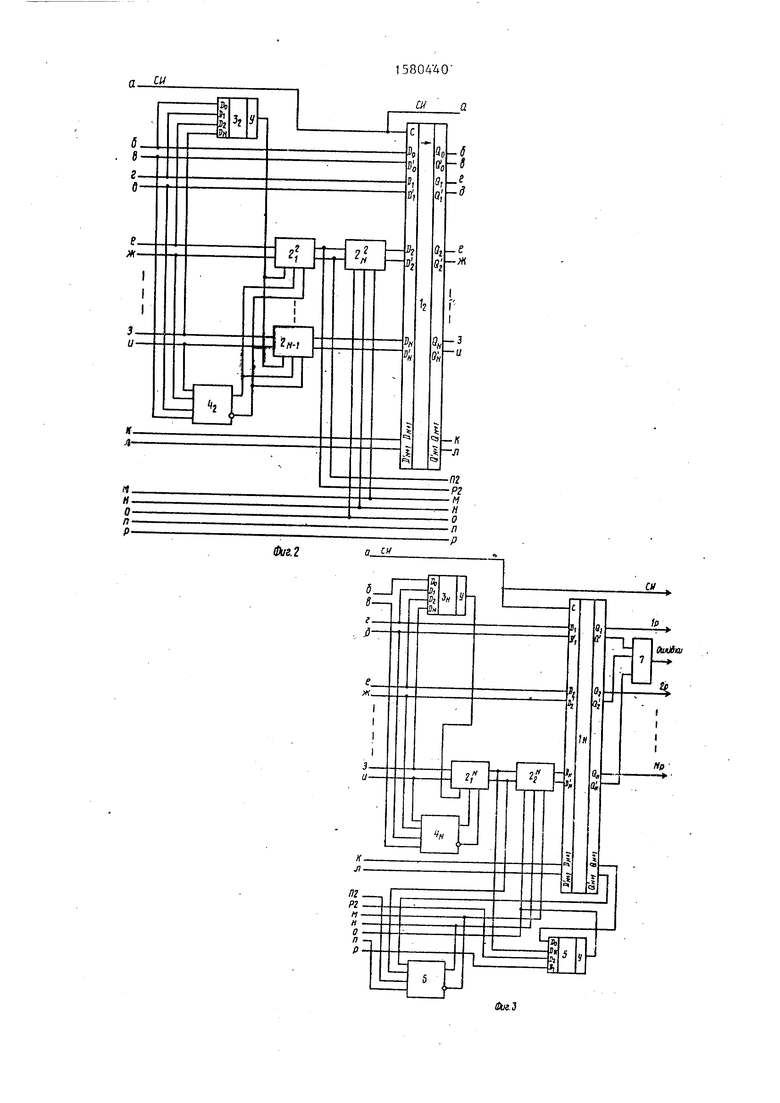

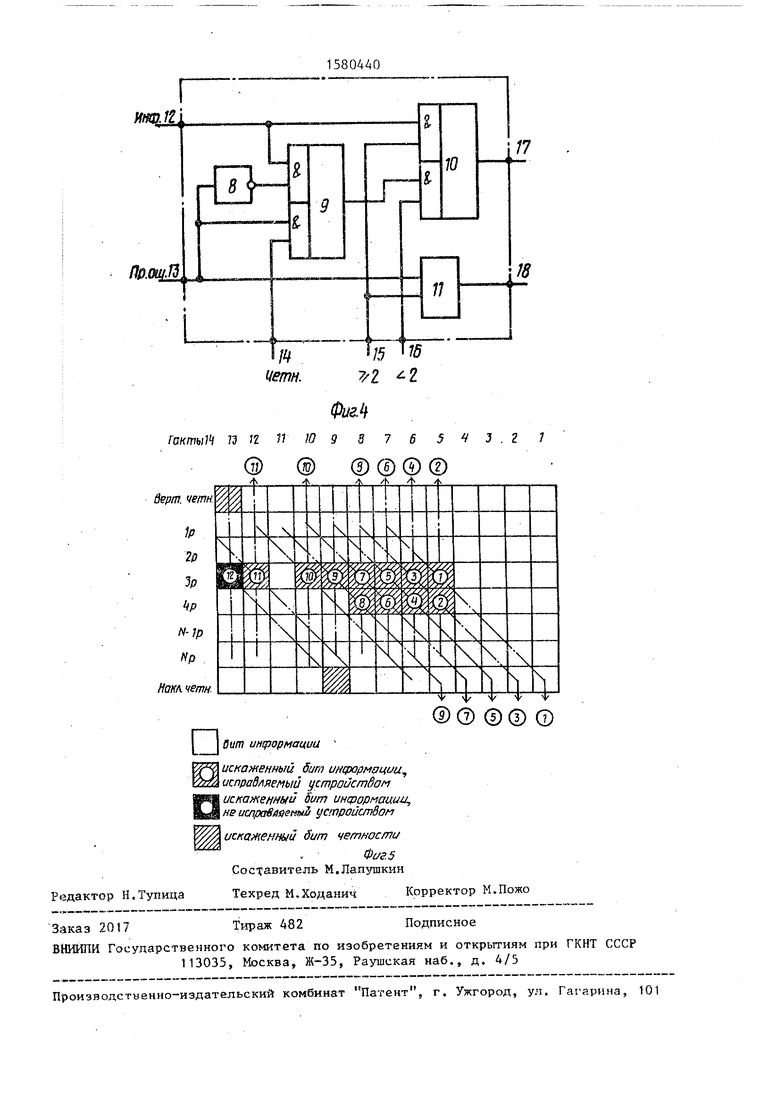

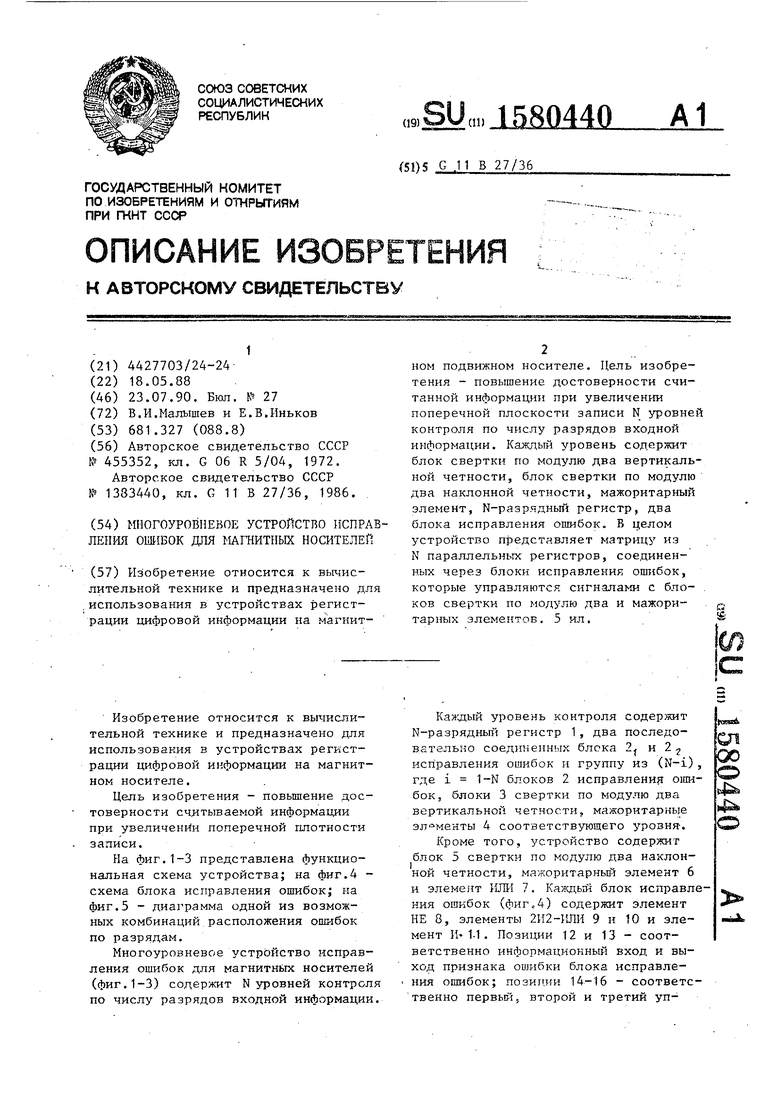

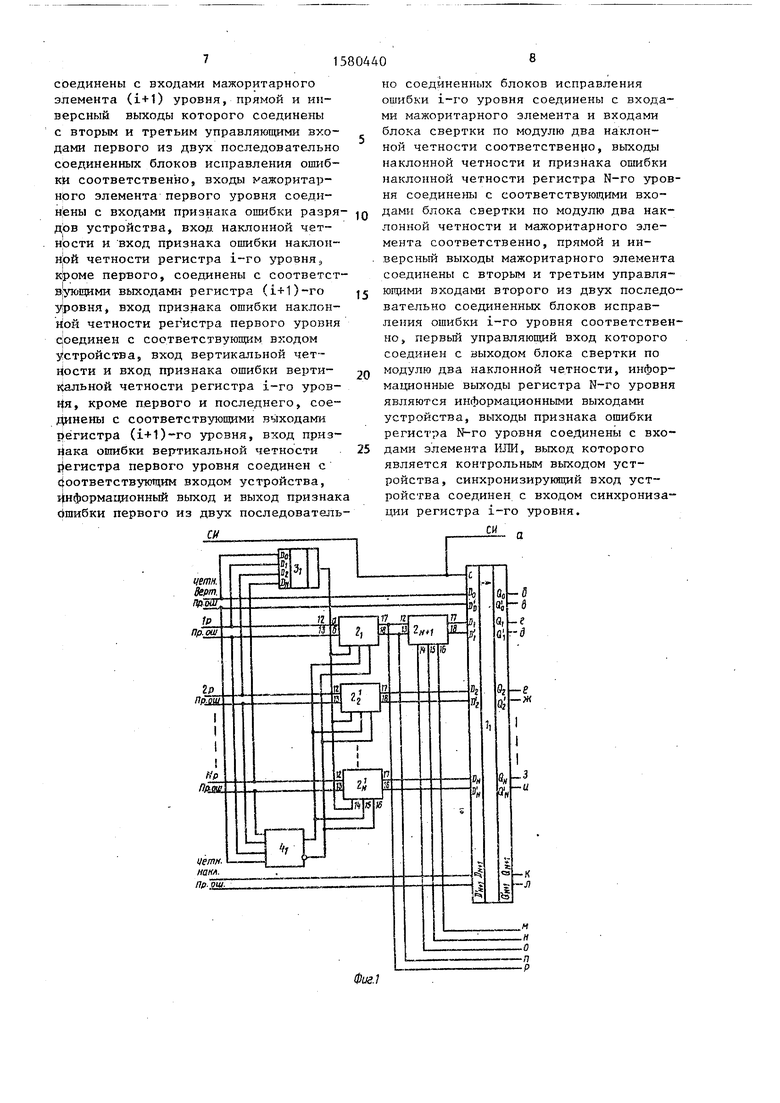

На фиг.1-3 представлена функциональная схема устройства; на фиг.4 - схема блока исправления ошибок; па фиг.5 - диаграмма одной из возможных комбинаций расположения ошибок по разрядам.

Многоуровневое устройство исправления ошибок для магнитных носителей (фиг.1-3) содержит N уровней контроля по числу разрядов входной информации.

Каждый уровень контроля содержит N-разрядный регистр 1, два последовательно соединенных блока 2 и 22 исправления ошибок и группу из (), где i 1-N блоков 2 исправления ошибок, блоки 3 свертки по модулю два вертикальной четности, мажоритарные элементы 4 соответствующего уровня-.

Кроме того, устройство содержит блок 5 свертки по модулю два наклонной четности, мажоритарный элемент 6 и элемент ИЛИ 7. Каждый блок исправления ошибок (фиг.,4) содержит элемент НЕ 8, элементы 2И2-ИЛИ 9 и 10 и элемент И-1-1 . Позиции 12 и 13 - соответственно информационный вход и выход признака ошибки блока исправления ошибок; позипни 14-16 - соответственно первый5 второй и третий уп00

равляющие входы блока исправления ошибок, позиции 17 и 18 - соответственно информационный выход и выход признака ошибки блока исправления ошибок.

Устройство работает следующим образом.

На входы устройства поразрядно поступают информационные сигналы, с|игналы вертикальной и наклонной qeT- йостей, считанные с магнитного носителя, сигналы признака ошибки, выделенные в декодерах (не показаны).

При этом информационные сигналы И сигналы признаков ошибки поступают на соответствующие входы 12 и 13 блоков 2 исправления ошибок, информационные сигналы поступают также на входы блока 3/ свертки по модулю два Первого уровня, на один из входов которого поступает сигнал вертикаль- Ной четности. На выходе блока 3,- проводится анализ информации на четность на каждом уровне исправления ошибок. На выходе блока 3 формируется сигнал суммарной вертикальной чет-- Ности как-результат сравнения анализируемой информации с четностью, считанной с магнитного носителя,

Сигналы вертикальной и наклонной четностей и их сигналы признака ошибки с входа устройства подаются на информационные входы регистра 1 первого УРОВНЯ КОНТРОЛЯ. СиГНаЛ ПрИЗНЭ-

ка ошибки может формироваться различными способами: с помощью порогового элемента или использованием запрещенной кодовой комбинации. В данном случае сигнал признака ошибки опреде- гдаот как наличие запрещенного временного интервала в кодовой последовательности условной фазовой манипуляции (УФМ)„

Например, наличие признака ошибки, когда имеются временные интервалы t- / 2,5Т и tj Ј0,5T5 где Т - период синхросигнала, и отсутствие признака ошибки, когда временные интервалы лежат в пределах 0,5Т t, 1 -i2,5T.

Сигналы признака ошибки по всем информационным разрядам поступают на входы мажоритарного элемента 4 первого уровня контроля, на один нз входов которого поступает сигнал признака ошибки вертикальной четности.

5 0 5 Q

е

0

0

5

На мажоритарных элементах 4 ...N на каждом уровне контропя проводится анализ признаков ошибок по вертикали. Мажоритарный элемент формирует размещающий потенциал при наличии признака ошибок в двух и более разрядах.

Сигнал суммарной вертикальной четности с выхода блока 31 подается на входы 14 блоков 2., исправления ошибок, при этом на выход 17 он проходит в случае наличия признака ошибки 1 на входе 13,, в случае сигнала на входе 13 О на выход блока исправления ошибок (элемент 2И2-ИЛИ 9) проходит информация с входа 12.

На входы 15 и 16 блоков, 2/ поступают сигналы с выходов мажоритарного элемента 4 .

При наличии признака ошибки только в одном разряде на выход элемента 2И2-ИЛИ 10 (выход 17) данного разряда проходит сигнал с элемента 2И2- ИЛИ 9 и запрещается прохождение сигнала признака ошибки на выход 18 элемента И 11 с входа 13.

При наличии признака ошибки в двух или более разрядах на выходы 17 элементов 2И2-ИЛИ 10 всех разрядов проходит входной информационный сигнал с входа 12 и проходят сигналы признака ошибки на выходы 18 элементов И 11 .

. Информационные сигналы с выходов 17 блоков 2/ исправления ошибок каждого уровня контроля поступают на соответствующие входы блока 5 свертки по модулю два наклонной четности, на нулевой вход которого подается сигнал наклонной четности с выхода регистра N-ro уровня, сдвинутый соответственно на N тактов. В блоке 5 анализируется информация и определяется наклонная четность. На выходе блока 5 формируется сигнал суммарной наклонной четности как результат сравнения анализируемой информации с наклонной четностхю, считанной с магнитного носителя. Сигналы признака ошибки с выхода 18 блоков 2./ каждого уровня контроля подаются на входы мажоритарного элемента 6, на нулевой вход которого подается сигнал признака ошибки наклонной четности с регистра последнего уровня контроля.

В результате на прямом выходе мажоритарного элемента 6 формируется единичный сигнал при наличии на входе двух или более признаков ошибок.

Алгоритм исправления ошибок всех блоков 2 исправления ошибок идентичен: исправление ошибки происходит при наличии признака ошибки на входе 13 и при наличии единичного потенциала на входе 16, а при наличии единичного потенциала на входе 15 или отсутствии признака ошибки на входе 13 информация проходит на выход 17 без исправления с входа 12. Признак ошибки проходит на выход 18 при наличии единичного потенциала на входе 15.

С выходов 17 и 18 второго из последовательно соединенных блоков 2,, исправления ошибок и всех блоков группы блоков исправления ошибок поступают на входы N-разрядного регистра 1 в каждом уровне и по сигналу синхронизации передаются в следующий уровень контроля.

Сигналы признака ошибок, прошедшие через все уровни контроля, с выходов последнего регистра 1 поступаю на входы элемента ИЛИ 7, с выхода которого снимается информация о наличии неисправленных ошибок,

На диаграмме, представленной на фиг.5, показано, что двойные ошибки исправляются для каждого разряда на соответствующем уровне контроля.

Искаженные биты 1, 3, 5, 7, 9 информации исправляются на третьем уровне контроля с помощью наклонной четности, искаженные биты 2, 4, 6, 3 информации исправляются в четвертом уровне контроля с помощью вертикальной четности, а искаженные биты 10 и 11 исправляются в первом уровне контроля с помощью вертикальной четности. Искаженный бит 12 информации не исправляется устройством, так как ошибка является двойной по обоим векторам - вертикальному и наклонному.

Использование предлагаемого уст- - ройства позволяет увеличить поперечную плотность записи более чем в два раза -с сохранением заданной достоверности считанной информации.

Формула изобретения

Многоуровневое устройство исправления ошибок для магнитных носителей содержащее N уровней контроля, мажоритарный элемент, блок свертки по модулю два наклонной четности, а первый уровень контроля содержит N

5

0

разрядный оегистр и блок свертки по модулю два вертикальной четности информационные входы которого поразрядно соединены и являются информационными входами устройства, вход вертикальной четности устройства соединен с соответствующим входом регистра и с входом блока свертки по модулю два вертикальной четности, вход наклонной четности устройства соединен с соответствующим входом регистра, отличающееся тем, что, с целью повышения достоверности считываемой информации при увеличении поперечной плотности записи, в устройство введены элемент ИЛИ и в каждый уровень контроля, кроме первого, - N-разрядный регистр, блок свертки по модулю два вертикальной четности, мажоритарный элемент, два последовательно соединенных блока исправления ошибки и группа из (N-i), где ) блоков исправления ошибки,

5 причем (i-1) информационных входов и входов признака ошибки регистра 1-го уровня соединены с соответствующими выходами регистра предыдущего уровня, кроме первого (N-i) информационных выходов и выходов признака ошибки которого соединены с соответствующими входами регистра 1-го уровня через (N-i) блоков исправления ошибки, информационный выход и выход признака ошибки i-ro разряда регистра i-ro уровня соединены с соответствующими входами регистра i+1 уровня через два последовательно соединенных блока исправления ошибки, информационные входы и входы признака ошибки i-ro разряда, кроме первого, регистра первого уровня соединены с одноименными входами устройства через (N-i) блоков исправления ошибки, информационный вход и вход признака ошибки

5 первого разряда регистра первого

уровня соединены с одноименными вхо дами устройства через последовательно соединенные блокг исправления ошибки, инАормационные выходы и выход вертикальной четности регистра 1-го уровня соединены с входами блока свертки по модулю два вертикальной четности i+1 уровня, выход которого соединен с первым управляющим входом первого из двух, последовательно соединенных блоков исправления ошибки и управляющими входами блоков исправления ошибки группы, выходы признака ошибки регистра i-ro уровня, кроме первого,

0

5

0

0

5

соединены с входами мажоритарного элемента (i+1) уровня, прямой и инверсный выходы которого соединены с вторым и третьим управляющими входами первого из двух последовательно соединенных блоков исправления ошибки соответственно, входы мажоритарного элемента первого уровня соединены с входами признака ошибки разрядов устройства, вход наклонной четности и вход признака ошибки наклонной четности регистра 1-го уровняэ кроме первого, соединены с соответст- в ующими выходами регистра (i-H)-ro уровня, вход признака ошибки наклонной четности регистра первого уровня соединен с соответствующим входом устройства, вход вертикальной четности и вход признака ошибки вертикальной четности регистра 1-го уров- Ня, кроме первого и последнего, соединены с соответствующими выходами регистра (i+1)-ro уровня, вход приз- йака ошибки вертикальной четности регистра первого уровня соединен с Соответствующим входом устройства, Информационный выход и выход признак Ошибки первого из двух последователь

5

0

5

но соединенных блоков исправления ошибки 1-го уровня соединены с входами мажоритарного элемента и входами блока свертки по модулю два наклонной четности соответственно, выходы наклонной четности и признака ошибки наклонной четности регистра N-го уровня соединены с соответствующими входами блока свертки по модулю два наклонной четности и мажоритарного элемента соответственно, прямой и инверсный выходы мажоритарного элемента соединены с вторым и третьим управляющими входами второго из двух последовательно соединенных блоков исправления ошибки 1-го уровня соответственно, первый управляющий вход которого соединен с выходом блока свертки по модулю два наклонной четности, информационные выходы регистра N-ro уровня являются информационными выходами устройства, выходы признака ошибки регистра N-ro уровня соединены с входами элемента ИЛИ, выход которого является контрольным выходом устройства, синхронизирующий вход устройства соединен с входом синхронизации регистра 1-го уровня.

Фиг.

nl1l09876S4321

65) ® 0 0 ©

AL /К /t .у

I

I I Вит информации ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

| ДВУХУРОВНЕВОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК | 1992 |

|

RU2037891C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ОШИБОК ДЛЯ МАГНИТНЫХ НАКОПИТЕЛЕЙ | 1992 |

|

RU2037890C1 |

| Запоминающее устройство с коррекцией групповых ошибок | 1987 |

|

SU1481863A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1785041A1 |

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Устройство для исправления двух ошибок в кодовой комбинации с самоконтролем в системах контроля и передачи информации | 1984 |

|

SU1239721A1 |

| Устройство для дешифрации команд | 1987 |

|

SU1532932A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Многоканальное резервированное устройство | 1981 |

|

SU991628A1 |

Изобретение относится к вычислительной технике и предназначено для использования в устройствах регистрации цифровой информации на магнитном подвижном носителе. Цель изобретения - повышение достоверности считанной информации при увеличении поперечной плоскости записи N уровней контроля по числу разрядов входной информации. Каждый уровень содержит блок свертки по модулю два вертикальной четности, блок свертки по модулю два наклонной четности, мажоритарный элемент, N-разрядный регистр, два блока исправления ошибок. В целом устройство представляет матрицу из N параллельных регистров, соединенных через блоки исправления ошибок, которые управляются сигналами с блоков свертки по модулю два и мажоритарных элементов. 5 ил.

| Устройство для исправления ошибок при параллельном считывании двоичной информации | 1972 |

|

SU455352A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство исправления ошибок для магнитных накопителей | 1986 |

|

SU1383440A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-07-23—Публикация

1988-05-18—Подача