Изобретение относится к области вычислительной техники, а точнее к оптозлектронике и может быть использовано в устройствах для считывания, логико-арифметической обработки и хранения оптической информации.

Целью изобретения является повышение надежности ячейки за счет повышения пороговой чувствительности ячейки и расширение динамического диапазона входных оптических сигналов, а также расширение функциональных возможностей ячейки за счет обеспечения возможности ассоциативного поиска информации.

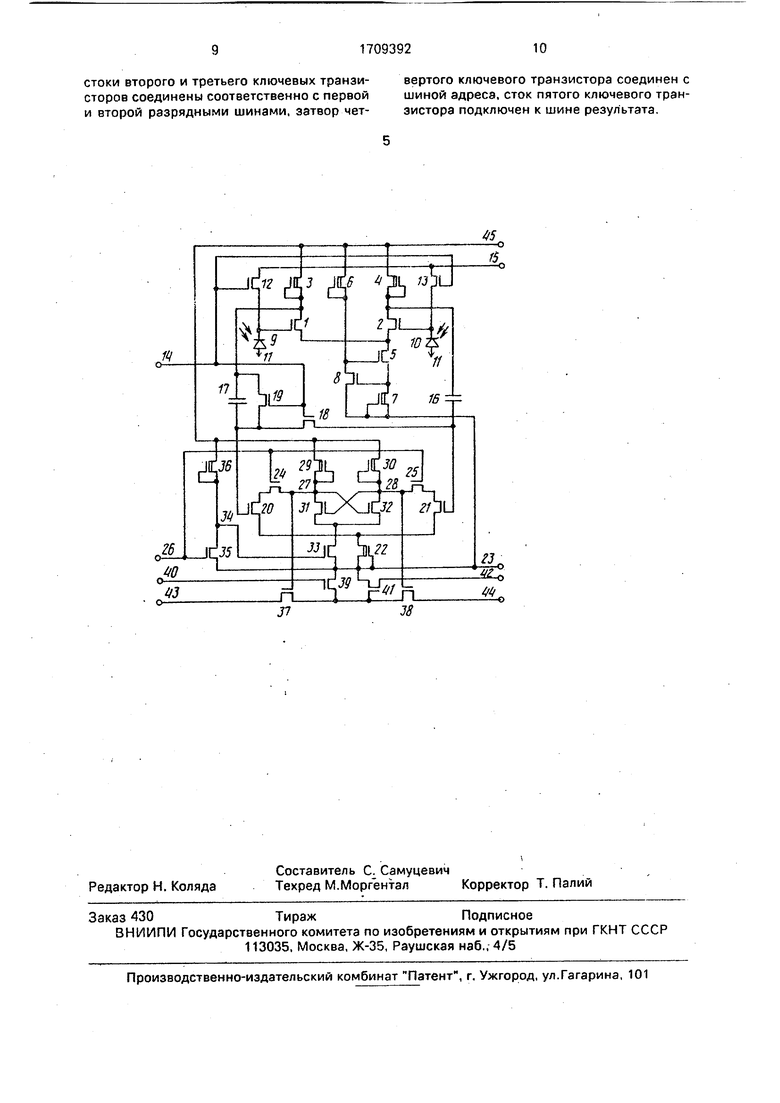

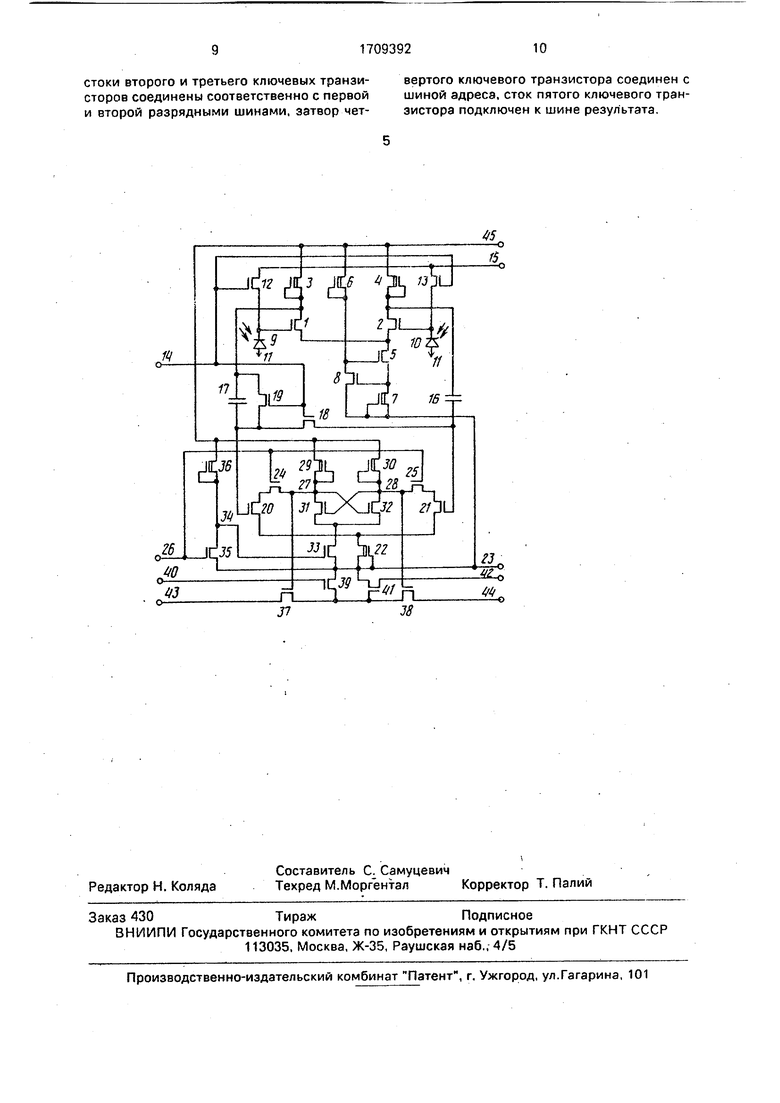

На чертеже представлена схема ячейки фоточувствительного матричного запоминающего устройства.

Ячейка содержит первый и второй усилительные транзисторы 1 и 2, первый и второй нагрузочные транзисторы 3 и 4, первый токостабилизирующий транзистор 5, шестой и седьмой нагрузочные транзисторы 6 и 7, седьмой усилительный транзистор 8, первый и второй фотодиоды 9 и 10, подложку 11 фотодиодов и транзисторов, первый и второй ключевые транзисторы стирания 12 и 13, шину стирания 14, источник смещения 15, первый и второй запоминающие конденсаторы 16 и 17, третий и четвертый транзисторы стирания 18 и 19, третий и четвертый усилительные транзисторы 20 и 21. второй токостабилизирующий транзистор 22. общую шину 23, первый и второй ключевые транзисторы записи 24 и 25, шину записи

26, информационные выходы 27 и28. третий и четвертый нагрузочные транзисторы 29 и 30, гтятый и шестой усилительные транзисторы 31 и 32, третий ключевой транзистор записи 33, инвертор 34, первый ключевой транзистор 35, пятый нагрузочный транзистор 36, второй, третий и четвертый ключевые транзисторы 37, 38 и 39, шину адреса 40, пятый ключевой транзистор 41, шину результата-42, первую и вторую разрядные шины 43 и44, шину питания 45.

Усилительные транзисторы 1 и 2, нагрузочные транзисторы 3 и 4, токсстабилизирующий транзистор 5 вместе с нагрузочным транзистором 7 образуют дифференциальный усилитель (ДУ),реЖим работы которого обеспечивается активной цепью из токостабилизирующего транзистора 5, нагрузочных транзисторов 6 и 7 и усилительного транзистора 8. Истоки усилительных транзисторов 1 м 2 соединены со стоком токостабилизирующего транзистора 5, исток которого подключен к стоку нагрузочного транзистора 7, затвору усилительного транзистора 8, а затвор к стоку усилительного транзистора 8, затвору и истоку нагрузочного транзистора 6. Фотодиоды 9 и 10 подсо8ди1 ень соответственно к затворам уси; -пельпыхтранзисторов 1 и 2, а другими одинчменными выводами к подложке 11. Затоорь ключевых транзисторов стирания 12- и 13 подключены к шине стирания 14, стоки к источнику смещения фотодиодов 15, а истоки соответственно к затворам усилительных TpaHst/iCTopOB 1 и 2; Между стоками усилительных транзисторов 1И 2 включена цепочка из последовательно соединенных запоминающего конденсатора 16, канала транзистора стирания 18 и канала транзистора стирания 19. Параллельно каналу транзи-. стора стирания 19, т.е. к стоку усилительного транзистора 1 и истоку транзистора стирания. 18, подключен запоминающий конденсатор 17. Затворы транзисторов стирания 18 и 19 соединены с шиной стирания 14. Сток и исток транзистора стирания 18 подключены соответственно к затвору усилительных транзисторов 20 и 21 дополнительного дифференциального усилителя, являющегося составной частью триггера-защелки..Истоки транзисторов 20 и 21 дополнительного ДУ соединены со стоком токостабилизирующего транзистора 22 этого усилителя, а затвор и исток токостабилизирующего транзистора 22 с общей шиной 23. Стоки усилительных транзисторов 20 121 соединены соответственно с истоками лючевых транзисторов записи 24 и 25, затворы которых подключены к шине записи 26, а стоки, являющиеся информационными выходами 27 и 28 дополнительного ДУ и ячейки (триггера-защелки), подсоединены соответственно к нагрузочным транзисторам 29 и 30 дополнительного ,дифференциального усилителя. Сток усилительного транзистора 31 и затвор усилительного транзистора 32 подключены к нагрузочному транзистору 29 (первому информационному выходу 27 ячейки), сток усилительного транзистора 32 и затвор усилительного транзистора 31 подключены к нагрузочному транзистору 30 (второму информационному выходу ячейки), Истоки усилительных транзисторов 31 и 32 соединены со стоком ключевого транзистора записи 33, исток которого подключен к общей шине 23, а, затвор к выходу инвертора 34 сигнала записи нйшине записи 26. Инвертор 34 сигнала записи содержит ключевой транзистор 35 и

0 нагрузочный транзистор 36. К информационным выходам 27 и 28 подключены затво-. ры соответственно ключевых транзисторов 37 и 38, истоки которых соединены между собой, а стоки подсоединены соответственно к первой и второй разрядным шинам 43 и 44. Затвор ключевого транзистора 39 соедине н с шиной адреса 40, а сток ключевого транзистора 41 -- с шиной результата 42. Сток ключевого транзистора 39 и затвор

0 ключевого транзистора 41 соединены с истоками ключевых транзисторов 37 и 38. Затвор и меток нагрузочного транзистора 7, истоки усилительного транзистора 8, ключевых транзисторов 35, 39, 41 подключены к

5 общей шине 23. Стоки нагрузочных транзисторов 3, 4, 6, 29, 30. 36 соединены с шиной питания 45.

Принцип работы ячейки состоит в следующем.

0По сигналу стирания с шины стирания

14 через открытые каналы ключевых транзисторов стирания 12 и 13 заряжаются до напряжения источника смещения 15 емкости фотодиодов 9 и 10. Появление на затворах

5 усилительных транзисторов 1 и 2 напряжений, смещающих в обратном направлении фотодиоды, приводит каналы этих транзисторов в проводящее состояние. ДУ выходит на рабочий режим, при котором ток

0 через усилительные транзисторы 1 и 2 задается параметрами токостабиг.изирующей цепи на транзисторах 5, 6, 7, 8. Стабильность тока через токостабилизируюш.ий транзистор 5 обеспечивается за счет последовательной отрицательной обратной связи (00С) потоку. Для повышения стабильности в петлю ООС включен инвертирующий усилитель на транзисторах 8 и б, на вход которого подается cигfiaл обратной связи по току с нагрузочного транзистора 7, С вкпючением усилителя увеличивается в К раз стабильность тока в транзисторе 5, где К коэффициент усиления по напряжению усилителя на транзисторах 8 и б.

На выходах ДУ (стоках усилительных транзисторов 1 и 2) устанавливается при этом напряжение АОвыхО начального разбаланса зтого усилителя, которое через открытые каналы транзисторов стирания 18м 19 подается на запоминающий конденсатор 16 и запоминается на его емкости.

Паразитные емкости между затворами (шиной стирания) и истоками, затворами (шиной стирания) и стоками транзисторов 18 и 19 также оказываются заряженными соответственно до напряжений Узе и изи транзистора 18. В предположении одинаковости геометрических размеров каналов транзисторов 18 и 19 емкость между истоком транзистора 18 (затвором транзистора 20) и его затвором будет в 2 раза больше емкости между стоком (затворомтранзистора 21) и затвором (шиной стирания) этого транзистора, так как паразитные емкости двух транзисторов оказываются соединенными параллельно.

По окончании сигнала стирания каналы транзисторов 12.13,18,19 запираются. Фотодиоды 9 и 10 оказываются обратно смещенными зарядами, запасенными их емкостями во время стирания, а на емкости запоминающего конденсатора 16 сохраняется напряжение Uebix.o+Unepea.i, где иперез.1 - напряжение, которое возникает на конденсаторе 16 в результате перезаряда емкости этого конденсатора через пар зитную емкость между затвором и стоком транзистора 18 по заднему фронту сигнала стирания. На запоминающем конденсаторе 17, который при стирании был зашунтирован открытым каналом транзистора 19 и поэтому был разряжен, при запирании каналов транзисторов 18 и 19 также возникает напряжение Unepe3.2. связанное с перезарядом этого конденсатора через удвоенную паразитную емкость затвор-исток (сток) транзисторов 18 и 19. Если конденсатор 17 выполнить со значением емкости, равным удвоенному значению емкости конденсатора 16, то Unepes.l-Unepea.a. Напряжения на запоминающих конденсаторах 16 и 17, суммируясь с выходным напряжением дифференциального усилителя (за счет последовательного соединения конденсаторов 16 и 17 с выходом этого усилителя), компенсирует на входах дополнительного ДУ действие как начального разбаланса Увых.о. так и действие паразитных емкостей транзисторов 18 и 19. В результате на входах дополнительного

ДУ будет сигнал, соответствующий только полезному сигналу первого каскада.

Дополнительный ДУ, включающий третий и четвертый усилительные транзисторы

20 и 21, нагрузочные транзисторы 29 и 30. соединенные последовательно с ключевыми транзисторами записи 24 и 25 и токостабилизирующим транзистором 22, образуют вместе с пятым и шестым усилительными

0 транзисторами 31 и 32, инвертором на транзисторах 35, 36 и транзистором записи 33 выходной каскад с функциями высокочувствительного компаратора с ячейкой памяти (триггера-защелки), имеющей информационные выходы 27 и 28. Дополнительные ключевые транзисторы 37-41 вместе с внешними шинами ввода (вывода) двумя разрядными шинами 43,44, адресной шиной 40 и шиной результата 42, связывающими ячейки в фоточувствительном матричном, запоминающем устройстве по столбцам и строкам, обеспечивают обращение к этой ячейке по адресу (шина 40) с выводом результата о состоянии ячейки памяти на разрядные шины 43,44 и логическое сравнение состояния ячейки с внешним запросом, подаваемым на разрядные шины 43 и 44, с выводом результата сравнения на шину результата 42.

0 При отсутствии сигнала записи на шине

26каналы ключевых транзисторов записи 24 и 5 заперты, а ключевой транзистор 33 открыт (выходным сигналом с выхода 34 инвертора сигнала записи). При этом конфигурация, состоящая из -транзисторов 29-32, образует статический триггер (транзистор 33 включает его питание), т.е. ячейку памяти с информационными выходами

27и 28. На время действия сигнала записи 0 питание этого триггера отключается (канал

транзистора 33 запирается), зато при замкнутых каналах ключевых транзисторов 24 и 25 из транзисторов 20, 21, 22, 24. 25, 29, 30 образуется конфигурация дифференциального усилителя, который усиливает дифференциальный сигнал на его входах (затворах транзисторов 20 и 21). Усиленный сигнал запоминаемся на паразитных емкостях выходов 27 и 28. По заднему

0 фронту сигнала записи, когда каналы транзисторов записи 24 и 25 запираются, а канал транзистора 33 открывается, происходит - срабатывание триггера в соответствии со знаком напряжения, установившегося на его

5 входах (выходах 27 и 28) перед концом сигнала записи. Таким образом, производится компарирование сигнала дифференциального усилителя с фотодиодами на входах. его нормирование по уровню и запись в триггер.

При адресном считывание состояния триггера на разрядные шины появление сигнала адреса на шине адреса 40 вызывает через открытый канал транзистора 39 и один из открытых каналов траизмсторЪв 37 или 38 (в зависимости от состояния триггера) соединение общей шины 23 с одной из разрядных шин 43 или 44. При логическом сравнении (ассоциативном поиске информации) транзисторь 37, 38. образуют две схемы И, пходы которых подключены к информационным выходам 27 и 28 триггера и к разрядным шинам 43 и 44. а выходы объединены в шинное ИЛИ, реализуемое по шине результата 42 транзистором 41 (в зависимости от результата сравнения шина 42 соединяется или не соединяется с общим выводом 23).

Ф о р мула изобретения Ячейка фоточувствительного матричного запоминающего устройства, содержащая первый и второй усилительные транзисторы, стоки которых подключены к истокам vt ззтворам соответственно первого и второго нагрузочных транзисторов, соединенных стоками с шиной питания, истоки первого и второго усилительных транзисторов соединены со стоком первого токостабилизирующего транзистора, первый и второй фотодиоды, которые подключены к затворам соответственно первого и второго усилительных транзисторов и к подложке, первый и второй ключевые транзисторы стирания, истоки которых соединены соответственно с первым и вторым фотодиодами, стоки первого и второго ключевых транзисторош стирания соединеныс источником смещения фотодиодов, а их затворы,- с шиной стирания, третий и четвертый усилЕ тельные транзисторы, истоки которых соединены со стоком второго токостабилмзирующего транзистора, стоки третьего и четвертого усилительных транзисторов подключены соответственно к истокам первого и второго ключевых транзисторов записи, затворы которых подключены к шине записи, стокм первого и второго ключевых транзисторое записи подключены к затворам м истокам соответственно третьего и четвертого нагрузочных транзисторов, третий транзистор стирания, исток которогоподключен к затвору третьего усилительного транзистора, затвор третьего транзистора стмрагия подключен к шине стирания, а сток - к Зсусвору четвертого усилительного транзиcт ; ра и через запоминающий конденсатор - к стоку второго усилительного транзистора, пятый и шестой усилительные транзисторы, истоки которых соединены со стоко

третьего ключевого транзистора записи, затвор которого подключен к стоку первого ключевого транзистора, затвору и истоку пятого нагрузочного транзистора, сток пятого усилительного транзистора и затвор шестого усилительного транзистора подключены к затвору и истоку третьего нагрузочного транзистора, сток шестого усилительного транзистора и затвор пятого усилительного транзистора соединены с затвором четвертого нагрузочного транзистора, затвор первого ключевого транзистора подключен к шине записи, стоки третьего, четвертого и пятого нагрузочных

5 транзисторов соединены с шиной питания, истоки первого ключевого транзистора и третьего транзистора записи, а также затвор и исток второго токостабилизирующеготранзистора подключены к общей шине,

0 отличающаяся тем, что, с целью повышения надежности ячейки и расширения ее функциональных возможностей за счет обеспечения возможности ассоциативного поиска информации, в ячейку вве5 даны четвертый ключевой транзистор стирания, второй запоминающий конденсатор, седьмой усилительный транзистор, шестой и седьмой нагрузочные транзисторы и ключевые транзисторы со второго по пятый. причем сток первого усилительного транзистора через второй запоминающий конденсатор соединен с истоком третьего ключевого транзистора стирания и затвором третьего усилительного транзистора,

5 сток четвертого ключевого транзистора стирания подключен к стоку первого усилительного транзистора, исток и затвор четвертого ключевого транзистора стиракия подключены соответственно к затвору третьего усилительного транзистора и к шине стирания, затвор первого токостаби.пмзирующего транзистора соединен со стоком седьмого усилительного транзистора, с затвором и истоком шестого нагрузочного

5 транзистора, сток которого подключен к шине питания, исток первого токостабилизирующего транзистора соединен с затвором седьмого усилительного транзистора и стоком седьмого нагрузочного транзистора, затвор и исток которого, а также исток седьмого усилительного транзистора подключены к общей шине, затворы второго и третьего ключевых транзисторов подключены соответственно к стокам пятого и шестого

5 усилительных транзисторов, являющимся информационными выходами ячейки, истоки второго и третьего ключевых транзисторов соединены со стоком четвертого и затвором пятого ключевых транзисторов, истоки которых подключены к общей шине.

стоки второго и третьего ключевых транзисторов соединены соответственно с первой и второй разрядными шинами, затвор четвертого ключевого транзистора соединен с шиной адреса, сток пятого ключевого транзистора подключен к шине результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фотоприемная ячейка | 1989 |

|

SU1619344A1 |

| Фотоприемная ячейка | 1989 |

|

SU1626261A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Фотоприемная ячейка | 1989 |

|

SU1619345A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1981 |

|

SU970461A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

Изобретение относится к оптоэлектро- нике к разделам считывания, обработки и хранения оптической информации. Целью изобретения является повышение надежности ячейки за счет повышения пороговойчувствительности и расширение динамического диапазона сравниваемых оптических сигналов и расширение функциональных возможностей ячейки за счет обеспечения ассоциативной выборки информации. Ячейка содержит дифференциальный усилитель, состоящий из усилительных 1, 2, 8. 20, 21, 31, 32, нагрузочных 3, 4, 6, 7, 29, 30 и 36 и токостабилизирующих 5 и 22 транзисторов, фотодиоды 9, 10, подключенные к затворам усилительных транзисторов и подложке 11, транзисторы стирания 12, 13, 18, 19, затворы которых подключены к шине стирания, стоки - к источнику смещения фотодиодов, а истоки - к фотодиодам и к соответствующим затворам усилительных транзисто- роа, триггер-защелку с цепочкой на входе из последовательно соединенных транзисторов стирания и запоминающих конденсаторов 16,17, ключевые транзисторы 35, 37. 38, 39, 41 адресной выборки и сравнения. 1 ил.

J7

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1980 |

|

SU868834A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-30—Публикация

1989-10-30—Подача