Изобретение относится к вычислительной технике, а точнее к опто- 15 электронике, и может быть использовано в устройствах для считывания и хранения оптической информации

Цель изобретения - повышение чув- ствительности фртоприемной ячейки и 20 расширение ее функциональных возможностей за счет обеспечения точности выполнения логико-арифметической обработки информации в составе многоэлементной фотоприемной матрицы

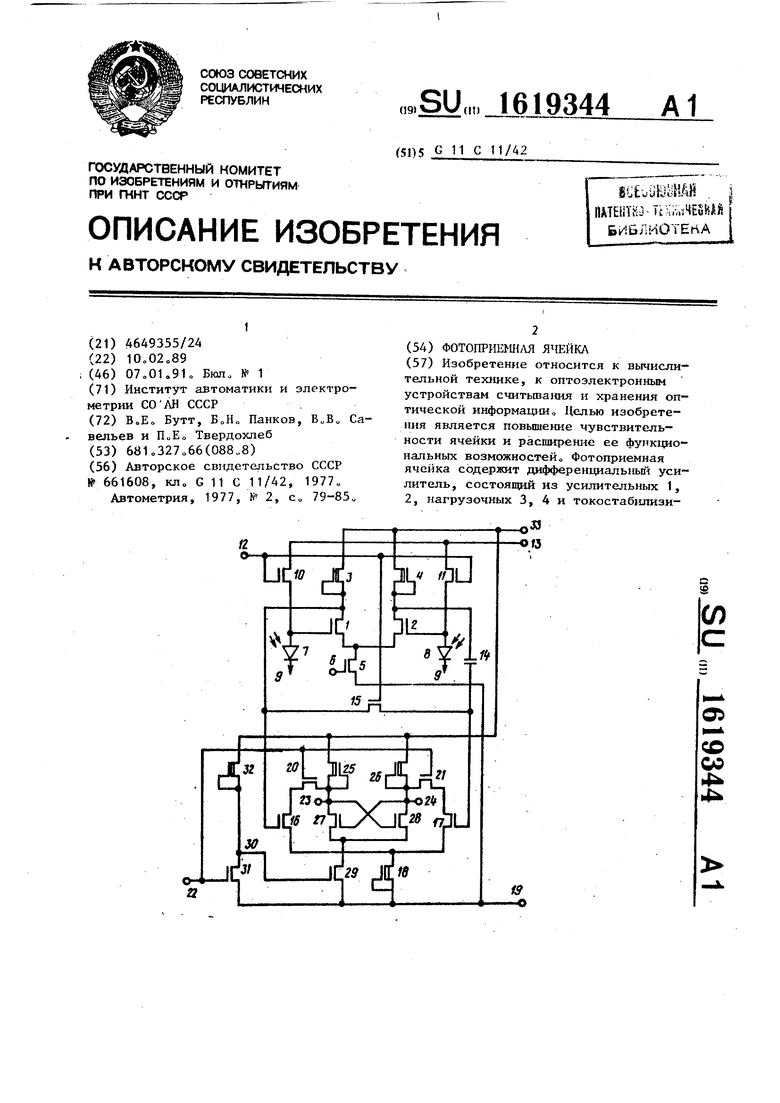

На чертеже представлена схема фо- топриемной ячейки для дифференциального сравнения двух оптических сигналов.

Фоточувствительная ячейка содер- 30 жит первый и второй усилительные транзисторы 1 и 2, первый и второй , нагрузочные транзисторы 3 и 4, hep- вый токостабилизирующий транзистор 5, шину 6 установки режима, фотодиоды 35 7 и 8, подложку 9 фотодиодов и транзисторов, ключевые транзисторы 10 и 11 стирания, шину 12 стирания, источник 13 смещения, запоминающий конденсатор 14, дополнительный транзистор 40 15 стирания, третий и четвертый усилительные транзисторы 16 к 17, второй токостабилизирующий транзистор 18, общую шину 19, первый и второй ключевые транзисторы 20 и 2 Г записи, шину 2245 записи, выходные шины 23 и 24 фотоприемной ячейки, третий и четвертый нагрузочные транзисторы 25 и 26, пятый и шестой усилительные транзисторы 27 и 28, третий ключевой транзистор 50 29 записи, инвертор 30, ключевой транзистор 31, пятый нагрузочный транзистор 32, шину 33 питанияо Усилительные транзисторы 1 и 2, нагрузочные транзисторы 3 и 4, токоста-- билизирующий .транзистор 5, управляемый от задающей режим шины 6, образуют дифференциальный усилитель0 Фотодиоды

7 и 8 подключены к затворам усилительных транзисторов 1 и 2 и к подложке 90 Затворы ключевых транзисторов 10 и 11 стирания подключены к шине 12 стирания, стоки - к источнику 13 смещения фотодиодов, а истоки - соответственно к затворам усилительных транзисторов 1 и 2о Между стоками усилительных транзисторов 1 и 2 включена цепочка, состоящая из последовательно соединенных запоминающего конденсатора 14 и дополнительного транзистора 15 стирания, затвор которого соединен с шиной 12 стиранияо Сток и исток транзистора 15 подключены соответственно к затворам усилительных транзисторов 16 и 17 дополнительного дифференциального усилителя, являющегося составной частью триггера-защелкио Истоки транзисторов 16 и 17 дополнительного дифференциального усилителя соединены со стоком токостабшшзирующего транзистора 18 этого усилителя, а затвор и исток токостабилизирующего транзистора 18 - с общей шиной 19„ Стоки третьего и четвертого усилительных транзисторов 16 и 17 соединены соответственно с истоками ключевых транзисторов 20 и 21 записи, затворы которых подключены к шине 22 записи, а стоки, являющиеся выходами 23 и 24 дополнительного дифференциального усилителя и фоточувствительной ячейки (триггера-защелки), - соответственно к нагрузочным транзисторам 25 и 26 дополнительного дифференциального усилителя о Сток усилительного транзистора 27 и затвор усилительного транзистора 28 подключены к нагрузочному транзистору 25 (первому выходу 23 фоточувствительной ячейки), сток усилительного транзистора 28 и затвор усилительного транзистора 27 подключены к нагрузочному транзистору 26 (второму выходу 24 фоточувствительной ячей-- ки). Истоки усилительных транзисторов

516

27 и 28 соединены со стоком ключевого транзистора 29 записи, исток которого подключен к общей шине 19, а затвор-i к выходу инвертора 30 сигнала на шине 22 записи Инвертор сигнала записи содержит ключевой 31 и нагрузочный 32 транзисторы,, Питание дифференциального усилителя, дополнительного дифференциального усилителя и инвер- тора сигнала записи осуществляется от источника питания по тине 33а

Принцип работы фотоприемной ячейки состоит в следующемо

По сигналу стирания с шины 12 сти- рання через открытые каналы ключевых транзисторов 10 и 11 стирания заряжаются до напряжения источника 13 смещения емкости фотодиодов 7 и 80 На выходах дифференциального усилителя (стоках усилительных транзисторов 1 и 2) устанавливается при этом напряжение й1 6Ыу Qначального разбаланса этого усилителя, которое через открытый канал дополнительного транзистора 15 стирания подается на запоминающий конденсатор 14 и запоминается на его емкостио

По окончании сигнала стирания каналы транзисторов 10, 11 и 15 запира- ются Фотодиоды 7 и 8 оказываются обратно смещенными зарядами, запасенными их емкостями во время стирания,а на емкости запоминающего конденсатора 14 сохраняется напряжение Дивь , соот- ветствующее начальному разбалансу дифференциального усилителя,, Это напряжение, суммируясь с выходным напряжением дифференциального усилителя (за счет последовательного соединения кон- денсатора 14 с выходом этого усилителя) , компенсирует на входах дополнительного дифференциального усилителя действие начального разбаланса„ В результате на входах дополнительного дифференциального усилителя будет сигнал, соответствующий только полезному сигналу первого каскада„

Дополнительный дифференциальный усилитель, включающий третий и четвертый усилительные транзисторы 16 и 17, нагрузочные транзисторы 25 и 26, включенные последовательно с ключевыми транзисторами 20 и 21 записи, об- разует вместе с дополнительными пятым и шестым усилительными транзисторами 27 и 28, инвертором на транзисторах 31 и 32 и транзистором записи 29

4

выходной каскад фотоприемной ячейки с функциями высокочувствительного компаратора с ячейкой памяти (триггера- защелки) о

При отсутствии сигнала записи на шине 22 каналы ключевых транзисторов 20 и 21 записи заперты, а ключевой транзистор 29 - открыт (выходным сигналом с выхода 30 инвертора сигнала записи)„ При этом конфигурация, состоящая из транзисторов 27, 28,, 25 и 2Ь, образует статический триггер (транзистор 29 включает его питание), т„е„ ячейку памяти с выходами 23 и 24 На время действия сигнала записи питание этого триггера отключается (канал транзистора 29 запирается), зато при замкнутых каналах кл.очевых транзисторов 20 и 21 из транзисторов 16, 17, 20, 21, 25, 26 и 18 образуется конфигурация дифференциального усилителя, который усиливает дифференциальный сигнал на его входах (затворах транзисторов 16 и 17)о Усиленный сигнал запоминается на паразитных емкостях выходов 23 и 24„ По заданному фронту сигнала стирания, когда каналы транзисторов 20 и 21 записи запираются, а капал транзисторов 29 открывается, происходит срабатывание триггера п соответствии со знаком напряжения, установившегося на его входах (иыходах 23 и 24) перед концом сигнала записи„ Таким образом производится компарирование сигнала дифференциального усилителя с фотодиодами на уходах, его нормирование по уровню и запись в триггрр

Отсутствие на входе дополнительного дифференциального усилителя начального разбаланса первого каскада повышает отношение сигнал/шум для ячейки в целом, а следовательно, увеличивает се пороговую чувствительность Применение в составе фотопри- емной ячейки триггера-защелки предложенной конфигурации расширяет ее функциональные возможности,, Это позволяет, использовать предложенную ячейку в качестве элементарной ячейки многоэле- ментнсй интегральной матрицы, способной выполнять в общем случае не только операции записи/чтения, но и многоканальную логико-арифметическую обработку страниц цифровой оптической информации,, Такие фотоматрицы (называемые фотоматричными процессорами),при использовании в них в качестве элемен-

тарной ячейки предложенной конфигурации, обладающей высокой фоточувствительностью, помехоустойчивостью и расширенными функциональными возможностями, обеспечивают высокие скорости выдачи и обработки потока цифровых данных, поступающих из оптической памяти.,

10 Формула изобретения

Фотоприемная ячейка, содержащая первый и второй усилительные транзисторы, стоки которых подключены к истокам и затворам соответственно пер- 15 вого и второго нагрузочных транзисторов, стоки которых соединены с шиной питания, истоки первого и второго усилительных транзисторов соединены со стоком токостабшшзирующего транзис- 20 тора, затвор которого подключен к управляющей шине, первый и второй фотодиоды, которые подключены к затворам соответственно первого и второго усилительных |транзисторов и к подложке, 25 первый и второй ключевые транзисторы стирания, истоки которых соединены соответственно с первым и вторым фотодиодами, а стоки подключены к источнику смещения фотодиодов, затворы зо первого и второго ключевых транзисторов стирания соединены с шиной стирания, отличающаяся тем, что, с целью повышения чувствительности ячейки и расширения ее функ- ,, циональных возможностей, в ячейку введены третий ключевой транзистор стирания и запоминающий конденсатор, третий и четвертый нагрузочные транзисторы, первый, второй и третий чевые транзисторы записи, третий и четвертый усилительные транзисторы, второй токостабилизирующий транзистор, пятый и шестой усилительные транзисторы, ключевой транзистор и пятый

нагрузочный транзистор, причем сток первого усилительного транзистора подключен к затвору третьего усилительного транзистора и к истоку третьего транзистора стирания, затвор которого подключен к шине стирания, сток второго усилительного транзистора соединен через запоминающий конденсатор со стоком третьего транзистора стирания и с затвором четвертого усилительного транзистора, истоки третьего и четвертого усилительных транзисторов соединены со стоками второго стабилизирующего транзистора, затвор и исток которого подключены

к общей шине, стоки третьего и четвертого усилительных транзисторов соединены соответственно к истокам первого и второго ключевых транзисторов записи, затворы которых подключены к шине записи, а стоки - к затворам и истокам соответственно третьего и четвертого нагрузочных транзисторов, сток пятого усилительного транзистора и затвор шестого усилительного транзистора подключены к затвору третьего нагрузочного транзистора, сток шестого усилительного транзистора и затвор пятого усилительного транзистора соединены с затвором четвертого нагрузочного транзистора, истоки пятого и шестого усилительных транзисторов соединены со стоком третьего ключевого транзистора записи, затвор которого подключен к стоку ключевого транзистора, затвору и истоку пятого нагрузочного транзистора, затвор ключевого транзистора подключен к шине записи, стоки третьего, четвертого и пятого нагрузочных транзисторов соединены с шиной питания, истоки ключевого транзистора и третьего ключевого транзистора записи подключены к общей шине. Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Фотоприемная ячейка | 1989 |

|

SU1619345A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Фотоприемная ячейка | 1989 |

|

SU1626261A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1992 |

|

RU2050600C1 |

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| УСИЛИТЕЛЬ ЗАПИСИ-СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 1987 |

|

SU1612801A1 |

| Устройство считывания для многоэлементных фотоприемников инфракрасного излучения | 2016 |

|

RU2645428C1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель считывания | 1982 |

|

SU1120405A1 |

Изобретение относится к вычислительной технике, к оптоэлектронным устройствам считывания и хранения оптической информации. Целью изобретения является повышение чувствительности ячейки и расширение ее функциональных возможностей,, Фотоприемная ячейка содержит дифференциальный усилитель, состоящий из усилительных 1, 2, нагрузочных 3, 4 и токостабилизи

| Оптоэлектронный элемент памяти | 1977 |

|

SU661608A1 |

| Автометрия, 1977, № 2, с„ 79-85„ | |||

Авторы

Даты

1991-01-07—Публикация

1989-02-10—Подача