Изобретение относится к электронной технике и может быть использовано для защиты информации в микропроцессорных системах от несанкционированного к ней доступа, например, фискальной памяти электронных контрольно-кассовых машин.

Известно устройство для защиты электронных систем, содержащее блок установочных данных, блок контроля ситуации, блок управления защиты и исполнительный блок [1]

Известен способ защиты электронных систем, включающий контроль ситуации и при действие защищающие механизмы [1]

Известно также устройство с защитой информации в микропроцессорных системах, содержащее шину исходных данных, адресов и управления, блок памяти, дешифратор и блок управления-защиты [2] прототип.

Известен также способ защиты информации в микропроцессорных системах, включающий контроль защищаемой в микропроцессорных системах информации, и при обнаружении незапрограммированной ситуации, формирование сигнала, предотвращающего развитие незапрограммированной ситуации [3] прототип.

Недостатком известных способов и устройств являются относительно низкие их функциональные и технические характеристики, в том числе неудобства практического использования при относительной их сложности.

Решаемой технической задачей в соответствии с изобретением является расширение функциональных возможностей с заявленных объектов, улучшение их технических характеристик с достижением технического результата, заключающегося в повышении удобств практического использования при относительном снижении уровня сложности.

Для достижения технического результата в устройстве с защитой информации в микропроцессорных системах, содержащем шину исходных данных, адресов и управления, блок памяти, дешифратор и блок управления-защиты, блок памяти выполнен в виде энергонезависимой программируемой памяти защищаемой информации, блок управления-защиты выполнен в виде шины данных, адресов и управления, соединенной с первым входом блока энергонезависимой программируемой памяти защищаемой информации, дешифратором и первым входом триггера разрешения доступа, а первый выход дешифратора через логический элемент И соединен с вторым блоком памяти защищаемой информации, второй выход дешифратора соединен со вторым входом триггера разрешения доступа, а третий выход дешифратора соединен с первым входом интегратора-формирователя блокировочного сигнала, выход интегратора-формирователя соединен со вторым входом триггера блокировки доступа, причем отношение суммы выходного сопротивления интегратора-формирователя и входного сопротивления триггера блокировки доступа к входному сопротивлению триггера блокировки доступа должно быть большим или равным 1,000001 и меньшим или равным 1,1, при этом выход триггера блокировки доступа соединен с дополнительным входом триггера разрешения доступа и третьим входом блока памяти защищаемой информации, а интегратор-формирователь выполнен таким образом, что он формирует блокировочный сигнал, устанавливающий триггер блокировки доступа к блоку памяти защищаемой информации в состояние блокировки доступа к блоку памяти защищаемой информации, при отсутствии сигналов на выходе триггера разрешения доступа, формируемых программой расположенной в разрешенной области памяти.

Способ защиты информации в микропроцессорных системах, включающий контроль защищаемой в микропроцессорных системах информации и, при обнаружении незапрограммированной ситуации, формирование сигнала, предотвращающего развитие незапрограммированной ситуации, отличается тем, что при включении системы сигналом СБРОС СИСТЕМЫ устанавливают триггер разрешения доступа и триггер блокировки доступа в исходное состояние, после чего программой, расположенной в разрешенной области памяти, записывают в триггер разрешения доступа сигнал, разрешающий доступ к блоку памяти защищаемой информации, с одновременным разрешением работы интегратора-формирователя, причем одновременно с выбором кода программы, расположенной в разрешенной области памяти, перезапускают интегратор-формирователь, в результате чего предотвращается формирование блокировочного сигнала интегратором-формирователем при запуске программы из отличающейся от разрешенной области памяти, осуществляющей доступ к блоку памяти защищаемой информации, запрещают перезапуск интегратора-формирователя, после чего, через заданно время Т равное времени настройки интегратора-формирователя и определяемое из условия (Т+t)/t больше или равно 2,1, но меньше или равно 3; где t время выполнения команды микропроцессорной системой.

Интегратором-формирователем формируют блокировочный сигнал и устанавливают им триггер блокировки доступа в состояние блокировки, запрещая доступ к блоку памяти защищаемой информации, причем последующую установку триггера разрешения доступа в исходное состояние осуществляют только путем подачи сигнала СБРОС СИСТЕМЫ.

Предложенные устройство и способ имеют одно и то же назначение, служат одной цели, обеспечивают достижение одного и того же технического результата и, таким образом, взаимосвязаны единым изобретательским замыслом,охарактеризованным формулой изобретения. При этом концепция правовой охраны основана на том, что неразрывность и взаимосвязанность предложенных объектов, а также допускаемая вариантность осуществления отдельных существенных признаков или их совокупностей предопределяют нетрадиционный характер формулировок некоторых признаков.

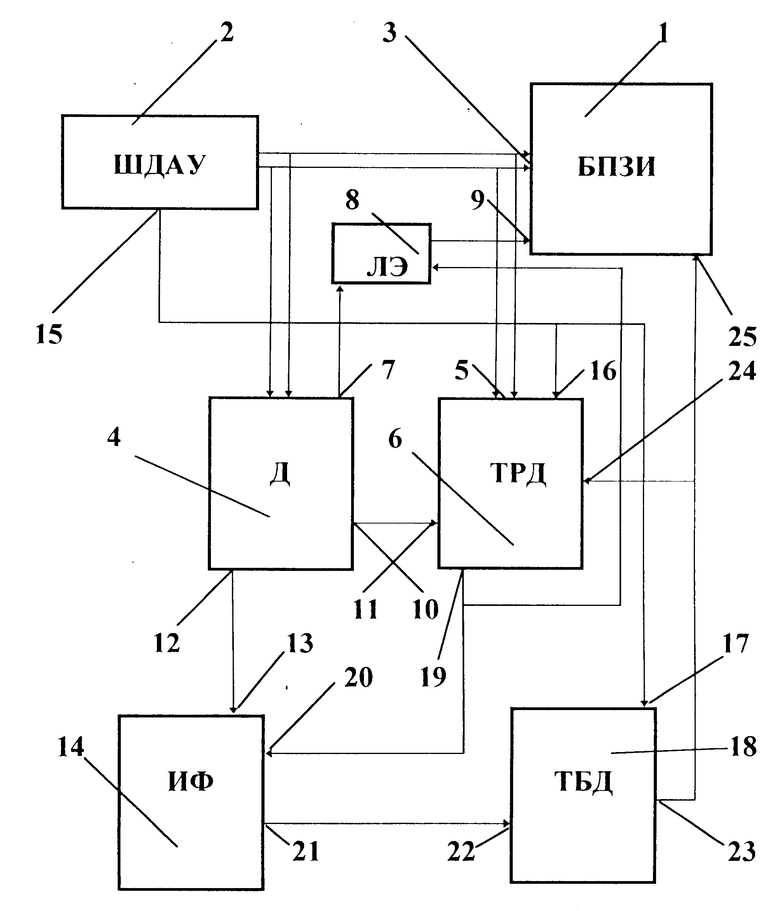

Заявленные способ и устройство поясняются чертежом, на котором схематически изображена блок-схема предложенного устройства.

Отличительные конструктивные особенности предложенного устройства заключатся в том, что блок памяти выполнен в виде блока 1 (БПЗИ) (см.чертеж) энергонезависимой программируемой памяти защищаемой информации. Блок 1 может представлять собой, например, фискальную память электронных контрольно-кассовых машин в виде комплекса известных программно-аппаратных средств в составе контрольно-кассовых машин, обеспечивающего некорректируемую, ежесуточную (ежесменную) регистрацию и энергонезависимое долговременное хранение итоговой информации о денежных расчетах с населением, необходимой для правильного исчисления налогов. Ежесуточная (ежесменная) регистрация означает безусловную запись итоговой информации о денежных расчетах с населением в фискальной памяти при проведении операции закрытия смены, причем продолжительность смены не должна превышать 24 ч. Энергонезависимое долговременное хранение означает долговременное хранение информации без использования внешних и внутренних источников питания. При попытке несанкционированных действий устройство должно блокировать выполнение всех несанкционированных операций. Информация, зарегистрированная в накопителе фискальной памяти, должна сохраняться в течение не менее 6 лет с момента перевода контрольно-кассовой машины в фискальный режим.

Блок управления защиты выполнен в виде шины 2 (ШДАУ), как правило, типовых данных, адресов и управления, соединенной с первым входом 3 блока 1 энергонезависимой программируемой памяти защищаемой информации, дешифратором 4 (Д) и первым входом 5 триггера 6 (ТРД) разрешения доступа. Первый выход 7 дешифратора 4 через логический элемент 8 (ЛЭ) И соединен со вторым входом 9 блока 1 памяти защищаемой информации, второй выход 10 дешифратора 4 соединен со вторым входом 11 триггера 6 разрешения доступа, а третий выход 12 дешифратора 4 соединен с первым входом 13 интегратора-формирователя 14 (ИФ).

Цепь 15 сброса системы шины 2 данных, адресов и управления соединена с третьим входом 16 триггера 6 разрешения доступа и с первым входом 17 триггера 18 (ТБД) блокировки доступа. Выход 19 триггера 6 разрешения доступа через логический элемент И соединен со вторым входом 9 блока 1 памяти защищаемой информации и со вторым входом 20 интегратора-формирователя 14 блокировочного сигнала. Выход 21 интегратора-формирователя 14 соединен со вторым входом 22 триггера 18 блокировки доступа, причем выходное сопротивление Rвых интегратора-формирователя 14 взаимосвязано со входным сопротивлением Rвх триггера 18 блокировки доступа соотношением 1,000001 ≅ (Rвых+Rвх)/Rвх ≅ 1,1. Выход 23 триггера 18 блокировки доступа соединен с дополнительным входом 24 блокировки триггера 6 разрешения доступа и третьим входом 25 блока 1 памяти защищаемой информации.

При описании способа нецелесообразно детально останавливаться на известных из опубликованных данных особенностях выполнения его операций, в частности, контроля защищаемой в микропроцессорных системах информации и при обнаружении незапрограммированной ситуации формирования сигнала, предотвращающего развитие незапрограммированной ситуации. Отличительные существенные особенности осуществления операций предложенного способа, заключаются в том, что при включении устройства сигналом СБРОС СИСТЕМЫ устанавливают триггер 6 разрешения доступа и триггер 18 блокировки доступа в исходное состояние. Программой, расположенной в разрешенной области памяти, записывают в триггер 6 разрешения доступа сигнал, например, логическую единицу, разрешающий доступ к блоку 1 памяти защищаемой информации и тем самым разрешают работу интегратора-формирователя 14. При этом выборкой кода программы, расположенной в разрешенной области памяти, вызывают перезапуск интегратора-формирователя 14, в результате чего интегратор-формирователь блокировочный сигнал не формирует.

При запуске программы из отличающейся от разрешенной области памяти, с помощью которой установят доступ к блоку 1 памяти защищаемой информации, сигнал выборки кода программы из разрешенной области памяти не формируют и тем самым не осуществляют перезапуск интегратора-формирователя 14. Через заданное время Т, которое выбирают в пределах 2,1 ≅ (T+t)/t ≅ 3, где t - время выполнения команды микропроцессорной системы, а Т время настройки срабатывания интегратораформирователя 14, интегратором-формирователем формируют блокировочный сигнал, и устанавливают им триггер 18 блокировки доступа в состояние блокировки. Блокирующий сигнал формируют, например, в виде импульсно возрастающего напряжения с амплитудой, минимальное значение U1 и максимальное значение U2 которой выбирают в пределах 1,1 ≅ (U1+U2)/U2 ≅ 1,8 и длительностью, минимальное значение t1 и максимальное значение t2 которой устанавливают в пределах 0,2 ≅ t1/t2 ≅ 1. Этим сигналом запрещают доступ к блоку 1 памяти защищаемой информации, а триггер 6 разрешения доступа устанавливают в исходное состояние только путем подачи сигнала СБРОС СИСТЕМЫ, предопределяя тем самым работу с блоком 1 памяти защищаемой информации только программы, находящейся в разрешенной области памяти и позапрограммированному в ней алгоритму.

Соответствие критерию промышленная применимость заявленных объектов доказывается как широким получением и использованием различных устройств подобного типа в промышленных масштабах, так и отсутствием в заявленных притязаниях каких-либо практически трудно реализуемых признаков. Указанные отличия дают основание сделать вывод о новизне данного технического решения, а совокупность испрашиваемых притязаний о ее изобретательском уровне, что доказывается также вышеприведенным детальным описанием заявленных объектов. Заявленные существенные отличительные признаки, нижние и верхние значения их пределов и приведенных аналитических соотношений были получены на основе статистической обработки результатов экспериментальных исследований, анализа и обобщения их и известных из опубликованных источников данных, взаимосвязанных условиями достижения указанного в заявке технического результата, а также с использованием изобретательской интуиции. Достигаемый технический результат, как показали данные экспериментов и охарактеризованные выше материалы, может быть реализован только взаимосвязанной совокупностью всех существенных признаков заявленных объектов, отраженных в формуле изобретения.

Кроме указанного выше технического результата практическое осуществление заявленных объектов позволяет, в частности, получить также существенный социальный эффект, в результате ориентации пользователей на правовые методы предпринимательской деятельности и, например, повышения собираемости налогов.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬ СИСТЕМНОГО КОНТРОЛЯ | 2003 |

|

RU2265240C2 |

| Устройство для измерения массы груза в кузове автосамосвала | 1985 |

|

SU1290085A1 |

| Устройство для контроля хода программы и перезапуска ЭВМ | 1987 |

|

SU1501066A2 |

| УСТРОЙСТВО ЗАЩИТЫ ИНФОРМАЦИИ ОТ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА ДЛЯ КОМПЬЮТЕРОВ ИНФОРМАЦИОННО-ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ | 2006 |

|

RU2321055C2 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| Микропроцессорная система для программного управления технологическими процессами | 1987 |

|

SU1418653A1 |

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| Устройство для контроля микропроцессора | 1988 |

|

SU1599862A1 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

Способ и устройство защиты информации в микропроцессорных системах обеспечивают контроль защищаемой в микропроцессорных системах информации и при обнаружении незапрограммированной ситуации формирование сигнала, предотвращающего развитие незапрограммированной ситуации. При включении системы сигналом СБРОС СИСТЕМЫ устанавливают триггер разрешения доступа и триггер блокировки доступа в исходное состояние, после чего программой, расположенной в разрешенной области памяти, записывают в триггер разрешения доступа сигнал, разрешающий доступ к блоку памяти защищаемой информации с одновременным разрешением работы интегратора-формирователя, причем одновременно с выбором кода программы, расположенной в разрешенной области памяти, перезапускают интегратор-формирователь, в результате чего предотвращается формирование блокировочного сигнала интегратором-формирователем, при запуске программы из отличающейся от разрешенной области памяти, осуществляющей доступ к блоку памяти защищаемой информации, запрещают перезапуск интегратора-формирователя, после чего через заданное время Т интегратором-формирователем формируют блокировочный сигнал и устанавливают им триггер блокировки доступа в состояние блокировки, запрещая доступ к блоку памяти защищенной информации, причем последующую установку триггера разрешения доступа в исходное состояние осуществляют только путем подачи сигнала СБРОС СИСТЕМЫ. 2 с.п. ф-лы, 1 ил.

(T + t)/t больше или равно 2,1, но меньше или равно 3,

где t время выполнения команды микропроцессорной системой,

интегратором-формирователем формируют блокировочный сигнал и устанавливают им триггер блокировки доступа в состояние блокировки, запрещая доступ к блоку памяти защищаемой информации, причем последующую установку триггера разрешения доступа в исходное состояние осуществляют только путем подачи сигнала "Сброс системы".

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| СПОСОБ ЗАЩИТЫ ЭЛЕКТРИЧЕСКОЙ СЕТИ ОТ ПЕРЕГРУЗКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2020681C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| СПОСОБ ЗАЩИТЫ АГРЕГАТА БЕСПЕРЕБОЙНОГО ПИТАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2033675C1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| СПОСОБ ПРЕДОТВРАЩЕНИЯ ИЛИ ИНГИБИРОВАНИЯ ИНФИЦИРОВАНИЯ Т-ЛИМФОЦИТОВ ЧЕЛОВЕЧЕСКИМ ВИРУСОМ ИММУНОДЕФИЦИТА (HIV) И РЕПЛИКАЦИИ IN VIVO | 1989 |

|

RU2145856C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-09-27—Публикация

1996-08-09—Подача