Изобретение относится к микропро- цессорной технике и может быть исполь эовано в автоматизированных системах управления технологическими процессами. ,

Цель изобретения - повышение быстродействия системы.

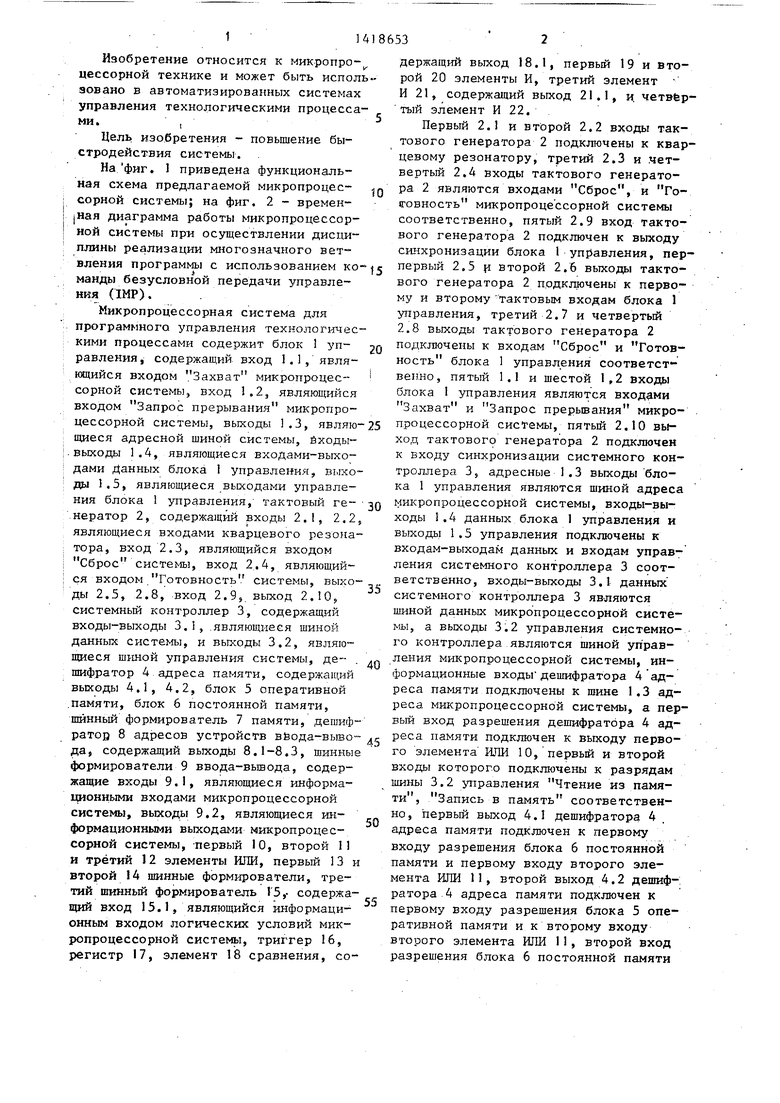

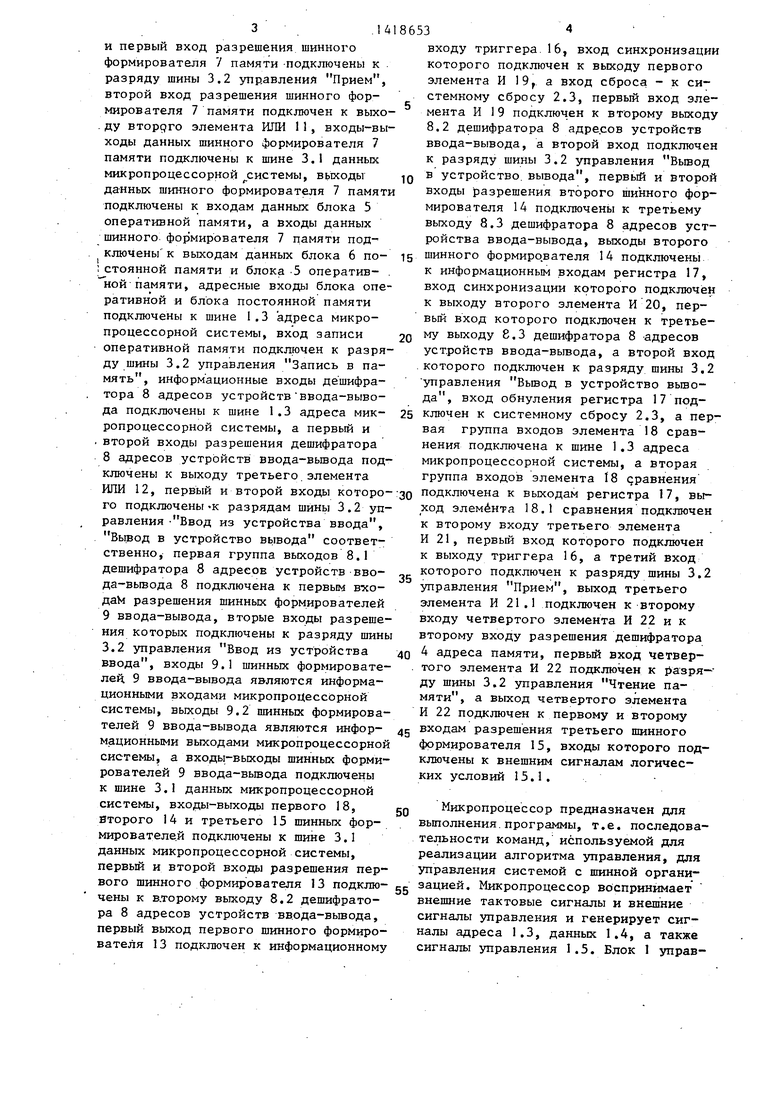

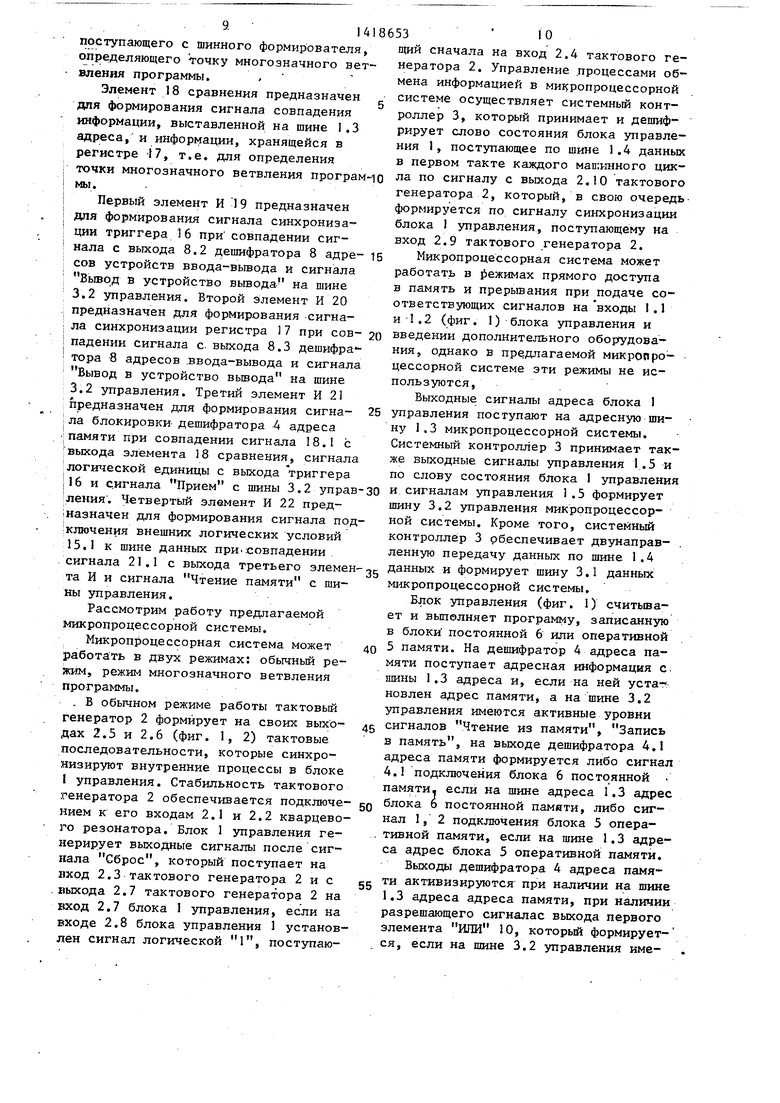

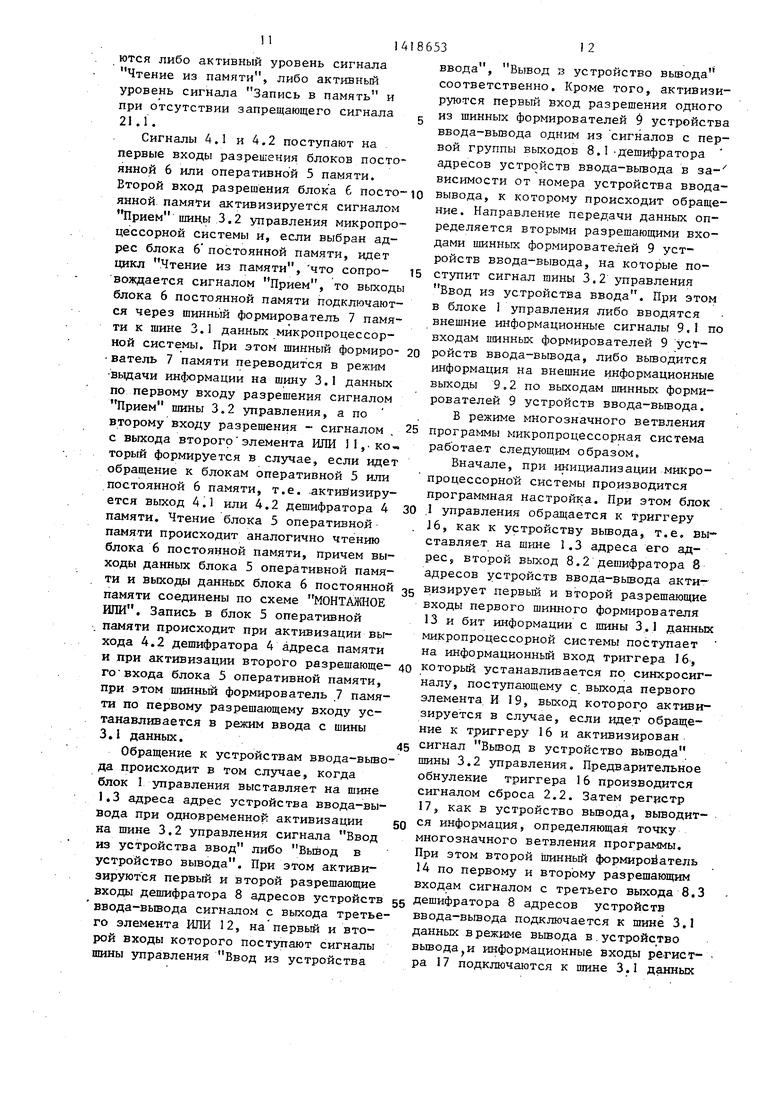

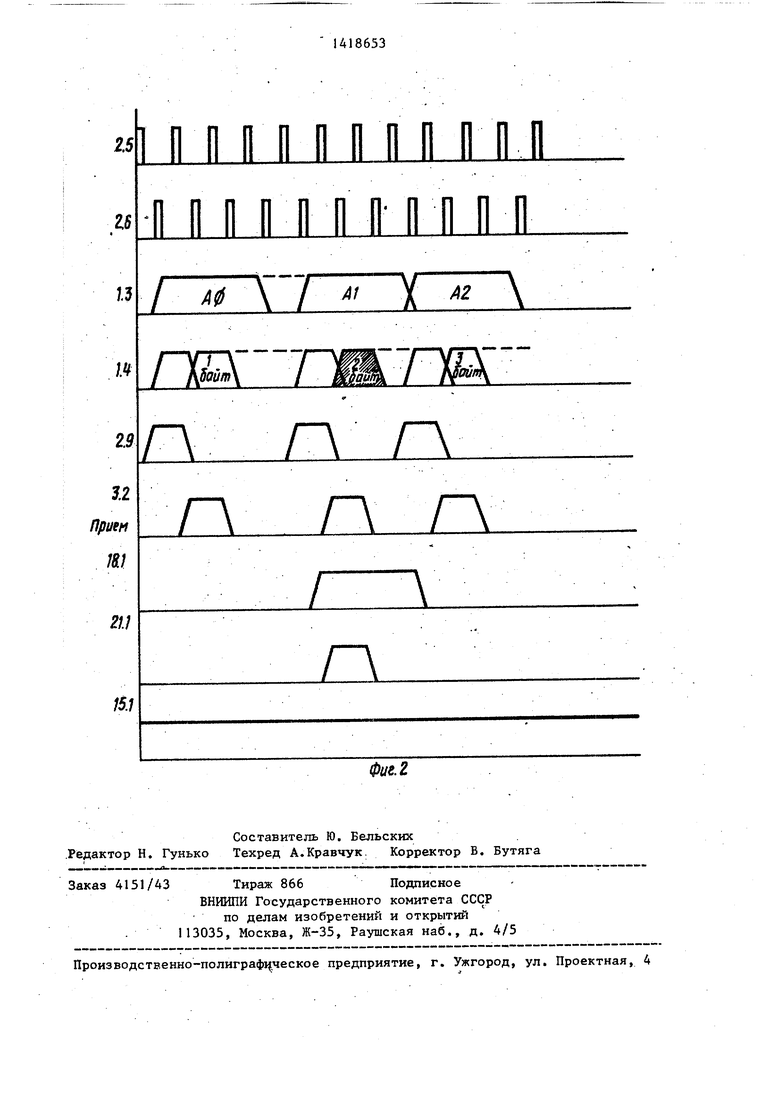

На фиг. 1 приведена функциональная схема предлагаемой микропроцессорной системы; на фиг. 2 - времен- |Ная диаграмма работы микропроцессорной системы при осуществлении дисциплины реализации многозначного ветвления программы с использованием команды безусловной передачи управления (IMP).

Микропроцессорная система для программного управления технологическими процессами содержит блок 1 управления, содержащий вход 1.1, явля- нщийся входом Захват микропроцессорной системы, вход 1.2, являющийся входом Запрос прерывания микропроцессорной системы, выходы 1.3, являющиеся адресной шиной системы, йходы- .выходы 1.4, являющиеся входами-выходами Данных блока 1 управления, выходы 1.5, являющиеся выходами управления блока 1 управления, тактовый ге- .нератор 2, содержащий входы 2., 2.2, являющиеся входами кварцевого резонатора, вход 2.3, являющийся входом Сброс системы, вход 2.4, являющийся входом Готовность системы, выходы 2.5, 2.8, вход 2.9,, выход 2.10,, системный контроллер 3, содержащий входы-выходы 3.1, .являющиеся шиной данньк системы, и выходы 3.2, являющиеся Ш1шой управления системы, де- . шифратор 4.адреса памяти, содержащий выходы 4.1, 4.2, блок 5 оперативной .памяти, блок 6 постоянной памяти, щйнный формирователь 7 памяти, дешиф- ратов 8 адресов устройств вёода-вьюо- да, содержавший выходы 8.1-8,3, шинные формирователи 9 ввод;а-вьшода, содержащие входы 9.1, являющиеся информационными входами микропроцессорной системы, выходы 9.2, являющиеся информационными вькодами микропроцессорной системы, -первый 10, второй 1 и третий 12 элементы ИЛИ, первый 13 и второй 14 шинные формирователи, третий шинный формирователь ГЗ,- содержащий вход 15.1, являющийся информационным входом логических условий микропроцессорной системь, триггер 16, регистр 17, элемент 18 сравнения, со

5

0

5

0

5

0

5

0

5

держащий выход 18.1, первый 19 и второй 20 элементы И, третий элемент И 21, содержащий выход 21.1, и, четвбр- тый элемент И 22.

Первый 2.1 и второй 2.2 входы тактового генератора 2 подключены к кварцевому резонатору, третий 2.3 и .четвертый 2.4 входы тактового генератора 2 являются входами Сброс, и Готовность микропроцессорной системы соответственно, пятый 2.9 вход тактового генератора 2 подключен к выходу синхронизации блока 1 уп1 авления, пер- первый 2.5 р второй 2.6 выходы тактового генератора 2 п.одключены к первому и второму тактовым входам блока 1 управления, третий 2.7 и четвертьй 2.8 выходы тактового генератора 2 подключены к входам Сброс и Готовность блока 1 управления соответственно , пятый 1.1 и шестой 1,2 входы блока 1 управления являются входами Захват и Запрос прерьгоания микропроцессорной системы, пятый 2.10 выход тактового генератора 2 подключен к входу синхронизации системного контроллера 3, адресные 1.3 выходы блока 1 управления являются шиной адреса микропроцессорной системы, входы-выходы 1.4 данных блока 1 управления и выходы 1.5 управления подключены к входам-выходам данных и входам управления системного контроллера 3 соответственно, входы-выходы 3.1 данных системного контроллера 3 являются шиной данных микропроцессорной систе- ivjbi, а выходы 3.2 управления системного контроллера являются шиной управления микропроцессорной системы, информационные входы дешифратора 4 адреса памяти подключены к шине 1.3 адреса микропроцессорной системы, а первый вход разрешения дешифратора 4 адреса памяти подключен к выходу первого элемента ИЛИ 10, первый и второй входы которого подключены к разрядам шины 3.2 управления Чтение из памяти, Запись в память соответственно , первый выход 4.I дешифратора 4 адреса памяти подключен к первому входу разрешения блока 6 постоянной памяти и первому входу второго элемента ИЛИ 11, второй выход 4.2 дешифратора. 4 адреса памяти подключен к первому входу разрешения блока 5 оперативной памяти и к второму входу второго элемента ИЛИ 11, второй вход разрешения блока 6 постоянной памяти

и первый вход разрешения шинного формирователя 7 памяти -подключены к разряду шины 3.2 управления Прием, второй вход разрешения шинного формирователя 7 памяти подключен к выхо- . ду ВТОР9ГО элемента ИЛИ 11, входы-выходы данных шинного формирователя 7 памяти подключены к шине 3.1 данных микропроцессорной системы, вькоды данных шинного формирователя 7 памяти подключены к входам данных блока 5 оперативной памяти, а входы данных шинного формирователя 7 памяти подвходу триггера.16, вход синхронизации которого подключен к выходу первого элемента И 19, а вход сброса - к системному сбросу 2.3, первый вход элемента И 19 подключен к второму выходу 8.2 дешифратора 8 адре.сов устройств ввода-вывода, а второй вход подключен к разряду шины 3.2 управления Вьшод в устройство, вывода, первый и второй входы разрешения второго шинного формирователя 14 подключены к третьему выходу 8.3 дешифратора 8 адресов устройства ввода-вывода, выходы второго

10

ключены к выходам данных блока 6 по- is шинного формиро.вателя 14 подключены ; стоянной памяти и блока 5 оператив- . к информационным входам регистра 17, ной памяти, адресные входы блока one- вход синхронизации которого подключён

ративной и блока постоянной памяти

подключены к шине 1.3 адреса микрок выходу второго элемента И 20, первый вход которого подключен к третье

653

входу триггера.16, вход синхронизации которого подключен к выходу первого элемента И 19, а вход сброса - к системному сбросу 2.3, первый вход элемента И 19 подключен к второму выходу 8.2 дешифратора 8 адре.сов устройств ввода-вывода, а второй вход подключен к разряду шины 3.2 управления Вьшод в устройство, вывода, первый и второй входы разрешения второго шинного формирователя 14 подключены к третьему выходу 8.3 дешифратора 8 адресов устройства ввода-вывода, выходы второго

10

к выходу второго элемента И 20, первый вход которого подключен к третье

| название | год | авторы | номер документа |

|---|---|---|---|

| Система для программного управления электроавтоматикой | 1988 |

|

SU1532899A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Микропроцессорная система для программного управления технологическим оборудованием | 1988 |

|

SU1525678A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 2000 |

|

RU2189623C2 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Система для программного управления технологическим оборудованием | 1989 |

|

SU1674062A1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

Изобретение относится к микропроцессорной технике и может быть ис пользовано в автоматизированных сиil 2«W стемах управления технолог ическими процессами. Цель изобретения - повышение быстродействия системы. Это достигается тем, что в известную систему, содержащую блок управления 1, тактовый генератор 2, системный .контроллер 3, дешифратор 4 адреса памяти, блок 5 оперативной памяти, блок 6 постоянной памяти, шинный формирователь памяти 7, дешифратор 8 адресов устройств ввода-вывода, шинные формирователи 9 ввода-вывода, первый 10, вто- второй 11 и третий 12 элементы ИЛИ, введены первьм.13, второй 14 и третий 15 шинные формирователи, триггер,16, регистр 17, элемент сравнения 18, пер-S вый 19, второй 20, третий 21 и четвертый 22 элементы И. Введение указанных Л элементов позволяет уменьшить время реализации программы многоальтерна- тивного ветвления. 2 ил., 2 табл.

процессорной системы, вход записи 20 оперативной памяти подключен к разряду шины 3.2 управления Запись в память, информационные входы дешифратора 8 адресов устройств ввода-вывому выходу 8.3 дешифратора 8 адресов устройств ввода-вьтода, а второй вход .которого подключен к разряду шины 3,2 управления Вьшод в устройство вьшо- да, вход обнуления регистра 17 под- да подключены к шине 1.3 адреса мик- 25 ключен к системному сбросу 2.3, а пер- ропроцессорной системы, а первый и вая группа входов элемента 18 срав- второй входы разрешения дешифратора нения подключена к шине 1.3 адреса

8адресов устройств ввода-вьшода под- микропроцессорной системы, а вторая ключены к выходу третьего.элемента группа входов элемента 18 (уравнения ИЛИ 12, первый и второй входы которо-:зо подключена к выходам регистра 17, вы- го подключены К разрядам шины 3.2 уп- ход элемента 18.1 сравнения подключен равления- Ввод из устройства ввода,

Вьшод в устройство вьршода соответственно, первая группа вькодов 8.1 дешифратора 8 адресов устройств ввода-вывода 8 подключена к первым входам разрешения шинньк формирователей

9ввода-вывода, вторые входы разрешения которых подключены к разряду шины 3.2 управления Ввод из устройства 40 ввода, входы 9.1 шинных формирователей 9 ввода-вывода являются информационными входами микропроцессорной системы, выходы 9.2 шинных формирователей 9 ввода-вывода являются инфор- 45 разрешения третьего шинного мационными выходами микропроцессорной формирователя 15, входы которого подсистемы, а входы-выходы шинных формирователей 9 ввода-вьшода подключены

к шине 3.1 данных микропроцессорной системы, входы-выходы первого 18, второго 14 и третьего 15 шинных фор- мирователе.й подключены к шине 3.1 данных микропроцессорной системы.

к второму входу третьего элемента И 21, первый вход которого подключен к выходу триггера 16, а третий вход которого подключен к разряду шины 3.2 управления Прием, выход третьего элемента И 21.1 подключен к второму входу четвертого элемента И 22 и к второму входу разрешения дешифратора 4 адреса памяти, первый вход четвертого элемента И 22 подключен к разря- ду шины 3.2 управления Чтение памяти, а выход четвертого элемента И 22 подключен к первому и второму

ключены к внешним сигналам логических условий 15.1.

50

Микропроцессор предназначен для выполнения.программы, т.е. последовательности команд, используемой для реализации алгоритма управления, для управления системой с шинной органи- вого шинного формирователя 13 подклю- gg зацией. Микропроцессор воспринимает чены к в.торому выходу 8.2 дешифрато- внешние тактовые сигналы и внешние ра 8 адресов устройств вв.ода-вьшода, сигналы управления и генерирует сиг- первый выход первого шинного формиро- налы адреса 1.3, данных 1.4, а также вателя 13 подключен к информационному сигналы управления 1.5. Блок 1 управпервый и второй входы разрешения пермикропроцессорной системы, а вторая группа входов элемента 18 (уравнения подключена к выходам регистра 17, вы- ход элемента 18.1 сравнения подключен

разрешения третьего шинного формирователя 15, входы которого подк второму входу третьего элемента И 21, первый вход которого подключен к выходу триггера 16, а третий вход которого подключен к разряду шины 3.2 управления Прием, выход третьего элемента И 21.1 подключен к второму входу четвертого элемента И 22 и к второму входу разрешения дешифратора 4 адреса памяти, первый вход четвертого элемента И 22 подключен к разря- ду шины 3.2 управления Чтение памяти, а выход четвертого элемента И 22 подключен к первому и второму

разрешения третьего шинного формирователя 15, входы которого под

ключены к внешним сигналам логических условий 15.1.

50

gg

5U18653 6

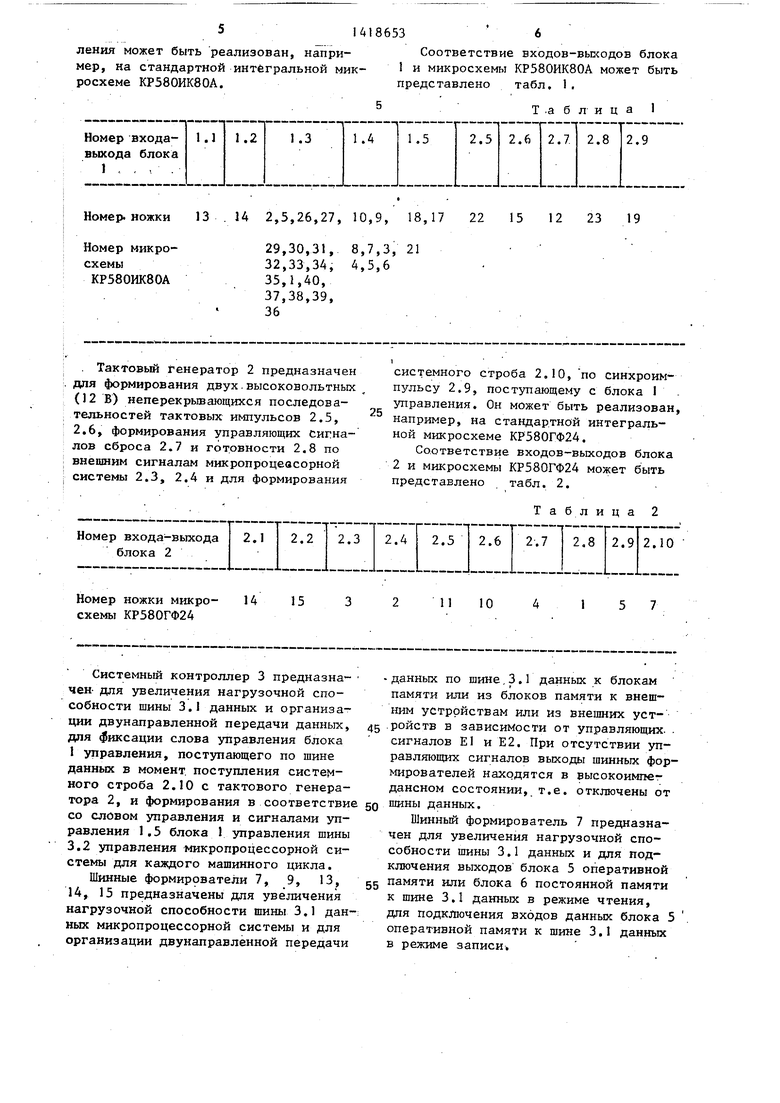

ления может быть реализован, напри- Соответствие вхсдов-вьпсодов блока мер, на стандартной интегральной мик- 1 и микросхемы КР580ИК80А может быть росхеме КР580ИК80А.представлено табл. 1.

5Т .а б л и ц а 1

Номер-ножки 13 . 14 2,5,26,27, 10,9, 18,17 22 15 12 23 19

29,30,31,

32,33,34,

35,1,40,

37,38,39,

36

. Тактовый генератор 2 предназначен для формирования двух.высоковольтных (12 В) неперекрьшающихся последовательностей тактовых импульсов 2.5, 2.6, формирования управляющих сигналов сброса 2.7 и готовности 2,8 по внешним сигналам микропроцевсорной системы 2.3, 2.4 и для формирования

Номер ножки микросхемы КР580ГФ24

14

15

Системный контроллер 3 предназна- чен- для увеличения нагрузочной способности шины 3.1 данных и организации двунаправленной передачи данных, для фиксации слова управления блока 1 управления, поступающего по шине данных в момент, поступления систе - ного строба 2,10 с тактового генератора 2, и формирования в соответстви со словом управления и сигналами управления 1.5 блока 1 управления шины 3.2 управления микропроцессорной системы для каждого машинного цикла.

Шинные формирователи 7, 9, 13, 14, 15 предназначены для увеличения нагрузочной способности шины 3.1 дан ных микропроцессорной системы и для организации двунаправленной передачи

8,7,3, 21 4,5,6

5

системного строба 2.10, по синхроимпульсу 2.9, поступающему с блока I управления. Он может быть реализован, например, на стандартной интегральной микросхеме КР580ГФ24.

Соответствие входов-вькодов блока 2 и микросхемы КР580ГФ24 может быть представлено табл. 2.

Таблица 2

11

10

данных по шине,3.1 данных к блокам памяти или из блоков памяти к внешним устройствам или из уст- .ройств в зависимости от управляющих. . сигналов Е1 и Е2. При отсутствии управляющих сигналов выходы шинных формирователей находятся в высокоимпег дансном состоянии, т.е. отключены от шины данных.

Шинный формирователь 7 предназначен для увеличения нагрузочной способности шины 3.1 данных и для подключения выходов блока 5 оперативной памяти или блока 6 постоянной памяти к шине 3.1 данных в режиме чтения, для подключения входов данных блока 5 оперативной памяти к шине 3.1 данных в режиме записи.

Шинные формирователи 9 ввода-вывода предназначены для увеличения нагрузочной способности шины 3.1 данных и ДЛЯ подключения к шине 3,1 данных g информационных входов.9.1 в режиме ввода из устройства ввода, для. подклю- чения шины 3.1 данных к информацион-j нын выходам 9.2 в режиме вывода в уст ройство вьшода.10

Шинный формирователь 13 предназначен для увеличения нагрузочной способ ности .разряда шины 3.1 данных и для

Дешифратор 8 адресов устройств ввода-вьтода предназначен для дешифра ции адресов устройств ввода-вьшода при наличии сигнала разрешения, который поступает на входы Е1, Е2 в том случае, если на шине 3.2 управления

приема программирующего бита в режиме вьшода в устройство вывода. 15 выставлен сигнал вывода в устройство Шинный формирователь 14 предназна- вывода либо.сигнал ввода в устройст- чен для увеличения нагрузочной способности .1 данных и приема информации об адресе точки многозначного

во ввода.

Дешифратор 8 адресов устройств вво да-вьшода в зависимости от адреса фо

ветвления программы в режиме вывода в 20мирует сигналы подключения шинных

устройство вьшода.формирователей устройств ввода-вьшода

Шинный формирователь 15 предназна- 8.1, подключения шинного формирова-течен для увеличения нагрузочной способ-ля 13 - сигнал 8.2, сигнал подслючености шины 3.1 данных и подключенияния шинного формирователя 1А - сигнал

к ней сигналов внешних логических 258.3. условий 15.1 в режиме чтения памяти. Первый элемент ИЛИ 10 предназначен

Дешифратор 4 адреса памяти пред-для формирования разрешающего сигнала . назначен для дешифрации адреса, вы-Е1 дешифратора 4 адреса памяти по наставленного на шине 1.3 адреса микро-личию на шине 3.2 управления одного процессорной системы, и выработки сиг-30из сигналов Чтение памяти, Запись налов подключения (выборки кристалла)р память. Второй элемент ИЛИ 11 предлибо блока 5 оперативной памяти, либо блока .6 постоянной памяти в том слу- чае, если на шине 3.2 управления микропроцессорной системы выставлены сигналы чтения памяти или записи в память. В этом случае имеется активный уровень сигнала на входе Е1.

Дешифратор 4 адреса памяти предназначен также для блокировки памяти в точке многозначного ветвления программы. В этом случае имеется активный уровень сигнала на входе Е2 дешифратора адреса памяти.

Блок 5 оперативной памяти предназначен для записи данных, поступающих из микропроцессора, и хранения их только во время работы микропроцессорной системы. Данные записьшаются и хранятся в ячейках памяти, которые выбираются в соответствии с их адресом по сигналам разрешения Е - выбора кристалла, WR - запись.

Блок 5 оперативной памяти может быть реализован, например, на стан- артньк интегральных микросхемах 541 РУ2.

Блок 6 постоянной памяти предназначен для хранения неразрушаемых данных

и считьшания их в блок 1 управления в соответствии с адресными сигналами при наличии разрешающих сигналов Е1, Е2. Блок 6 постоянной памяти может быть реализован, например, на стандартных интегральных микросхемах 556 РТ4.

Дешифратор 8 адресов устройств ввода-вьтода предназначен для дешифрации адресов устройств ввода-вьшода при наличии сигнала разрешения, который поступает на входы Е1, Е2 в том случае, если на шине 3.2 управления

выставлен сигнал вывода в устройство вывода либо.сигнал ввода в устройст-

выставлен сигнал вывода в устройство вывода либо.сигнал ввода в устройст-

во ввода.

Дешифратор 8 адресов устройств ввода-вьшода в зависимости от адреса форназначен для формирования разрешающего сигнала Е2 шинного формирователя памяти по наличию на выходах дешифратора 4 адреса памяти одного из сигналов 4.1, 4.2, т.е. тогда, когда идет обращение блока упр авления либо к блоку 6 постоянной, либо к блоку 5 . оперативной памяти. Третий элемент

ИЛИ 12 предназначен для формирования разрешающего сигнала Е1, Ё2 для де- , шифратора 8 адресов устройств ввода- вывода по наличию на шине 3.2 управ- ления одного из сигналов Вывод в. .

устройство вьшода, Ввод в устройство ввода.

Триггер 16 предназначен для приема с первого выхода шинного формирователя 13 и хранения программирующего бита для разрешения дисциплины многозначного ветвления программы (при установке триггера в состояние логической 1). Триггер 16 может быть реализован, например, на стандартной интегральной микросхеме 155 Ш2.

Регистр 17 предназначен для приема и хранения программирующего сигнала,.

поступающего с шинного формирователя, определяющего точку многозначного нет- влеиия программы, /

Элементов сравнения предназначен для формирования сигнала совпадения информации, выставленной на шине 1.3 адреса, и информации, хранящейся в регистре 17, т.е. для определения точки многозначного ветвления програм-ю мы.

Первый элемент И 19 предназначен для формирования сигнала синхрониза- ции триггера 16 при совпадении сигнала с выхода 8.2 дешифратора 8 адре- 15 сов устройств ввода-вывода и сигнала Вывод в устройство вьюода на шине 3.2 управления. Второй элемент И 20 предназначен для формирования сигнала синхронизации регистра 17 при сов- 20 падении сигнала с. выхода 8.3 дешифратора 8 адресов .ввода-вывода и сигнала Вывод в устройство вьшода на шине 3.2 управления. Третий элемент И 21 предназначен для формирования сигна- 25 Iла блокировки дешифратора 4 адреса ;памяти при совпадении сигнала 18.1 с ;выхода элемента 18 сравнения, сигнала I логической единицы с выхода триггера

щий сначала на вход 2.4 тактового ге нератора 2. Управление .процессами об мена информацией в микропроцессорной системе осуществляет системный контроллер 3, который принимает и дешифрирует слово состояния блока управле ния 1, поступающее по шине 1.4 данны в первом такте каждого мап;инного цик ла по сигналу с выхода 2.10 тактовог генератора 2, который, в свою очеред формируется по сигналу синхронизации блока 1 управления, поступающему на вход 2.9 тактового генератора 2.

Микропроцессорная система может работать в режимах прямого доступа в память и прерьгоания при подаче соответствующих сигналов на входы 1.1 и 1.2 (фиг. I) блока управления и введении дополнительного оборудования, однако в предлагаемой микропроцессорной системе эти режимы не используются, .

Выходные сигналы адреса блока 1 управления поступают на адресную шину 1,3 микропроцессорной системы. Системный контроллер 3 принимает так же выходные сигналы управления 1.5 и по слову состояния блока 1 управлени

16 и сигнала Прием с шины 3.2 управ-30 и сигналам управления 1.5 формирует

:ления. Четвертый элемент И 22 пред- |Назначен для формирования сигнала под ключения внешних логических условий 15.1 к шине данньгх при совпадении сигнала 21.1 с выхода третьего элемента И и сигнала Чтение памяти с шины управления.

Рассмотрим работу предлагаемой микропроцессорной системы.

Микропроцессорная система может работать в двух режимах: обычньй режим, режим многозначного ветвления программы.

. В обычном режиме работы тактовый генератор 2 формирует на своих выходах 2.5 и 2.6 (фиг. 1, 2) тактовые последовательности, которые синхронизируют внутренние процессы в блоке I управления. Стабильность тактового генератора 2 обеспечивается подключением к его входам 2.1 и 2.2 кварцевого резонатора. Блок 1 управления генерирует выходные сигналы после сигнала Сброс, который поступает на вход 2.3 тактового генератора 2 и с .выхода 2.7 тактового генератора 2 на вход 2.7 блока 1 управления, если на входе 2.8 блока управления 1 установлен сигнал логической 1, поступающий сначала на вход 2.4 тактового генератора 2. Управление .процессами обмена информацией в микропроцессорной системе осуществляет системный контроллер 3, который принимает и дешифрирует слово состояния блока управления 1, поступающее по шине 1.4 данных в первом такте каждого мап;инного цикла по сигналу с выхода 2.10 тактового генератора 2, который, в свою очередь формируется по сигналу синхронизации блока 1 управления, поступающему на вход 2.9 тактового генератора 2.

Микропроцессорная система может работать в режимах прямого доступа в память и прерьгоания при подаче соответствующих сигналов на входы 1.1 и 1.2 (фиг. I) блока управления и введении дополнительного оборудования, однако в предлагаемой микропро цессорной системе эти режимы не используются, .

Выходные сигналы адреса блока 1 управления поступают на адресную шину 1,3 микропроцессорной системы. Системный контроллер 3 принимает также выходные сигналы управления 1.5 и по слову состояния блока 1 управления

5

0

шину 3.2 управления микропроцессорной системы. Кроме того, системный контроллер 3 рбеспечивает двунаправ- . ленную передачу данных по шине 1.4 данных и формирует шину 3.1 данных микропроцессорной системы.

Блок управления (фиг. 1) считьша- ет и выполняет программу, записанную в блоки постоянной 6 или оперативной 5 памяти. На дешифратор 4 адреса памяти поступает адресная информация с. шины 1.3 адреса и, если на ней уста- новлен адрес памяти, а на шине 3.2 управления имеются активные уровни 5 сигналов Чтение из памяти, Запись в память, на вькоде дешифратора 4,1 адреса памяти формируется либо сигнал 4.1 подключения блока 6 постоянной памяти, если на шине адреса 1.3 адрес блока 6 постоянной памяти, либо сигнал 1,2 подключения блока 5 оперативной памяти, если на шине 1.3 адреса адрес блока 5 оперативной памяти. Выходы дешифратора 4 адреса памяти активизируются при наличии на шине 1.3 адреса адреса памяти, при наличии разрешающего сигналас выхода первого элемента ИЛИ 10, который формирует- ся, если на шине 3.2 управления име0

5

11

ются либо активный уровень сигнала Чтение из памяти, либо активный уровень сигнала Запись в память и при отсутствии запрещающего сигнала 21.1.

Сигналы 4.1 и 4.2 поступают на первые входы разрешения блоков постоянной 6 или оперативной 5 памяти, Второй вход разрешения блока б постоянной памяти активизируется сигналом Прием шичы 3.2 управления микропроцессорной системы и, если выбран адрес блока 6 постоянной памяти, идет цикл Чтение из памяти, что сопро- вождается сигналом Прием, то выходы блока 6 постоянной памяти подключаются через шинный формирователь 7 памяти к шине 3.1 данных микропроцессорной системы. При этом шинный формиро- ватель 7 памяти переводится в режим вьщачи ин(}хэрмации на шину 3.1 данных по первому входу разрешения сигналом Прием шины 3.2 управления, а по второму входу разрешения - сигналом , с выхода второго элемента ИЛИ II,. который формируется в случае, если идет обращение к блокам оперативной 5 или постоянной 6 памяти, т.е. .активизируется выход 4.1 или 4.2 дешифратора 4 памяти. Чтение блока 5 оперативной памяти происходит аналогично чтению блока 6 постоянной памяти, причем выходы данных блока 5 оперативной памяти и выходы данных блока 6 постоянной памяти соединены по схеме МОНТАЖНОЕ ИПИ. Запись в блок 5 оперативной памяти происходит при активизации выхода 4.2 дешифратора 4 адреса памяти и при активизации второго разрешающего входа блока 5 оперативной памяти, при этом шинный формирователь 7 памяти по первому разрешающему входу устанавливается в режим ввода с шины 3.1 данных.

Обращение к устройствам ввода-вывода происходит в том случае, когда блок 1 управления выставляет на шине 1,3 адреса адрес устройства ввода-вывода при одновременной активизации на шине 3.2 управления сигнала Ввод из устройства ввод либо Вывод в устройство вывода. При этом активи- зируют ся первый и второй разрешающие входы дешифратора 8 адресов устройств ввода-вьшода сигналом с выхода третьего элемента ИПИ 12, на первый и второй входы которого поступают сигналы шины управления Ввод из устройства

8653 2

ввода, Вывод s устройство вьшода соответственно. Кроме того, активизируются первый вход разрешения одного

(- из шинных формирователей $ устройства ввода-вывода одним из сигналов с первой группы выходов 8.1-дешифратора адресов устройств ввода-вывода в висимости от номера устройства ввода10 вывода, к которому происходит обращение. Направление передачи данных определяется вторыми разрешающими входами шинных формирователей 9 устройств ввода-вывода, на которые по15 ступит сигнал шины 3.2 управления Ввод из устройства ввода. При этом в блоке 1 управления либо вводятся внешние информационные сигналы 9,1 по входам шинных формирователей 9 уст20 ройств ввода-вывода, либо вьшодится информация на внешние информационные выходы 9.2 по выходам шинных формирователей 9 устройств ввода-вывода. В режиме многозначного ветвления

25 программы микропроцессорная система работает следующим образом.

Вначале, при инициализации микропроцессорной системы производится программная настройка. При этом блок

13и бит информации с шины 3.1 данных микропроцессорной системы поступает на информационный вход триггера 16,

40 который устанавливается по синхросигналу, поступающему с выхода первого элемента И 19, выход которого активизируется в случае, если идет обращение к триггеру 16 и активизирован

45 сигнал Вывод в устройство вьтода шины 3.2 управления. Предварительное обнуление триггера 16 производится сигналом сброса 2.2. Затем регистр I7j как в устройство вьгоода, выводит5Q ся информация, определяющая точку многозначного ветвления программы. При этом второй шинный формирователь

14по первому и второму разрешающим входам сигналом с третьего выхода 8.3

55 дешифратора 8 адресов устройств ввода-вывода подключается к шине 3.1 данных в режиме вьшода в.устройство вьшодаJи информационные входы регистра 17 подключаются к шине 3.1 данных

микропроцессорной системы. Запись информации в регистр 17 проирходит при активизации сигнала на выходе второго Ьлемента И 20, т.е. на вход синхрони- зации регистра 17 поступает сигнал с

случае, если на шине 1.3 адреса уста- йовлен адрес регистра 17 и активизирован сигнал Вывод в устройство вы- Вода шины 3.2 управления, который юдключен к второму входу второго Элемента И 20, первый вход которого одклю ен к третьему выходу 8.3 де- цшфратора 8 адресов устройства ввода- фывода, а второй вход подключен к . 15 разряду шины 3.2 управления Вывод В устройство вьтода. Предварительное Обнуление регистра 17 может произво- ;диться сигналом сброса 2.3. : Таким образом, предварительная

йастройка микропроцессорной системы для режима многозначного ветвления программы заключается в установке Триггера 16, выходной сигнал которого разрешает проведение режима много- начного ветвления программы и в записи в регистр 17 йдреса точки много- ёначного ветвления программы.

Точку многозначного ветвления программы определяет элемент 18 сравнения, выход 18.1 (фиг. 1, 2) активизируется при совпадении адреса, выставленного на шине 1.3 адреса (фиг. 1, 2), и .адреса, записанного в регистр 17. При этом, если режим, многозначного йетвления программы разрешен (установлен триггер 16), на шине 3.2 уп10

20 25

30

35

равления активизирован сигнал При

4м, то активизируется выход 21.1 (фиг. 1, 2) третьего.элемента И 21, 1 отЬрый отключает дешифратор 4 аДреса Памяти по второму инверсному разрешающему (запрещающему) входу, и шин- Ный формирователь 7 памяти переводится в высокоимпедансное состояние по своим входам-выходам. Выход четвертого элемента, И 22, первый вход которого активизируется сигналом шины 3.2 управления Чтение памяти, а второй вход активизируется сигналом с выхода 21.1 третьего элемента И 21, переводит третий шинный формирователь 15 по первому и второму разрешающим входам в режим выдачи информации на тину 3.1- данных. Поэтому внешние ло- гические условия 15,1 поступают на ши Ишну З . далных микропроцессорной системы. Внешние логические условия 15.1 таким образом воспринимаются бло

блоком управления как один из байтов команды (второй байт на фиг. 2). Поэтому осуществляется многозначное ветвление программы в зависимости от набора логических условий 15.1 (фиг. 2),т.е. второй байт адреса перехода трехбайткой команды безусловной передачи управления (IMP) опреде- -ляется самими внешними логическими условиями 15.1, поэтому адрес перехода является многозначным, зависящим непосредственно от внешних логических условий 15.1.

Рассмотрим пример реализации предлагаемой микропроцессорной системы для микропроцессора КР580ИК80А.

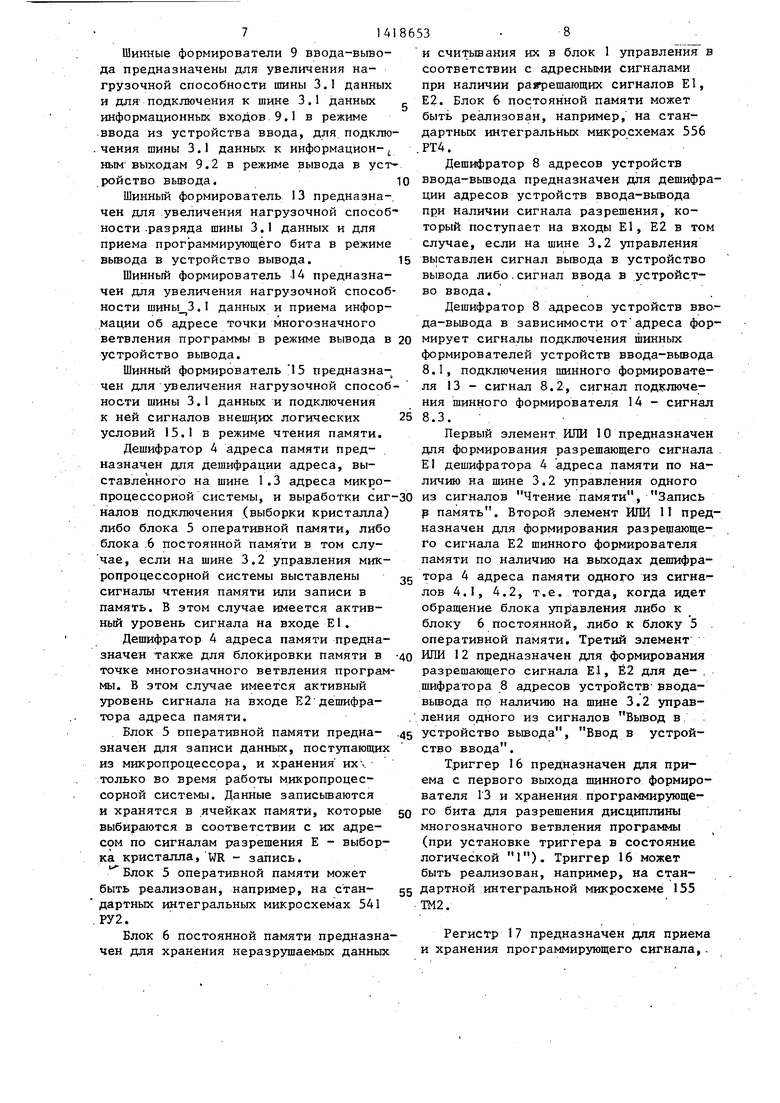

Необходимо обеспечить многозначную передачу управления в микропро- цессорной системе в зависимости от внешних сигналов логических условий X,, Хд в процессе выполнения некоторой подпрограммы PofA (т.е. обеспечить переход на одну из четырех меток МО, Ml, М2, МЗ).

Используем двухальтернативные команды перехода по переполнению 1C. Порт ввода 07..

30

Р( А

I

; сдвиг влево содержимого AJ; ; Переход на метку Ml, если

МО:

INPORT07 J ввод логических условий;

EAd ICM1

С 1;

RAoi ; сдвиг влево содержимого ICM2 ; .переход на метку М2, если

С 5 .. ; х, О, Xfl 0;

Ml -RAd ICM3

; сдвиг влево содержимого AJ) ; переход на метку МЗ, если

С

;

;

; XQ

0;

55

50

М2

0; хр l,

- 1-- : X

11; хо 1;

По времени такая операция многозначной передачи управления занимает 38 тактов работы микропроцессорной системы, причем время передачи управления увеличиваете при увеличении разрядности внешних сигналов логических условий и увеличении количестляется временем вьшолнения команды безусловной передачи управления (IM Причем вре1мя настройки для дисципл

ва обращений к подпрограмме и оп- реализации многозначного ветвления

ределяется соотношением:

программы не входит в общее время полнения подпрограммы и произв дится в процессе предварительной и цииализации микропроцессорной сист мы: NSTR:MVC8 (и ввод в аккумулятор числ

k (to + 2

h-1

t.),

где Т - общее время передачи управления;п - разрядность внещних сигналов

логических условий; tg - время ввода внешних сигналов

логических условий; t. - суммарное время выполнения команд сдвига и перехода по переполнению;.

k - количество обращений к подпрограмме.

Используем команду РСН с. Порт ввода ф 7. Разрядность логических условий 8:

PrfA : .

PUSHH ; сохранить содержимое Н, L; INPORT07; ввод логических условий; MOVH, А $ загрузка регистра Н; MVIL, 0 ; обнуление регистра L; PCHL ; переход на метки МО+М2; РОРН ; восстановление Н, о(;

МО: . : . .

Ml:

I

M2:

Ю:

40

По времени это 48 тактов работы микропроцессорной системы, при- причем общее время передачи управления увеличивается при увеличении количества обращений к подпрограмме и 45 определяется соотношением:

T k..t,,

где Т - общее время передачи управления;

k - количество обращений к подпрограмме;

t - время многозначной передачи управления с помощью команды РСН в 48 тактам. При использовании предлагаемой микропроцессорной системы время многозначной передачи управления определяется временем вьшолнения команды безусловной передачи управления (IMP). Причем вре1мя настройки для дисциплины

программы не входит в общее время выполнения подпрограммы и производится в процессе предварительной ини- цииализации микропроцессорной системы:NSTR:MVC8 (и ввод в аккумулятор числа

80; ,

OUTPORT J5; вьшод в триггер;; MVI DP ; ввод в аккумулятор числа

DP;

ОиТРОНТ б; вывод в регистр 17; Ра(А:

20

IMP

DP: f -if ф f f

МО: . . .

25

30

Ml:

М2:

35

M3:

0

5

0

5

Здесь DP-адрес второго байта команды IMP. Таким образом, переход.на одну из меток МО : МЗ в процессе выполнения каждого обращения к подпрограмме будет осуществляться за время вьтолнения команды безусловного перехода, т.е. за 10 тактов. Время предварительной настройки, осуществляемой при инициировании микропроцессорной системы, не входящее во время вьтолнения подпрограммы , 34 такга.

Передача управления происходит на метке DP, т.е. в точке программы, когда содержимое программного счетчика или адрес, выставленный на щине 1.3 адреса (фиг. I, 2) было равно адресу второго байта команды IMP в подпрограмме . В этом случае адрес на шине 1.3 адреса равен адресу, записанному в регистре 17 (фиг. 1, 2).По сигналу Прием шины 3.2 управления

17

14

выход третьего элемента И 21 активи- зируется (триггер 16 установлен) .и память системы отключается, шинный формирователь 7 памяти переводится в высокоимпедансное состояние, а третий щинный формирователь 15 подключает к шине .3.2 данных сигналы внешних логи- |Ческих условий 15.1. Таким образом,, |на шину 3.2 данных выводятся сигналы |15.10(,, которые воспринима- тся микропроцессором как второй байт |командЬ1 IMP.

Следовательно, осуществляется пе- |реходпо адресу 000 yi ,0«((г)(( 2 т.е.. на одну из меток МО т М2 в зависимости от текущего значения сигналов внешних логических условий х,, х ,

аким образом, время многозначной |передачи управления в предлагаемой микропроцессорной системе определяет- |ся соотношением

Т k

-3

е Т k t

3

общее- вр.емя передачи управления;

количество обращений к подпрограмме;

время выполнения команды IMP (равно 10 тактам).

Формула изобретения

Микропроцессорная система для программного управления технологическими процессами, содержащая блок управления, тактовый генератор, системный контроллер, дешифратор адреса памяти, блок оперативной памяти, блок постоянной памяти, шинный формирователь памяти, дешифратор адреса устройств ввада-вьшода, шинные формирователи ввода-вьшода, первый, второй и третий элементы ИЛИ, причем первый и второй входы тактового генератора являются входами Сброс и Готовность микропроцессорной системы, пятый вход тактового генератора подключен к выходу с инхронизации блока управления, первый и второй выходы тактового гене ратора подключены к первому-и второму тактовым входам блока управления, третий и четвертый выходы тактового генератора подключены к входам Сброс, Готовность блока управления соответственно, пятый и шестой входы блока управления являются входами Захват и Запрос прерывания

0

5

0

микропроцессорной системы, пятьй выход тактового генератора подключен к входу синхронизации системного контроллера, адресные выходы блока управления являются шиной адреса микропроцессорной системы, входы-выходы данных блока управления и выходы управления подключены к входам-выходам ,- данных и входам управления системного контроллера соответственно, входы- выходы данных системного контроллера являются шиной данных мик ропроцессор- ной системы, а выходы управления системного контроллера являются шиной управления микропроце.ссорной системы,- информационные входы дешифратора адреса памяти подключены к шине адреса микропроцессорной системы, а первый вход разрешения дешифратора адреса памяти подключен к выходу первого элемента ШШ, первый и второй входы которого подключены к разрядам шины управления Чтение из памяти, За5 пись в память соответственно, первый выход дешифратора адреса памяти подключен к первому входу разрешения блока постоянной памяти и первому входу второго элемента ИЛИ, второй

Q выход дешифратора адреса памяти подключен к первому входу разрешения блока оперативной памяти и к второму входу второго элемента ИЛИ, второй вход разрешения блока постоянной памяти и первый вход разрешения шинного формирователя памяти подключены к разряду шины управления Прием,вто-. рой вход разрешения шинного формирователя памяти подключен к выходу вто.Q рого элемента ИЛИ, входы-выходы данных шинного формирователя памяти подключены к шине данных микропроцессорной системы, выходы данных шинного формирователя памяти подключены к.входам

.g данных блока оперативной памяти, а входы данных шинного формирователя памяти подключены к выходам данных блока постоянной памяти и блока оперативной памяти, адресные входы блока оперативной и блока-посто.янной памяти подключены к шине адреса микропроцессорной системы, вход записи оператив- ной памяти подключен к разряду шины управления Запись в память, .информационные входы дешифратора адресов устройств ввода-вьшода подключены к шине адреса микропроцессорной систе мы, а первый и второй входь, разрешения дешифратора адресов устройств

У

5

0

55

ввода-вывода подключены к выходу третьего элемента ИЛИ, первый и второй входы которого подключены к разрядам шины управления Ввод из устройства ввода, Вьюод в устройство вьюода - соответственно, первая группа выходов дешифратора адресов устройств ввода- вывод подключена к первым входам разрешения шинных формирователей ввода- вывода, вторые входы разрешения которых подключены к разряду шины управления Ввод из устройства ввода, входы шиннь1х формирователей ввода-вывода являются информационными входами шифратора адресов устройств вводамикропроцессорной системы, выходы шинных формирователей ввода-вьшода являются информационными выходами микропроцессорной системы, а входы- выходы шинных формирователей ввода- вьвода подключены к шине данных микропроцессорной системы, о т л и - ч а ю щ а я с я тем, что, с целью повьш1ения быстродействия, в нее введены первый, второй и третий,шинные формирователи, триггер, регистр, элемент сравнения, первый, второй, третий и четвертый элементы И, причем входы-выходы первого, второго и тре20

вывода, а второй вход которого под ключен к разряду шины управления В вод в устройство вывода, вход рбну ления регистра подключен к системно му сбросу - третьему выходу тактово генератораf первая группа входов эл мента сравнения подключена к шине а реса микропроцессорной системы/ а вторая группа входов элемента срав25 нения подключена к выходам регистра выход элемента сравнения подключен второму входу третьего элемента И, первый вход KOTorforo подключен к вы ходу триггера, а третий вход которо

тьего шинных формирователей подключе- - го подключен k разряду шины .управления Прием, выход третьего элемента И подключен к второму входу четвертого элемента Ник второму входу разрешения дешифратора адреса памяти, первый вход четвертого элемента И

ны к шине данных микропроцессорной системы, первый и второй входы разрешения первого шинного формирователя подключены к второму выходу дешифратора адресов устройств ввода-вьшоМ|да, первый выход первого шинного фор- подключен к разряду шины управления

мироватеЛя подключен к информационному входу триггера, вход синхронизации которого подключен к выходу первого элемента И, а вход сброса - к системному-сбросу, третьему выходу генератора, первьй вход первого элемента. И подключен к второму выходу.

Чтение памяти, а выход четвертого элемента И подключен к первому и второму взводам разрешения третьего шин- .Q ного формирователя, входы которого подключены к внешним сигналам логичес ких условий.

дешифратора адресов устройств ввода- вьшода, а второй вход подключен к разряду шины управления Вьшод в уст« ройство вьшода, первый и второй хо- ды разрешения второго шинного формирователя подключены к третьему выходу дешифратора адресов устройств вво- да-вьшода, выходы второго шинного формирователя подключены к информационным входам регистра, вход синхронизации которого подключен к выходу второго элемента И, первый вход которого подключен к третьему выходу де0

вывода, а второй вход которого подключен к разряду шины управления Вывод в устройство вывода, вход рбну- ления регистра подключен к системному сбросу - третьему выходу тактового генератораf первая группа входов элемента сравнения подключена к шине адреса микропроцессорной системы/ а вторая группа входов элемента срав. 5 нения подключена к выходам регистра, выход элемента сравнения подключен к второму входу третьего элемента И, первый вход KOTorforo подключен к вы-- ходу триггера, а третий вход которо Чтение памяти, а выход четвертого элемента И подключен к первому и второму взводам разрешения третьего шин- ного формирователя, входы которого подключены к внешним сигналам логичес ких условий.

п п по п по | поп

16

13

/.

12 рием

т ш

п п п о гп о-п и и п

/ А0 I А, у Аг

Шт

г г г

гл г г

г

г

| Микропроцессорная система | 1981 |

|

SU1172455A3 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство программного управления | 1981 |

|

SU1012205A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Г.,Пийль Е | |||

| И,,,Туру- та Е | |||

| Н | |||

| Построение программируемых .управляющих устройств | |||

| - М..: Энерго- атомиздат, 1984, с | |||

| Способ приготовления пищевого продукта сливкообразной консистенции | 1917 |

|

SU69A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-28—Подача