Изобретение относится к системам автоматики и может быть использовано в автоматизированных системах управления машинами, механизмами, сигнализацией, поточными линиями и т.д.

Целью изобретения является повышение быстродействия устройства.

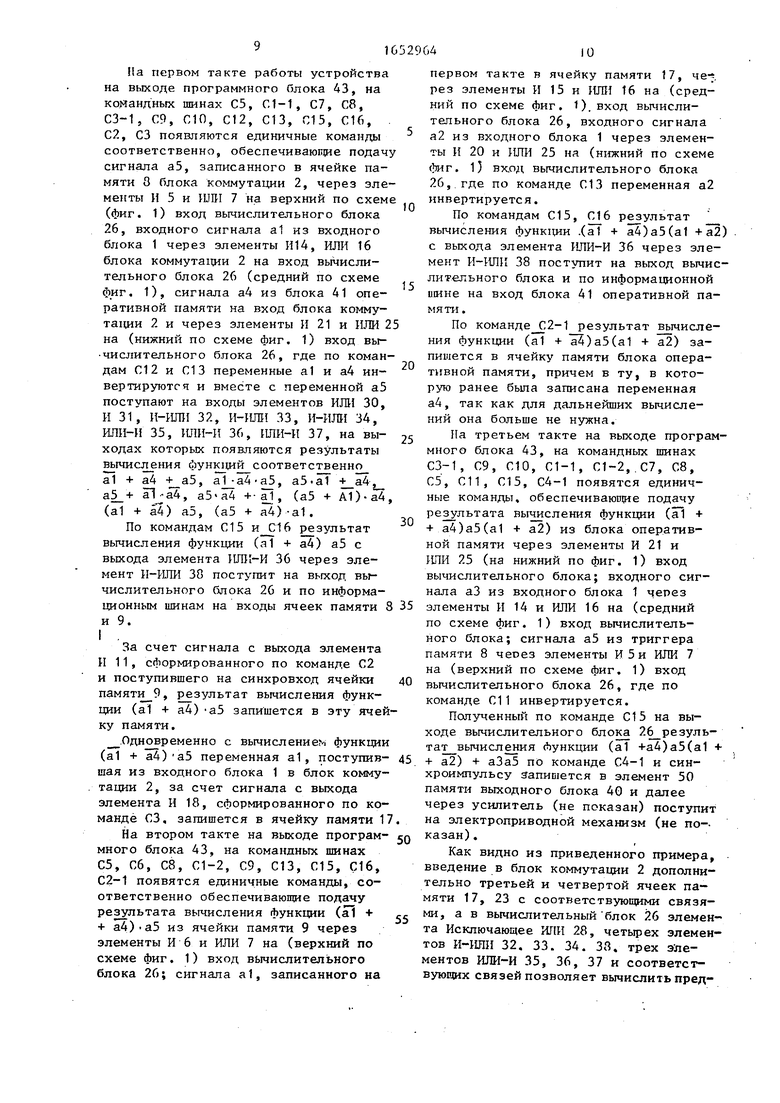

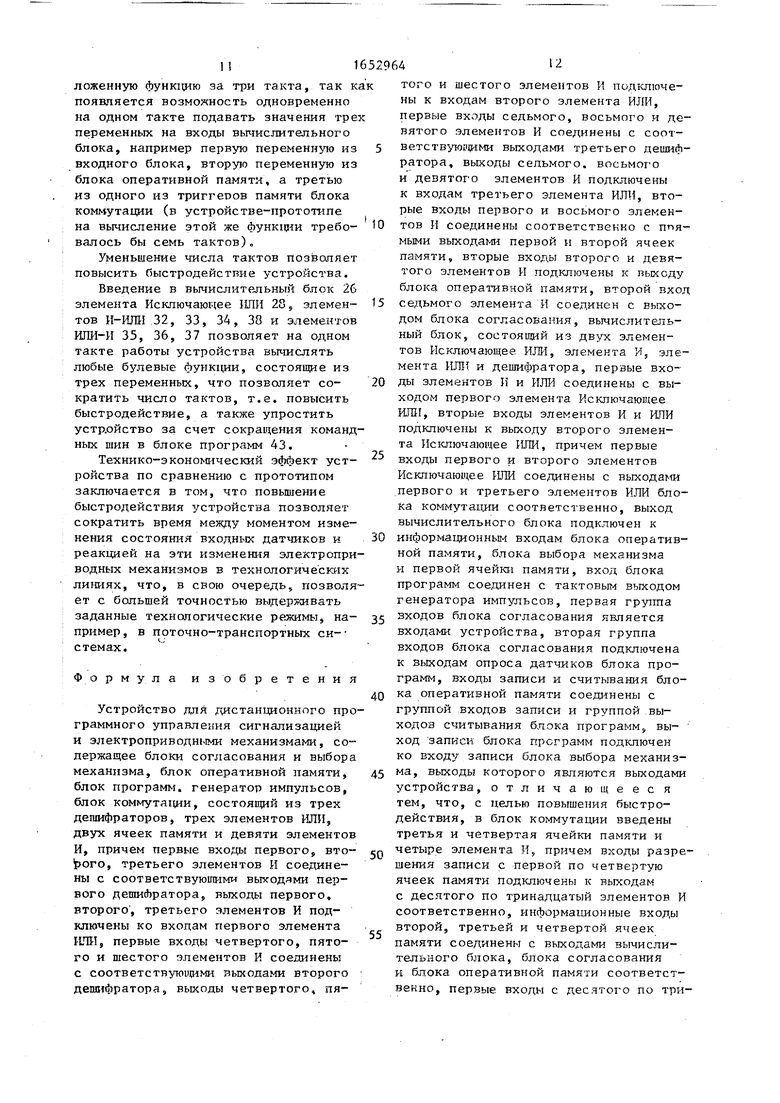

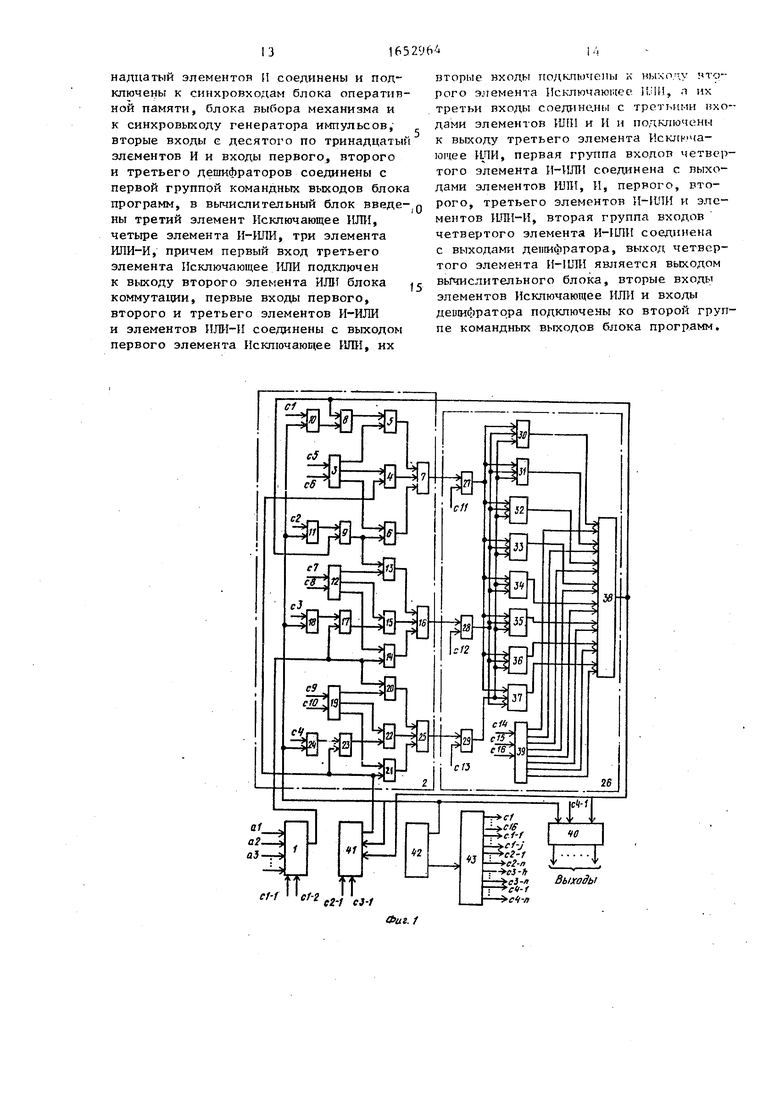

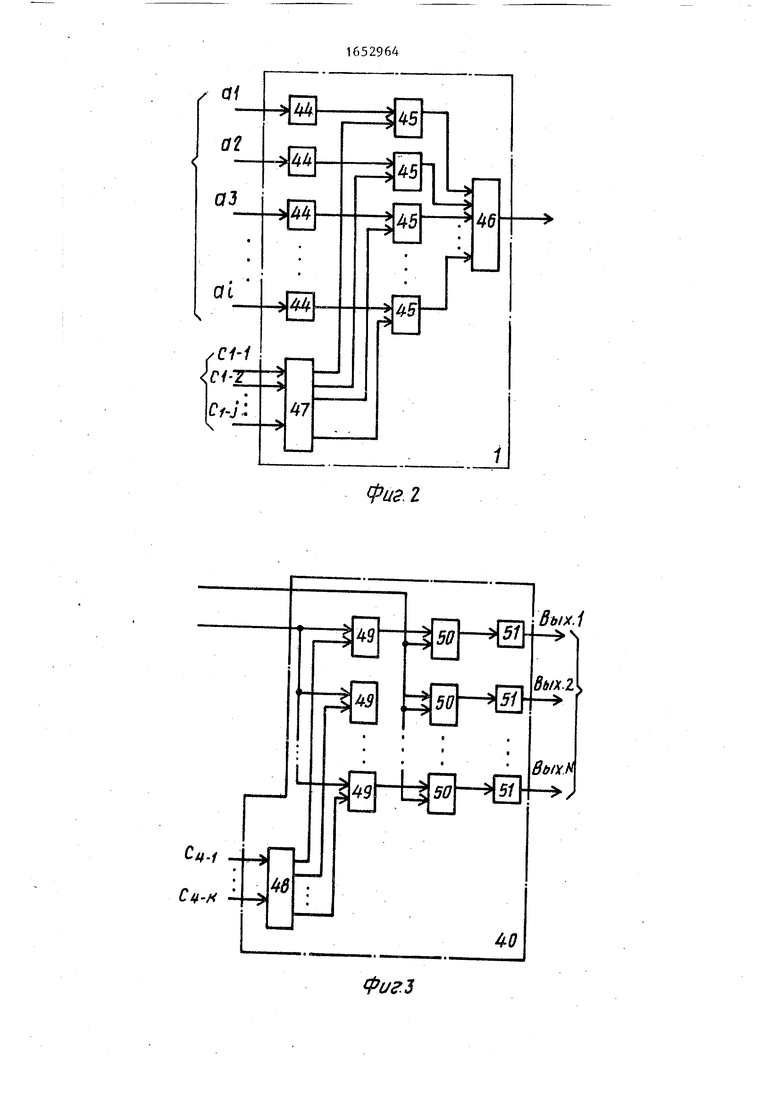

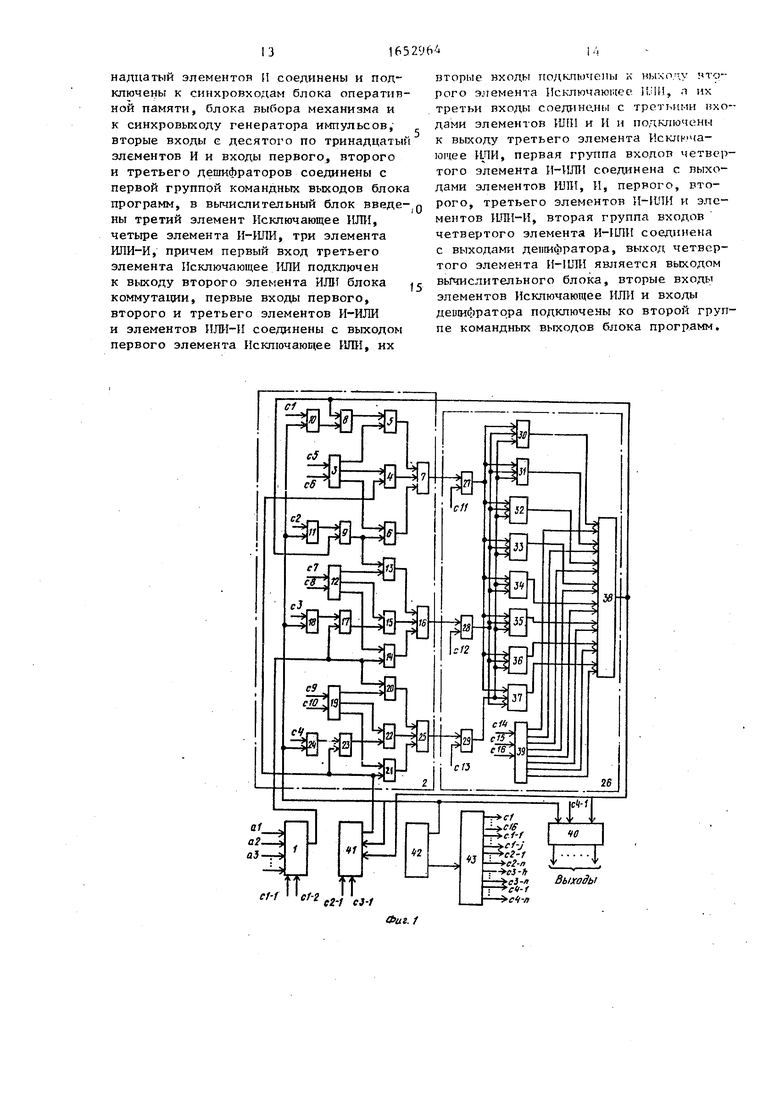

На фиг. 1 представлена функциональная схема устройства; на фиг.2 - структурная схема построения блока

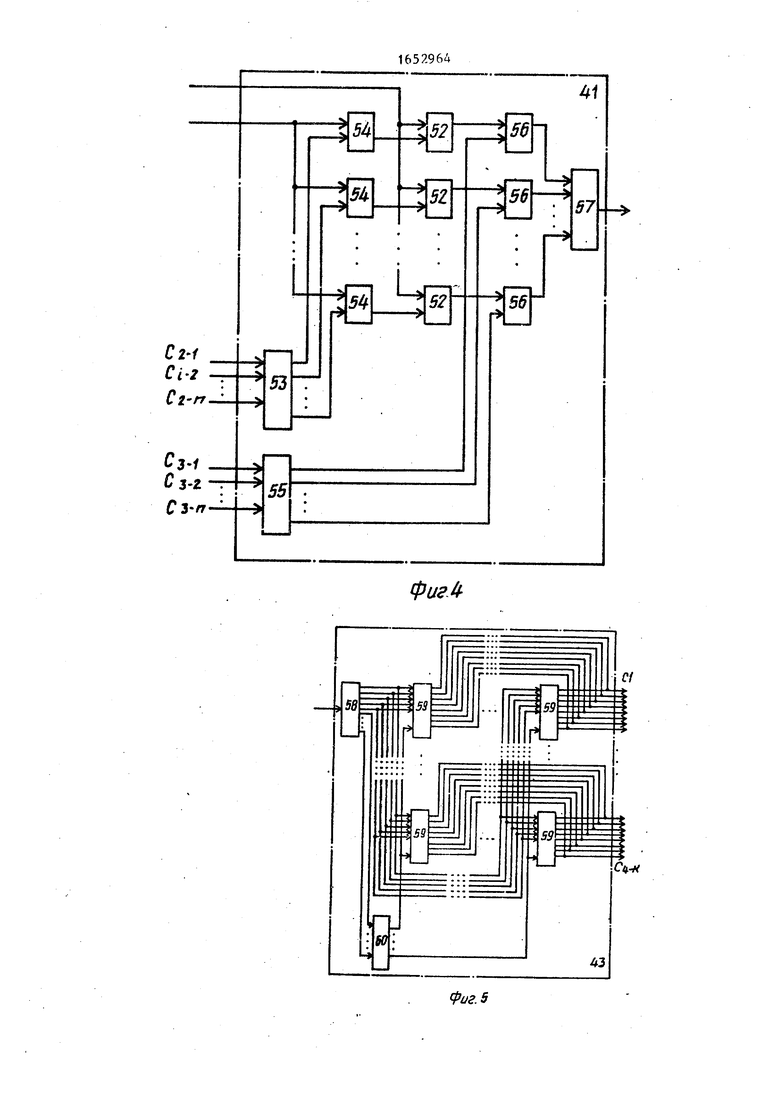

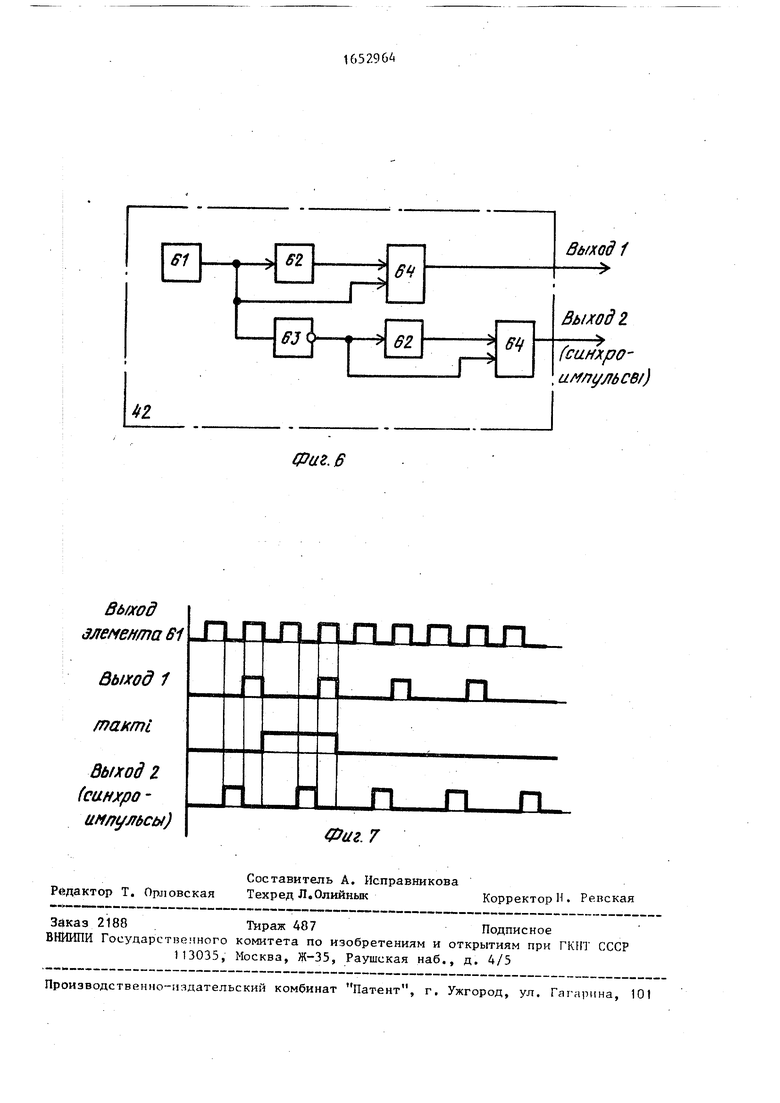

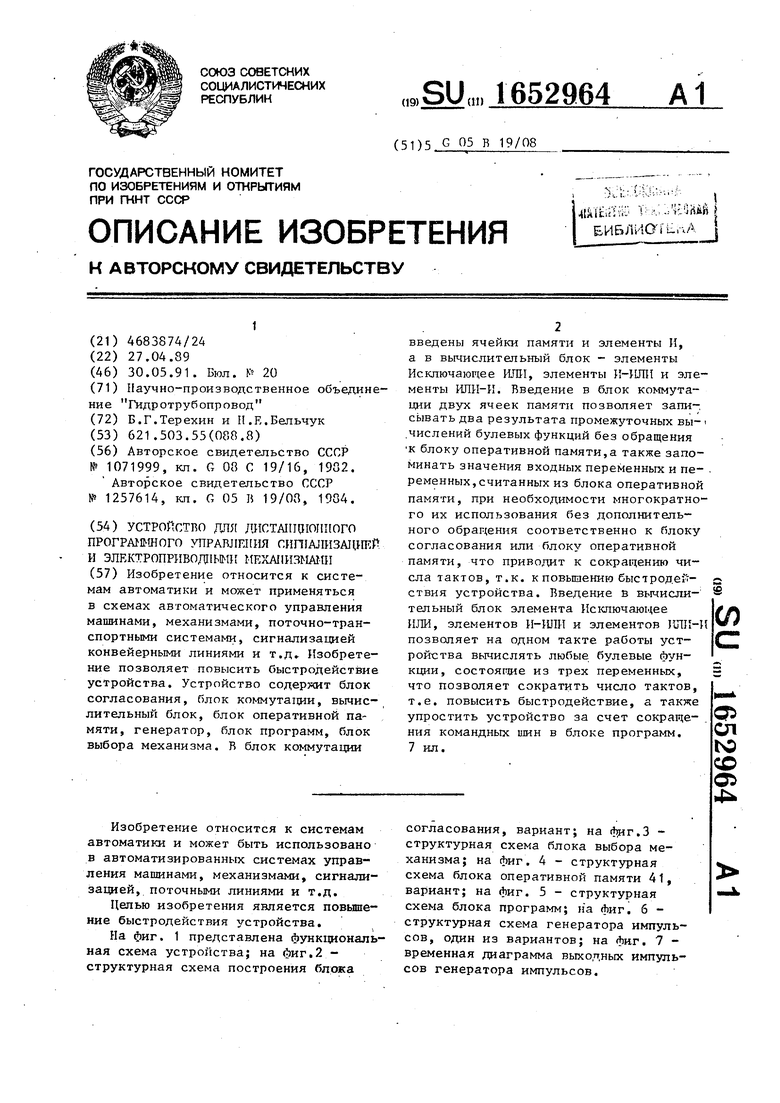

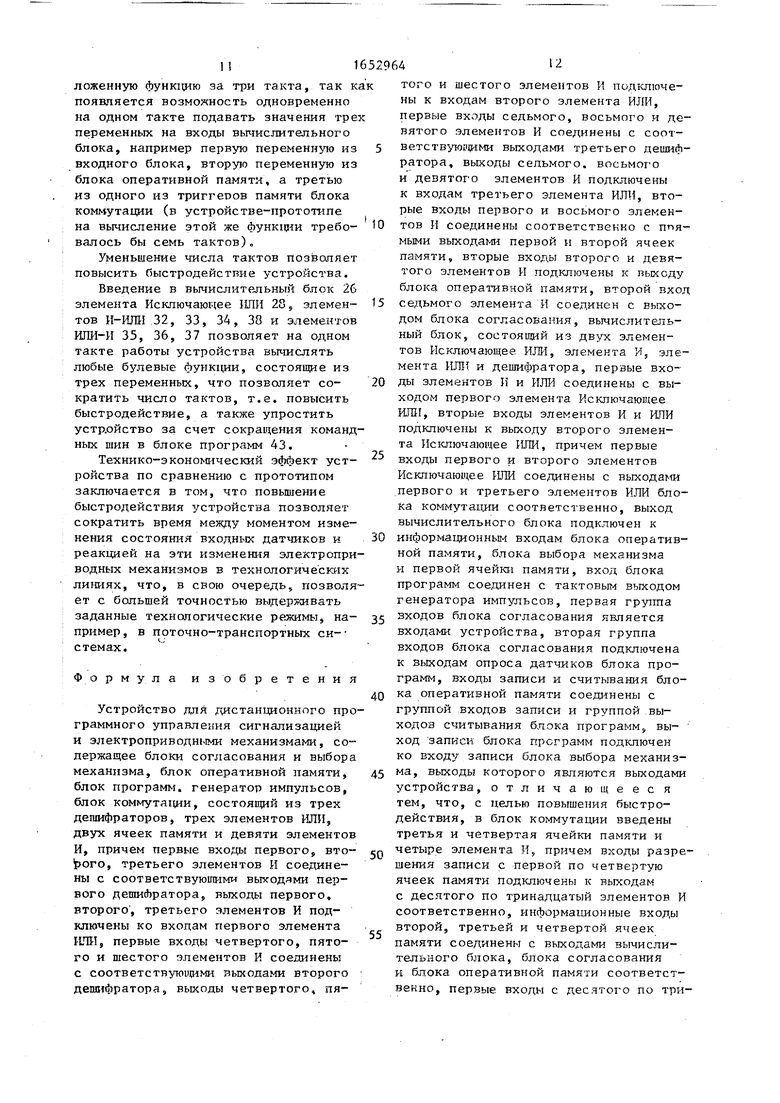

согласования, вариант; на фиг.З - структурная схема блока выбора механизма; на фиг. 4 - структурная схема блока оперативной памяти 41, вариант; на фиг. 5 - структурная схема блока программ; на фиг. 6 - структурная схема генератора импульсов, один из вариантов; на фиг. 7 - временная диаграмма выходных импульсов генератора импульсов.

Устройство состоит из входного блока 1, входы которого подключены к первичным дз1чикам (не показаны), а выход связан с блоком коммутации , содержащим дешифратор 3, элементы И 4, 5, (, ИЛИ 7, ячейки памяти 8 и 9 элементы И 10 и 11, дешифратор 12, элементы И 13, 14, 15, ИЛИ 16, ячейку памяти 17, элемент И 18, дешифра- тор 19, элементы И 20, 21, 22, ячейку памяти 23 и элементы И 24, ИЛИ 25; вычислительного блока 26, содержащего элементы Исключающее ИЛИ 27-29, элемент ИЛИ 30, элемент И 31, элементы И-ИПИ 32-34, элементы ИЛИ-И 35-37, элемент И-ИЛИ 33 и дешифратор 39, блока выбора 40 механизма, блока 41 оперативной памяти, генератора импульсов 42, синхронизирующего работу устройства, и блока программ 43. Символами С1...С16, C1-1...C1-J, С2-1... ...C2-n, C3-1...C3-n, C4-1...C4-k обозначены командные шины, по которым поступают соответствующие коман- ды, формируемые блоком программ 43 для управления устройством; символами а1, а2, a3...ai обозначены сигналы, поступающие от первичных датчиков на входы входного блока 1.

Входной блок 1 (фиг. 2) состоит из стандартных элементов согласования 44, (например элементов И-208 серии Логика И,на вход которых поступают сигналы от первичных датчиков, с выхода снимаются унифицированные сигналы, соответствующие логическим сигналам О и 1), элементов считывания 45, в качестве которых можно применять двухвходовые элементы И, элемента ИЛИ 46, объединяющего по выходу все элементы считывания 45, и дешифратора 47, управляющего элементами считывания 45 по командам C-1...C1-J, поступающим из программного блока.

Блок выбора 40 механизма (фиг.З) состоит из дешифратора 48, элементов И 49, элементов памяти 50, усилителей 51.

Плок 41 оперативной памяти (фиг. 4 состоит из ячеек памяти 52, дешифра- тора 53, элементов И 54, дешифратора 55, элементов И 56, элемента ИЛИ 57.

Цпок программ 43 (фиг. 5) состоит из счетчика импульсов 58, элементов памяти 59 и дешифратора 60.

Генератор импульсов 42 (фиг. 6) состоит из мультивибратора 61, счет0

0 5 0

5

0

5

ных триггеров 62, инвертора 63 и элементоь И 64.

Из структурной схемы входного блока 1 видно, что для опроса имеющихся первичных датчиков нужно определенное количество команд С1-1...С1-1, причем количество команд определяется по формуле

Nc 1°82п,

где N - количество команд, поступающих на входы дешифратора из программного блока и необходимых для опроса первичных датчиков, подключенных к входному блоку;

п - количество первичных датчиков, подключенных к входному блоку.

Блок 41 оперативной памяти имеет информационный вход, на который с выхода вычислительного блока 26 поступают результаты промежуточных вычислений функций булевых переменных, необходимых для. дальнейших вычислений; синхровход, на который с выхода генератора импульсов 42 поступают синхроимпульсы, необходимые для надежной записи информации в ячейки памяти 52; входы, на которые из блока 43 поступают команды записи и считывания, необходимые для выбора конкретной ячейки памяти, в которую необходимо записать информацию или произвести считывание информации.

С выхода блока 41 оперативной памяти считанная из какой-либо ячейки памяти 52 информация поступает на вход блока коммутации 2, где используется для дальнейших вычислений„

Для записи информации в какую-либо ячейку памяти 52 (фиг. 4) на вход дешифратора 53 необходимо подать соответствующие команды из блока 43. При этом активизируется один н выходов дешифратора 53 и сигнал логической 1 с его выхода поступит на вход конкретного элемента И 54, на выходе которого, по совпадению сигнала с дешифратора 53 с синхроимпульсом, поступившим с выхода генератора 42, появится сигнал разрешения записи в ячейку памяти 52. Таким образом, информация, поступившая на вход блока оперативной памяти, запишется в конкретную ячейку памяти 52.

При считывании информации из ячейки памяти 52 на вход дешифратора 55 необходимо подать соответствующие

команды из программного блока 43. При этом сигнал логической-единицы с соответствующего выхода дешифратора 55 поступит на вход элемента If 5fS н на его выходе появится сигнал, соответствующий информации, записанной в ячейку памяти 52, которая подключена к его второму входу.

Таким образом, информация из ячейки памяти 52 считывается через элемент И 56 и поступает на вход элемента ИЛИ 57, выход которого является выходом блока 41 оперативной памяти.

Количество команд записи зависит от необходимого количества ячеек памяти в блоке оперативной памяти и определяется по формуле

NC 1оКгпа где N - количество команд записи,

оступаюших на вход дешифратора 55 блока оперативной пмяти 41 из программного блока 43;

п0 - количество ячеек памяти п блоке оперативной памяти.

Количество команд считывания определяется аналогично командам записи.

Структурная схема одного из вариантов блока программ приведена в прототипе (авт.свид. СССР № 1257614, кл. О 05 В 19/08) изобретения.

На фиг. 5 приведен другой вариант структурной схемы блока программы 43 построенной на стандартных ГТПЗУ (например, серии 155РЕЗ).

На вход блока программ 43 поступают тактовые импульсы с выхода генератора импульсов 42, а на выходе, на командных шинах, в соответствующи моменты времени (согласно записанной в ПГПУ программе) появляются команды управления.

Команды С1-С10 с выхода блока программ 43 поступают на вход блока коммутации 2, команды С11-С16 поступают на вход вычислительного блока 26, команды C1-1...C1-J - на вход блока 1, команды С2-1...С2-П, СЗ-1.. ...СЗ-п - на вход блока 41 оперативной памяти, а команды C4-1...C4-k - на вход блока 40.

Количество команд, поступающих на входы блока 1, блока 42 и блока 41 оперативной памяти, зависит от количества необходимых входов, выходов и ячеек памяти.

0

5

0

5

0

5

0

5

На яход счетчика импутьгор 5Я поступают тактовые импульсы с яьгхода генератора импульсов. Выхолы счетчика импульсов 58 подключены соотьетст- венно к входам эпементов памяти 59 и к входам дешифратора 60.

С вьгхоцов дешифратора 60 на входы элементов памяти 59 поступают сигналы Разрешение считывания, а по сигналам с выхода счетчика импульсов 58, поступающим на входы элементов памяти 59, происходит тюследовател ная выборка элементов памяти, в которые записана )трограмма работы устройства.

Генератор импульсов 42 льцчает две серии импульсon, сдвинутых одна относительно другой. Первая серия тактовых импульсон поступает в программный блок 43, и на их основе формируются команды управления, л вторая серия синхроимпульсов поступает на блок 41 оперативной памяти вместе с командами записи через -элементы И 54 на син- хронходы ячеек памяти 52, что обеспечивает окончание импульсов записи в ячейки памяти 52 до окончания импульсов, несуг(их информацию. В качестве такого генератора можно ИСПОЛЬЧОРЛТЬ, например, микросхему серии 580 или представленный на с шг. 6.

Блок выбора 40 механизма имеет информационный вход, на который с выхода вычислительного блока 26 поступают результаты вычислений функций булевых переменных, являющиеся командами управления для электроприводных механизмов и элементов сигнализации; синхровход, на который с выхода генератора импульсов 42 поступают синхроимпульсы, необходимые для надежной записи информации л элементы памяти блока 40; входы чаписи, на которые из программного блока 43 поступают команды, необходимые для выбора конкретного элемента памяти в блоке 40, в которую записывается результат вычисления функции булевых переменных, причем количество команд зависит от количества элементов памяти в блоке 40, т.е. от количества выходов и, соответственно, элементов сигнализации и электроприводных механизмов, к ним подключенных.

Таким образом, в блоке выбора 40 механизма на вход дешифратора 40 поступают команды из программного блока 43, в зависимости от которых активизируется один из выходов дешифраi орл (появляется сигнал логической 1), и по солпадению сигнала логической 1 и синхроимпульса на выходе одного из элементоп 49 (двухвходового элемента И) появляется импульс разре - шения записи информации п один из элементов памяти 50 (триггер).

С выхода элемента памяти 50 информация через усилитель 51 поступит на один из выходов выходного блока и далее на конкретный электроприводной механизм или элемент индикации.

На одном такте вычислительный

+ а4) а5 (а1 + а2) + аЗа5. необходимо иметь возможность опрашивать три первичных датчика, что и предусмотрено наличием команд С1-1 и С1-2, поступающих во входной блок из программного блока, причем условимся, что по командам С1-1 1, С1-2 О опрашивается первый датчик, и на выход входного блока поступает переменная а1, по командам С1-1 О, С1-2 1 на ьыход входного блока поступает переменная а2, по командам С1-1 С1-2 1 на выход входного

Изобретение относится к системам автоматики и может применяться в схемах автоматического управления машинами, механизмами, поточно-транспортными системами, сигнализацией конвейерными линиями и т.д. Изобретение позволяет повысить быстродействие устройства. Устройство содержит блок согласования, блок коммутации, вычислительный блок, блок оперативной памяти, генератор, блок программ, блок выбора механизма. В блок коммутации введены ячейки памяти и элементы И, а в вычислительный блок - элементы Исключающее ИЛИ, элементы И-ИЛИ и элементы ИЛИ-И. Введение в блок коммутации двух ячеек памяти позволяет записывать два результата промежуточных вычислений булевых функций без обращения к блоку оперативной памяти,а также запоминать значения входных переменных и переменных,считанных из блока оперативной памяти, при необходимости многократного их использования без дополнительного обращения соответственно к блоку согласования или блоку оперативной памяти, что приводит к сокращению числа тактов, т.к. к повышению быстродействия устройства. Введение в вычислительный блок элемента Исключающее ИЛИ, элементов И-ИЛИ и элементов ГЛП-Н позволяет на одном такте работы устройства вычислять любые булевые функции, состоящие из трех переменных, что позволяет сократить число тактов, т.е. повысить быстродействие, а также упростить устройство за счет сокращения командных тин в блоке программ. 7 ил. Ј (Л Ф СЛ IsD СО о 4

20

блок 26 может вычислить одну из логи- 15 блока поступает переменная аЗ.

ческих функций:

А1 А2-АЗ А А2-АЗд А1-А2-АЗ; A T A2vA3; A1j A2-A3; А1 А2- A3; А1 А2 « «A3; А1-А2-АЗ; А2 + A3; А1 + + А2 AJ + А2 А1 + А2 +

+ L. + А2 + А3; А1 + А2 + A3; А2 + А1 A3; AJ-A2 + A3; А2 + A3; А1-А2 + A3; А1-А2 + A3; А1-А2 + A3; А1-А2 + A3; А1 -А2 + A3; А1-АЗ + А2; AJ-A3 + А2; 25 А1-АЗ + А1-АЗ + A2j АГАЗ + А1 - A3 + А2; А1-АЗ + А2; А1-АЗ + А2; А1 + А2-АЗ; Aj + А2 АЗ; А1 + А2 АЗ ; А1 + А2.АЗ; АТ + А1 + А2-АЗ; А1 + А2-АЗ; А1 + А2-А1; А1- (А2 ч- A3); Al (А2 )j А1 (А2 ) ;А1 (А2 + + A3)j А1ЧА2 A1 + A3); А1 -(А2 + A3h А1- (А2 ) ; А2-(А1 + + A3); A2-(A1 + A3)j А2-(А1 ); A2(A1 + A3)j А2ЧА1 + + A3); A2-(A1 + АЗ А2-(А1 + A3); A3-(A1 ); A3 (A1 + АЗЧА1 + )j A3-(A1 ); A3(A1 )j A3j(A1 -t- A2); A3-(A1 + A2); A3-(A1 + + A2)

где Al, A2, A3 - переменные булевых функций, поступающие на входы вычислительного блока; А есть инверсия А. Принцип действия предлагаемого

30

Для считывания информации и ка оперативной памяти предусмо команда СЗ-1, а для записи инф ции в блок оперативной памяти смотрена команда С2-1, причем вимся, что по команде СЗ-1 выход блока оперативной памяти пает информация из ячейки, в к была записана переменная аА. а команде С2-1 1 в эту ячейк ти записывается инЛормация, по щая на вход блока оперативной ти с выхода вычислительного бл

Условимся, что на дешифрато 12 и 19 активизируются верхние

при наличии на входах сочетани гналов 1, О, средние выход при сочетании на входах сигнал О, 1 и нижние выходы при с тании на входах сигналов Г

35 на дешифраторе 39 активизирует верхний выход при сочетании си лов на входах О, О, О, в выход - при сочетании сигналов входах 1. О, О, третий в при сочетании сигналов на вход О, 1, О, четвертый выход сочетании сигналов на входах О, пятмй РЫХОД - при сочетан гналов на входах О, О, 1

40

35 на дешифраторе 39 активизируется верхний выход при сочетании сигналов на входах О, О, О, второ выход - при сочетании сигналов на входах 1. О, О, третий выход при сочетании сигналов на входах О, 1, О, четвертый выход - пр сочетании сигналов на входах 1, О, пятмй РЫХОД - при сочетании си гналов на входах О, О, 1, ше

устройства рассмотрим на примере рабо-15 той выход при сочетании сигналов

ты электропривода механизма в зависимости от результата вычисления функции (ai + 53) а5 (а1 + а2) + аЗа5.

Пудем считать, что переменные а1, а2, аЗ обозначают сигналы, поступающие на вход устройства от первичных датчиков, переменная а4 обозначает переменную, которая была вычислена ранее и записана в ячейку памяти блока Д1 оперативной памяти, а переменная а5, вычисленная ранее, записана в ячейку памяти Я блока коммутации 2.

Дня пояснения процесса вычисления предложенной в примере функции (а1 +

на входах 1, О, 1, седьмой вы ход - при сочетании сигналов на вхо де О, 1, 1 и восьмой выход при сочетании сигналов на входе 1 it in at и

I a I . .

Для записи информации в выходно блок 40 предусмотрена команда С4-1. На фиг. 1 показано только то количе во команд (С1...С16, С1-1, С1-2, СЗ-1, С4-1), которое необходимо для вычислений приведенной в качестве примера функции (а1 + аи) а5 (а1 + + А2) + аЗа5.

0

блока поступает переменная аЗ.

5

0

Для считывания информации из блока оперативной памяти предусмотрена команда СЗ-1, а для записи информации в блок оперативной памяти предусмотрена команда С2-1, причем условимся, что по команде СЗ-1 1 на выход блока оперативной памяти поступает информация из ячейки, в которой была записана переменная аА. а по команде С2-1 1 в эту ячейку памяти записывается инЛормация, поступа- щая на вход блока оперативной памяти с выхода вычислительного блока.

Условимся, что на дешифраторах 3, 12 и 19 активизируются верхние выходы

при наличии на входах сочетания сигналов 1, О, средние выходы - при сочетании на входах сигналов О, 1 и нижние выходы при сочетании на входах сигналов Г

1

на дешифраторе 39 активизируется верхний выход при сочетании сигналов на входах О, О, О, второй выход - при сочетании сигналов на входах 1. О, О, третий выход - при сочетании сигналов на входах О, 1, О, четвертый выход - при сочетании сигналов на входах 1, 1 О, пятмй РЫХОД - при сочетании сигналов на входах О, О, 1, шес

той выход при сочетании сигналов

на входах 1, О, 1, седьмой выход - при сочетании сигналов на входе О, 1, 1 и восьмой выход при сочетании сигналов на входе 1, it in at и

I a I . .

Для записи информации в выходной блок 40 предусмотрена команда С4-1. На фиг. 1 показано только то количество команд (С1...С16, С1-1, С1-2, СЗ-1, С4-1), которое необходимо для вычислений приведенной в качестве примера функции (а1 + аи) а5 (а1 + + А2) + аЗа5.

Па первом такте работы устройства на выходе программного блока 43, на командных шинах С5, Г.1-1, С7, Г,8, СЗ-1, С9, СЮ, С12, С13, С15, С16, С., СЗ появляются единичные команды соответственно, обеспечивающие подачу сигнала а5, записанного в ячейке памяти 0 блока коммутации 2, через элементы И 5 и ИЛИ 7 на верхний по схеме (фиг. 1) вход вычислительного блока 26, входного сигнала al из входного блока 1 через элементы И14, ИЛИ 16 блока коммутации 2 на вход вычислительного блока 26 (средний по схеме фиг. 1), сигнала а4 из блока 41 оперативной памяти на вход блока коммутации 2 и через элементы И 21 и ИЛИ 2 на (нижний по схеме фиг. 1) вход вы- числительного блока 26, где по командам С12 и С13 переменные al и а4 инвертируются и вместе с переменной а5 поступают на входы элементов ИЛИ 30, И 31, И-ИЛИ 32, И-ИЛИ 33, И-ИЛИ 34, ИЛИ-И 35, ИЛИ-И 36, ИПИ-И 37, на выходах которых появляются результаты вычисления функций соответственно а1 + а4 , ajja4 a5, a5-a1 51ja4, +-aj, (a5 + А1)-а4, (а1 + а4) а5, (а5 + а4)-а1.

По командам С15 и С16 результат вычисления функции (л1 + а4) а5 с выхода элемента ИЛИ-И 36 через элемент И-ИЛИ 38 поступит на выход вычислительного блока 26 и по информационным шинам на входы ячеек памяти 8 и 9.

I

За счет сигнала с выхода элемента

И 11, сформированного по команде С2 и поступившего на синхровход ячейки памяти 9, результат вычисления функции (а1 + а4)-а5 запишется в эту ячейку памяти.

Одновременно с вычислением функции

(а1 + а4) а5 переменная al, поступив- шая из входного блока 1 в блок коммутации 2, за счет сигнала с выхода элемента И 18, сформированного по команде СЗ, запишется в ячейку памяти 17

На втором такте на выходе програм- много блока 43, на командных шинах С5, Сб, С8, С1-2, С9, С13, С15, С16, С2-1 появятся единичные команды, соответственно обеспечивающие подачу результата вычисления функции (al + + а4)-а5 из ячейки памяти 9 через элементы И 6 и ИЛИ 7 на (верхний по схеме фиг. 1) вход вычислительного блока 26; сигнала а1, записанного на

o

5

0

5

5

0

5

Q

первом такте в ячейку памяти 17, через элементы И 15 и ИЛИ 16 на (средний по схеме фиг. 1). вход вычислительного блока 26, входного сигнала а2 из входного блока 1 через элементы И 20 и ИЛИ 25 на (жпкний по схеме фиг. 1) вход вычислительного блока 26, где по команде С13 переменная а2 инвертируется.

Но командам С15, С16 результат

вычисления функции .(а1 + a4)a5(at + а2) с выхода элемента ИЛИ-И 36 через элемент И-ИЛН 38 поступит на выход вычислительного блока и по информационной пине на вход блока 41 оперативной памяти .

По команде С2-1 результат вычисле- ния функции (al + а4)а5(а1 + а2) запишется в ячейку памяти блока оперативной памяти, причем в ту, в которую ранее была записана переменная а4, так как для дальнейших вычислений она больше не нужна.

Па третьем такте на выходе программного блока 43, на командных шинах СЗ-1, С9, СЮ, С1-1, С1-2, С7, С8, С5, С11, С15, С4-1 появятся единичные команды, обеспечивайте подачу результата вычисления функции (а1 + + а4)а5(а1 + а2) из блока оперативной памяти через элементы И 21 и ИЛИ 25 (на нижний по фиг. 1) вход вычислительного блока; входного сигнала аЗ из входного блока 1 через элементы И 14 и ИЛИ 16 на (средний по схеме фиг. 1) вход вычислительного блока; сигнала а5 из триггера памяти 8 чеоез элементы И5и ИЛИ 7 на (верхний по схеме фиг. 1) вход вычислительного блока 26, где по команде С11 инвертируется.

Полученный по команде С15 на выходе вычислительного блока 26 резуль- тат вычисления Функции (а +а4)а5(а1 + + а2) + аЗа5 по команде С4-1 и синхроимпульсу Запишется в элемент 50 памяти выходного блока 40 и далее через усилитель (не показан) поступит на электроприводной механизм (не по-, казан).

Как видно из приведенного примера, введение в блок коммутации 2 дополнительно третьей и четвертой ячеек памяти 17, 23 с соответствующими связями, а в вычислительный блок 26 элемента Исключающее ИЛИ 28, четырех элементов И-ИЛИ 32. 33. 34. За. трех элементов ИЛИ-И 35, 36, 37 и соответствующих связей позволяет вычислить пред0 t -т

ложенную функцию за три такта, так к появляется возможность одновременно на одном такте подавать значения трех переменных на входы вычислительного блока, например первую переменную из входного блока, вторую переменную из блока оперативной памяти, а третью из одного из триггеров памяти блока коммутации (в устройстве-прототипе на вычисление этой же функции требовалось бы семь тактов).

Уменьшение числа тактов позволяет повысить быстродействие устройства.

Введение в вычислительный блок 26 элемента Исключающее ИЛИ 28, элементов И-ШШ 32, 33, 34, 30 и элементов ИЛИ-И 35, 36, 37 позволяет на одном такте работы устройства вычислять любые булевые функции, состоящие из трех переменных, что позволяет сократить число тактов, т.е. повысить быстродействие, а также упростить устройство за счет сокращения командных шин в блоке программ 43.

Технико-экономический эффект устройства по сравнению с прототипом заключается в том, что повышение быстродействия устройства позволяв сократить время между моментом изменения состояния входных датчиков и реакцией на эти изменения электрспри водных механизмов в технологических линиях, что, в свою очередь, позволяет с большей точностью выдерживать заданные технологические режимы, например, в поточно-транспортных си-- стемах.

Формула изобретения

Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами, содержащее блоки согласования и выбора

50

механизма, блок оперативной памяти, 45 ма выходы которого являются выходами блок программ, генератор импульсов, блок коммутации, состоящий из трех дешифраторов, трех элементов ИЛИ, двух ячеек памяти и девяти элементов И, причем первые входы первого, второго, третьего элементов И соединены с соответствующими выходами первого дешифратора, выходы первого, второго, третьего элементов И подключены ко входам первого элемента ИЛИ, первые входы четвертого, пятого и шестого элементов И соединены с соответствукн сими выходами второго дешифратора, выходы четвертого, пя55

устройства, отличаю ще ее я тем, что, с пелью повышения быстродействия, в блок коммутации введены третья и четвертая ячейки памяти и четыре элемента И, причем входы разрешения записи с первой по четвертую ячеек памяти подключены к выходам с десятого по тринадцатый элементов И соответственно, информационные входы второй, третьей и четвертой ячеек памяти соединены с выходами вычислительного блока, блока согласования и блока оперативной памя;и соответственно, первые входы с десятого по трик

52964

того и шестого элементов И подключены к входам второго элемента ИЛИ, первые входы седьмого, восьмого и девятого элементов И соединены с соот-

5 ветствуккчими выходами третьего дешифратора, выходы седьмого, восьмого и девятого элементов И подключены к входам третьего элемента ИЛИ, вторые входы первого и восьмого элемен)0 тов И соединены соответственно с гтя- мыми выходами первой и второй ячеек памяти, вторые входы второго и девятого элементов И подключены к выходу блока оперативной памяти, второй вход

15 седьмого элемента И соединен с выходом блока согласования, вычисчитсль- ный блок, состоя ищи из двух элементов Исключающее ИЛИ, элемента И, элемента и дешифратора, первые входы элементов II и ИЛИ соединены с выходом первого элемента Исключающее ИЛИ, вторые входы элементов И и ИЛИ подключены к выходу второго элемента Исключающее ИЛИ, причем первые входы первого и второго элементов Исключающее ИЛИ соединены с выходами первого и третьего элементов ИЛИ блока коммутации соответственно, выход вычислительного блока подключен к

30 информационным входам блока оперативной памяти, блока выбора механизма и первой ячейки памяти, вход блока программ соединен с тактовым выходом генератора импульсов, первая группа

35 входов блока согласования является входами устройства, вторая группа входов блока согласования подключена к выходам опроса датчиков блока программ, входы записи и считывания бло40 ка оперативной памяти соединены с группой входов записи и группой выходов считывания бпока программ, выход эаписч блока программ подключен ко входу записи блока выбора механиз20

25

ма выходы которого являются выходами

устройства, отличаю ще ее я тем, что, с пелью повышения быстродействия, в блок коммутации введены третья и четвертая ячейки памяти и четыре элемента И, причем входы разрешения записи с первой по четвертую ячеек памяти подключены к выходам с десятого по тринадцатый элементов И соответственно, информационные входы второй, третьей и четвертой ячеек памяти соединены с выходами вычислительного блока, блока согласования и блока оперативной памя;и соответственно, первые входы с десятого по три13

надцатый элементов И соединены и подключены к сиихровходам блока оперативной памяти, блока выбора механизма и к синхропыходу генератора импульсов, вторые входы с десятого по тринадцатый элементов И и входы первого, второго и третьего дешифраторов соединены с первой группой командных выходов блока программ, в вычислительный блок введе- ны третий элемент Исключающее ИЛИ, четыре элемента И-ИЛИ, три элемента ИЛИ-И, причем первый вход третьего элемента Исключающее ИЛИ подключен к выходу второго элемента ИЛИ блока коммутации, первые входы первого, второго и третьего элементов И-ИЛИ и элементов ИЛИ-И соединены с выходом первого элемента Исключающее ИЛИ, их

вторые входи подключены к ныхо- У что рого элемента Исключающее li. IM, л их третьи входы соединены с тротькми и.п- дами элементов ИЛИ и И и подключены к выходу третьего элемента Исключающее ИЛИ, первая группа входов четвертого элемента И-ИЛИ соединена с выходами элементов ИЛИ, И, первого, второго, третьего элементов И-ИЛИ и элементов ИЛИ-И, вторая группа входов четвертого элемента И-ИЛИ соединена с выходами дешиоЪратора, выход четвертого элемента И-ИЛИ является выходом вычислительного блока, вторые входы элементов Исключающее ИЛИ и входы дешифратора подключены ко второй группе командных выходов блока программ.

c

Ul Ni ЧО

ON -PфигЬ

ГIn-F

5

55

Фиг. в

Фиг. 7

| Устройство для дистанционного программного управления электроприводными механизмами | 1982 |

|

SU1071999A1 |

| Г, 08 С 19/16, 19S2 | |||

| Устройство для дистанционного программного управления электроприводными механизмами | 1984 |

|

SU1257614A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-05-30—Публикация

1989-04-27—Подача