Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех.

Известен однофазный D-триггер (см. книгу: Букреев И.Н. и др. Микроэлектронные схемы цифровых устройств. Изд. 2-е, перераб. и доп. М. Сов.радио, 1975, с. 65, рис.2.11а), который содержит элемент И-ИЛИ, два инвертора, информационную, тактовую и выходную шины. Первый вход первого элемента И элемента И-ИЛИ соединен с тактовой шиной и через первый инвертор - с первым входом второго элемента И элемента И-ИЛИ. Второй вход первого элемента И элемента И-ИЛИ соединен с выходом второго инвертора вход которого соединен с информационной шиной. Выход элемента И-ИЛИ соединен со вторым входом своего второго элемента И и с выходной шиной.

Недостатками этого устройства являются низкая помехоустойчивость и инверсная запись информации.

Низкая помехоустойчивость устройства обусловлена:

1) возможностью непереключения устройства в новое состояние в случаях, когда помеха поступает по информационной шине перед окончанием тактового импульса и искажает поданный по этой шине логический уровень сигнала;

2) возможностью переключения устройства в предыдущее состояние в случаях, когда помеха поступает по тактовой шине после снятия с информационной шины установленного логического уровня;

3) возможностью потери устройством своего текущего состояния при поступлении помех по шинам питания;

4) возможностью прохождения напрямую на выход устройства помех, поступающих по информационной шине в течение длительности тактового импульса, ввиду наличия постоянного разрешения на первом входе первого элемента И элемента И-ИЛИ в течение длительности указанного импульса.

Инверсная запись информации в устройство в ряде случае требует дополнительного инвертирования сигнала на его выходе или на информационном входе.

Указанные недостатки устройства ограничивают его применение.

Известен однофазный D-триггер (см. книгу: Букарев И.Н. и др. Микроэлектронные схемы цифровых устройств. Изд. 2-е, перераб. и доп. М. Сов. радио, 1975, с.65, рис.2.12б), который выбран в качестве прототипа и содержит элемент И-ИЛИ и инвертор, выход которого соединен с первым входом первого элемента И элемента И-ИЛИ. Вход инвертора соединен с тактовой шиной и с первым входом второго элемента И элемента И-ИЛИ, второй вход которого соединен с информационной шиной. Выход элемента И-ИЛИ соединен со вторым входом своего первого элемента И и с выходной шиной.

Данное устройство свободно от второго недостатка предыдущего устройства, однако первый недостаток предыдущего устройства присущ и данному.

Таким образом, недостатком прототипа является низкая помехоустойчивость, обусловленная:

1) возможностью непереключения устройства в новое состояние при поступлении помехи по информационной шине перед окончанием тактового импульса и искажении поданного по этой шине логического уровня сигнала;

2) возможностью переключения устройства в предыдущее состояние при поступлении помехи по тактовой шине после снятия с информационной шины установленного логического уровня;

3) возможностью переключения устройства в предыдущее состояние при поступлении помех по шинам питания;

4) возможностью прямого прохождения на выход устройства помех, поступающих по информационной шине в течение длительности тактового импульса, ввиду наличия постоянного разрешения на первом входе второго элемента И элемента И-ИЛИ в течение длительности указанного импульса.

Достигаемым техническим результатом является повышение помехоустойчивости однофазного D-триггера.

Указанный технический результат достигается тем, что в однофазный D-триггер, содержащий основной элемент И-ИЛИ и инвертор, выход которого соединен с первым входом первого элемента И основного элемента И-ИЛИ, вход с тактовой шиной и с первым входом второго элемента И основного элемента И-ИЛИ, второй вход которого соединен с информационной шиной, второй вход первого элемента И основного элемента И-ИЛИ соединен с выходной шиной, введены дополнительный элемент И-ИЛИ и две интегрирующие RC-цепи, выход основного элемента И-ИЛИ через первую интегрирующую RC-цепь соединен с первым входом первого элемента И дополнительного элемента И-ИЛИ, второй вход которого соединен с выходом инвертора, выход дополнительного элемента И-ИЛИ соединен с выходной шиной и через вторую интегрирующую RC-цепь с первым входом своего второго элемента И, второй вход которого соединен с тактовой шиной.

Указанная совокупность признаков позволяет повысить помехоустойчивость однофазного D-триггера как к помехам, поступающим по информационной и тактовой шинам (за счет "анализа" длительности сигналов на указанных входных шинах), так и к внутренним помехам в шинах питания (за счет хранения текущих состояний триггера на конденсаторах интегрирующих RC-цепей).

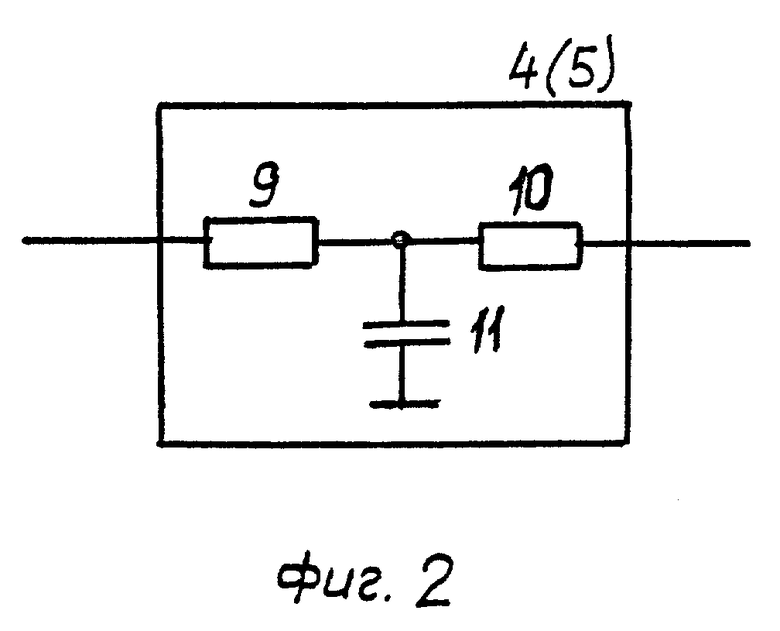

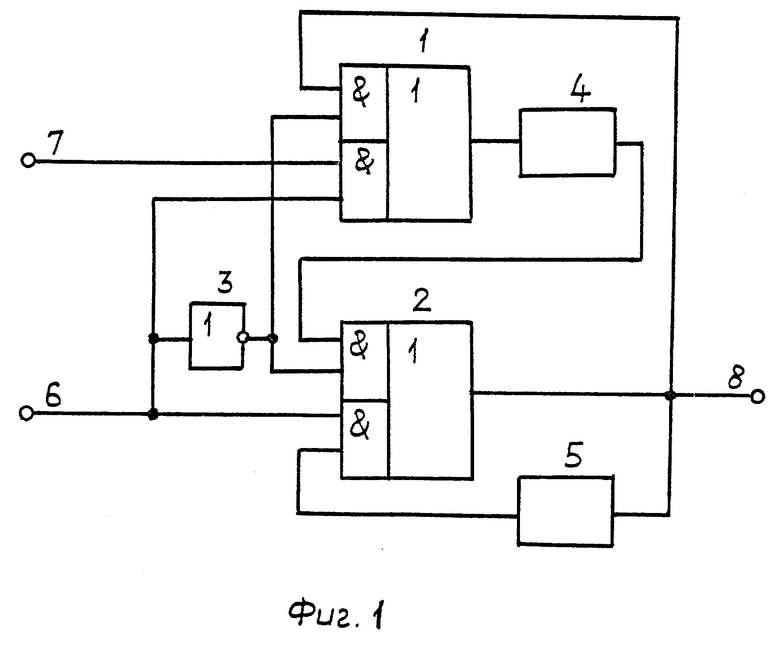

На фиг. 1 приведена схема однофазного D-триггера; на фиг.2 схема RC-элементов, входящих в состав устройства.

Устройство содержит основной элемент 1 И-ИЛИ, дополнительный элемент 2 И-ИЛИ, инвертор 3, первую 4 и вторую 5 интегрирующие RC-цепи. Первый вход первого элемента И элемента 1 И-ИЛИ соединен со вторым входом первого элемента И элемента 2 И-ИЛИ и выходом инвертора 3, вход которого соединен с тактовой 6 шиной и первым входом второго элемента И элемента 1 И-ИЛИ, второй вход которого соединен с информационной 7 шиной. Выход элемента 1 И-ИЛИ через RC-элемент 4 соединен с первым входом первого элемента И элемента 2 И-ИЛИ. Выход элемента 2 И-ИЛИ соединен со вторым входом первого элемента И элемента 1 И-ИЛИ, с выходной 8 шиной и через интегрирующую цепь 5 с первым выходом своего второго элемента И, второй вход которого соединен с тактовой 6 шиной.

Интегрирующие RC-цепи 4, 5 выполнены по одинаковой схеме, приведенной на фиг.2, на резисторах 9, 10 и конденсаторе 11. Выходной 10 резистор интегрирующих RC-цепей 4, 5 не является обязательным элементом последних, наличие этого резистора необходимо лишь в частных случаях реализации устройства для защиты соответствующих входов элементов 1, 2 И-ИЛИ по входному току (например, при отключении питания при заряженных конденсаторах RC-элементов в случае реализации устройства на базе интегральных микросхем, изготавливаемых по КМОП-технологии). Входной 9 резистор и конденсатор 11 указанных интегрирующих RC-цепей определяют уровень помехозащиты устройства.

Однофазный D-триггер (фиг.1) работает следующим образом.

В исходном состоянии на информационной 7 и тактовой 6 шинах устройства поддерживается уровень логического 0 (здесь и далее в тексте уровни сигналов соответствуют положительной логике), на выходе инвертора 3 уровень логической 1, на выходах элементов 1, 2 И-ИЛИ уровень логического 0, конденсаторы 11 RC-элементов разряжены. В таком исходном нулевом состоянии (логический 0 на выходной 8 шине) устройство само себя поддерживает по замкнутой цепи: выход интегрирующей RC-цепи 4 первый вход первого элемента И элемента 2 И-ИЛИ выход элемента 2 И-ИЛИ второй вход первого элемента И элемента 1 И-ИЛИ выход элемента 1 И-ИЛИ вход интегрирующей RC-цепи 4.

В указанное исходное состояние устройство при включении питания устанавливается самостоятельно, для чего достаточны разряженное состояние конденсаторов интегрирующих RC-цепей 4, 5 и наличие уровня логического 0 на информационной 7 или тактовой 6 шине.

Для переключения устройства в единичное состояние (для записи "1") по информационной 7 шине нужно подать уровень логической 1, затем по тактовой 6 шине тактовый импульс с уровнем логической 1. После подачи тактового импульса к обоим входам второго элемента И элемента 1 И-ИЛИ оказываются приложенными уровни логической 1. Это приводит к появлению уровня логической 1 на выходе элемента 1 И-ИЛИ, и начинается заряд конденсатора 11 интегрирующей цепи RC-цепи 4 через резистор 9 последнего. В течение тактового импульса на выходе инвертора 3 присутствует уровень логического 0, который запирает по соответствующим входам первые элементы И элементов 1, 2 И-ИЛИ. Одновременно в течение тактового импульса открыт по второму входу второй элемент И элемента 2 И-ИЛИ, что приводит к "прохождению" уровня логического 0 с выхода интегрирующей RC-цепи 5 (разряженное состояние его конденсатора 11) через второй элемент И элемента 2 И-ИЛИ на выход последнего.

Таким образом, в течение тактового импульса на выходе элемента 1 И-ИЛИ поддерживается уровень логической 1 (то есть уровень сигнала, присутствующего на информационной 7 шине), и конденсатор 11 интегрирующей RC-цепи 4 заряжается, а на выходе элемента 2 И-ИЛИ (и тем самым на выходной 8 шине) поддерживается уровень логического 0 (то есть уровень предыдущего исходного состояния устройства) по замкнутой цепи: выход интегрирующей RC-цепи 5 - первый вход второго элемента И элемента 2 И-ИЛИ выход элемента 2 И-ИЛИ - вход RC-элемента 5. Постоянная времени интегрирующей RC-цепи 4 выбирается таким образом, чтобы в течение длительности тактового импульса его конденсатор успел зарядиться до уровня логической 1 (или разрядиться до уровня логического 0).

После снятия тактового импульса на тактовой 6 шине восстанавливается исходный уровень логического 0, а на выходе инвертора 3 исходный уровень логической 1. Это приводит к запиранию по соответствующим входам вторых элементов И элементов 1, 2 И-ИЛИ и отпиранию по соответствующим входам первых элементов И элементов 1, 2 И-ИЛИ. В результате уровень логической 1 с заряженного конденсатора 11 интегрирующей RC-цепи 4 через первый элемент И элемента 2 И-ИЛИ проходит на выход последнего, на выходную 8 шину и, проходя через первый элемент И элемента 1 И-ИЛИ на выход последнего, поступает на вход интегрирующей RC-цепи 4 и поддерживает заряженное состояние его конденсатора 11. Одновременно начинает заряжаться конденсатор 11 интегрирующей RC-цепи 5. Постоянная интегрирующей RC-цепи 5 выбирается таким образом, чтобы между тактовыми импульсами его конденсатор успел зарядиться до уровня логической 1 (или разрядиться до уровня логического 0).

Таким образом, после окончания тактового импульса (по срезу последнего) устройство принимает единичное состояние, при котором на выходной 8 шине имеет место уровень логической 1, который поддерживается по упомянутой выше замкнутой цепи (в которой фигурирует интегрирующая RC-цепь 4) и которым заряжается конденсатор 11 интегрирующей RC-цепи 5.

Для переключения устройства, находящегося в единичном состоянии, в нулевое состояние (для записи "0") по информационной 7 шине нужно подать уровень логического 0, затем по тактовой 6 шине тактовый импульс. При этом устройство работает аналогично предыдущему случаю, когда в устройство "записывалось" логическая 1. Отличие в работе устройства в данном случае будет заключаться только в том, что в течение тактового импульса конденсатор 11 интегрирующей RC-цепи 4 разряжается до уровня логического 0, а на выходной 8 шине поддерживается уровень логической 1 (уровень предыдущего состояния устройства) по упомянутой выше замкнутой цепи, в которой фигурирует интегрирующая RC-цепь 5. А после окончания тактового импульса на выходной 8 шине появляется (и поддерживается аналогично предыдущему случаю) уровень логического 0, который приводит к разряду заряженного конденсатора 11 интегрирующей RC-цепи 5.

Устройство нормально функционирует, если длительности тактового импульса и сигнала на информационной 7 шине достаточны для заряда до уровня логической 1 (разряда до уровня логического 0) конденсатора 11 интегрирующей RC-цепи 4, а длительность интервала между тактовыми импульсами достаточна для заряда до уровня логической 1 (разряда до уровня логического 0) конденсатора 11 интегрирующей RC-цепи 5. Если же длительность тактового импульса или сигнала на информационной 7 шине недостаточна для заряда (разряда) конденсатора 11 интегрирующей RC-цепи 4, то есть, если по информационной 7 и(или) тактовой 6 шинам поступают помехи, то после окончания такого импульса (помехи) на тактовой 6 шине устройство сохраняет свое прежнее состояние.

Помехи, поступающие по информационной 7 шине в течение тактового импульса, могут пройти на выход элемента 1 И-ИЛИ, но на выход устройства пройти не смогут не только из-за наличия интегрирующей RC-цепи 4 на их пути, а в основном потому, что в течение этого импульса первый элемент И элемента 2 И-ИЛИ закрыт уровнем логического 0 с выхода инвертора 3.

Информация о состояниях устройства, выдаваемая на выходную 8 шину с выхода элемента 2 И-ИЛИ, имеет крутые фронт и срез. При некритичности подключаемых к выходу устройства нагрузок к длительности фронта и среза сигналов выходной сигнал устройства может сниматься с выхода интегрирующей RC-цепи 5.

В целях подтверждения осуществимости заявляемого объекта и достигнутого технического результата в институте был изготовлен и испытан в нормальных условиях и в диапазоне температур окружающей среды от минус 50oC до 50oC лабораторный макет на базе микросхем серии 564 и дискретных резисторов и конденсаторов. При этом элементы 1, 2 И-ИЛИ были реализованы на мультиплексоре 564ЛС2. Проведенные испытания показали осуществимость заявляемого помехоустойчивого однофазного D-триггера и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1995 |

|

RU2106744C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

| ГЕНЕРАТОР ИМПУЛЬСОВ | 1997 |

|

RU2129331C1 |

| СДВИГАЮЩИЙ РЕГИСТР | 1995 |

|

RU2105357C1 |

| ГЕНЕРАТОР ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ | 1997 |

|

RU2146075C1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1995 |

|

RU2105411C1 |

| МНОГОКАНАЛЬНЫЙ ДАТЧИК ОДИНОЧНЫХ ИМПУЛЬСОВ | 1996 |

|

RU2118042C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2178617C2 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2212095C1 |

Изобретение относится к импульсной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех. Достигаемый технический результат - повышение помехоустойчивости. Однофазный D-триггер содержит элементы И-ИЛИ 1, 2, инвертор 3, интегрирующие RC-цепи 4, 5, тактовую шину 6, информационную шину 7, выходную шину 8. 2 ил.

Однофазный D-триггер, содержащий основной элемент И-ИЛИ и инвертор, выход которого соединен с первым входом первого элемента И основного элемента И-ИЛИ, вход с тактовой шиной и с первым входом второго элемента И основного элемента И-ИЛИ, второй вход которого соединен с информационной шиной, второй вход первого элемента И основного элемента И-ИЛИ соединен с выходной шиной, отличающийся тем, что в него введены дополнительный элемент И-ИЛИ и две интегрирующие RС-цепи, выход основного элемента И-ИЛИ через первую интегрирующую RС-цепь соединен с первым входом первого элемента И дополнительного элемента И-ИЛИ, второй вход которого соединен с выходом инвертора, выход дополнительного элемента И-ИЛИ соединен с выходной шиной и через вторую интегрирующую RС-цепь с первым входом своего второго элемента И, второй вход которого соединен с тактовой шиной.

| Букреев И | |||

| Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств, Изд | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и доп | |||

| - М.: Сов.радио, 1975, с | |||

| Разборное приспособление для накатки на рельсы сошедших с них колес подвижного состава | 1920 |

|

SU65A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1997-11-10—Публикация

1994-06-07—Подача