Изобретение относится к программируемым и управляющим вычислительным устройствам и может применяться самостоятельно в системах управления различными технологическими линиями, вычислительных комплексах в качестве устройств пересылки однобитовой информации и вычисления булевых функций, освобождая от этих функций многоразрядные микропроцессоры, которые выполняют эти функции неэффективно.

Известно устройство, содержащее входной блок, подключенный через общую информационную шину к выходу блока оперативной памяти и к входу вычислительного блока, выход которого через триггер памяти связан с выходным блоком, блоком оперативной памяти и управляемым инвертором, выход которого соединен с управляющим блоком, на входы которого поступают дополнительные командные шины из программного блока, передающие номер внеочередного такта (SU, авторское свидетельство N 1226508, кл. G 08 C 19/16, 1984).

Недостатком данного устройства является то, что для передачи внеочередного такта используются дополнительные командные шины, идущие из программного блока в управляющий блок, что увеличивает число проводов связи, а значит, понижает надежность работы устройства и делает его громоздким.

Наиболее близким по технической сущности, надежной и эффективной организации процесса управления работой всего устройства является устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, коммутационно-вычислительный блок, генератор импульсов и программный блок, причем генератор импульсов связан с блоком синхронизации, который своими выходами соединен с входами коммутационно-вычислительного блока, блока оперативной памяти, выходного и программного блоков, выходы последнего связаны командными и адресными шинами со всеми блоками, кроме блока синхронизации, а выход входного блока связан с входом коммутационно-вычислительного блока, выходы которого соединены соответственно с блоком оперативной памяти и выходным блоком (RU, патент N 1801223, кл. G 05 B 19/08, 1993).

К недостаткам этого устройства можно отнести обязательность вычисления всей булевой функции, например конъюнкции, даже тогда, когда определено, что первый член в конъюнкции равен "0" и, значит, вся конъюнкция равна "0". Вычисляется и вся дизъюнкция, когда уже установлено, что, например, первая переменная дизъюнкции равна "1", а значит, и вся дизъюнкция равна "1".

Технический результат изобретения направлен на ускорение процесса вычисления булевых функций при использовании уже имеющихся в прототипе командных и адресных шин в качестве носителей информации о внеочередном номере такта. Этот результат достигается тем, что в известное устройство для дистанционного программного управления электроприводными механизмами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, программный блок и генератор импульсов, причем коммутационно-вычислительный блок связан входами с выходами входного блока, блок оперативной памяти и блока синхронизации, двумя управляющими выходами соединен с входами блоков оперативной памяти и выходного, а информационным выходом связан с соответствующими входами последних блоков, оставшиеся два входа которых и вход программного блока подключены к выходам блока синхронизации, вход которого соединен с выходом генератора импульсов, дополнительно введен блок ускорения, состоящий из элементов ИЛИ и НЕ, двух= и четырехвходовых элементов И, контрольного триггера, ячеек памяти, первого и второго электронных ключей, при этом входы элемента ИЛИ соединены с управляющими выходами коммутационно-вычислительного блока, выход элемента ИЛИ связан с входами элемента НЕ и двухвходового элемента И, второй вход которого подключен к второму выходу блока синхронизации, а выход соединен с входом установки нуля контрольного триггера, установочный в "1" вход которого связан с дополнительной шиной программного блока, а выход контрольного триггера и вход элемента НЕ подключены к двум входам четырехвходового элемента И, остальные входы которого соединены с первым выходом блока синхронизации и с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ коммутационно-вычислительного блока, а выход - с управляющим входом первого электронного ключа, выходы которого связаны с установочными входами счетчика импульсов программного блока, а входы подключены к выходам ячеек памяти, входы которых подключены вместе с входами второго электронного ключа к командным, адресным и дополнительной шинам блока программ, а выходы второго электронного ключа связаны с командными входами коммутационно-вычислительного блока.

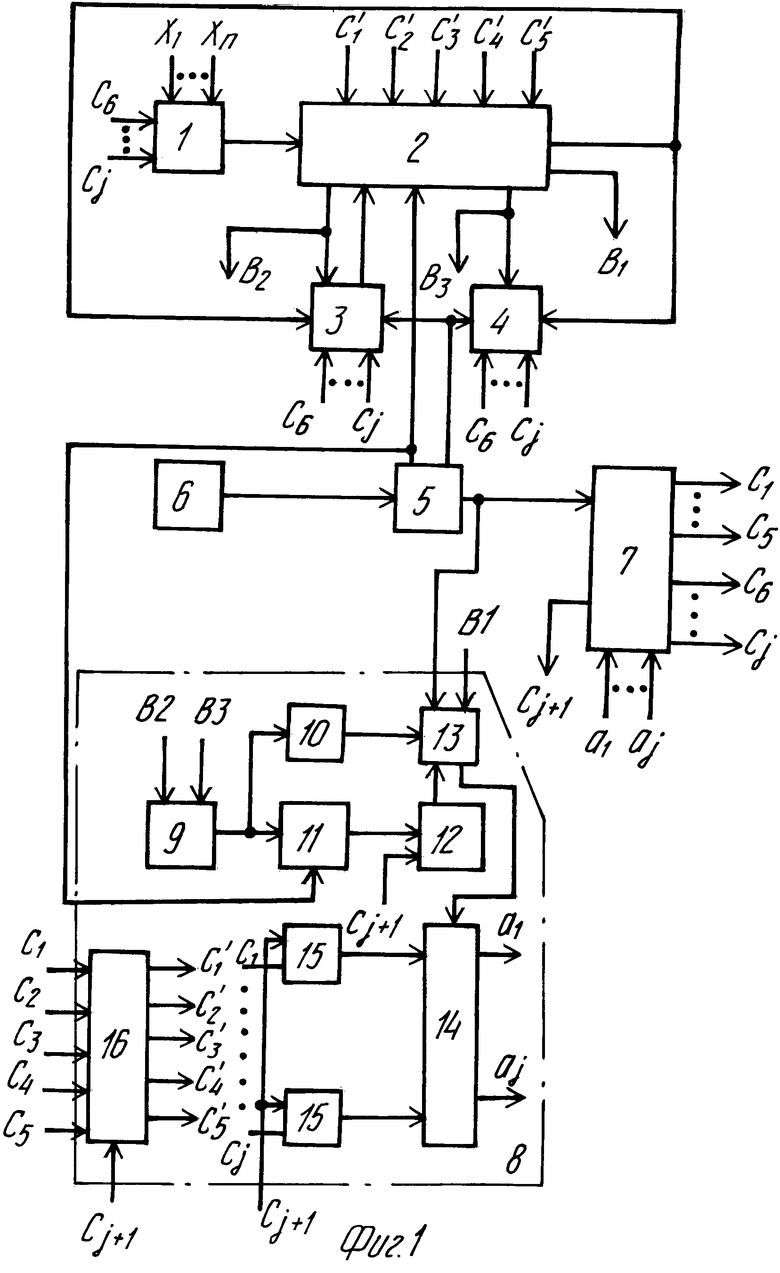

Предлагаемое устройство поясняется схемой, изображенной на фиг.1.

Устройство состоит из входного блока 1, соединенного с входом коммутационно-вычислительного блока 2, связанного с блоком 3 оперативной памяти, с выходным блоком 4 и через блок 5 синхронизации - с генератором 6 импульсов, программным блоком 7 и блоком 8 ускорения, содержащим элемент ИЛИ 9, соединенный через элемент НЕ 10 и двухвходовой элемент И 11 с контрольным триггером 12 и с четырехвходовым элементом И 13, выход которого подключен к входу управления первого электронного ключа 14, связанного оставшимися входами с выходами ячеек 15 памяти, управляющий вход которого связан с управляющим входом второго электронного ключа 16.

Работа электронного ключа 14 блока 8 состоит в том, что при наличии логической "1" на выходе элемента И 14 ключ 14 пропускает логические сигналы с выходов ячеек памяти 15 на входы A1 ... Aj блока 7 программ, а при наличии логического "0" - не пропускает и на выходах A1 ... Aj имеются логические "0". Работа ключа 16 состоит в том, что при наличии логического "0" на шине C блока 7 значения командных сигналов C1 ... C5 поступают на входы блока 2. При Cj+1 = 1 значения C'1 ... C'5 всегда равны "0". Стрелками, направленными к элементам и блокам, помечены входы всех элементов блоков.

C'1. ..C'5 - командные сигналы, равные сигналам C1 ... C5 при C = 0, управляющие работой блока 2;

C6...Cj - адресные сигналы, определяющие номер ячеек памяти в блоках 3 и 4, или номер входа в блоке 1. Они также определяют номер внеочередного такта при C = 1.

X1 . .. Xn - значения входных сигналов, поступающих от объекта управления;

a1 ... aj - сигналы, устанавливающие счетные триггера блока 7 в состояние, соответствующее внеочередному номеру следующего такта;

b1 - значение выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ в блоке 2;

b2 и b3 - сигналы, поступающие из блока 2 в блок 8.

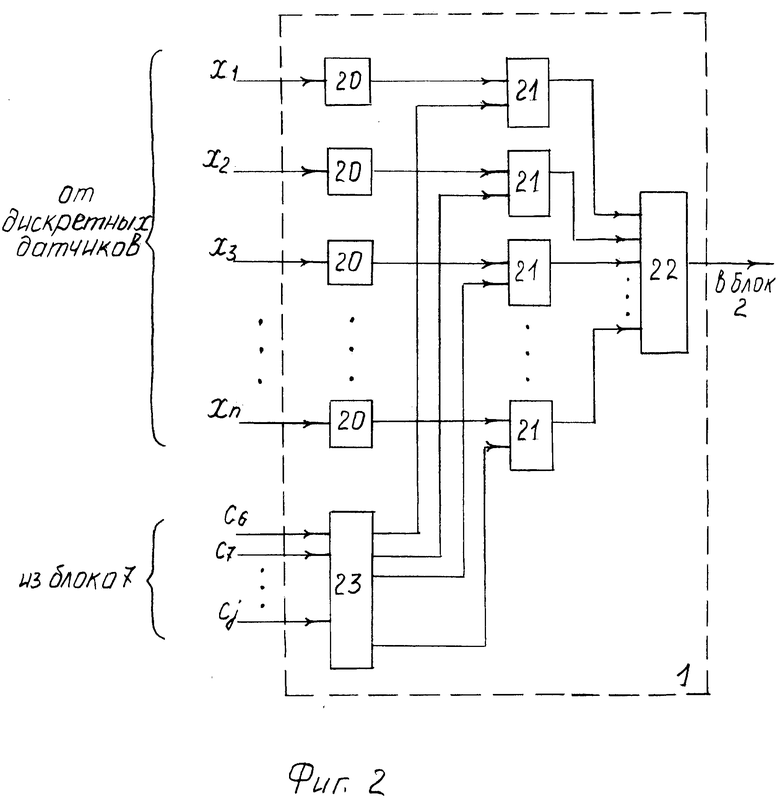

Входной блок известной конструкции представлен на фиг.2, Он состоит из элементов 20 согласования, через которые входные сигналы X в нужной форме поступают на элементы 21 считывания типа элементов И, выходы которых связаны с элементом ИЛИ 22, дешифратор 23 управляет элементами 21 по сигналам C6 ... Cj.

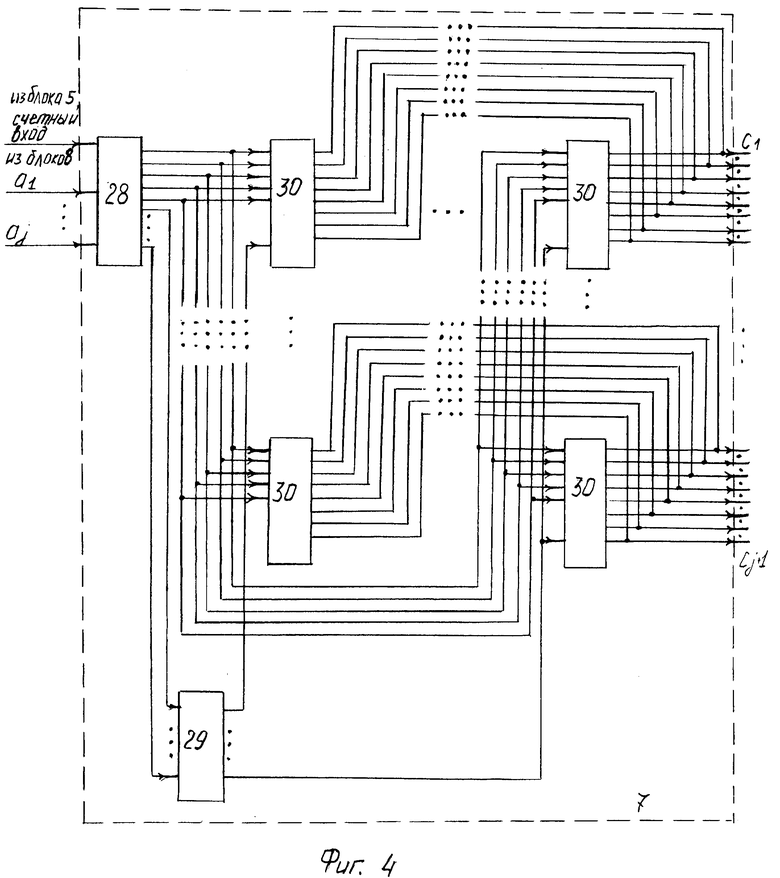

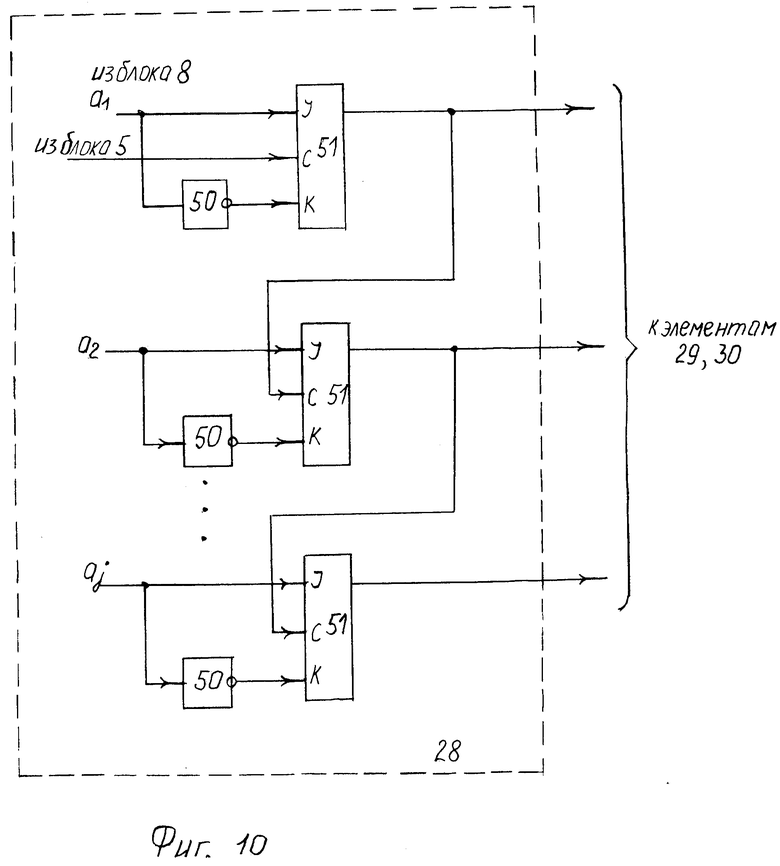

Программный блок 7 (фиг.4) известной конструкции состоит из счетчика 28 импульсов, на счетный вход которого поступают импульсы из блока 5 синхронизации, а на установочные входы подаются сигналы a1 ... aj из блока 8, которые при Cj+1 = 1 переводят счетчик 28 во внеочередное состояние. При Cj+1 = 0 счетчик 28 работает в обычном режиме дешифратора 29, распределяющего импульсы по элементам 30 постоянной памяти (например, серии ПЗУ 155РЕ3), на которые записывается программа работы всего устройства. Перед началом работы счетчик импульсов устанавливается в нулевое состояние. Подробная схема счетчика 28 представлена на фиг.10, где индексом 50 обозначен элемент НЕ, а индексом 51-счетные триггеры с установочными входами J и K.

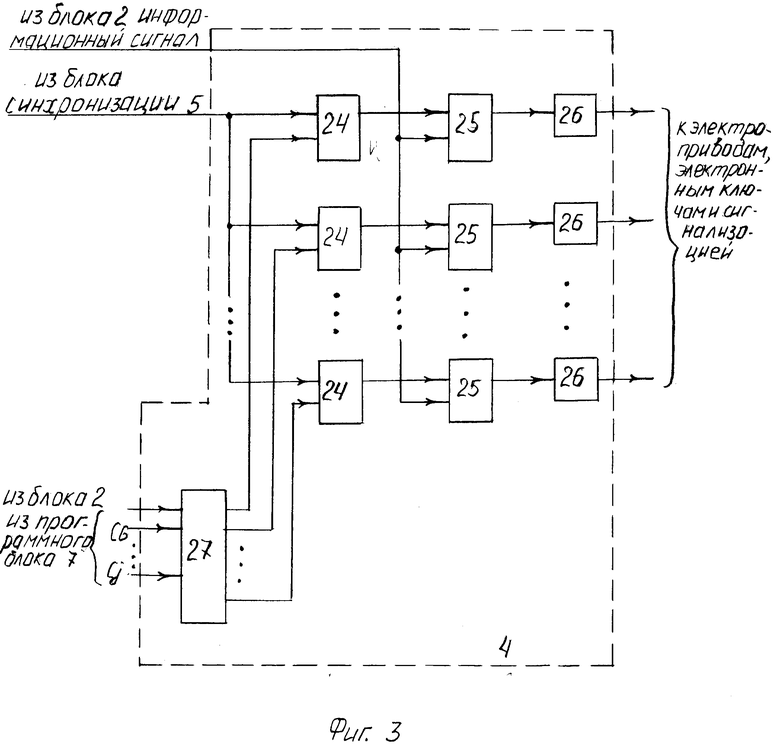

Выходной блок 4 (фиг.3) состоит из элементов И 24, ячеек 25 памяти, куда заносится информация из блока 2 и соответствующих усилителей 26, передающих логические сигналы из ячеек памяти на электроприводы, по адресным сигналам C6 ... Cj и командам из блока 2, поступающим на дешифратор 27.

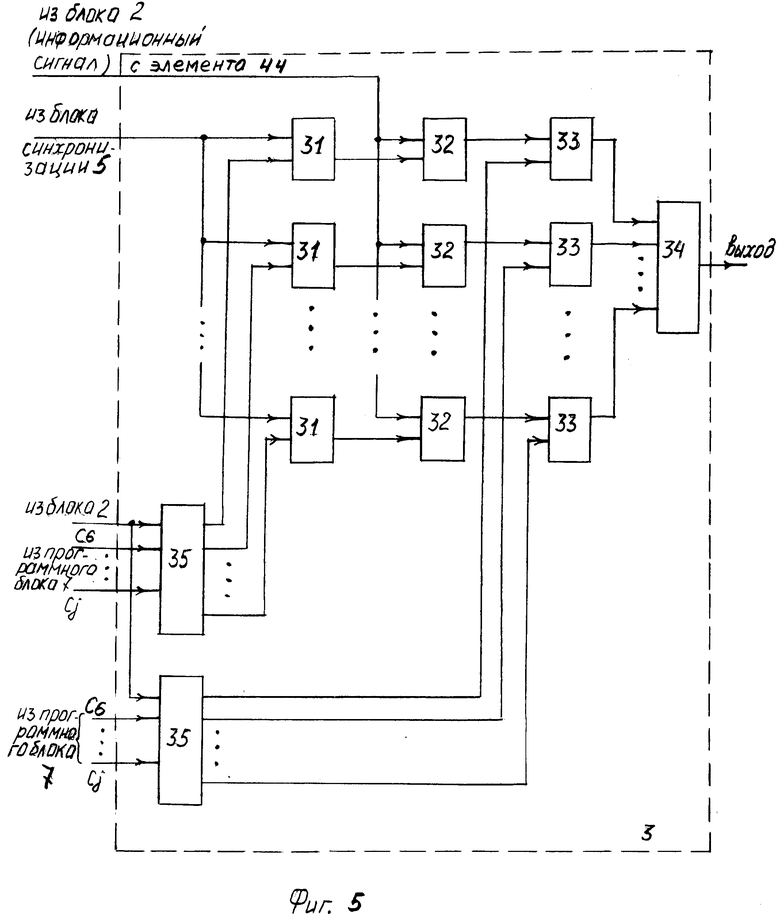

Блок 3 оперативной памяти, который представлен на фиг.5, содержит элементы И 31 обращения к ячейкам памяти, в качестве последних можно использовать стандартные ОЗУ, или, как в нашем примере, отдельные элементы 32 памяти, элементы 33 считывания (элементы И), элементы ИЛИ 34, первый и второй дешифраторы 35, через соответствующий элемент заносит или считывает информацию соответствующую ячейку памяти по командам из блока 2 и адресному коду C6 ... Cj.

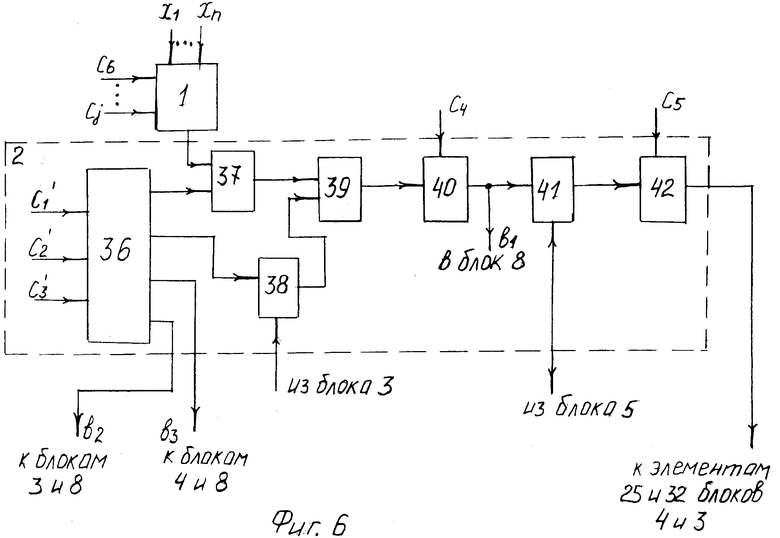

Блок 2 известной структуры (фиг.6) состоит из трехвходового дешифратора 36, своими входами связанного с выходами C1, C2, C3 блока 8, а первым /верхним/ и вторым выходами соединенного с первыми входами элементов И 37 и 38, вторые входы последних подключены к входному блоку и блокам оперативной памяти 1 и 3, а выходы - к входам элемента ИЛИ 39, выход которого связан с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 40, второй вход последнего соединен с выходом C4 блока 8, а выход соединен через элемент И 41 с управляющим входом ячейки 42 памяти, информационный вход которой соединен с выходом C5 блока 8 ускорения, а выход - с информационными входами блока 3 и блока 4. Третий и четвертый выходы дешифратора 36 связаны с управляющими входами блоков 3, 4 и 8.

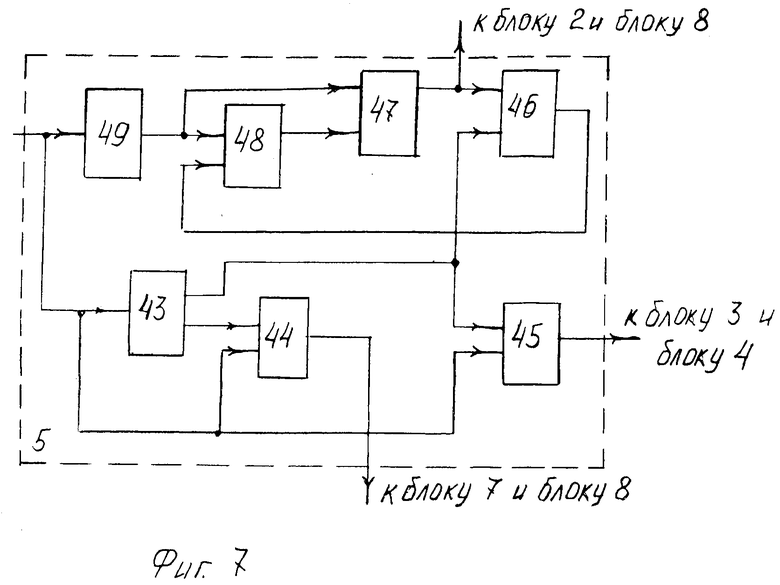

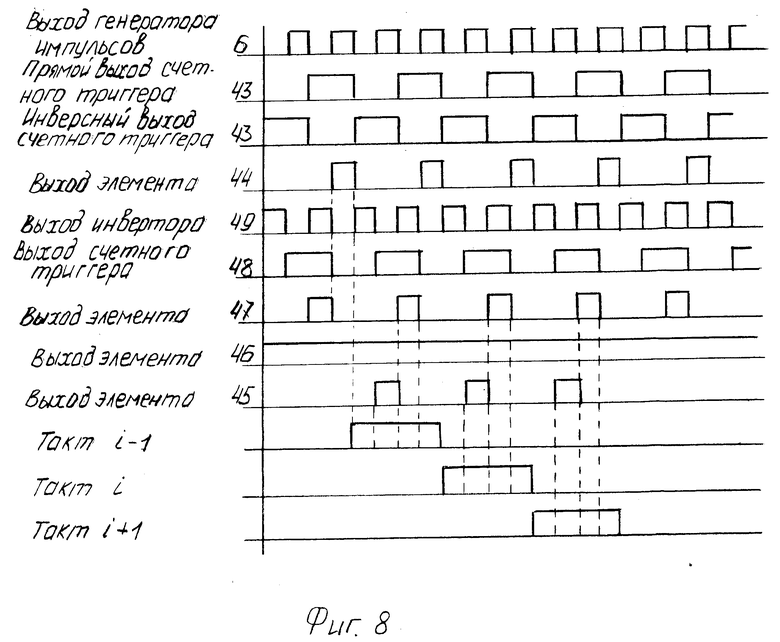

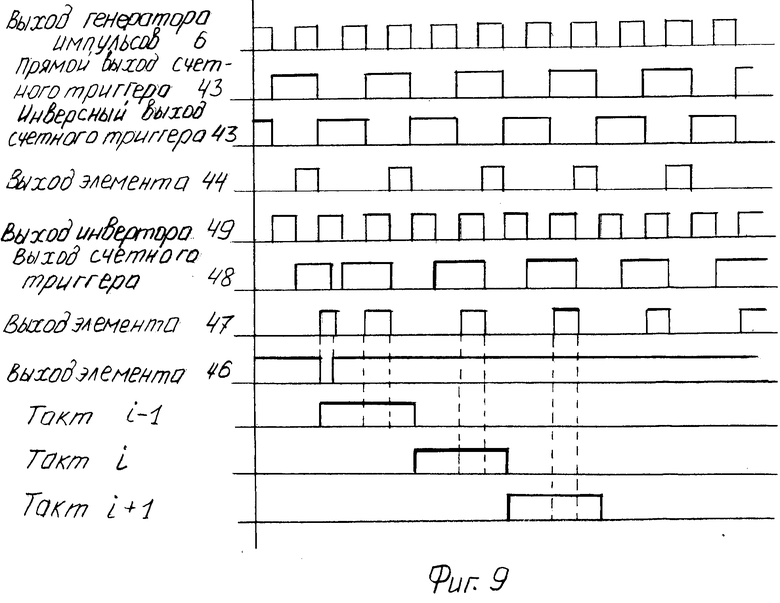

Блок 5 синхронизации известной конструкции (фиг. 7) содержит первый счетный триггер 43, подключенный прямым выходом к элементу И 44, а инверсным выходом - к первым входам элементов И 45 и И 46, второй вход последнего подключен к выходу элемента И 47, входы которого связаны с прямым выходом второго счетного триггера 48 и с выходом инвертора 49, вход которого вместе с входом триггера 43 являются входами блока 5 и соединены с генератором 6 импульсов. При этом выход элемента И 44 блока 5 подключен к счетному входу счетчика 28 блока 7 и входу элемента И 13 блока 8, выход элемента И 47 блока 5 связан с входом элемента И 41 блока 2 и с входом элемента И 11 блока 8, а выход элемента И 45 блока 5 связан с входами дешифраторов 35 и 27 соответственно блоков 3 и 4. Работа блока 5 поясняется диаграммами на фиг. 8 и фиг. 9.

Работу предлагаемого устройства опишем на примере вычисления логической функции X1 • X2 • X3 (X4 + X5 • X6 + X7) = Ф, содержащей функционально полный набор логических функций. На первом такте по команде Cj+1 = 1 в ячейки 15 памяти блока 8 записывается номер такта, записывающий результат вычисления функции Ф в блок 3 и одновременно триггер 12 блока 8 переводится в единичное состояние. На втором такте при C'4 = 1; C'5 = 1 и при нулевых значениях C'1, C'2 и C'3 в ячейку 42 памяти блока 2 записывается "1". На третьем такте переменная X1 под действием команд C'1, C'2 и C'3, а также адресных сигналов C6 ... Cj поступает из блока 1 через элементы 37, 39, 40 и 41 на вход управления ячейки 42 памяти. Учитывая, что на третьем такте C'4=1 и C'5=0 можно утверждать, что, если X1 = 1, то в ячейке 42 памяти сохранится "1" и процесс вычисления функции Ф будет продолжаться, а если X1=0, то очевидно, что функция Ф равна "0" и дальше ее вычислять нет смысла. Поэтому под действием команды b1, поступающей с выхода элемента 40 блока 2, единичного сигнала на выходе триггера 12 блока 8 и очередного счетного импульса на выходе блока 5 на выходе элемента 13 блока 8 появляется "1" и значение номера такта, ранее записанного в ячейки 15 блока 8, через ключ 14 поступает на установочные входы счетчика 28 блока 7 и на его выходах C1 ... Cj устанавливаются сигналы, обеспечивающие запись результата вычисления функции Ф в нужную ячейку памяти блока 3. Таким образом для вычисления функции Ф потребовалось всего три такта вместо тринадцати, как это требовалось бы в прототипе.

Допустим, что результат вычисления конъюнкции X1, X2, X3 равен "1", тогда этот результат запишется в блок 3 по адресу C6 ... Cj и одновременно при C'4 = 1 и C'5 = 0 логический "0" запишется в ячейку памяти 42 блока 2, а триггер 12 блока 8 возвращается в нулевое состояние. На седьмом такте под действием команды Cj+1 = 1 в ячейке памяти 15 блока 8 запишется номер такта, который определяется значениями C1 ... Cj, поступающими из блока 7 и определяющими работу всего устройства после вычисления всей функции Ф, и одновременно триггер 13 блока 2 примет единичное значение. На восьмом такте при Cj+1 = 0 и C'5 = 1 под действием команд C'1, C'2 и C'3 активизируется первый выход дешифратора 36 блока 2 и переменная X4, адрес которой в блоке 1 определяется значениями C6 ... Cj, через элементы 37 и 39 блока 2 поступает на вход элемента 40, на второй вход которого поступает команда C'4 = 1 и, если переменная X4 = 0, функцию Ф нет смысла вычислять дальше, т.к. она равна "1" и на выходе элемента 40 блока 2 появится единичный сигнал, который обеспечит вместе с сигналом на выходе блока 5 наличие "1", на выходе элемента 13, и на установочные входы счетчика тактов блока 7 с выхода элементов 14 блока 8 поступит номер такта, записанный ранее в ячейки 15 блока 8, который определяет работу всего устройства после вычисления функции Ф. Таким образом функция Ф была вычислена за 8 тактов вместо тринадцати. Если же значение функции Ф еще не определено (X4 = 1), то вычисление функции Ф продолжается.

Из вышеизложенного можно сделать два вывода:

- применение блока 8 ускорения новой конструкции и с новыми связями позволяет ускорить процесс вычисления булевых функций за счет анализа только активных входных сигналов X, т.е. от которых зависит значение конъюнкции или дизъюнкции в булевых функциях;

- применение блока 8 позволяет использовать командные и адресные шины C1 . . . Cj в качестве шин, передающих номера внеочередных тактов, которые предварительно, как это было показано выше, записывались в ячейки 15 памяти блока 8 из блока 7 памяти.

При этом команды C'1 ... C'5 блокируются сигналом Cj+1 = 1 и никаких операций в блоке 2 не производится, что, в отличие от аналога, позволяет существенно сократить число линий связи вустройстве.

Технико-экономический эффект от применения предложенного устройства заключается в возможности повысить быстродействие обработки дискретной информации, что повышает точность управления за счет уменьшения времени между изменением сигналов датчиков (X) на объекте управления и выдачей управляющих сигналов на электропривод объекта управления. Также сокращается число линий связи в устройстве, а значит, его надежность и помехоустойчивость повышаются.

Изобретение относится к устройствам для программного логического управления электроприводами, электронными ключами и сигнализацией. Технический результат предложения направлен на ускорение процесса вычисления булевых функций. Этот результат достигается тем, что устройство, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, прогаммный блок и генератор импульсов, снабжено блоком ускорения, содержащим элементы ИЛИ и НЕ, двух- и четырехвходовые элементы И, контрольный триггер, управляемые ячейки памяти, первый и второй электронные ключи с соответствующими связями между собой и вышеперечисленными блоками, что позволяет ускорить процесс вычисления булевых функций по сравнению с прототипом путем учета только тех переменных, входящих в вышеуказанную функцию, которые в данный момент времени активны, а также сократить число линий связи между программным блоком и блоком ускорения по сравнению с аналогичными устройствами. 10 ил.

Устройство для программного логического управления электроприводами, электронными ключами и сигнализацией, содержащее входной и выходной блоки, блок оперативной памяти, блок синхронизации, коммутационно-вычислительный блок, программный блок и генератор импульсов, коммутационно-вычислительный блок связан соответствующими входами с выходами соответственно входного блока, блока оперативной памяти и блока синхронизации, а соответствующими выходами - с соответствующими входами блока оперативной памяти и выходного блока, другие входы последних блоков подключены к программному блоку и блоку синхронизации, связанному с генератором импульсов и программным блоком, отличающееся тем, что в него введен блок ускорения, содержащий элементы ИЛИ и НЕ, двухвходовой и четырехвходовой элементы И, контрольный триггер, управляемые ячейки памяти, первый и второй электронные ключи, причем входы элемента ИЛИ соединены с управляющими работой блока оперативной памяти и выходного блока выходами коммутационно-вычислительного блока, выход элемента ИЛИ связан с входами элементов НЕ и двухвходового элемента И, второй вход последнего связан с соответствующим входом коммутационно-вычислительного блока и подключен к соответствующему выходу блока синхронизации, а выход двухвходового элемента И соединен с входом установки в "0" контрольного триггера, установочый в "1" вход которого связан с дополнительной шиной программного блока, а выход контрольного триггера соединен с первым входом четырехвходного элемента И, второй вход которого подключен к выходу элемента НЕ, третий и четвертый входы четырехвходого элемента И связаны с одним из выходов блока синхронизации и с единичным выходом коммутационно-вычислительного блока, выход четырехвходового элемента И связан с управляющим входом первого электронного ключа, выходы последнего соединены с установочными входами программного блока, а другие входы первого электронного ключа подключены к выходам управляемых ячеек памяти блока ускорения, входы последних вместе с входами второго электронного ключа связаны с выходами программного блока, выходы второго электронного ключа соединены с управляющими входами коммутационно-вычислительного блока.

| SU, авторское свидетельство N 1226508, кл | |||

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| RU, патент N 1801223, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ЕР, заявка, N 573827, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| GB, патент N 1379184, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| DE, заявка N 2846686, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1998-03-10—Публикация

1996-03-22—Подача