Изобретение относится к программируемым и управляющим вычислительным устройствам и может применяться самостоятельно в системах управления различными технологическими линиями, вычислительных комплексах в качестве устройств пересылки однобитовой информации и вычисления булевых функций, освобождая от этих операций многоразрядные микропроцессоры, выполняющие вычисления булевых функций сложными и длительными процедурами.

Известно устройство, содержащее входной блок, подключенный через общую информационную шину к выходу блока оперативной памяти и к входу вычислительного блока, выход которого, через триггер памяти связан с выходным блоком, блоком оперативной памяти и управляемым инвертором, выход которого соединен с управляющим блоком, на входы которого поступают дополнительные командные шины из программного блока передающие номер внеочередного такта /авт. св. СССР N 1071999, G 05 B 19/08/.

Недостатком данного устройства является то, что оно обладает относительно низким быстродействием и для передачи внеочередного такта в нем используются дополнительные командные шины, идущие из программного блока в управляющий блок, что увеличивает число проводов связи, а значит понижает надежность работы устройства и делает его громозким.

Наиболее близким по технической сущности, надежной и эффективной организации процесса управления работой всего устройства является устройство, содержащее входной и выходной блоки, блоки оперативной памяти и синхронизации, коммутационно-вычислительный блок, генератор импульсов и программный блок, причем генератор импульсов связан с блоком синхронизации, который своими выходами соединен с входами коммутационно-вычислительного блока, блока оперативной памяти, выходного и программного блоков /авт. св. СССР N 1801223, G 05 B 19/08, 1993/.

Недостатком данного устройства является относительно низкое быстродействие из-за того, что необходимо "перебрать" все переменные, входящие в состав вычисляемых булевых функций независимо от их влияния на результат вычисления булевых функций в настоящий момент времени.

Целью изобретения является повышение быстродействия устройства при вычислении булевых функций, за счет учета только активных переменных в данный момент времени.

Поставленная цель достигается тем, что в известное устройство для дистанционного программного логического управления электроприводами, электронными ключами и сигнализацией, содержащее коммутационно-вычислительный блок, связанный входами с входным блоком, блоком синхронизации и через командные шины с программным блоком, а выходами с блоком оперативной памяти и выходным блоком, генератор импульсов, причем коммутационно-вычислительный блок состоит из дешифратора, входы которого связаны с тремя командными шинами, а выходы соединены с блоком оперативной памяти, выходным блоком и внутри блока, через элементы первого и второго И, элементы ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, третьего элемента И с управляющим входом ячейки памяти, а вторые входы первого и второго элементов И подключены к входному блоку и блоку оперативной памяти, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и информационный вход ячейки памяти связаны с четвертой и пятой управляющими шинами, введен блок ускорения, содержащий первый и второй ряды управляемых ячеек памяти, три электронных ключа, четыре элемента И, дешифратор, инвертор, ряд двухвходовых элементов ИЛИ, пять элементов ИЛИ, причем информационные входы двух рядов ячеек памяти соединены со всеми, кроме двух первых и двух последних, выходами программного блока, а управляемые входы двух рядов ячеек памяти связаны с первым и вторым выходами дешифратора, входы которого подключены к двум последним выходам программного блока, выходы первого и второго рядов ячеек памяти соединены соответственно с информационными входами первого и второго рядов электронных ключей, выходы которых связаны, через ряд двухвходовых элементов ИЛИ с установочными входами счетных триггеров программного блока, управляемый вход первого электронного ключа соединен с выходом первого элемента И, первый вход которого подключен к третьему выходу дешифратора, а второй - к выходу блока синхронизации и входу программного блока, а третий вход к выходу второго элемента И и через инвертор к первому входу третьего элемента И, второй, третий и четвертый входы которого связаны соответственно с выходом блока синхронизации, четвертым выходом дешифратора и выходом первого элемента ИЛИ, а выход подключен к первому входу второго элемента ИЛИ, выход которого связан с управляющим входом второго электронного ключа, а второй вход соединен с выходом четвертого элемента И, первый, второй, третий и четвертый входы которого связаны соответственно с вторым и третьим входами третьего элемента И, с выходом третьего элемента ИЛИ и с выходом второго элемента И, первый вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ коммутационно-вычислительного блока, а второй вход связан с выходом четвертого элемента ИЛИ, входы которого соединены через третий электронный ключ с тремя выходами программного блока, информационные входы третьего электронного ключа связаны с тремя выходами программного блока, а выходы с управляющими входами коммутационно-вычислительного блока, управляющий вход третьего электронного ключа соединен через пятый элемент ИЛИ с первым и вторым выходами дешифратора, входы первого и третьего элементов ИЛИ связаны с дополнительными выходами дешифратора коммутационно-вычислительного блока, в последний блок введены два элемента ИЛИ и дешифратор дополнен двумя выходами и связями по входу с соответствующими выходами блока ускорения, причем входы введенных элементов ИЛИ подключены к четырем выходам дешифратора, а выходы соединены с вторыми входами двух элементов И.

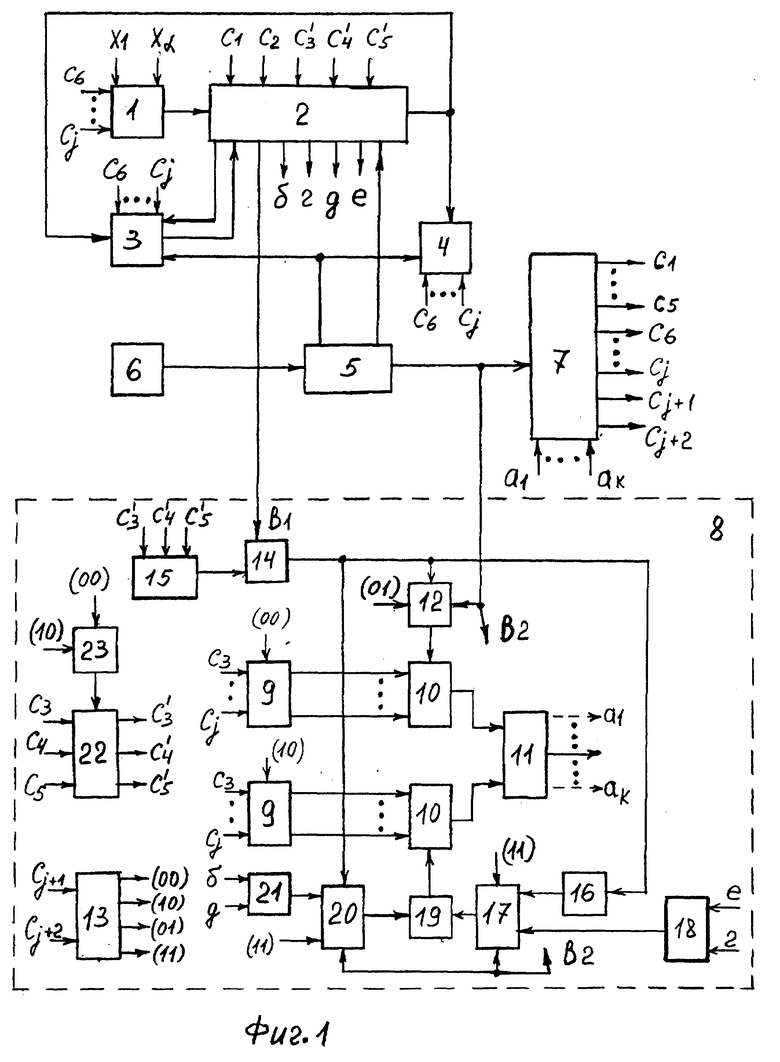

Предлагаемое устройство поясняется функциональной схемой на фиг.1.

Устройство состоит из входного блока /далее БН/ 1, соединенного с входом коммутационно-вычислительного блока /далее БКВ/ 2, связанного с блоком оперативной памяти /далее БОП/ 3, с выходным блоком /далее БВ/ 4 и через блок синхронизации /далее БС/ 5 с генератором импульсов /далее ГИ/ 6, программным блоком /далее БП/ 7 и блоком ускорения /далее БУ/ 8, содержащим первый и второй ряды управляемых ячеек памяти /далее УЯП/ 9, выходами соединенных с информационными входами соответственно первого и второго рядов электронных ключей /далее ЭК/ 10, связанных выходами с рядом двухвходовых элементов ИЛИ 11, а своим управляемым выходом первый ЭК связан с выходом первого элемента И 12, один вход последнего связан с дешифратором 13, а другой вход, через второй элемент И 14 с четвертым элементом ИЛИ 15 и через инвертор 16 с третьим элементом И 17, который вторым входом подключен к первому элементу ИЛИ 18, а выходом, через второй элемент ИЛИ 19 к четвертому элементу И 20, своим входом соединенного с третьим элементом ИЛИ 21, третьего электронного ключа 22, управляющий вход которого связан с пятым элементом ИЛИ 23, а информационные входы с выходами программного блока.

Работа первого и второго рядов ЭК 10 состоит в том, что при наличии единичных сигналов на их управляющих входах, они пропускают сигналы с выходов первого или второго рядов ячеек памяти 9 на входы двухвходовых элементов ИЛИ 11.

При наличии нулевого сигнала на управляющем входе третьего ЭК 22 последний пропускает логические команды C3...C5, поступающие с БП 7 на входы БКВ 2 и C3...C5 после этого обозначаются через C'3...C'5 и которые вместе с командами C1 и C2, поступающими с двух первых выходов блока 7 управляют работой блока БКВ 2.

C6. ..Cj - адресные команды, определяющие номера ячеек памяти в блоках 3 и 4, или номер входного сигнала в блоке 1, а также номера внеочередных тактов при определенных сочетаниях команд Cj+1 и Cj+2 двух последних выходов блока 7.

Cj+1 и Cj+2 - команды, определяющие процедуру перескока номеров выполняемых команд.

X1. . .Xn - входные сигналы, поступающие с дискретных датчиков /на схеме не показаны/ от объема управления.

a1. . . ak - сигналы, устанавливающие счетные триггеры 54 блока 7 в состояние, соответствующее внеочередному номеру такта.

b1 - синхроимпульс, поступающий с выхода элемента 42 блока БКВ 2.

b2 - сигнал синхронизации, поступающий на каждом такте из блока БС 5 на элементы 17, 20 и 22 блока БУ 8.

е, б, г, д - сигналы, поступающие с выходов дешифратора 3 блока 2 на соответствующие входы элементов 18 и 21 блока 8.

Первый и второй ряды ячеек памяти принимает и записывает информационные сигналы C3...Cj при наличии единичных командных сигналов, поступающих с выхода дешифратора 13 блока 8 при Cj+1=0 и Cj+2=0 для первого ряда и при Cj+1=1 и Cj+2= 0 для второго ряда. При этом третий электронный ключ 22 заперт и не пропускает значения C3, C4 и C5 на входы блока 2. На выходе ЭК 22 в этом случае имеются сигналы "0".

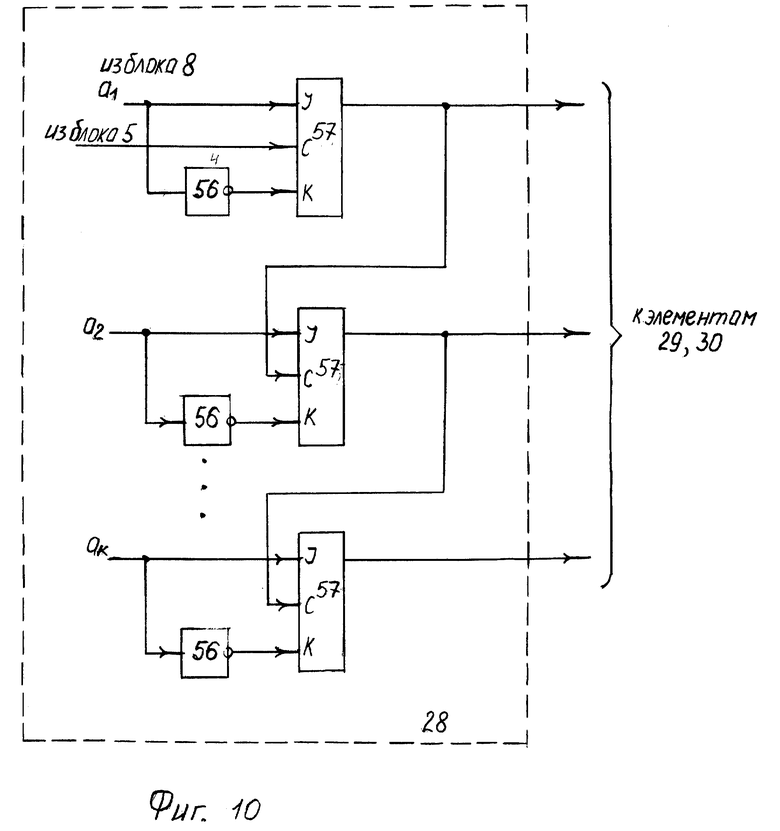

Программный блок 7 известной конструкции /фиг.3/ состоит из счетчика импульсов с установочными входами 28 на счетный вход которого поступают импульсы из блока синхронизации 5, а на установочные входы подаются сигналы a1. . .ak из блока БУ 8, которые при Cj+2=1 переводят счетчик 28 во внеочередное положение. При Cj+2=0 счетчик 28 работает в обычном счетном режиме, дешифратора 29, распределяющего импульсы по элементам постоянной памяти 30 /например серии ПЗУ 155РЕЗ/, на которые записываются программы работы всего устройства. Перед началом работы счетчик 28 устанавливается в исходное нулевое положение. Подробнее схема счетчика 28 представлена на фиг.10, где индексом 50 обозначен элемент НЕ, а индексом 51 обозначены счетные триггеры с установочными J и K-входами.

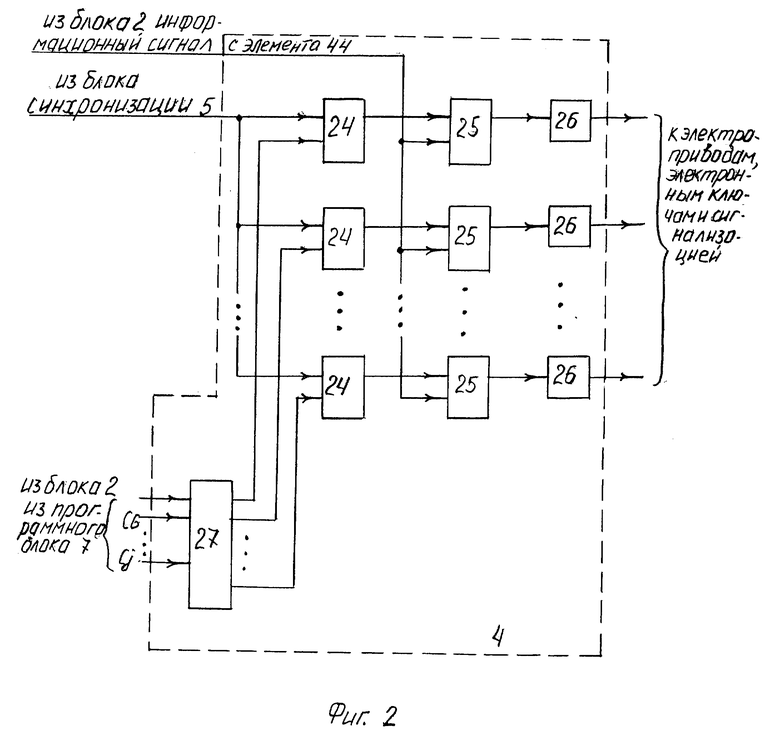

Выходной блок 4 /фиг. 2/ состоит из элементов И 24, ячеек памяти 25, куда заносится информация из блока БКВ 2 и соответствующих усилителей 26, передающих логические сигналы из ячеек памяти на электроприводы и т.д., по адресам, определяемым адресными сигналами C6...Cj, командам из блока 2, поступающим на дешифратор 27.

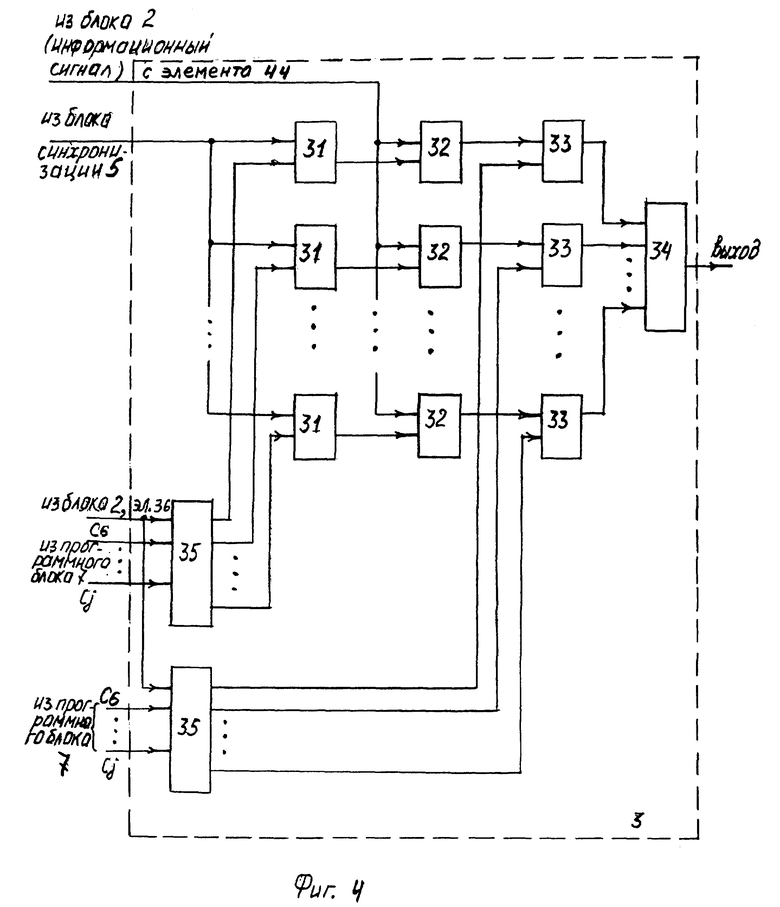

Блок оперативной памяти 3, который представлен на фиг.4 содержит элементы И 31 обращения к ячейкам памяти. В качестве последних можно использовать стандартные ОЗУ, или как в нашем примере отдельные элементы памяти 32, элементы считывания 33 /например элемент И/, элемент ИЛИ 34, первый и второй дешифраторы 35, при этом через соответствующий элемент заносится или считывается информация по команде из блока БКВ 2 и в соответствии с адресным кодом C6...Cj.

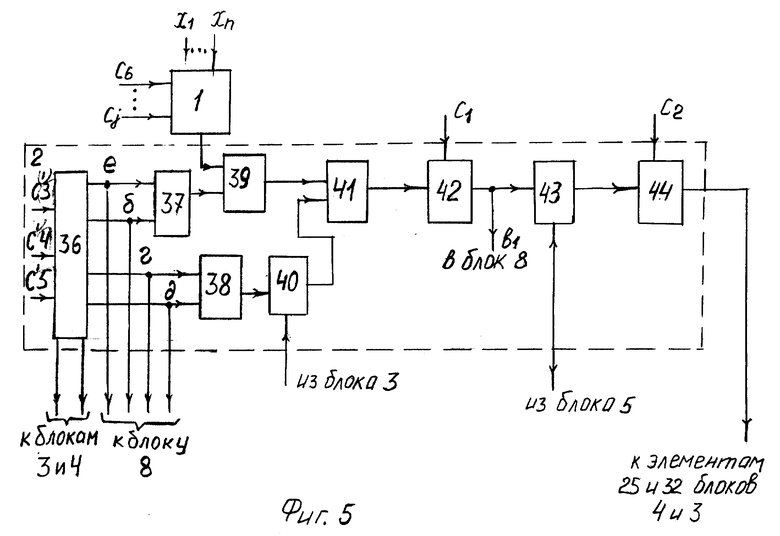

Блок БКВ 2 логической структуры /фиг. 5/ состоит из трехвходового дешифратора 36, своими входами связанного с выходами C'3, C'4 и C'5 блока 8, а первым /верхним/, вторым введенным, третьим и четвертым введенным выходами, соединенного с входами введенных элементов ИЛИ 37 и 38, выходы которых связаны с первыми входами элементов И 39 и 40, вторые входы последних подключены к входному блоку и блоку БОП 1 и 3, а выходы к входам элемента ИЛИ 41, выход которого связан с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 42, второй вход последнего соединен с выходом C1 блока 7, а выход подключен, через элемент И 43 с управляющим входом ячейки памяти 44, информационный вход которой соединен с выходом C2 блока БП 7, а выход с информационными входами блока 3 и блока 4. Пятый и шестой выходы дешифратора 36 связаны с управляющими входами блоков БОП 3 и БВ 4, а первые четыре выхода соединены также с блоком БУ 8. Принцип работы блока БКВ 2 известен.

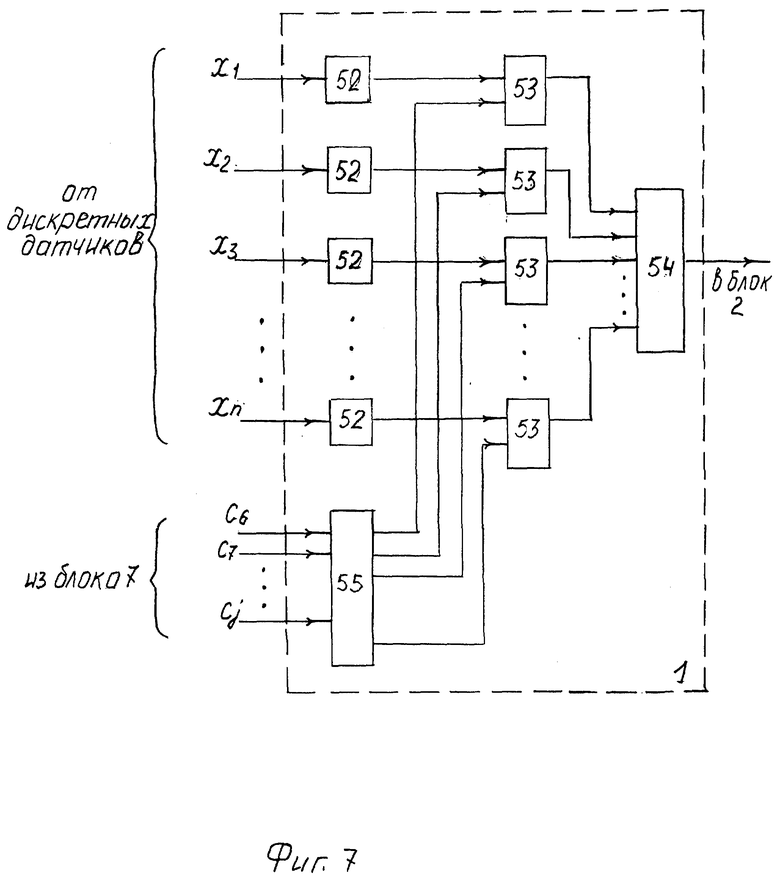

Входной блок 1 /фиг. 7/ содержит элементы согласования 52, связанные входами с датчиками, а выходами с первыми входами элементов И 53, выходы которых через элемент ИЛИ 54 соединены с блоком 2, а вторые входы элементов 53 подключены к выходам дешифратора 55. входы которого соединены с блоком программ 7.

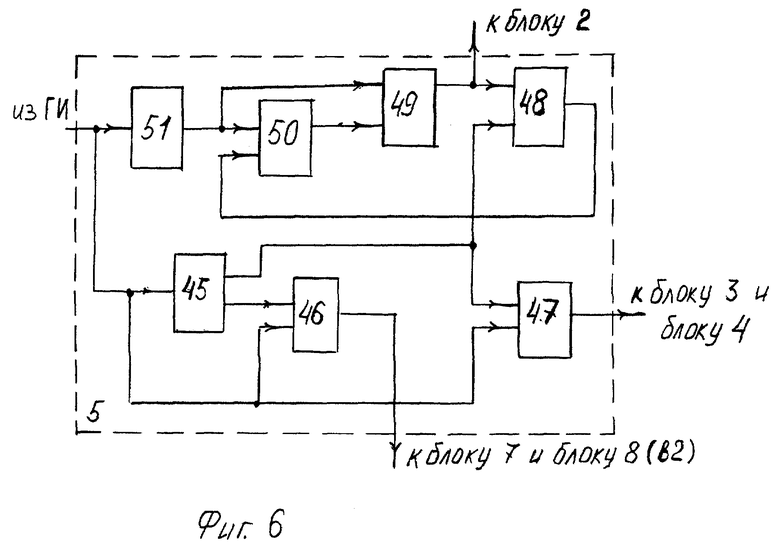

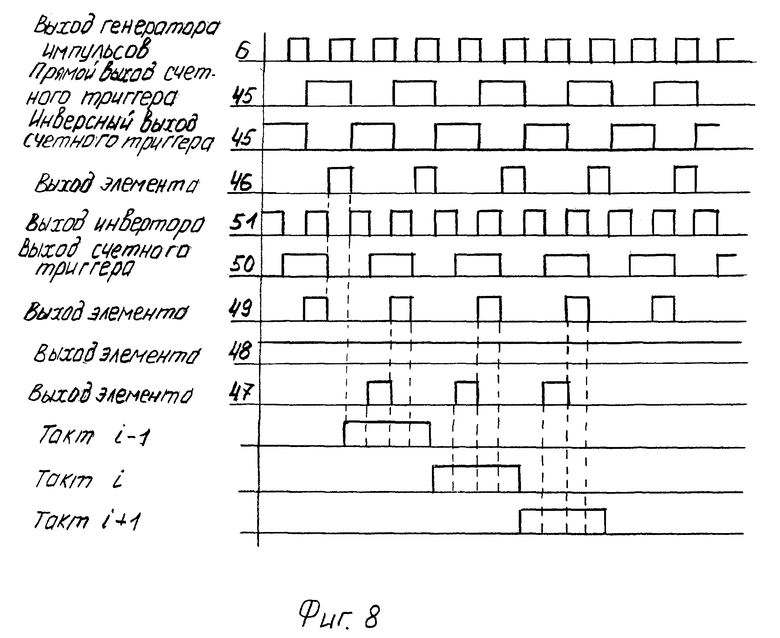

Блок синхронизации 5 известной конструкции /фиг. 6/ содержит первый счетный триггер 45, подключенный прямым выходом к элементу И 46, а инверсным выходом к первым входам элементов И 47 и И 48, второй вход последнего подключен к выходу элемента И 49, входы которого связаны с прямым выходом второго счетного триггера 50 и с выходом инвертора 51, вход которого вместе с входом триггера 45 являются входами блока 5 и соединены с ГИ 6. Работа блока 5 поясняется диаграммами /фиг. 8 и 9/.

Принцип работы устройства раскроем на примере вычисления двух функций f1 и f2:

f1=(X1+X2+...+Xm)(Xm+1+...+ Xm+k)...(Xm+n+...+Xm+n+L)+f'1.

Обозначим функцию, содержащую переменные X1...Xm+n+L через f'1

f2=  X2...Xm(Xm+1+...+ Xm+k)...(Xm+n+...+Xm+n+L)+f'2.

X2...Xm(Xm+1+...+ Xm+k)...(Xm+n+...+Xm+n+L)+f'2.

Обозначим функцию, содержащую переменные X1...Xm+n+L через f''2.

При вычислении f1 на первом такте при C1=1 и C2=0 ячейку памяти 44 блока 2 устанавливаем в состояние "0". Затем на этом же такте из блока 7b первый /верхний/ ряд ячеек памяти 9 записываются значения C3...Cj, соответствующие номеру такта, с которого начинается вычисление второй дизъюнкции функции f''1 при Cj+1 и Cj+2, равными "0". На втором такте во второй ряд ячеек памяти 9 под действием команд Cj+1=1 и Cj+2=0 записываются значения C3...Cj, соответствующие номеру такта на котором начинается вычисление функции f'1. На третьем такте под действием команд /ЭК 22 открыт/ C1=0, C2=1, C'3=1, C'4= 0 и C'5=0 значение X1, проходит на элемент 39 блока 2 и далее, через элементы 41, 42 и 43, поступает на управляемый вход ячейки 44. При этом, если X1= 0 ячейка 44 не меняет своего состояния и вычисление продолжается известным порядком, описанным в прототипе, т.е. на следующем такте вызывается переменная X2 и т.д., пока не обследуется последняя переменная Xm и если одна из переменных X1. . .Xm равна "1", то под действием этой "1" при C1=0 значение C2=1 запишется в ячейку памяти 44 блока 2, а если все переменные X1...Xm равны "0", то состояние ячейки 44 не изменятся. Это и будет результатом вычисления первой дизъюнкции функции f''1. Вернемся к третьему такту. При X1=1 вычислять значение первой дизъюнкции нет смысла, т.к. она обязательно равна "1" и ее значение в нашем случае от переменных X2...Xm независит. Под действием единичного сигнала b1 с выхода элемента 42 блока 2 /C1=0 и X1=1/ при C'3= 1, C'4=0, C'5=0, Cj+1=0, Cj+2=1 и b2=1 активизируется первый выход "е" дешифратора 36 блока 2 и под действием управляющего сигнала, сформированного при помощи элементов 15, 14 и 12 блока 8 открывается первый /верхний/ ряд ЭК 10 и под действием сигналов, ранее записанных в первый ряд ячеек памяти 9 блока 8 и проходящих через ряд элементов ИЛИ 11 на установочные J-K-входы триггеров 28 блока 7, при этом триггеры 28 устанавливаются в положение, соответствующее номеру такта, на котором начинается вычисление второй дизъюнкции функции f''1. Вышеописанный алгоритм /процедура/ реализуется при первом значении любой переменной из X1...Xm равном "1". Аналогичный процесс реализуется, если переменная, ранее записанная в блок БОП 3 считывается из него при C3= 1, C4=1 и C5=0, но при этом активизируется третий выход дешифратора 36 блока 2. Допустим, что все значения X1...Xn равны "0", тогда под действием команд C'3=1, C'4=0, C'5=0, Cj+1=1 и Cj+2=1 активизируется первый выход "е" дешифратора 36 блока 2 и переменная Xm=0 поступает на вход элемента 42 блока 2 и при C1=0 на выходе элемента 42 сохраняется "0", т.е. b1=0. При этом на выходе элемента ИЛИ 19 появится сигнал "1", т.к. под действием единичных сигналов на выходе инвертора 16, элемента 18, четвертом выходе дешифратора 13 и при b2=1 на выходе элемента И 17 появится сигнал "1", т.е. на управляющий вход второго ряда ЭК 10 поступит сигнал "1" с выхода элемента 19 и ранее /на втором такте/ записанная информация во второй ряд ячеек памяти 9, через второй ряд открытых ЭК 10 и элементы ИЛИ 11 попадает на J-K-входы триггеров 28 блока 7 и устанавливает их в положение, обеспечивающее начало вычисление функции f'1, т.к. при нулевых значениях X1...Xm f''1=0. Из вышеизложенного следует, что предложенное устройство позволяет учитывать только те переменные из набора X, которые являются в данный момент активными, т.е. от которых зависит результат вычисления функции f1 и тем самым сокращает число тактов, необходимых для вычисления функций f1. Устройство позволяет делать три выбора для оптимальных вычислений автоматическим способом. Первый выбор позволяет проводить вычисления известным путем, проверяя значения всех переменных данной подфункции. Второй выбор позволяет сократить число тактов при вычислении подфункций, например дизъюнкции, если одна из переменных равна "1". Третий выбор состоит в том, что в случае нулевого значения первой дизъюнкции, входящей в состав конъюнкции автоматически организуется вычисление последующей функции, как например в нашем случае функции f'1. Поэтому в примере были заранее записаны номера внеочередных тактов для двух возможных переходов при вычислении функций f''1 и f'1. Перейдем к вычислению функции f2. На первом такте в ячейку памяти 44 блока 2 запишем "1" при C1=1, C2=1, запишем в первый ряд ячеек памяти 9 блока 8 сигналы C3...Cj, соответствующие номеру такта для начала вычисления второй дизъюнкции функции f''2 при Cj+1=0 и Cj+2= 0. На втором такте при Cj+1=1 и Cj+2=0 запишем сигналы C3...Cj, обеспечивающие вычисление функции f'2. На третьем такте при C3=0, C4=1, C5=1 и C2=0 активизируется выход "b" дешифратора 36 блока 2 и значение переменной  через элементы 39, 41, 42 и 43 подается на управляющий вход ячейки памяти 44 блока 2. Если

через элементы 39, 41, 42 и 43 подается на управляющий вход ячейки памяти 44 блока 2. Если  = 1, то процесс вызова и анализа переменных X2...Xm продолжается и если они также равны "1", то никакого перехода к внеочередному такту не будет. Если же одна из переменных

= 1, то процесс вызова и анализа переменных X2...Xm продолжается и если они также равны "1", то никакого перехода к внеочередному такту не будет. Если же одна из переменных  ,,, Xm равна "0" то на выходе элемента 42 появится "1" при C1=1, C2=0, C3=0, C4=1, C5=0 /в случае вызова X1/, активизируется выход "b", на выходе элемента 42 появится "1", b1= 1 и при Cj+1=1, Cj+2=1 с помощью логических операций в элементах 15, 14, 21, и 19 на управляющий вход нижнего ряда ЭК 10 поступит сигнал, открывающий нижний ряд ЭК 10 и ранее записанная в нижний ряд ячеек памяти 9 информация поступит, через элементы ИЛИ 11 на J-K-входы триггеров 28 блока 7 и установит их в положение, обеспечивающее начало вычисления функции f'2, т.к. функция f''2 равна "0". Введение в блок 2 дополнительных выходов для дешифратора 36 и элементов ИЛИ 37 и 38 позволяет автоматически менять работу блока 8 в зависимости от типа функций, например приведенных в примере при помощи элементов 18 и 21 в блоке 8. Третий и четвертый выходы дешифратора 36 активизируются, когда переменные вызываются из блока БОП 3.

,,, Xm равна "0" то на выходе элемента 42 появится "1" при C1=1, C2=0, C3=0, C4=1, C5=0 /в случае вызова X1/, активизируется выход "b", на выходе элемента 42 появится "1", b1= 1 и при Cj+1=1, Cj+2=1 с помощью логических операций в элементах 15, 14, 21, и 19 на управляющий вход нижнего ряда ЭК 10 поступит сигнал, открывающий нижний ряд ЭК 10 и ранее записанная в нижний ряд ячеек памяти 9 информация поступит, через элементы ИЛИ 11 на J-K-входы триггеров 28 блока 7 и установит их в положение, обеспечивающее начало вычисления функции f'2, т.к. функция f''2 равна "0". Введение в блок 2 дополнительных выходов для дешифратора 36 и элементов ИЛИ 37 и 38 позволяет автоматически менять работу блока 8 в зависимости от типа функций, например приведенных в примере при помощи элементов 18 и 21 в блоке 8. Третий и четвертый выходы дешифратора 36 активизируются, когда переменные вызываются из блока БОП 3.

Представленное устройство позволяет уменьшить количество тактов при вычислении булевых функций, что позволяет сократить время реакции системы управления на изменение входных параметров в объекте управления и повысить быстродействие вычислительных и управляющих комплексов.

Изобретение относится к программируемым и управляющим вычислительным устройствам и может применяться в системах управления различными технологическими линиями, вычислительных комплексах. Технический результат - повышение быстродействия устройства за счет возможности выбора направления вычисления булевых функций. Это достигается тем, что устройство содержит коммутационно-вычислительный блок, блок оперативной памяти, входной и выходной блоки, генератор импульсов, блок ускорения, программируемый блок. 10 ил.

Устройство для дистанционного программного управления электроприводами, электронными ключами и сигнализацией, содержащее коммутационно-вычислительный блок, связанный входами с входным блоком, первая группа входов которого связана с дискретными датчиками, а вторая группа входов - с блоком синхронизации, связанным с генератором импульсов и программным блоком, соединенным с входным блоком и блоком синхронизации, генератор импульсов соединен выходом с входом блока синхронизации, причем коммутационно-вычислительный блок состоит из дешифратора, элементов И, ячейки памяти, первого элемента ИЛИ и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы дешифратора подключены к соответствующим входам блока оперативной памяти и выходного блока, первые входы двух элементов И связаны с выходами входного блока и блока оперативной памяти, а выходы соединены с входами первого элемента ИЛИ, вход которого соединен с элементом ИСКЛЮЧАЮЩЕЕ ИЛИ, который соединен с третьим элементом И, подключенным к управляющему входу ячейки памяти, выход которой связан с информационными входами блока оперативной памяти и выходного блока, передающим сигналы на электроприводы, электронные ключи и сигнализацию, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и информационный

вход ячейки памяти соединены с соответствующими выходами программного блока, второй вход третьего элемента И подключен к блоку синхронизации, отличающееся тем, что в устройство введен блок ускорения, содержащий первый и второй ряды управляемых ячеек памяти, четыре элемента И, первый и второй ряды электронных ключей и третий электронный ключ, дешифратор, инвертор, ряд двухвходовых элементов ИЛИ и пять элементов ИЛИ, причем информационные входы двух рядов ячеек памяти соединены с всеми выходами, кроме двух первых и двух последних, программного блока, а управляемые входы двух рядов ячеек памяти связаны с первым и вторым выходами дешифратора блока ускорения, входы упомянутого дешифратора подключены к двум выходам программного блока, выходы первого и второго рядов ячеек памяти соединены соответственно с информационными входами первого и второго рядов электронных ключей, выходы которых связаны с рядом двухвходовых элементов ИЛИ, а выходы ряда двухвходовых элементов ИЛИ соединены с установочными входами счетных триггеров программного блока, управляющий вход первого ряда электронных ключей соединен с выходом первого элемента И блока ускорения, первый вход первого элемента И блока ускорения подключен к третьему выходу дешифратора блока ускорения, второй вход связан с выходом блока синхронизации и входом программного блока, а третий вход соединен с выходом второго элемента И блока ускорения и через инвертор с первым входом третьего элемента И блока ускорения, второй, третий и четвертый входы третьего элемента И блока ускорения связаны соответственно с выходом блока синхронизации, четвертым выходом дешифратора блока ускорения и с выходом первого элемента ИЛИ

блока ускорения, а выход третьего элемента И блока ускорения подключен к первому входу второго элемента ИЛИ, выход которого связан с управляющим входом второго ряда электронных ключей, а второй вход соединен с выходом четвертого элемента И блока ускорения, первый - четвертый входы четвертого элемента И блока ускорения подключены соответственно к второму и третьему входам третьего элемента И блока ускорения, к выходу третьего элемента ИЛИ блока ускорения и к выходу второго элемента И блока ускорения, первый вход второго элемента И блока ускорения подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ коммутационно-вычислительного блока, а второй вход связан с выходом четвертого элемента ИЛИ блока ускорения, входы четвертого элемента ИЛИ блока ускорения соединены через третий электронный ключ с тремя выходами программного блока, информационные входы третьего электронного ключа подключены к трем выходам программного блока, а выходы - к управляющим входам коммутационно-вычислительного блока, управляющий вход третьего электронного ключа соединен с пятым элементом ИЛИ блока ускорения, пятый элемент ИЛИ соединен с первым и вторым выходами дешифратора коммутационно-вычислительного блока, входы первого и третьего элементов ИЛИ блока ускорения подключены к соответствующим выходам дешифратора коммутационно-вычислительного блока, при этом в коммутационно-вычислительный блок введены два элемента ИЛИ, входы введенных элементов ИЛИ коммутационно-вычислительного блока подключены к четырем выходам дешифратора коммутационно-вычислительного блока, а выходы соединены с первыми входами двух элементов И коммутационно-вычислительного блока, вторые входы которых связаны с выходами входного блока и блока оперативной памяти.

| Устройство для дистанционного программного управления сигнализацией и электропроводными механизмами | 1990 |

|

SU1801223A3 |

| Устройство для дистанционного программного управления электроприводными механизмами | 1982 |

|

SU1071999A1 |

| Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами | 1988 |

|

SU1635162A1 |

| Устройство для дистанционного программного управления сигнализацией и электроприводными механизмами | 1990 |

|

SU1799478A3 |

Авторы

Даты

1999-08-10—Публикация

1997-07-11—Подача