Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частот.

Цель изобретения - повышение быстродействия многоразрядного управляемого делителя частоты.

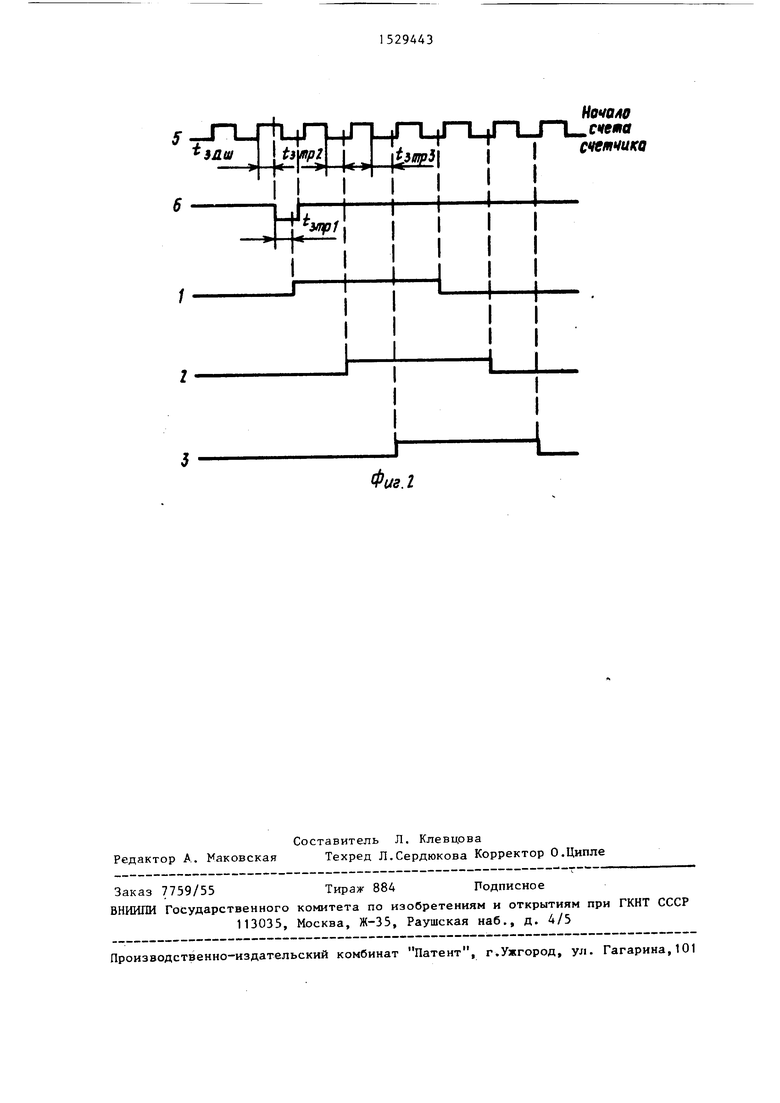

На фиг, 1 приведена электрическая функциональная схема многоразрядного управляемого делителя частоты, на фиг. 2 - временные диаграммы, поясняющие его работу.

Многоразрядный управляемый делитель частоты содержит первый 1, второй 2 и третий 3 УК-триггеры, счет чики 4 импульсов со схемой записи кода, входную шину 5, выходную шину 6, шину 7 управления, при этом счетный вход счетчика 4 соединен с вход- ной пшной 5 и входами синхронизации первого 1, второго 2 и третьего 3 триггера, входы управления - с шиной 7 управления, выход переноса - с выходом 9 установки в единицу первого триггера 1, входом R установки в нул второго триггера 2 и входной шиной 6. Вход 7 первого триггера 1 подключен к нулевой шине, прямой и инверсный выходы первого триггера 1 соединены соответственно с входами Э и К второго триггера 2, прямой выход которого соединен с входом третьего триггера 3 и входом предварительной установки счетчика 4 импульсов, инверсный выход второго триггера 2 соединен с входом К третьего триггера 3 и входом разрешения переноса счетчика 4 импульсов, вход разрешения счета которого соединен с инверсным выходом третьего триггера 3, прямой выход которого соединен с входом К первого триггера 1,

Устройство работает следующим образом.

В момент наполнения счетчика 4, подсчитывающего отрицательные перепады входной частоты, на выходе переноса этого счетчика повляется сигнал переполнения, длительность которого равна длительности импульса входной частоты, поступающей на входную шину 5, а задержка относительно фронта входной частоты равна времени задержки одного цифрового логического элемента, так как схема переноса строби руется импульсами входной частоты J-вход первого -триггера 1 подключен

5

0

5

0

5

0

35

40

45

50

55

к нулевой шине, поэтому после подачи питания на устройство первый 1, второй 2 и третий 3 триггеры через несколько интервалов входной опорной частоты установятся в состояние О (триггеры переключатся по отрицательному перепаду входной частоты) и будут находиться в этом состоянии до прихода импульса переполнения с выхода переноса счетчика 4 импульсов.

Импульс переполнения переключает первый триггер 1 в состояние 1 по приоритетному входу S установки в единицу и удерживает второй триггер 2 в состоянии о по приоритетному входу R установки в нуль, не давая возможности переключиться второму триггеру 2 в состояние Г по отрицательному перепаду входной опорной частоты, поступающей на вход синхронизации, даже при наличии на 7 -входе второго триггера 2 логической единицы. После следующего отрицательного перепада входной опорной частоты первый триггер 1 не изменит своего состояния, так как на его}- и К-вхо- ды будут поданы уровни логического нуля с нулевой шины и прямого выхода третьего трнгтера 3 соответствен:- но. Второй триггер 2 переключится, в состояние 1, так как на его входе У будет присутствовать уровень логической единицы,а на пходе-К - уровень логического нуля, поступающие соответственно с прямого и инверсного выходов первого триггера 1, Причем сигнал переполнения на входе R установки в нуль к этому времени прекратится.

После следующего среза сигнала входной частоты, поступающего с входной шины 5, третий триггер, 3 переключается в состояние 1. Задержка сигналов на прямом и инверсном выходах второго 2 и третьего 3 триггеров относительно среза входной опорной частоты равна только времени их переключения.Сигнал записи с прямого выхода второго триггера 2 поступает на вход предварительной установки счетчика импульсов, при наличии уровня логической единицы на входе которого (или положительного перепада) осуществляется запись информации с шины 7 управления в счетчик 4 импул1 сов. Одновременно с инверсного выхода второго триггера 2 поступает сигнал на вход

5

разрешения переноса счетчика 4 импульсов и закрывает схему формирования сигнала переноса, Закрывание схемы переноса счетчика 4 импульсов позволяет исключить появление ложных сигналов на ее выходе при многоступенчатой схеме переноса и времени записи информации с шин 7 управления, соизмеримом с периодом входной частоты. Через время,равное периоду входной частоты, после поступления импульса записи с триггера 2 на вход предварительной установки счетчика 4 импульсов запрещается подсчет входных импульсов, поступающих с шины 5. Так как на вход разрешения счета поступает сигнал запрета с инверсного выхода третьего триггера 3,

После переключения третьего триггера 3 в состояние 1 на К-вход первого триггера 1 поступает уровень логической единиць с прямого выхода третьего триггера 3 и по следующему отрицательному перепаду, поступающему на вход синхронизации, первый триггер 1 переключается в состояние О. Через время, равное периоду входной частоты, переключается в со- состояние О второй триггер 2, а еще через период опорной частоты - третий триггер 3 по отрицательным перепадам входной частоты, поступающей на входы синхронизации с шины 5 Длительность импульса записи, формируемого вторым триггером 2, равна трем периодам входной частоты, что обеспечивает надежную запись информации с шины 7 управления в счетчик 4.импульсов при высокой частоте вход ного сигнала, поступающего на ши1гу 5 Б случае осуществления записи информации в счетчик 4 импульсов низким уровнем входного сигнала (или от рицательным перепадом) на вход пред варительной установки счетчика 4 импульсов следует подавать сигнал с ин версного выхода второго триггера 2.

Сигнал, формируемый третьим триггером 3, задержан относительно сигна ла записи, поступающего на вход пред варительной установки счетчика 4 импульсов, на период входной частоты. Таким образом, сигнал разрешения записи информации с шины 7 в счетчик 4 импульсов, формируемый вторым триг гером 2, закончится раньше, чем сигнал запрета счета, поступающий на

29443

вход разрешения счета счетчика 4 импульсов с инверсного выхода третьего триггера 3.

Время, равное периоду входной частоты, требуется для прохождения сигнала в схеме записи кода и триггерах счетчика 4 импульсов с учетом задержки распространения сигнала.

Q После переключения третьего триггера в состояние О и появления на его инверсном выходе уровня напряжения логической единицы сигнал запрета счета снимается и счетчик 4 пере(5 ходит в режим счета импульсов, поступающих с шины 5.

Далее цикл повторяется до момента наполнения счетчика 4 импульсов и появления сигнала переполнения на

20 выходе схемы переноса. Сигнал переноса счетчика является и выходным сигналом многоразрядного управляемого делителя частоты. Выходной сигнал может сниматься с выходов второго 2

25 и третьего 3 триггеров, в этом случае задержка его относительно фронта опорной частоты будет- равна только времени их переключения.

В случае использования вьгчитающе30 го счетчика 4 импульсов коэффициент деления управляемого делителя частоты следования импульсов .определяется выражением

л ,

г вых

40

35 - 1вых

где Кд - коэффициент деления многоразрядного управляемого делителя частоты, значение частоты выходного , игнала;

f, - значение частоты, входного

WA

сигнала-,

N - значение двоичного кода, 45подаваемого на шину 7 управления.

Быстродействие предлагаемого многоразрядного делителя частоты определяется условием

50 т f + t

n Чр МАГ

где t-p - задержка переключения тригrepai

tjj - время между окончанием им- 55пульса запрета счета и перепадом входной частоты,необходимое для подготовки триггера 1 к очередному переключению .

Условие вытекает из того, что сигналы на выходах триггеров 2.3 задержаны относительно перепада входной частоты только на время перегатючения одного триггера, и счет в очередном цикле начинается после окончения им- .пульса на инверсном выходе третьего триггера 3 по ближайшему отрицательному перепаду.

Быстродействие описанного многоразрядного управляемого делителя частоты равно быстродействию счетного триггера младшего разряда счетчика 4 импульсов.

Для надежной работы делителя частоты задержка сигнала переноса счетчика 4 импульсов относительно фронта входной частоты не должна превьшать половины периода входного сигнала (при условии, что входной сигнал - типа меандр).

В многоразрядном делителе при многоступенчатом дешифраторе схемы переноса счетчика импульсов и времени записи информации с шины управления, соизмеримом с периодом входной частоты, данная схема многоразрядного управляемого делителя частоты позволяет существенно повысить быстродействие делителя, так как скорость переключения в этом случае определяется временем переключения только одного триггера.

Таким образом, в предлагаемом многоразрядном управляемом делителе введение третьего триггера и дополнительных связей позволяет увеличить интервал, отводимый для записи кода, и, следовательно, произвести уверен- нную запись, ис-ключшз появление ложных импульсов на выходе дешифратора, т.е. устранить сбои в работе делителя и увеличить быстродействие при

сохранении стабильности работы.

Быстродействие предлагаемого многоразрядного делителя частоты по сравнению с прототипом, выбранным за базовый объект, увеличивается в 22,5 раза.

Формула изобретения

Многоразрядный управляемый делитель частоты, содержащий первый У Ктриггер, прямой и инверсный выходы которого соединены соответственно с J- и К-входами второго J К-триггера, вход синхронизации -, с входом синхронизации второго 7 К-триггера, счетIным входом счетчика импульсов и входной шиной,S-вход - с выходной шиной и выходом переноса счетчика импульсов, информационные входы которого соединены с соответствующими разрядами шины управления, отличающийся тем, что, с целью по- вьш1ения быстродействия, в него введен третий У К-триггер,J -вход которого соединен с входом предварительиой установки счетчика импульсов и прямым выходом второго, К-триггера, К-вход - с входом разрешения переноса счетчика импульсов и инверсным выходом второго J К-триггера, вход

синхронизации - с входной шиной, инверсный выход - с входом разрешения счета счетчика импульсов, прямой вы ход - с К-входом первого -7 К-триггера, J -вход которого соединен с

шиной логического нуля,-а S-вход с R-входбм второгоJ К-триггера.

9йШ

HOfOAff

|Г |П |ГП |ГП П счета

CWnHUKQ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь код-временной интервал | 1989 |

|

SU1654980A1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1669079A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1653153A1 |

| Управляемый делитель частоты импульсов | 1983 |

|

SU1088135A1 |

| Многофункциональное счетное устройство | 1979 |

|

SU819969A2 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Цифровой линейный интерполятор | 1986 |

|

SU1310779A1 |

| СЕЛЕКТОР ПСЕВДОСЛУЧАЙНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 1993 |

|

RU2072627C1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники, а также в синтезаторах частот. Цель изобретения - повышение быстродействия многоразрядного управляемого делителя частоты. Она достигается за счет того, что сигналы на выходах триггеров 2 и 3 задержаны относительно перепада входной частоты только на время переключения одного триггера и счет в очередном цикле начинается после окончания импульса на инверсном выходе третьего триггера 3 по ближайшему отрицательному перепаду и за счет введения в делитель частот IK - триггера 3 и образования новых функциональных связей. Кроме того, делитель частот содержит два IK-триггера 1, 2, счетчик 4 импульсов, шины 5, 6, 7 входную, выходную, кодовую соответственно и шину логического нуля. Изобретение позволяет повысить быстродействие делителя, произвести уверенную запись кода в многоразрядном делителе при многоступенчатом дешифраторе схемы переноса счетчика импульсов. 2 ил.

Фиг.г

| Угрюмов Е.А | |||

| Элементы и узлы ЭЦВМ | |||

| М., Высшая школа, 1976, с.218, рис | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Управляемый делитель частоты следования импульсов | 1984 |

|

SU1218461A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-18—Подача