Изобретение относится к устройству включения более высоких напряжений на полупроводниковой интегральной схеме с первой последовательной схемой из первого p-канального и первого n-канального транзистора, которая включена между выводом для первого высокого и выводом для первого низкого потенциала, с второй последовательной схемой из второго p-канального и второго n-канального транзистора, которая включена между выводом для первого высокого потенциала и первым входным выводом, причем точка соединения обоих транзисторов первой последовательной схемы соединена с выводом затвора второго p-канального транзистора и образует вывод для выходного сигнала, причем точка соединения транзисторов второй последовательной схемы соединена с выводом затвора первого p-канального транзистора, и причем вывод затвора второго n-канального транзистора образует второй входной вывод.

Изобретение относится, кроме того, к способу эксплуатации такого устройства.

Такое устройство является известным из публикации Proceedings ISSCC 1991, стр. 260. При этом вывод затвора первого n-канального транзистора соединен с выводом затвора первого p-канального транзистора. Кроме того, первый низкий потенциал равен потенциалу корпуса.

В интегральных схемах на полупроводниковых кристаллах часто является необходимым, кроме обычных напряжений питания, например +5 В и 0 В, в транзисторно-транзисторной логике и КМОП подводить или формировать на интегральной схеме из напряжений питания и, при необходимости, включать и выключать другие напряжения, которые могут быть значительно более высокими или также отрицательными. Если такие полупроводниковые интегральные схемы содержат нетеряемые при отключении питания накопители, как, например, стираемые программируемые постоянные накопители (EPROM), электронно-стираемые программируемые постоянные накопители (EEPROM) или стираемые вспышкой (Flash-) накопители, то для них требуются программирующие напряжения, которые должны иметь значения в области от 12 В до 20 В или в зависимости от конструкции накопителя могут быть также отрицательными. Известное устройство служит для включения более высокого программирующего напряжения. Однако этим известным устройством нельзя включать никакие отрицательные напряжения.

Задачей изобретения является указание устройства для включения более высоких напряжений на полупроводниковой интегральной схеме, в котором могут включаться как положительные, так и отрицательные напряжения и которые при этом являются свободными от поперечных токов. Другой задачей изобретения является указание способа, которым может эксплуатироваться такое устройство.

Эта задача в соответствующем ограничительной части устройстве решается отличительными признаками пункта 1 формулы изобретения. Способы для эксплуатации такого устройства указаны в пунктах 4 и 5 формулы изобретения. Предпочтительные дальнейшие формы развития изобретения приведены в зависимых пунктах формулы изобретения.

Соответствующее изобретению устройство может простым образом использоваться без дополнительных схемно-технических затрат в качестве неинвертирующего или инвертирующего переключателя. Функционирование является зависимым только от напряжений, которые прикладываются к четырем входным выводам и от того, как эти последние соединены между собой. Особенно предпочтительным является, если подключаемое напряжение при включении имеет линейно нарастающий ход. Для избежания напряжения смещения подложки в логической части полупроводниковой интегральной схемы является выгодным, в случае n-подложки соединенные с первым высоким потенциалом p-канальные транзисторы, а в случае p-подложки соединенные с первым низким потенциалом n-канальные транзисторы выполнять в ванне того же типа проводимости, что и подложка, которая изолирована от подложки областью другого типа проводимости.

Изобретение поясняется ниже на примерах выполнения с помощью фигур. При этом на фигурах показано:

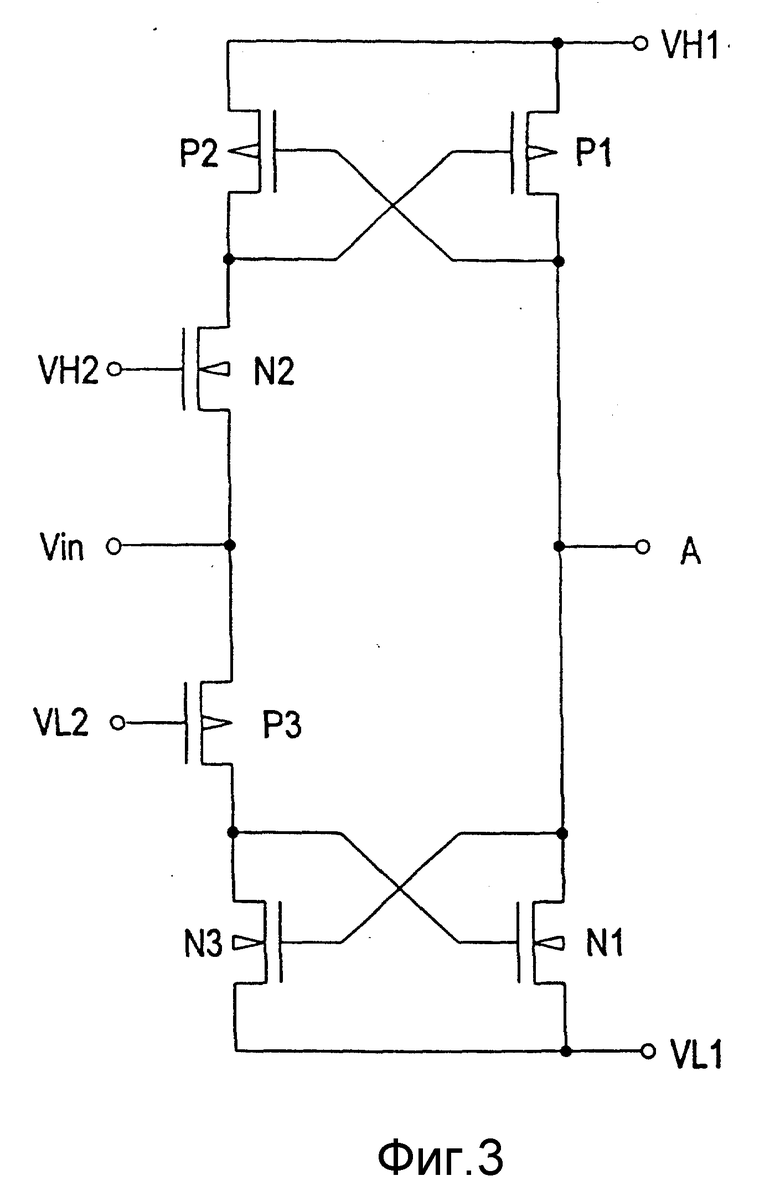

фиг. 1 общее представление соответствующего изобретению устройства с возможностью трех состояний;

фиг. 2 представление неинвертирующего переключателя;

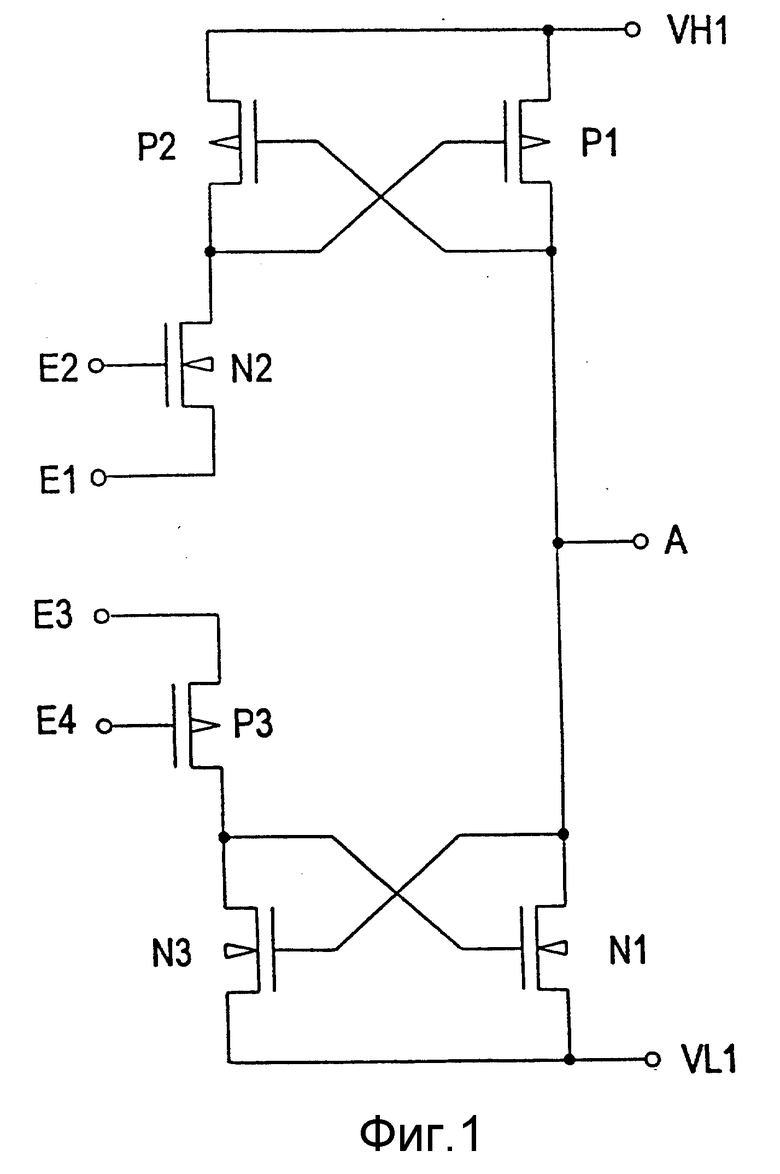

фиг. 3 представление инвертирующего переключателя и

фиг. 4 возможности технологической реализации.

В соответствующем изобретению устройстве согласно фиг. 1 между выводом для первого высокого потенциала VH1 и выводом для первого низкого потенциала VL1 включена последовательная схема из первого p-канального транзистора P1 и первого n-канального транзистора N1. Точка соединения обоих транзисторов образует выходной вывод A. Между выводом для первого высокого потенциала VH1 и выводом затвора первого p-канального транзистора P1 включен нагрузочный участок второго p-канального транзистора P2. Вывод затвора этого второго p-канального транзистора P2 соединен с выходным выводом A. Вывод затвора первого p-канального транзистора P1 через нагрузочный участок второго n-канального транзистора N2 соединен, кроме того, с первым входным выводом E1. Вывод затвора этого второго n-канального транзистора N2 соединен с вторым входным выводом Е2. Между выводом затвора первого n-канального транзистора N1 и выводом для первого низкого потенциала VL1 включен нагрузочный участок третьего n-канального транзистора N3. Вывод затвора этого третьего n-канального транзистора N3 соединен также с выходным выводом A, в то время как вывод затвора первого n-канального транзистора N1 через нагрузочный участок третьего p-канального транзистора P3 соединен с третьим входным выводом E3. Вывод затвора третьего p-канального транзистора P3 соединен с четвертым входным выводом E4. Этим устройством с помощью подходящего выбора потенциалов на входных выводах E1 - E4 может переключаться к выходному выводу A или первый высокий потенциал VH1, или первый низкий потенциал VL1, или выходной вывод A может переключаться на высокое сопротивление. Особенным преимуществом этого устройства является то, что первый низкий потенциал VL1 может принимать отрицательные значения.

Для проключения первого высокого потенциала VH1 к выходному выводу A к второму входному выводу E2 должен быть приложен более высокий потенциал, чем к первому входному выводу E1. При этом потенциал на первом входном выводе E1 должен быть ниже, чем первый высокий потенциал VH1. За счет этого второй n-канальный транзистор N2 переключается в проводящее состояние, за счет чего также первый p-канальный транзистор P1 переключается в проводящее состояние. Выходной вывод A принимает тем самым значение первого высокого потенциала VH1 и переключает таким образом в проводящее состояние также второй p-канальный транзистор P2, за счет чего первый p-канальный транзистор P1 блокируется в своем проводящем состоянии. Если одновременно потенциал на четвертом входном выводе E4 является большим или равным потенциалу на третьем входном выводе E3, третий p-канальный транзистор P3 запирается, в то время как третий n-канальный транзистор N3 вследствие высокого потенциала на выходном выводе А и тем самым на своем выводе затвора является проводящим и подтягивает вывод затвора первого n-канального транзистора N1 к более первому низкому потенциалу VL1, за счет чего первый n-канальный транзистор N1 надежно запирается и блокируется третьим n-канальным транзистором N3 в этом положении.

Если потенциал на четвертом входном выводе E4 выбирают меньше, чем потенциал на третьем входном выводе E3, и потенциал на втором входном выводе E2 меньше, чем потенциал на первом входном выводе E1, то эквивалентным образом первый низкий потенциал VL1 проключается к выходному выводу A.

Устройство согласно изобретения эксплуатируется особенно выгодным образом, если проключаемый к выходному выводу A потенциал включается только после приложения потенциалов к входным выводам E1 - E4 и/или имеет линейно-возрастающий характер, то есть включается не внезапно, а медленно выводится до его конечного значения. За счет этого достигается особенно надежная работа.

Специальный вариант соответствующего изобретению устройства согласно фиг. 1 представлен на фиг. 2. Здесь входные выводы E1 и E4 объединены и нагружены управляющим сигналом Vin. На первом входном выводе E1 приложен второй низкий потенциал VL2, который больше или равен первому низкому потенциалу VL1, в то время как на четвертом входном выводе приложен второй высокий потенциал VH2, который меньше или равен первому высокому потенциалу VH1. Этот вариант представляет собой неинвертирующий относительно управляющего сигнала Vin переключатель, так как при уровне этого управляющего сигнала Vin, который равен второму высокому потенциалу VH2, выходной вывод A принимает значение первого высокого потенциала VH1 и наоборот.

В противоположность этому фиг. 3 показывает инвертирующий относительно управляющего сигнала Vin переключатель. Для этого первый и третий входные выводы E1, E3 объединены и нагружены управляющим сигналом Vin, в то время как на втором входном выводе E2 приложен второй высокий потенциал VH2 и на четвертом входном выводе E4 второй низкий потенциал VL2. Для значений вторых потенциалов справедливы те же самые условия, что и для схемы согласно фиг. 2.

Описанные устройства хотя и применимы в общем случае, однако особенно предпочтительным образом являются пригодными для управления линии слов в Flash-накопителях. Там второй высокий потенциал VH2 является напряжением питания интегральной схемы и второй низкий потенциал VL2 опорным потенциалом. Первый высокий потенциал VH1 является стирающим напряжением, а первый низкий потенциал VL1 программирующим напряжением. Кроме того второе положительное напряжение должно включаться в качестве считывающего напряжения на линию слов. Это происходит таким образом, что вместо стирающего напряжения это считывающее напряжение выбирают в качестве первого высокого потенциала. В зависимости от выбранного варианта соответствующего изобретению устройства в качестве инвертирующего или неинвертирующего переключателя таким образом за счет подходящего выбора управляющего сигнала Vin на линию слов может включаться желаемое напряжение.

Технологическая реализация устройств является возможной с помощью стандартной КМОП-технологии. В случае технологии с n- или соответственно p-ванной следует учитывать, что потенциал подложки должен лежать на самом низком (самом отрицательном) или соответственно самом высоком (самом положительном) напряжении. Для случаев, когда первый низкий потенциал является меньше, чем второй низкий потенциал, и предусмотрена n-ванна, или соответственно когда первый высокий потенциал является больше второго высокого потенциала и предусмотрена p-ванна, это означает, что n-канальный или соответственно p-канальный транзистор в логической части полупроводниковой интегральной схемы (которая снабжена первым и вторым низким потенциалом) нагружены напряжением смещения подложки. С помощью так называемой техники "Triple-Well" можно избежать этого напряжения смещения подложки в логической части. В случае p-подложки, как это представлено на фиг. 4, первый и третий n-канальный транзистор реализуют в изолированной p-ванне, так что потенциал подложки для логических транзисторов может лежать на втором низком потенциале, то есть обычно на потенциале корпуса. В случае n-подложки соответственно первый и второй p-канальный транзистор должны располагаться в изолированной n-ванне.

Для включения высоких положительных или отрицательных напряжений на выходном выводе (А) устройства первый р-канальный транзистор (Р1) и первый n-канальный транзистор (N1) расположены последовательно между выводами (VH1, VL1) для этих обоих напряжений. Затворы обоих транзисторов через нагрузочные участки транзисторов соответственно другого типа (N2, P3) соединены с первым и третьим входным выводом (Е1, Е3). Затворы этих транзисторов соединены с вторым или соответственно четвертым входным выводом (Е2, Е3). Первый р-канальный транзистор и первый n-канальный транзистор (Р1, N1) являются блокируемыми через соответственно включенные между выводами затворов и выводами для высокого положительного или соответственно высокого отрицательного потенциала (VН1, VL1) нагрузочные участки транзисторов соответственно одинакового типа (Р2, N3), затворы которых соединены с выходным выводом (А). В зависимости от потенциала на входных выводах к выходному выводу (А) может подключаться или высокий положительный или соответственно высокий отрицательный потенциал. 5 з.п. ф-лы, 4 ил.

| US 5266848, A, 30.11.93 | |||

| Соклоф С., Аналоговые интегральные схемы | |||

| - М.: Мир, 1988, с.455, рис.6.21 а | |||

| Способ химического травления нержавеющей и жароупорной стали | 1949 |

|

SU82208A1 |

| US 4568842 A, 04.02.86. | |||

Авторы

Даты

1999-03-20—Публикация

1995-12-15—Подача