Если техника эмиттерносвязанной логики отличается такими характеристиками, как высокая скорость работы, (средняя-) высокая степень интеграции и (средняя-) высокая мощность потерь, то техника полевых транзисторов характеризуется - при, конечно, лишь средней скорости работы - весьма высокой степенью интеграции и весьма низкими величинами мощности потерь. Эти последние свойства обусловили попытки проникновения с интегральными схемами техники полевых транзисторов также в диапазоны быстродействия, которые сохранялись до настоящего времени за биполярной техникой.

Для устройства связи широкополосных сигналов с матрицей точек связи, которая содержит образованные двумя сигнальными проводниками входные линии матрицы, которые, с одной стороны, подключены к двум дифференциальным (дополнительным) выходам входной схемы цифровых сигналов и, с другой стороны, могут соединяться через точки связи с также образованными двумя сигнальными проводниками выходными линиями матрицы, которые подведены с их обоими сигнальными проводниками к обоим сигнальным входам образованной дифференциальным усилителем выходной усилительной схемы, в этой взаимосвязи (Европейская заявка N 0264046) известна выполненная в технике полевых транзисторов матрица точек связи с предусмотренными в точках связи, образованными двумя нагружаемыми на управляющих электродах сигналом переключения или блокировки переключательными транзисторами парами элементов связи, переключательные транзисторы которых подключены одним своим главным электродом к одному или другому сигнальному проводнику соответствующей выходной линии матрицы, которая в свою очередь оснащена выходным дифференциальным усилителем с триггерной характеристикой опрокидывания, причем пары элементов связи содержат каждая два образующих одним переключателем транзисторов каждый последовательную схему добавочных транзистора, которые управляющим электродом каждый подключены к одному или другому сигнальному проводнику соответствующей входной линии матрицы, и те или иные, обращенные от последовательной схемы главные электроды которых соединены через считывающий транзистор с одним выводом (массой) источника рабочего напряжения, с другим выводом которого соединен каждый сигнальный проводник той или иной выходной линии матрицы через транзистор предварительного заряда, и причем транзистор предварительного заряда и считывающий транзистор встречно относительно друг друга нагружаются на своих управляющих электродах подразделяющими временной интервал переключениями двоичных разрядов на фазу предварительного заряда и саму фазу переключения тактовыми импульсами управления полем связи, в результате чего в течение каждой предварительной фазы при запертом считывающем транзисторе оба сигнальных проводника выходной линии матрицы заряжаются через тот или иной транзистор предварительного заряда по меньшей мере приблизительно до потенциала, который действует на названном другом выводе источника рабочего напряжения.

Это известное устройство коммутации широкополосных сигналов обуславливает дополнительно к преимуществам, которые связаны с построенной по технике полевых транзисторов матрицей точек связи, достижение дополнительного преимущества, заключающегося в том, что, с одной стороны, - при запертой точке связи - также и без принятия дополнительных мер по демпфированию через точку связи к выходу матрицы не поступает никаких мешающих сигналов, и что, с другой стороны, - при проводящей точке связи - происходящие при самом переключении двоичных разрядов в случае необходимости перезаряды выходной линии матрицы выполняются всегда исходя из соответствующего одному состоянию сигнала рабочего потенциала лишь в одном направлении перезаряда и, следовательно, уже с незначительным (соседним с превышением одного этого значения рабочего потенциала, соответствующим порогу, соответствующему точке опрокидывания дифференциального усилителя) перезарядом - и, следовательно, с соответствующим быстродействием - связан однозначный переход возникающего на выходе устройства связи, переключенного цифрового сигнала из одного состояния сигнала в другое.

В случае такого устройства коммутации широкополосных сигналов дальнейшее повышение скорости работы может быть достигнуто за счет того, что оба транзистора предварительного заряда соединены своими, обращенными к той или иной выходной линии матрицы главными электродами между собой с помощью поперечного транзистора, управляющий электрод которого соединен с управляющими электродами транзисторов предварительного заряда (патент ФРГ N 38194910); в совокупности с преимуществом, выраженным в ускорении предварительного заряда выходных линий матрицы, это обуславливает достижение следующего преимущества, которое выражено в заблаговременном симметричном выравнивании потенциала выходных линий матрицы, в результате чего соответственно заблаговременно задаются исходные условия для надежного усиления с помощью последующего дифференциального усилителя.

Следующее повышение скорости работы устройства коммутации широкополосных сигналов может быть достигнуто в том случае, если рядом с индивидуальным по отношению ко входной линии матрицы считывающим транзистором предусмотрен индивидуальный по отношению ко входной линии матрицы транзистор предварительного заряда или, в качестве альтернативы к указанному, рядом с индивидуальным по отношению к выходной линии матрицы считывающим транзистором предусмотрен индивидуальный в отношении выходной линии матрицы транзистор предварительного заряда (патент ФРГ N 38194910).

Относящиеся к требуемой мощности потерь и скорости работы, достижимые преимущества такого известного устройства связи широкополосных сигналов, которое содержит образованные двумя сигнальными проводниками входные линии матрицы, сопряжены с соответствующей потребностью в площади для таких двух сигнальных проводников входных линий матрицы. В отличие от этого изобретение показывает путь, позволяющий существенно уменьшить эту потребность в площади.

Изобретение касается устройства коммутации широкополосных сигналов с матрицей точек связи в технике полевых транзисторов, входные линии матрицы которой через образованные парами элементов связи точки связи могут соединяться с образованными двумя сигнальными проводниками выходными линиями матрицы, к обоим сигнальным проводникам которых могут подключаться оба сигнальных входа образованной дифференциальным усилителем с характеристикой опрокидывания выходной усилительной схемы, причем пары элементов связи образованы каждая двумя нагруженными на управляющем электроде сигналом переключения или блокировки и подключенными главным электродом к одному или другому сигнальному проводнику соответствующей выходной линии матрицы переключательными транзисторами и двумя, образующими каждый одним переключательным транзистором одну последовательную схему добавочными транзисторами, которые подключены каждый управляющим электродом к одному сигнальному проводнику соответствующей входной линии матрицы, и тот или иной, обращенный от последовательной схемы главный электрод которых соединен через индивидуальный по отношению к элементу связи, входной линии матрицы или выходной линии матрицы считывающий транзистор с одним выводом источника рабочего напряжения, с другим выводом которого каждый сигнальный проводник той или иной выходной линии матрицы соединен через транзистор предварительного заряда, причем транзисторы предварительного заряда и считывающий транзистор нагружаются встречно по отношению друг к другу на их управляющим временной интервал переключения двоичных разрядов на фазу предварительного заряда и саму фазу переключения тактом управления полем связи, в результате чего в течение каждой предварительной фазы при запертом считывающем транзисторе оба сигнальных проводника выходной линии матрицы заряжаются через тот или иной транзистор предварительного заряда по меньшей мере приблизительно до потенциала, действующего на другом названном выводе источника рабочего напряжения, и причем оба транзистора предварительного заряда соединены своими, обращенными к той или иной выходной линии матрицы главными электродами между собой через поперечный транзистор, управляющий электрод которого соединен с управляющими электродами транзисторов предварительного заряда; это устройство связи широкополосных сигналов отличается в соответствии с изобретением тем, что пары элементов связи содержат каждая два добавочных транзистора с различными типами канала, которые своими управляющими электродами подключены к одному и тому же сигнальному проводнику соответствующей входной линии матрицы.

Изобретение обеспечивает достижение того преимущества, что для одной входной линии матрицы необходим лишь один единственный сигнальный проводник - при соответственно уменьшенной потребности в площади, - при сохранении, однако, прочих особенностей и предпочтительных свойств названного выше известного устройства связи широкополосных сигналов.

Еще более явное уменьшение необходимой площади достигается в том случае, если при следующем исполнении изобретения пары элементов связи содержат два переключательных транзистора с различными типами канала, которые одним добавочным транзистором одного и того же типа канала образуют одну последовательную схему.

Для того чтобы при этом избежать несимметричной нагрузки на оба сигнальных проводника выходных линий матрицы и, следовательно, несимметричной нагрузки обоих входов последующего дифференциального усилителя, в соответствии с изобретением устройство связи широкополосных сигналов может быть выполнено так, что только при одной части ведущих к одной и той же выходной линии матрицы пар элементов связи транзисторная последовательная схема одного типа канала соединена с одним сигнальным проводником, а транзисторная последовательная схема другого типа канала - с другим сигнальным проводником выходной линии матрицы, в то время как при другой части ведущих к соответствующей выходной линии матрицы пар элементов связи транзисторная последовательная схема названного другого типа канала соединена с названным одним сигнальным проводником, а транзисторная последовательная схема названного одного типа канала соединена с названным другим сигнальным проводником выходной линии матрицы; это может осуществляться, в частности, таким образом, что соединенные тем или иным образом с сигнальными проводниками соответствующей выходной матрицы пары элементов связи следуют друг за другом с чередованием в соответствующем ряду матрицы.

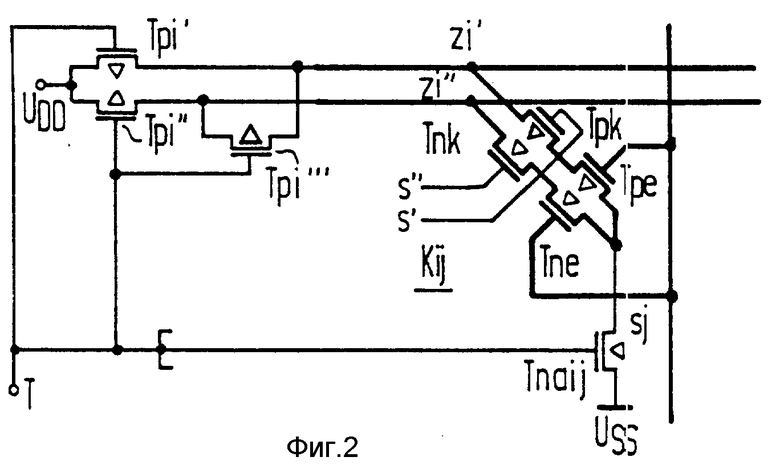

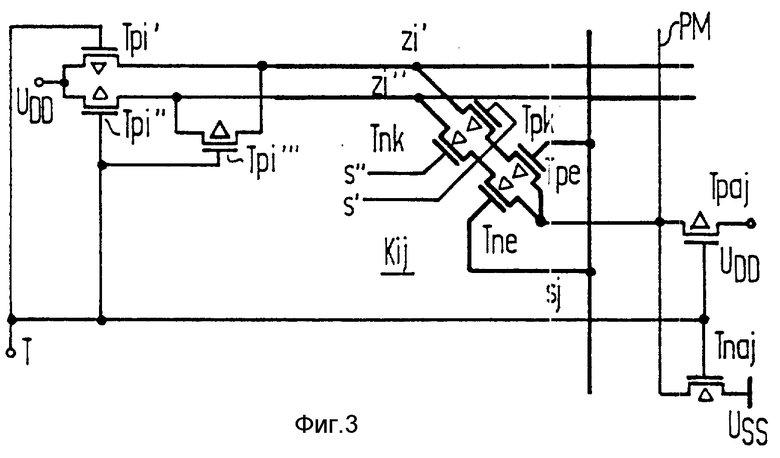

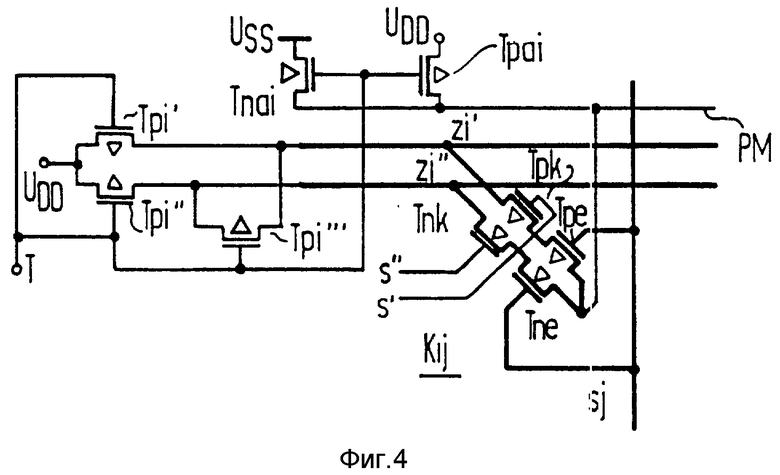

Дальнейшие особенности изобретения вытекают из последующего, более подробного пояснения изобретения на основании фигур, на которых показано: фиг.1 - схема соответствующего изобретению устройства коммутации широкополосных сигналов; фиг. 2, 3 и 4 - примеры технической реализации ее элементов связи; фиг. 5 - характеристики сигналов.

На фиг. 1 схематически и в необходимом для понимания сути изобретения объеме изображено устройство связи широкополосных сигналов, на ведущих к линиям sl...sj...Sn столбцов одной матрицы точек связи входах el...ej...en которого предусмотрены входные схемы El...Ej...En цифровых сигналов, достигнутые линиями Zl...Zj...Zn строк матрицы точек связи выходы al...ai...am снабжены выходами усилительными схемами Al...Ai...Am. Матрицы точек связи содержит точки KPll...KPij...KPmn связи, элементы связи которых, как это поясняется более подробно в дальнейшем применительно к точке KPij связи для пары Kij элементов связи, могут управляться на управляющих входах S', S'' (не изображенным на фигуре) элементом для декодирования адреса или удерживающим элементом памяти, что не нуждается в дальнейшем пояснении, поскольку такого рода способы управления элементами связи являются в целом известными и соответствующие пояснения уже приведены в других публикациях (Европейский патент N 0262479).

Образованные с помощью лишь одного сигнального проводника входные линии матрицы (линии столбцов) соединены через образованные парами (Kij применительно к точке KPij связи на фиг. 1) элементов связи точки KPll,...,KPil,... , KPnm связи с выходными линиями матрицы (линиями строк), которые образованы двумя сигнальными проводниками Zl', Zl'',..., Zi', Zi'',...; Zm', Zm'' и ведут вместе с ними к обоим сигнальным входам образованной дифференциальным усилителем с характеристикой опрокидывания выходной усилительной схемы Al,.. .Ai,...: Am.

Такой дифференциальный усилитель с характеристикой опрокидывания может быть реализован на базе триггера, как это в принципе известно из: (а) IEEE Journal of Solide-State Circuits, окт. 1973, стр. 319-323, фиг. 6 и в различных модификациях, например, из (b)выложенной заявки ФРГ N 2422136, фиг. 3, (16') и из (c) заявки ФРГ N 2608119, фиг. 5, причем предусмотренный там симметрирующий транзистор (в (a) и (b)), равно как и предусмотренные там транзисторы предварительного заряда ( в (b)) или нагрузочные транзисторы (в (b)) выполнены в целесообразном случае в виде p-канального транзистора; служащая возможность реализации известна из Европейской заявки N 0264046, фиг. 5.

Фиг. 2, 3 и 4 поясняют, каким образом могут быть технически реализованы пары . . . Kij... элементов связи. Пары...Kij...элементов связи образованы двумя нагружаемыми на управляющем электроде сигналом переключения или сигналом блокировки и подключенными главным электродом к одному или другому сигнальному проводнику Zi', Zi'' соответствующей выходной линии матрицы переключательными транзисторами Tpk, Tnk и двумя образующими с одним переключательным транзистором Tpk или Tnk последовательную схему добавочными транзисторами Tpe и Tne различного типа канала, которые подключены управляющим электродом к (единственному) сигнальному проводнику sj соответствующей входной линии матрицы (линии столбцов)...Sj...; если при этом, как это видно из фиг. 2, фиг. 3 и фиг. 4, также и оба переключательных транзистора Tpk, Tnk являются транзисторами с различным типом канала, то в этом случае один переключательный транзистор Tpk (или Tnk) и один добавочный транзистор Tpe (или Tne) того же типа канала образуют последовательную схему. Своими обращенными от последовательной схемы главными электродами добавочные транзисторы Tpe и Tne соединены через считывающий транзистор Tha (а именно, Tnaij на фиг. 2 или Tnaj на фиг. 3 или Tnai на фиг. 4) с одним выводом Uss (массой) источника рабочего напряжения. С другим присоединением UDD источника рабочего напряжения соединены оба сигнальных проводника (Zi', Zi'') той или иной выходной линии матрицы (линии строк)...Zi... через транзистор Tp или Tp'' предварительного заряда; на своих обращенных к той или иной выходной линии (Zi', Zi'') матрицы главных электродах оба транзистора Tpi', Tpi'' предварительного заряда соединены между собой через поперечный транзистор Tpi'', управляющий электрод которого соединен с управляющими электродами транзисторов Tpi', Tpi'' предварительного заряда.

Как видно также из фиг. 2, может быть предусмотрен индивидуальный в отношении пары элементов связи считывающий транзистор Tnaij; альтернативно к этому, как показывает фиг. 3, для всех подключенных к одной и той же входной линии (линии столбцов). ..Sj...матрицы пар элементов связи может быть предусмотрен общий и, следовательно, индивидуальный для входной линии матрицы считывающий транзистор (Tnaj на фиг. 3), или - как показано на фиг. 4 - может быть предусмотрен общий для всех подключенных к одной и той же выходной линии (линии строк). . .Zi...матрицы пар элементов связи и, следовательно, индивидуальный для выходной линии матрицы считывающий транзистор (Tnai на фиг. 4). При этом, как показано на фиг. 3, наряду с индивидуальным для входной линии матрицы считывающим транзистором Tnaj может быть предусмотрен индивидуальный для входной линии матрицы транзистор Tpaj предварительного заряда, и - как видно из изображенного на фиг. 4 - наряду с индивидуальным для выходной линии матрицы считывающим транзистором Tnai может быть предусмотрен индивидуальный для выходной линии матрицы транзистор Tpai предварительного заряда.

Как показано также на фиг. 2-4, в выполненной в соответствии с техникой КМОП матрице точек связи переключательный транзистор Tnk и добавочный транзистор The одной последовательной схемы Tne - Tnk, равно как и соответствующий считывающий транзистор Tna могут представлять собой n-канальные транзисторы, в то время как переключательный транзистор Tpk и добавочный транзистор Tpe другой последовательной схемы Tpe-Tpk, равно как и транзисторы Tpi предварительного заряда, могут представлять собой p-канальные транзисторы.

Поскольку p-канальные транзисторы (при той же эффективности по току) должны быть выполнены с шириной, в два раза большей по сравнению с n - канальными транзисторами, во избежание вытекающей из этого несимметричной нагрузки обоих сигнальных проводников Zi', Zi'' одной линии матрицы в случае представленной на фиг. 2-4 реализации пар элементов связи с двумя транзисторными последовательными схемами с различными типами каналов целесообразным является случай, когда лишь при одной части ведущих к одной и той же выходной линии матрицы пар элементов связи транзисторная последовательная схема (Tpe, Tpk) одного типа канала соединена с одним сигнальным проводником (Zi), а транзисторная последовательная схема (Tne, Tnk) другого типа канала соединена с другим сигнальным проводником (Zi'') выходной линии матрицы, в то время как при другой части ведущих к соответствующей выходной линии матрицы пар элементов связи транзисторная последовательная схема (Tne, Tnk) названного другого типа канала соединена с названным одним сигнальным проводником (Zi') и последовательная транзисторная схема (Tpe, Tpk) названного одного типа канала соединена с названным другим сигнальным проводником (Zi'') выходной линии матрицы; в частности, при этом соединенные тем или иным образом с сигнальными проводниками соответствующей выходной линии матрицы пары элементов связи могут следовать одна за другой с чередованием в соответствующем ряду матрицы.

Такие расположенные один за другим с чередованием элементы связи указаны также на фиг. 1: применительно к точке KPij связи выход p p-канальной транзисторной последовательной схемы (Tpe-Tpk на фиг. 2) подключен к одному сигнальному проводнику Zi' соответствующей выходной линии матрицы, а выход n n- канальной транзисторной последовательной схемы (Tne-Tnk на фиг. 2) подключен к другому сигнальному проводнику Zi''. На фиг. 1 в этом случае указано, что соответствующим образом также и прочие, подключенные ко входной линии Sj матрицы точки связи подключены к прочим выходным линиям матрицы. Одновременно на фиг. 1 указано, что при подключенных ко входной линии Sn матрицы точках связи выходы элементов связи подключены противоположным образом к обоим сигнальным проводникам той или иной выходной линии матрицы: как более подробно показано на фиг. 1 для точки KPin связи, в этом столбце матрицы выход n (см. также фиг. 2) n - канальной транзисторной последовательной схемы той или иной пары элементов связи (например, Kin) соединен с одним сигнальным проводником (Zi'' на фиг. 1), в то время как выход p (см. также фиг. 2) p-канальной транзисторной последовательной схемы той или иной пары элементов связи (например, Kin) соединен с другим сигнальным проводником (Zm'' на фиг. 1) той или иной выходной линии матрицы. Соответствующим образом элементы связи всех ведущих от различных входных линий Sl...Sn (на фиг. 1) матрицы к одной и той же выходной линии (например, Zi', Zi'') матрицы точек связи могут быть подключены своей n - канальной ветвью с чередованием от столбца к столбцу матрицы к одному сигнальному проводнику (Zi') и другому сигнальному проводнику (Zi'') соответствующей выходной линии матрицы и могут быть подключены своей p-канальной ветвью чередующимся образом к этому другому сигнальному проводнику (Zi'') и названному выше одному сигнальному проводнику (Zi') соответствующей выходной линии матрицы.

На фиг. 2-4 дополнительно показано, что транзисторы Tpi предварительного заряда и считывающие транзисторы Tha встречно по отношению друг к другу нагружаются на своих управляющих электродах тактом T, подразделяющим временной интервал переключения двоичных разрядов изображенным на фиг. 5, внизу, образом на предварительную фазу pV и основную фазу ph, как это показано на фиг. 5 в строке T.

В течение предварительной фазы p (см. фиг. 5, нижнюю часть) оба сигнальных проводника (Zi', Zi'') выходных линий ... Zi... матрицы (линий строк) заряжаются через тот или иной транзистор (Tpi' или Tpi'' на фиг. 2-4) по меньшей мере приблизительно до рабочего потенциала UDD, для чего образованные в случае примера p-канальными транзисторами транзисторы Tpi, Tpi'' предварительного заряда отпираются тактовым сигналом T "Low" и переводятся в проводящее состояние (см. фиг. 5, строка T).

При этом при поступлении спадающего фронта тактового сигнала T одновременно расположенный между обоими сигнальными проводниками Zi', Zi'' поперечный транзистор Tpi''' также переводится в проводящее состояние, в результате чего возникает короткое замыкание между обоими сигнальными проводниками Zi', Zi'', на основании которого к началу предварительной фазы весьма быстро (момент tl времени на фиг. 5, строка Zi) осуществляется компенсация потенциалов обоих сигнальных проводников Zi', Zi'', после этого оба (теперь выравненных по потенциалу) сигнальных проводника Zi', Z'' заряжаются через оба транзистора Tpi, Tpi'' предварительного заряда до рабочего потенциала UDD, причем длительность заряда сокращается в общей сложности за счет того, что после осуществленного с помощью поперечного транзистора Tpi''' выравнивая потенциала оба транзистора Tpi, Tpi'' вовлекаются в процесс заряда.

Одновременно в деблокированием транзисторов Tpi, Tpi'' предварительного заряда и поперечного транзистора Tpi''' образованные n - канальными транзисторами считывающие транзисторы Tna (Tnaj на фиг. 2, Tnaj на фиг. 3, Tnai на фиг. 4) управляются в случае настоящего примера тем же тактовым сигналом T "Low" в противоположном смысле, то есть запираются, в результате чего заряд обоих сигнальных проводников (Zi', Zi'') выходных линий (линий строк). . . Zi. .. матрицы может осуществляться независимо от управления работой тех или иных переключательных транзисторов Tpk, Tnk (на фиг. 2-4) и тех или иных добавочных транзисторов Tpe, Tne (на фиг. 2-4) отдельных пар...Kij...элементов связи. В той или иной входной линии (линии столбцов)...Sj....матрицы может создаваться (или сохраняться) при этом уже соответствующий в случае необходимости подлежащему переключению двоичному разряду потенциал, как это показывает строка Sj на фиг. 5.

Если наряду с индивидуальным для входной линии матрицы считывающим транзистором Tnaj предусмотрен индивидуальный для входной линии матрицы транзистор Tpaj предварительного заряда, как это показано на фиг. 3, или если наряду с индивидуальным для выходной линии матрицы считывающим транзистором Tnaj предусмотрен индивидуальный для выходной линии матрицы транзистор Tpai предварительного заряда, как это показано на фиг. 4, то в этом случае в течение предварительной фазы p через этот транзистор (Tpaj на фиг. 3; Tpai на фиг. 4) осуществляется заряд линии PM псевдомассы, в результате чего та или иная пара...Kij...элементов связи существенно разгружается. Это, в частности, при наличии обширных матриц точек связи с большим количеством подключенных к линии PM псевдомассы пар...Kij элементов связи, ведет в существенному сокращению времени заряда, которое, в свою очередь, способствует соответствующему повышению скорости работы.

На основании обеспеченного поперечным транзистором Tpi''' равенства потенциалов обоих сигнальных проводников Zi', Zi'' исходные условия для надежного усиления дифференциальным усилителем Ai (на фиг. 1) создаются соответственно заблаговременно, в результате чего уже к соответственно раннему моменту времени может использоваться последующая основная фаза ph (см. фиг. 5, нижняя часть). В течение этой основной фазы ph (см. нижнюю часть фиг. 5) в случае данного примера в результате поступления тактового сигнала T "HIGH" (см. фиг. 5, строка T) транзисторы Tpi', Tpi'' предварительного заряда и поперечный транзистор Tpi''' (на фиг. 2-4) запираются и одновременно осуществляются деблокирование считывающих транзисторов Tna (Tnaij на фиг. 2, Tnaj на фиг. 3, Tnai на фиг. 4). Если теперь в одной паре...Kij...элементов связи ее переключательные транзисторы Tpk, Tnk (на фиг. 2-4) находятся в проводящем состоянии вследствие приложенного к управляющему входу S'переключательного сигнала (в случае данного примера переключательного сигнала "HIGH") (см. фиг. 5, строка S) и если точка связи находится в результате этого в состоянии переключения, то в этом случае в зависимости от соответствующего подлежащему переключению двоичному разряду, действующего на соответствующей входной линии матрицы (линии столбцов)...Sj...состояния сигнальные проводники Zi, Zi'' соединенной с этой входной линией (линией столбцов). . . Sj. ..матрицы через соответствующий элемент связи...Kij...выходной линии (линии строк)...Zi...матрицы разряжаются или остаются на величине потенциала UDD, действовавшего в течение предварительной фазы.

Если в соответствующей входной линии (линии столбцов) Sj матрицы действует состояние сигнала "Low" и в соответствии с этим n - канальный добавочный транзистор Tne (на фиг. 2-4) соответствующей пары Kij элементов связи является запертым, то в этом случае соответствующий сигнальный проводник Zi'' выходной линии (линии строк) Zi матрицы не разряжается через соответствующий элемент связи этой пары Kij элементов связи, а сохраняет состояние потенциала UDD, если ни одна другая, ведущая к этой выходной линии (линии столбцов) Zi матрицы точка связи не находится в состоянии переключения.

Одновременно добавочный транзистор Tpe (на фиг. 2-4) рассмотренной пары Kij элементов связи, в также переключательный транзистор Tpk и соответствующий считывающий транзистор Tna переводятся в проводящее состояние, в результате чего приданный сигнальный проводник Zi' выходной линии (линии строк) Zi матрицы разряжается через этот элемент связи пары Kij элементов связи и переходит к потенциалу Uss.

Если, напротив, в только что рассмотренной входной линии Sj матрицы действует состояние сигнала "High" и в соответствии с этим n - канальный добавочный транзистор Tne (на фиг. 2-4) соответствующей пары Kij элементов связи находится в проводящем состоянии, то соответствующий сигнальный проводник Zi'' выходной линии (линии строк) Zi матрицы разряжается через соответствующий элемент связи этой пары Kij элементов связи и приводится к потенциалу Uss.

Одновременно добавочный транзистор Tpe (на фиг. 2-4) рассмотренной пары Kij элементов связи находится в непроводящем состоянии, так что приданный сигнальный проводник Zi' выходной линии (линии строк) матрицы не разряжается через этот элемент связи пары Kij элементов связи, а сохраняет состояние потенциала UDD, если ни одна другая, ведущая к этой выходной линии (линии строк) Zi точка связи не находится в состоянии переключения.

В случае описанных выше на основании фиг. 2-4 примеров исполнения транзисторы (Tpi', Tpi'') предварительного заряда образованы p-канальными транзисторами, причем эти p-канальные транзисторы )Tpi) предварительного заряда и образованные n - канальными транзисторами считывающие транзисторы (Tna) в результате различных типов канала управляются встречно по отношению друг к другу одним и тем же сигналом (T). В отличие от этого возможен также случай, когда транзисторы предварительного заряда реализуются на базе n - канальных транзисторов, в результате чего - если также переключательные транзисторы (Tnk), добавочные транзисторы (Tne) и считывающие транзисторы (Tna) представляют собой n - канальные транзисторы - используются только транзисторы одного и того же типа канала; с тем, чтобы в этом случае обеспечить возможность взаимно встречного управления транзисторами предварительного заряда и считывающими транзисторами поступающим на их управляющие электроды управляющим тактовым сигналом, тактовый управляющий сигнал (T) поля связи должен подводиться к считывающим транзисторам (Tna) - в аналогии к описанным на основании фиг. 2-4 примерам исполнения - непосредственно, а к (n - канальным) транзисторам предварительного заряда должен подводиться, напротив, инвертированный управляющий тактовый сигнал поля связи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2103832C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2103831C1 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1838887A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

В матрице точек связи, в которой входные линии матрицы через пары элементов связи ведут к содержащим два сигнальных проводника выходным линиям матрицы с подключенными к ним сигнальными входами дифференциального усилителя с характеристикой опрокидывания и в которой оба сигнальных проводника каждой выходной линии матрицы через транзистор предварительного заряда могут соединяться с источником рабочего потенциала, пары элементов связи содержат два добавочных транзистора с различными типами канала, которые своим управляющим электродом подключены к единственному сигнальному проводнику соответствующей входной линии матрицы и которые образуют с одним переключательным транзистором, предпочтительно с тем же типом канала, последовательную схему. Выходные клеммы поочередно следующих элементов связи одной выходной линии матрицы подключены к ее сигнальным проводникам. 6 з.п.ф-лы, 5 ил.

| EP, патент, 0264046, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-02-20—Публикация

1990-03-21—Подача