Изобретение относится к технике связи, в частности к устройствам коммутации, выполненным в виде матриц на полевых транзисторах.

Известна (из Европейской заявки 0 264 046) выполненная на основе техники полевых транзисторов и состоящая из точек связи матрица с парами элементов связи, предусмотренных в точках связи и образованных двумя переключающими транзисторами, управляющие электроды которых нагружены сигналом для транзитного переключения или запирающим сигналом.

Управляющие электроды включающих транзисторов этих точек подключены к тому или другому сигнальному проводу соответствующей выходной шины матрицы, которая, в свою очередь, снабжена выходным дифференциальным усилителем с характеристикой опрокидывания, при этом пары элементов связи имеют транзисторы предварительного включения, образующие с переключающим транзистором последовательную цепь, причем управляющие электроды транзисторов предварительного включения подсоединены к тому или другому сигнальному проводу соответствующей выходной шины матрицы, а их главный электрод, обращенный в противоположную от последовательной цепи сторону, соединен через следующий транзистор с одним полюсом (масса) источника рабочего напряжения, а с другим полюсом источника соединен через транзистор предварительного заряда соответствующий провод соответствующей выходной матрицы, и при этом управляющие электроды транзисторов предварительного заряда и считывающего транзистора нагружены тактовым сигналом, который управляет полем связи и разделяет период времени подключения бита на предварительную фазу и собственно фазу переключения, вследствие чего в каждой предварительной фазе при запертом считывающем транзисторе оба сигнальных провода выходной шины матрицы заряжаются через соответствующий транзистор предварительного заряда приблизительного до потенциала, имеющегося на другом, уже названном, полюсе источника рабочего напряжения.

Достигаемый технический результат - уменьшение габаритов и снижение потребляемой мощности.

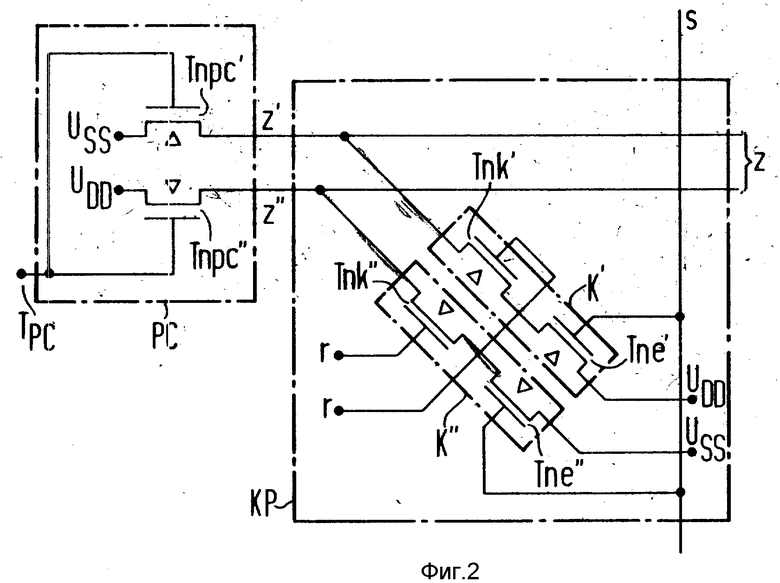

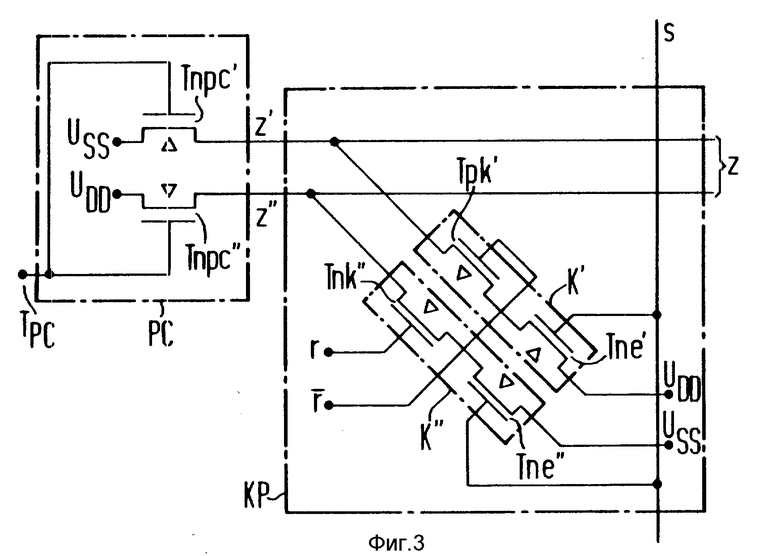

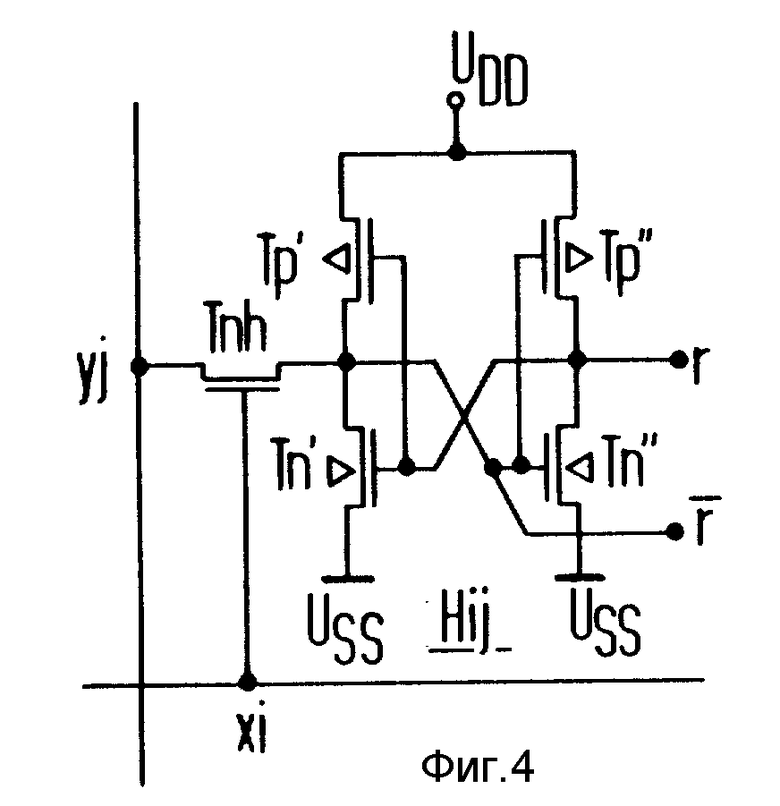

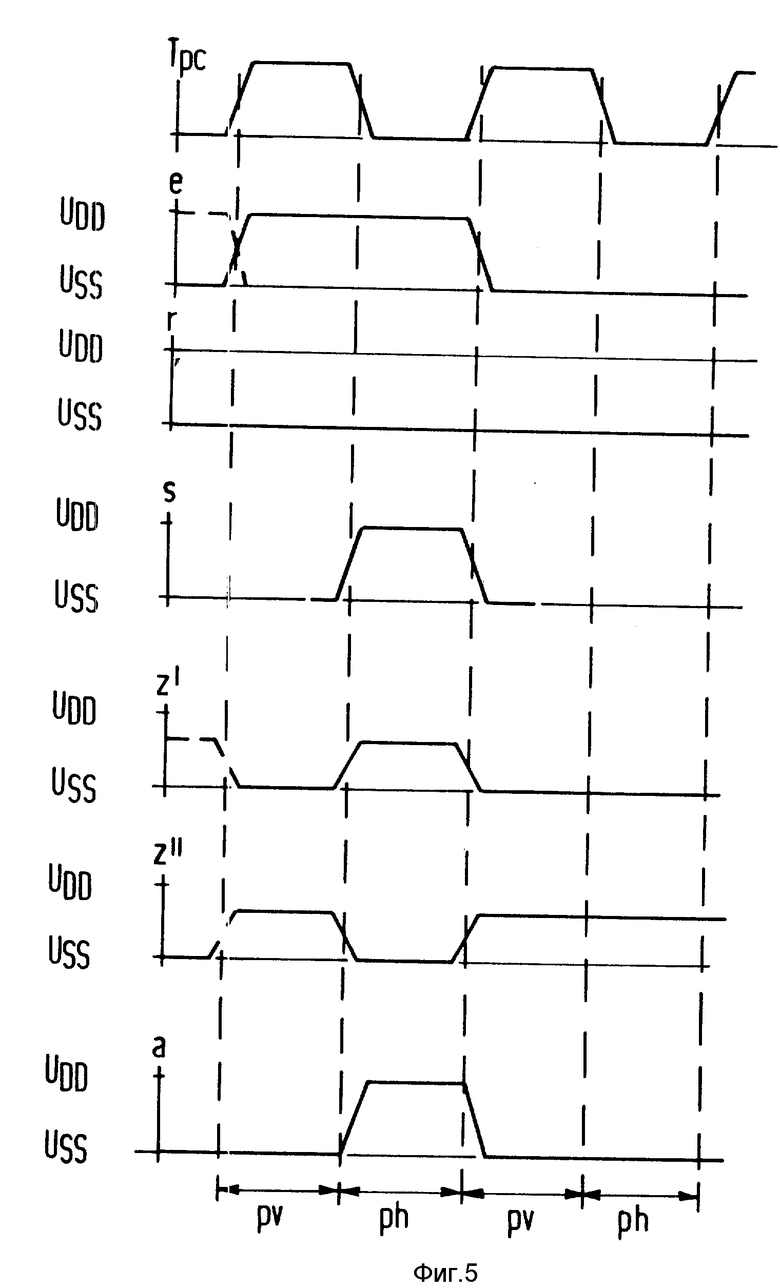

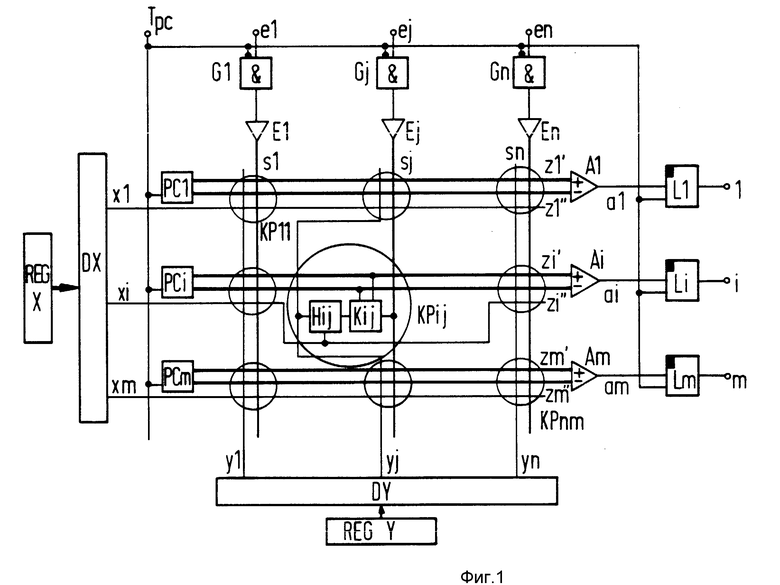

На фиг. 1 представлена структурная электрическая схема устройства связи для широкополосных сигналов согласно изобретению; на фиг. 2 и 3 - примеры схематического выполнения точек связи; на фиг. 4 - пример технической реализации запоминающей ячейки с удержанием.

На фиг. 1 для лучшего понимания изобретения схематически показано устройство связи широкополосных сигналов, на входах которого, снабженных в данном примере выходными задающими схемами E1...En и ведущих к шинам выбора столбца Se...Sn (выходные шины матрицы), предусмотрена логическая схема Ge-Gn. Кроме того, выходы Ae...An, проходящие к двойным шинам сигналов переключения строк (выходные шины матрицы)  , снабжены выходными схемами опроса Al... Am, которые имеют, смотря по обстоятельствам, дифференциальные входные ступени. Выходы Al-Am проходят к индивидуальному для каждой строки запоминающему устройству задержки Le-Lm (Latch), к которым подводится тактовый сигнал Трс. Запоминающие устройства с удержанием уже достаточно известны и поэтому в данном случае подробнее не поясняются. Логическая схема Ge-Gn со стороны входа в матрицу может представлять собой, как показано на фиг. 1, логическую схему, реализующую U1 - функцию, и к которой подается через инвертирующий вход тактовый сигнал Трс, который управляет описываемыми ниже схемами предварительного заряда PCc - PCm, индивидуальными для каждой строки.

, снабжены выходными схемами опроса Al... Am, которые имеют, смотря по обстоятельствам, дифференциальные входные ступени. Выходы Al-Am проходят к индивидуальному для каждой строки запоминающему устройству задержки Le-Lm (Latch), к которым подводится тактовый сигнал Трс. Запоминающие устройства с удержанием уже достаточно известны и поэтому в данном случае подробнее не поясняются. Логическая схема Ge-Gn со стороны входа в матрицу может представлять собой, как показано на фиг. 1, логическую схему, реализующую U1 - функцию, и к которой подается через инвертирующий вход тактовый сигнал Трс, который управляет описываемыми ниже схемами предварительного заряда PCc - PCm, индивидуальными для каждой строки.

Матрица имеет точки связи KP11-KPnm, коммутирующий элемент Kij которых, показанный подробно на одной точке Kpij, может управляться ячейкой памяти с удержанием Hij, индивидуальной для каждой точки связи, выход которой ведет к управляющему входу соответствующего элемента связи (Kij у точки связи Kpij).

Запоминающие ячейки с удержанием Hij управляются согласно фиг. 1 посредством двух управляющих дешифраторов строк DX и дешифратора DY через соответствующие управляющие шины X1...Xm I1...In в двух координатах. Для этого оба управляющих дешифратора DX DY, как это показано на фиг. 1, могут быть нагружены от входных регистров RegX RegY адресом строки или столбца точки связи, общим для ряда точек связи матрицы (строки или столбцы), в ответ на который они выдают на управляющую шину управляющий сигнал "I". Встреча управляющего сигнала столбца "I" и управляющего сигнала строк "I" в точке пересечения соответствующего столбца и строки при осуществлении соответствующего соединения вызывает там соответствующую активизацию запоминающей ячейки с удержанием, например, запоминающей ячейки Hij, что управляемый соответствующей запоминающей ячейкой элемент связи, например элемент Kij, становится проводящим.

Чтобы рассматриваемый в данном примере элемент связи при уничтожении соответствующего соединения снова был заперт, управляющий дешифратор DX нагружается снова от входного регистра RegX соответствующим адресом ячейки, вследствие чего дешифратор строк DX выдает снова на свою выходную шину Xi строчный управляющий сигнал "I" и одновременно дешифратор столбцов DX от своего входного регистра нагружается снова свободным адресом или адресом столбца, где имеются невключенные точки связи, вследствие чего он выдает на свою выходную шину Yi сигнал выбора столбца "0". Встреча сигнала выбора строки 1 "I" и сигнала выбора столбца "0" вызывает возврат в исходное положение запоминающей ячейки с удержанием Hij, благодаря чему управляемый этой ячейкой элемент связи Kij запирается.

Запоминающие ячейки с удержанием Hij могут быть выполнены известным образом. Например, запоминающие ячейки с удержанием, показанные схематично на фиг. 4, образованы транзистором с n-каналом Tnh и двумя перекрестными инвертирующими схемами (инвертирующие схемы CMOS  ), при этом инвертирующая схема со стороны входа соединена с соответствующим выходом дешифратора Yi через транзистор Tnh n-типа. Управляющий электрод этого транзистора в свою очередь нагружен выходным сигналом с соответствующего выхода дешифратора Xi, при этом инвертирующая схема

), при этом инвертирующая схема со стороны входа соединена с соответствующим выходом дешифратора Yi через транзистор Tnh n-типа. Управляющий электрод этого транзистора в свою очередь нагружен выходным сигналом с соответствующего выхода дешифратора Xi, при этом инвертирующая схема  со своего выхода выдает сигнал для транзитной передачи или блокирующий сигнал τ, в противоположность этому другая инвертирующая схема

со своего выхода выдает сигнал для транзитной передачи или блокирующий сигнал τ, в противоположность этому другая инвертирующая схема  со своего выхода выдает сигнал для транзитной передачи или запирающий сигнал

со своего выхода выдает сигнал для транзитной передачи или запирающий сигнал  .

.

Выполнение элементов связи K', K'' показано на фиг. 2 и фиг. 3. Сначала рассмотрим элементы связи по фиг. 2. Элементы K', K'', образованные переключающими транзисторами  , главные электроды которых подсоединены к тому или другому проводу Z', Z'' соответствующей шины строчек Z (выходная шина матрицы), а сами транзисторы нагружены сигналом транзитного включения или запирающим сигналом τ, который приложен к управляющему электроду, имеют входной транзистор

, главные электроды которых подсоединены к тому или другому проводу Z', Z'' соответствующей шины строчек Z (выходная шина матрицы), а сами транзисторы нагружены сигналом транзитного включения или запирающим сигналом τ, который приложен к управляющему электроду, имеют входной транзистор  , образующий с переключающим транзистором

, образующий с переключающим транзистором  последовательную цепь, причем управляющий электрод входного транзистора подсоединен к соответствующей шине выбора столбца S (входная ширина матрицы), а главный электрод управляющего транзистора, обращенный в противоположную от последовательной цепи сторону, подсоединен к тому или другому полюсу источника рабочего напряжения UDD-USS. Транзисторы в элементах связи K', K" согласно фиг. 2 относятся к одному и тому же типу с самозакрывающимся n-каналом.

последовательную цепь, причем управляющий электрод входного транзистора подсоединен к соответствующей шине выбора столбца S (входная ширина матрицы), а главный электрод управляющего транзистора, обращенный в противоположную от последовательной цепи сторону, подсоединен к тому или другому полюсу источника рабочего напряжения UDD-USS. Транзисторы в элементах связи K', K" согласно фиг. 2 относятся к одному и тому же типу с самозакрывающимся n-каналом.

Форма выполнения элемента сопряжения K' по фиг. 2 может быть изменена согласно фиг. 3 так, что вместо переключающего транзистора  n-канального типа, который при последовательном соединении со входным транзистором

n-канального типа, который при последовательном соединении со входным транзистором  образует элемент связи, главный электрод которого, обращенный в противоположную от цепи последовательного соединения сторону, соединен с имеющим более высокий потенциал полюсу UDD источника рабочего напряжения UDD-USS. Используют переключающий транзистор

образует элемент связи, главный электрод которого, обращенный в противоположную от цепи последовательного соединения сторону, соединен с имеющим более высокий потенциал полюсу UDD источника рабочего напряжения UDD-USS. Используют переключающий транзистор  p-типа.

p-типа.

Чтобы этот переключающий транзистор  сделать проводящим, необходимо подать инвертированный относительно сигнала τ, необходимого для включения транзистора T и K', сигнал для транзитного соединения

сделать проводящим, необходимо подать инвертированный относительно сигнала τ, необходимого для включения транзистора T и K', сигнал для транзитного соединения  , который снимают в точке соединения транзисторов

, который снимают в точке соединения транзисторов  запоминающей ячейки с удержанием (на фиг. 4). Сигнальные провода Z', Z'' шин выбора строк Z соединены с индивидуальными для каждой строки схемами предварительного заряда PC, через которые сигнальные провода Z', Z'' шин выбора строчек (выходные шины матрицы) заряжаются до потенциала предварительного заряда, расположенного между рабочими потенциалами или до самого рабочего потенциала. UDD-USS источник потенциала предварительного заряда для получения потенциала, расположенного между обоими рабочими потенциалами, получен с помощью обладающего обратной связью КМОП-инвертора, через который в фазе предварительного заряда во время транзитного переключения бита выходные шина матрицы заряжаются приблизительно до потенциала, соответствующего порогу включения инвертора.

запоминающей ячейки с удержанием (на фиг. 4). Сигнальные провода Z', Z'' шин выбора строк Z соединены с индивидуальными для каждой строки схемами предварительного заряда PC, через которые сигнальные провода Z', Z'' шин выбора строчек (выходные шины матрицы) заряжаются до потенциала предварительного заряда, расположенного между рабочими потенциалами или до самого рабочего потенциала. UDD-USS источник потенциала предварительного заряда для получения потенциала, расположенного между обоими рабочими потенциалами, получен с помощью обладающего обратной связью КМОП-инвертора, через который в фазе предварительного заряда во время транзитного переключения бита выходные шина матрицы заряжаются приблизительно до потенциала, соответствующего порогу включения инвертора.

В противоположность этому в примерах выполнения на фиг. 2 и 3 сигнальные провода Z', Z'' шины сигналов переключения строк Z (выходная шина матрицы) через самозапирающийся транзистор предварительного заряда с каналом n-типа соединены с другим полюсом источника рабочего напряжения. Управляющие электроды транзисторов предварительного заряда  соединены с шиной, проводящей тактовый сигнал Tpc.

соединены с шиной, проводящей тактовый сигнал Tpc.

Выходные задающие схемы Al...Am на фиг. 1 могут быть представлены в виде двух дифференциальных усилителей с характеристикой опрокидывания, которые реализуются в так называемой логической триггерной схеме.

Если сигнальные провода Z', Z'' шин сигналов переключения строк Z (выходные шины матрицы) в фазе предварительного заряда PV, как это описано выше, заряжаются приблизительно до другого потенциала источника рабочего напряжения UDD-USS, то в качестве выходного задающего устройства A достаточно использовать дифференциальный усилитель, который может представлять собой операционный усилитель, в частности, выполненный в технике полевых транзисторов.

Выходные задающие схемы Al...Am, представленные на фиг. 1 в виде дифференциальных усилителей, подсоединены своим инвертированным входом (+) к сигнальному проводу, а своим инвертированным входом (-) к сигнальному проводу Z'' соответствующей шины сигналов переключения строк (выходная шина матрицы). При таком способе соединения получают показанное на фиг. 5 в строчке, а фазовое положение сигнала a.

На фиг. 5 показана передача логического сигнала "I" (высокий уровень) и за ним нулевого сигнала (низкий уровень) (сравни строчку e), например, от входа ej (на фиг. 1) к выходу Ai (на фиг. 1) матрицы для двух следующих друг за другом периодов времени транзитной передачи бита с помощью соответствующего тактового сигнала Tpe (строки Tpe на фиг. 5), (например сигнала "Высокого уровня"), подаваемого на управляющие электроды каждого транзистора предварительного заряда Tnpe (по фиг. 2 и 3). Этот сигнал приводит к тому, что в каждой фазе предварительного заряда (на фиг. 5 внизу) в период транзитной передачи бита, который разделен с помощью тактового сигнала Tpe на фазу предварительного заряда рV и последующую главную фазу (на фиг. 5 внизу), каждый транзистор предварительного заряда  открывается, вследствие чего во время предварительного заряда pV сигнальные провода Z', Z'' шин сигналов выбора строк Z (выходные шины матрицы) заряжаются до промежуточного потенциала, расположенного между рабочими потенциалами UDD, USS или до самого рабочего потенциала UDD, USS. Так как в примерах выполнения согласно фиг. 2 и фиг. 3 сигнальные провода Z' соответствующей шины сигналов переключения строк разряжаются до более низкого потенциала (USS, масса) источника рабочего напряжения (UDD-USS) (фиг. 5, строка Z'), а в противоположность этому сигнальные провода соответствующей шины сигналов переключения строк (выходная шина матрицы) заряжаются от высокого потенциала UDD источника рабочего напряжения UDD-USS (ср. фиг. 5, строчка Z''). Благодаря тому, что транзисторы предварительного заряда

открывается, вследствие чего во время предварительного заряда pV сигнальные провода Z', Z'' шин сигналов выбора строк Z (выходные шины матрицы) заряжаются до промежуточного потенциала, расположенного между рабочими потенциалами UDD, USS или до самого рабочего потенциала UDD, USS. Так как в примерах выполнения согласно фиг. 2 и фиг. 3 сигнальные провода Z' соответствующей шины сигналов переключения строк разряжаются до более низкого потенциала (USS, масса) источника рабочего напряжения (UDD-USS) (фиг. 5, строка Z'), а в противоположность этому сигнальные провода соответствующей шины сигналов переключения строк (выходная шина матрицы) заряжаются от высокого потенциала UDD источника рабочего напряжения UDD-USS (ср. фиг. 5, строчка Z''). Благодаря тому, что транзисторы предварительного заряда  работают относительно соответствующего сигнала провода Z'' по так называемой схеме слежения за источником, сигнальные провода Z'' заряжаются до потенциала, который уменьшен относительно высокого потенциала UDD источника рабочего напряжения UDD-USS на величину порогового напряжения между управляющим электродом и главным электродом соответствующего транзистора предварительного заряда

работают относительно соответствующего сигнала провода Z'' по так называемой схеме слежения за источником, сигнальные провода Z'' заряжаются до потенциала, который уменьшен относительно высокого потенциала UDD источника рабочего напряжения UDD-USS на величину порогового напряжения между управляющим электродом и главным электродом соответствующего транзистора предварительного заряда  , который связан с сигнальным проводом Z''.

, который связан с сигнальным проводом Z''.

В следующей за этим главной фазе ph (фиг. 5) внизу транзисторы предварительного заряда  на фиг. 2 и 3 заперты с помощью "Низкого" - тактового сигнала Tpe (фиг. 5, строчка Tpe и одновременно деблокируются вентильные схемы Cl...Cn на фиг. 1, расположенные со стороны входа матрицы). Благодаря этому приложенные к выходным шинам el...en матрицы сигналы транзитно передаются через соответствующие управляющие схемы El...En на соответствующие шины выбора столбца S, выходные шины матрицы (фиг. 5), строчки e, S.

на фиг. 2 и 3 заперты с помощью "Низкого" - тактового сигнала Tpe (фиг. 5, строчка Tpe и одновременно деблокируются вентильные схемы Cl...Cn на фиг. 1, расположенные со стороны входа матрицы). Благодаря этому приложенные к выходным шинам el...en матрицы сигналы транзитно передаются через соответствующие управляющие схемы El...En на соответствующие шины выбора столбца S, выходные шины матрицы (фиг. 5), строчки e, S.

Если шина выбора столбца входная шина матрицы находится в "Низком" - состоянии, то все выходные транзисторы, соединенные через свои управляющие электроды с этой шиной выбора столбца заперты, то в противоположность этому ранее названные транзисторы  ,

,  пeреводятся в открытое положение с помощью сигнала "Высокий" на соответствующей шине выбора столбца S.

пeреводятся в открытое положение с помощью сигнала "Высокий" на соответствующей шине выбора столбца S.

Если точка связи KP находится в состоянии передачи сигнала благодаря приложенному сигналу r, на фиг. 2, сигнал "Высокий" для  на фиг. 3 сигнал "Высокий" для

на фиг. 3 сигнал "Высокий" для  и сигнал "Низкий" для

и сигнал "Низкий" для  , который необходим для перевода в открытое положение транзисторов, и соответствующая шина выбора столбца приводит "Высокий" - сигнал фиг. 5, строчка Z'', то сигнальный провод Z' соответствующей шины сигналов переключения строк Z выходная шина матрицы заряжается от высокого потенциала UDD источника рабочего напряжения UDD-USS (фиг. 5, ячейка Z').

, который необходим для перевода в открытое положение транзисторов, и соответствующая шина выбора столбца приводит "Высокий" - сигнал фиг. 5, строчка Z'', то сигнальный провод Z' соответствующей шины сигналов переключения строк Z выходная шина матрицы заряжается от высокого потенциала UDD источника рабочего напряжения UDD-USS (фиг. 5, ячейка Z').

Благодаря тому, что соответствующие входные транзисторы Tne работают относительно соответствующего сигнального провода Z по схеме слежения за источником, соответствующий сигнальный провод Z заряжается до потенциала, который уменьшен относительно высокого потенциала UDD источника рабочего напряжения на величину порогового напряжения между управляющим электродом и главным электродом транзистора Tne, который обращен к схеме последовательного соединения, состоящей из входного транзистора  и переключающего транзистора

и переключающего транзистора  или τ.

или τ.

На входе выходной управляющей схемы a, которая соединена с соответствующими сигнальными проводами Z', Z'' рассматриваемой шины сигнала переключения строк Z (выходная шина матрицы) происходит изменение полярности разности напряжений с помощью описанной выше перезарядки сигнальных проводов Z', Z''.

Эта разность напряжений усиливается выходной задающей схемой и приводит к крутому изменению сигнала на выходе выходной задающей схемы A (сравн. фиг. 5, ячейка a).

Приложенный к соответствующей шине выбора столбца (входная шина матрицы) сигнал транзитно подается через точку связи KP, деблокированную с помощью переключающих транзисторов (сравн. фиг. 5, строчка a) τ к концу главной фазы ph возникший на выходе a выходной возбуждающей схемы A сигнал "Высокий" (сравн. фиг. 5, строка a) переписывается в соответствующее запоминающее устройство (Latch) со сменой тактового сигнала из "Низкого" состояния в "Высокое" состояние.

Во время следующего периода времени передачи бита может быть передан через рассматриваемую входную шину согласно фиг. 5 только один "Низкий" сигнал. В фазе предварительного заряда pV сначала предварительно заряжаются все сигнальные провода Z', Z'' шин выбора строк Z (выходные шины матрицы). В примыкающей главной фазе ph переключающие транзисторы τ могут снова поставлены в положение транзитной передачи. Так как на входной шине возникает "Низкий" сигнал (сравн. фиг. 5, строчка e) соответствующая шина выбора столбца S также находится в "Нижнем" положении, это приводит к тому, что все связанные с этой шиной выбора столбца входные транзисторы τ остаются запертыми, соответствующие сигнальные провода Z', Z'' шины выбора строки выходная шина матрицы не перезаряжаются и таким образом значение сигнала на этой выходной шине a сохраняется (фиг. 5, строчка a) при предположении, что никакая точка связи KP, связанная с этой шиной выбора строки (выходная шина матрицы) не находится в проводящем состоянии. Поэтому к концу этой главной фазы ph, "Низкий" - сигнал переписывается в соответствующее запоминающее устройство с удержанием (Latch).

Как видно на фиг. 5, строчки Z', Z'', сигнальные провода Z', Z'' шины выбора строки Z выходные шины матрицы работают с меньшим по сравнению с величиной рабочего напряжения размахом сигнала, благодаря чему происходит уменьшение потерь на перезарядку на шинах выбора строки (выходные шины матрицы).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1991 |

|

RU2105431C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2105430C1 |

| ШИРОКОПОЛОСНОЕ УСТРОЙСТВО КОММУТАЦИИ | 1991 |

|

RU2103841C1 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2106755C1 |

| УСТРОЙСТВО СВЯЗИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1990 |

|

RU2013877C1 |

| УСТРОЙСТВО ПРОСТРАНСТВЕННОЙ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1986 |

|

RU2011304C1 |

| Устройство коммутации широкополосных сигналов | 1989 |

|

SU1838888A3 |

| Устройство коммутации широкополосных сигналов | 1987 |

|

SU1738105A3 |

| УСТРОЙСТВО КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1989 |

|

RU2103831C1 |

| СПОСОБ КОММУТАЦИИ ШИРОКОПОЛОСНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 1987 |

|

RU2105428C1 |

Устройство коммутации широкополосных сигналов в матрице связи с точками связи, выполненными в технике полевых транзисторов, в которой входные шины проходят к имеющим два сигнальных провода выходным шинам с подсоединенными там входами сигналов дифференциального усилителя и в которой оба сигнальных провода каждой выходной шины матрицы соединены через транзистор предварительного заряда с полюсом источника рабочего напряжения и сигнальные провода каждой выходной шины матрицы соединены с другим полюсом источника рабочего напряжения через элемент связи, который образован последовательным соединением входного транзистора, управляющий электрод которого соединен с одним сигнальным проводом соответствующей входной шины матрицы, и переключающим транзистором, электрод которого нагружается сигналом транзитной передачи или запирающим сигналом. 4 з.п. ф-лы, 5 ил.

| EP, патент, 0264046, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1998-01-27—Публикация

1990-09-10—Подача