Изобретение относится к радиотехнике и вычислительной технике и предназначено для параметрической оценки закона распределения потоков многопакетных сообщений в средствах многоканальной (спутниковой, радиорелейной, тропосферной) радиосвязи, объединенных в цифровую сеть связи интегрального обслуживания (ЦСИО).

Известно устройство для параметрической оценки закона распределения, содержащее входной усилитель, блок памяти, блок проверки согласия, блок управления и синтезатор функции распределения (см. авт.св. СССР 1024935, G 06 F 15/36, G 06 G 7/52, 1983, бюл.23).

Недостатком данного устройства является низкий уровень быстродействия при его использовании для оценки распределения потоков многопакетных сообщений (МПС) в сетях интегрального обслуживания, обусловленный необходимостью перебора множества М сочетаний параметров распределения потока сообщений, состоящих из множества пакетов.

Известно устройство для параметрической оценки закона распределения потоков сообщений, содержащее входной усилитель, блок вычисления параметров, блок вычисления средних арифметических значений, блок определения типа распределения, вычислитель распределения и блок управления (см. патент РФ 2094844, G 06 F 17/18, 1997, бюл.30).

Однако данное устройство не способно производить оценку закона распределения неоднородных (смешанных) потоков МПС, имеющих место в ЦСИО и обусловленных наличием в ней источника информации, выдающего как явно выраженные независимые одиночные информационные сообщения пользователя (ИСП), так и пачки ИСП, длины которых распределены по геометрическому закону. В этом случае при аппроксимации реальной статистики входящих потоков ИСП невозможно свести их к трем классическим модификациям потоков сообщений.

Наиболее близким по технической сущности к заявляемому устройству (прототипом) является устройство для параметрической оценки закона распределения потоков сообщений (см. патент РФ 2165100, 7 G 06 F 17/18, 2001, бюл. 10), содержащее входной усилитель, на вход которого подана бинарная импульсная последовательность, блок вычисления параметров, блок вычисления средних арифметических значений, блок определения типа распределения, вычислитель распределения, блок управления и блок анализа интенсивности.

Причем тактовый выход блока управления подключен к тактовому входу вычислителя распределения, обнуляющий и управляющий выходы блока управления соединены соответственно с обнуляющим и управляющим входами блока вычисления параметров, информационный вход которого соединен с выходом входного усилителя, первый и второй информационные выходы блока вычисления параметров подключены соответственно к первому и второму информационным входам блока вычисления средних арифметических значений, первый информационный выход которого соединен с первым информационным входом вычислителя распределения и с входом блока определения типа распределения, первый, второй и третий модификационные выходы которого подключены соответственно к первому, второму и третьему модификационным входам вычислителя распределения, второй информационный вход которого соединен со вторым информационным выходом блока вычисления средних арифметических значений, выход вычислителя распределения является выходом "плотность вероятности" (в описании прототипа этот выход обозначен словом "выход") устройства, вход блока анализа интенсивности подключен ко второму информационному выходу блока вычисления параметров, первый и второй параметрические выходы блока анализа интенсивности соединены соответственно с первым и вторым параметрическими входами вычислителя распределения, управляющий выход блока анализа интенсивности подключен к управляющему входу блока вычисления средних арифметических значений.

В прототипе реализуется возможность оценки параметров распределения как однородных, так и неоднородных (смешанных) потоков МПС - потоков, периодически меняющих свою интенсивность в ходе функционирования ЦСИО, тем самым осуществляется расширение области применения устройства.

Однако прототип имеет недостаток - устройство не способно производить текущую оценку математического ожидания и дисперсии числа ИСП, поступающих в ЦСИО за период наблюдения. Известно, что плотность вероятности числа ИСП, на получение которой ориентировано устройство-прототип, не есть универсальная форма закона распределения потока сообщений, но является более наглядной характеристикой, чем функция распределения. Простейшими, но крайне важными с точки зрения анализа и синтеза ЦСИО, характеристиками случайной величины числа ИСП, поступающих на вход сети, служат ее первый и второй центральные моменты - математическое ожидание и дисперсия [1, 2]. Математическое ожидание и дисперсия закона распределения играют главную роль при определении вероятностно-временных характеристик (ВВХ) различных потоков МПС, а значит, при выработке оптимальных алгоритмов управления потоками и процедур динамического управления сетью в целом. Кроме того, существующая система критериев оценки качества и эффективности функционирования ЦСИО [3] с точки зрения анализа процессов коммутации, маршрутизации и ограничения потоков ИСП опирается на критерий ВВХ, а значит, на текущие показатели математического ожидания и дисперсии, без которых оценочные значения ВВХ потоков сообщений не могут быть получены. В данном случае для определения ВВХ недостаточно иметь лишь оценочные значения плотности вероятности, на получение которых ориентировано устройство-прототип, необходимы данные о текущих значениях математического ожидания и дисперсии числа ИСП, поступающих в ЦСИО за период наблюдения.

Целью изобретения является создание устройства для параметрической оценки закона распределения потоков сообщений с более широкой областью применения, устройства, способного оценивать как плотность вероятности различных потоков МПС, так и производить текущую оценку математического ожидания и дисперсии числа ИСП, поступающих в ЦСИО за период наблюдения, - ключевых параметров, необходимых для определения вероятностно-временных характеристик потоков, циркулирующих в ЦСИО.

Указанная цель достигается тем, что в известное устройство для параметрической оценки закона распределения потоков сообщений, содержащее входной усилитель, на вход которого подана бинарная импульсная последовательность, блоки вычисления параметров, вычисления средних арифметических значений, определения типа распределения, вычислитель распределения, блок анализа интенсивности и блок управления, тактовый выход которого подключен к тактовому входу вычислителя распределения, обнуляющий и управляющий выходы блока управления соединены соответственно с обнуляющим и управляющим входами блока вычисления параметров, информационный вход которого соединен с выходом входного усилителя, первый информационный выход блока вычисления параметров подключен к первому информационному входу блока вычисления средних арифметических значений, второй информационный выход блока вычисления параметров подключен к входу блока анализа интенсивности и ко второму информационному входу блока вычисления средних арифметических значений, первый информационный выход которого соединен со входом блока определения типа распределения, управляющий выход блока анализа интенсивности подключен к управляющему входу блока вычисления средних арифметических значений, выход вычислителя распределения является выходом "плотность вероятности" устройства, дополнительно введен вычислитель математического ожидания и дисперсии.

Первый информационный вход последнего соединен с первым информационным выходом блока вычисления средних арифметических значений, второй информационный выход блока вычисления средних арифметических значений подключен ко второму информационному входу вычислителя математического ожидания и дисперсии, первый, второй и третий модификационные выходы блока определения типа распределения подключены соответственно к первому, второму и третьему модификационным входам вычислителя математического ожидания и дисперсии, первый и второй параметрические входы которого соединены соответственно с первым и вторым параметрическими выходами блока анализа интенсивности, первый, второй и третий модификационные выходы вычислителя математического ожидания и дисперсии подключены соответственно к первому, второму и третьему модификационным входам вычислителя распределения, первый и второй информационные входы которого соединены соответственно с первым и вторым информационными выходами вычислителя математического ожидания и дисперсии, первый и второй параметрические выходы которого подключены соответственно к первому и второму параметрическим входам вычислителя распределения, первый и второй главные выходы вычислителя математического ожидания и дисперсии являются соответственно выходами "математическое ожидание" и "дисперсия" устройства.

Вычислитель математическою ожидания и дисперсии состоит из первого, второго и третьего элементов ЗАПРЕТ, первичного и вторичного электронных ключей, делителя математического ожидания, делителя дисперсии, сумматора-умножителя, умножителя соотношений длин, сумматора неоднородного потока, делителя неоднородного потока, граничного умножителя, первичного и вторичного постоянных запоминающих устройств, сумматора первичной интенсивности, умножителя первичной интенсивности, первичного и вторичного преобразователей степени, умножителя вторичной интенсивности, вычислителя произведения, промежуточного сумматора, промежуточного умножителя, сумматора, предварительного умножителя, предварительного сумматора, оконечного сумматора, умножителя первого порядка, умножителя значений степени, умножителя второго порядка и оконечного элемента ЗАПРЕТ.

Причем запрещающие входы первого, второго и третьего элементов ЗАПРЕТ являются соответственно первым, вторым и третьим модификационными входами и первым, вторым и третьим модификационными выходами вычислителя математического ожидания и дисперсии, а запрещающий вход третьего элемента ЗАПРЕТ дополнительно подключен к запрещающему входу оконечного элемента ЗАПРЕТ, первый вход делителя математического ожидания подключен ко второму входу сумматора-умножителя, первому и второму входам умножителя соотношений длин, второму входу делителя неоднородного потока, второму входу вычислителя произведения, первому входу промежуточною сумматора и является первым информационным входом и первым информационным выходом вычислителя математического ожидания и дисперсии, разрешающий вход первого элемента ЗАПРЕТ подключен к разрешающим входам второго и третьего элементов ЗАПРЕТ и является вторым информационным входом и вторым информационным выходом вычислителя математического ожидания и дисперсии.

Первый вход сумматора неоднородного потока соединен с входами первичного и вторичного постоянных запоминающих устройств, вторым входом сумматора первичной интенсивности, вторым входом умножителя первичной интенсивности и является первым параметрическим входом и первым параметрическим выходом вычислителя математического ожидания и дисперсии, первый вход делителя неоднородного потока соединен с первым входом умножителя значений степени, n входами, где n≥40, первичного преобразователя степени и является вторым параметрическим входом и вторым параметрическим выходом вычислителя математического ожидания и дисперсии, выход первого элемента ЗАПРЕТ подключен к первому входу сумматора-умножителя и ко второму входу первичного электронного ключа, выход второго элемента ЗАПРЕТ соединен с первыми входами первичного и вторичного электронных ключей, выход сумматора-умножителя подключен ко второму входу вторичного электронного ключа, выход которого соединен со вторым входом делителя дисперсии, первый вход которого подключен к выходу умножителя соотношений длин, выход делителя неоднородного потока подключен ко второму входу сумматора неоднородного потока.

Выход первичного постоянного запоминающего устройства соединен с первым входом сумматора первичной интенсивности, вторым входом промежуточного сумматора и вторым входом сумматора, первый вход которого подключен к выходу промежуточного умножителя, выход сумматора первичной интенсивности соединен с первым входом умножителя первичной интенсивности, первым входом вычислителя произведения и вторым входом промежуточного умножителя, первый вход которого подключен к выходу промежуточного сумматора, выход умножителя первичной интенсивности соединен с первым входом умножителя первого порядка, второй вход которого подключен к n выходам первичного преобразователя степени, разрешающий вход которого соединен с разрешающим входом вторичного преобразователя степени, вторым входом умножителя значений степени и выходом вторичного постоянного запоминающего устройства, выход вычислителя произведения подключен к n входам вторичного преобразователя степени и к первому входу умножителя вторичной интенсивности, второй вход которого соединен с n выходами вторичного преобразователя степени.

Выход умножителя вторичной интенсивности подключен ко второму входу умножителя второго порядка, первый вход которого соединен с выходом умножителя значений степени, выход умножителя второго порядка подключен ко второму входу предварительного умножителя, первый вход которого соединен с выходом сумматора, выход предварительного умножителя подключен ко второму входу предварительного сумматора, первый вход которого соединен с выходом умножителя первого порядка, выход предварительного сумматора подключен ко второму входу оконечного сумматора, первый вход которого соединен с выходом граничного умножителя, выход первичного электронного ключа подключен ко второму входу делителя математического ожидания, выход сумматора неоднородного потока соединен с первым и вторым входами граничного умножителя, выходом третьего элемента ЗАПРЕТ, разрешающим входом оконечного элемента ЗАПРЕТ, выходом делителя математического ожидания и является первым главным выходом вычислителя математического ожидания и дисперсии, выход делителя дисперсии соединен с выходом оконечною элемента ЗАПРЕТ, выходом оконечного сумматора и является вторым главным выходом вычислителя математического ожидания и дисперсии.

Принцип создания предлагаемого устройства основан на возможности оценки математического ожидания, дисперсии и плотности распределения числа ИСП, поступающих на вход ЦСИО за период наблюдения, с использованием усредненных за период наблюдения значений параметров различных разновидностей разнородных (однородных и неоднородных) потоков МПС, опираясь на алгоритмы оценивания их первого и второго центральных моментов (математического ожидания и дисперсии) [3], на алгоритмы аппроксимации реальной статистики входящих потоков и сведения их непосредственно к трем известным модификациям [3], на алгоритмы суперпозиции входящих потоков [3, 4, 5] - в случаях, когда имеется источник неоднородной (смешанной) информации, выдающий как явно выраженные независимые и одиночные ИСП, так и пачки ИСП, длины которых распределены по геометрическому закону.

Известны три основные разновидности потоков МПС пользователей ЦСИО, математические ожидания, дисперсии и плотности вероятности которых описаны в [3]:

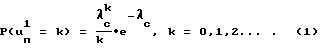

1. Простой поток МПС (количество элементов в информационной части пакетов сообщения равно количеству элементов, содержащихся в информационной части МПС, то есть mп=mс и ξ=mп/mс=1), плотность вероятности числа пакетов которого определяется выражением

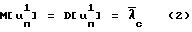

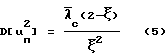

Математическое ожидание и дисперсия числа пакетов (и сообщений), поступающих на вход ЦСИО, определяются выражением [3]

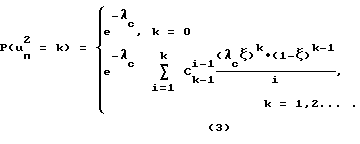

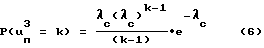

2. Сложный поток МПС (mп<mс и ξ<1) с плотностью вероятности числа пакетов

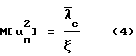

Математическое ожидание и дисперсия числа ИСП, поступающих на вход ЦСИО, при сложном потоке МПС определяются выражениями [3]

3. Прореженный поток МПС (mп>mс и ξ>1) с плотностью вероятности числа пакетов

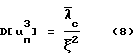

Математическое ожидание и дисперсия числа ИСП, поступающих на вход ЦСИО, при прореженном потоке МПС определяются выражениями [3]

Если при аппроксимации реальной статистики входящих потоков ИСП не удается свести их непосредственно к трем рассмотренным выше модификациям потоков сообщений, то используют суперпозицию входящих потоков [3-5]. Например, если в составе ЦСИО имеется оконечный терминал - источник информации, который передает смешанные МПС - как явно выраженные независимые и одиночные ИСП, так и пачки ИСП, длины которых распределены по геометрическому закону, то для описания такого входящего потока ИСП используется суперпозиция потоков, описываемых выражениями (1) и (3) [3].

Тогда плотность вероятности Р(uп=k) является сверткой соответствующих плотностей вероятности и равна

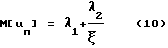

Математическое ожидание числа ИСП, поступающих на вход ЦСИО при неоднородном потоке МПС, определяется с помощью выражения [3]

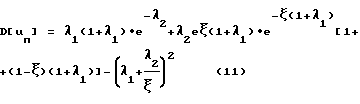

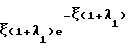

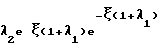

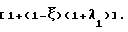

Зная вид плотности вероятности (9) и выражение для получения значений математического ожидания (10), нетрудно подучить выражение для дисперсии числа ИСП, поступающих на вход ЦСИО при неоднородном потоке МПС. С помощью функций Лагерра выражение для оценки значений дисперсии записывается в виде

Анализ приведенных выражений позволяет сделать вывод о том, что оценку математического ожидания, дисперсии и плотности вероятности разнородного (однородного и неоднородного) потока МПС можно получить на основе определения параметров потока λc и ξ. Использование в этих целях устройства-прототипа (см. патент РФ 2165100, 7 G 06 F 17/18, 2001, бюл.10) является нецелесообразным в силу его неспособности производить оценку математического ожидания и дисперсии как однородного, так и неоднородного (смешанного) потоков МПС, поступающих на вход ЦСИО за период наблюдения. Для определения ВВХ, а значит, для получения текущих значений математического ожидания и дисперсии потока сообщений, циркулирующего в реальной ЦСИО, недостаточно реализовать расчет плотности вероятности поступления заявок пользователей (1, 3, 6, 9) по усредненным за интервал наблюдения параметрам λc и ξ, необходимы верификация решения об однородности или неоднородности потока МПС и параметрическая оценка центральных моментов потока сообщений (значений математического ожидания и дисперсии) в соответствии с выражениями (2, 4, 5, 7, 8, 11) и на основе предварительного решения о разновидности потока МПС, циркулирующего в ЦСИО.

Анализ выражений (1-11) позволяет сделать вывод о возможности технической реализации получения оценочных значений математического ожидания, дисперсии и плотности вероятности - трех ключевых параметров закона распределения разнородных (однородных и неоднородных) потоков МПС, циркулирующих в ЦСИО.

Построение устройства, основанного на предложенном принципе работы, позволяет получить преимущество перед прототипом, обеспечивая способность оценивать значения математического ожидания, дисперсии и плотности вероятности закона распределения как однородных, так и неоднородных (смешанных) потоков МПС пользователей ЦСИО. Это существенно расширяет функциональные возможности устройства, позволяя оценивать весь (необходимый и достаточный) диапазон параметров потоков сообщений, характеризующий динамику процесса вероятностно-временных изменений разнородных потоков МПС пользователей ЦСИО, обеспечивая тем самым основу для построения робастных алгоритмов анализа качества и эффективности процессов коммутации, маршрутизации и ограничения потоков ИСП в ЦСИО, для синтеза оптимальных алгоритмов управления потоками и процедур динамического управления сетью в целом [3].

Заявленное устройство поясняется чертежами, на которых представлены:

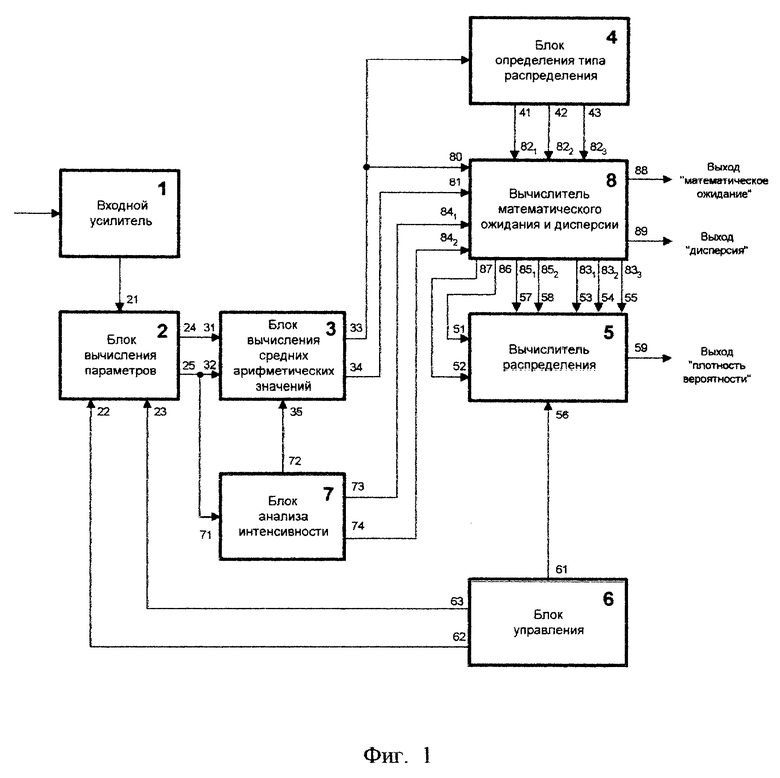

на фиг. 1 - структурная схема устройства для параметрической оценки закона распределения потоков сообщений;

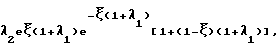

на фиг.2 - структурная схема вычислителя математического ожидания и дисперсии;

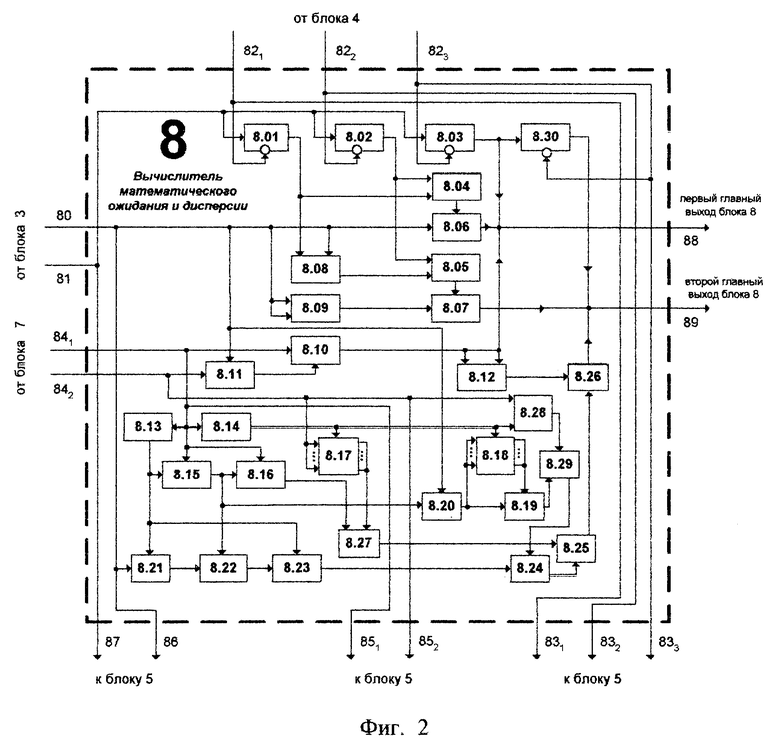

на фиг.3 - структурная схема первичного преобразователя степени;

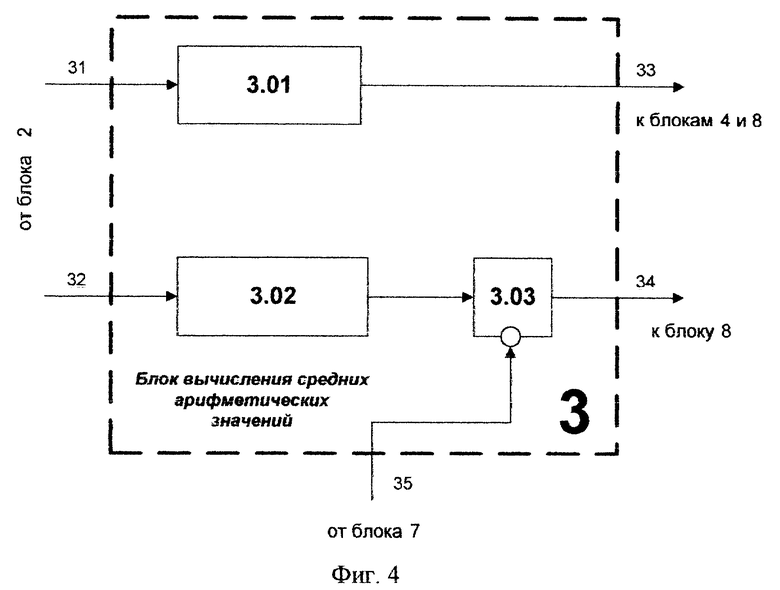

на фиг. 4 - структурная схема блока вычисления средних арифметических значений;

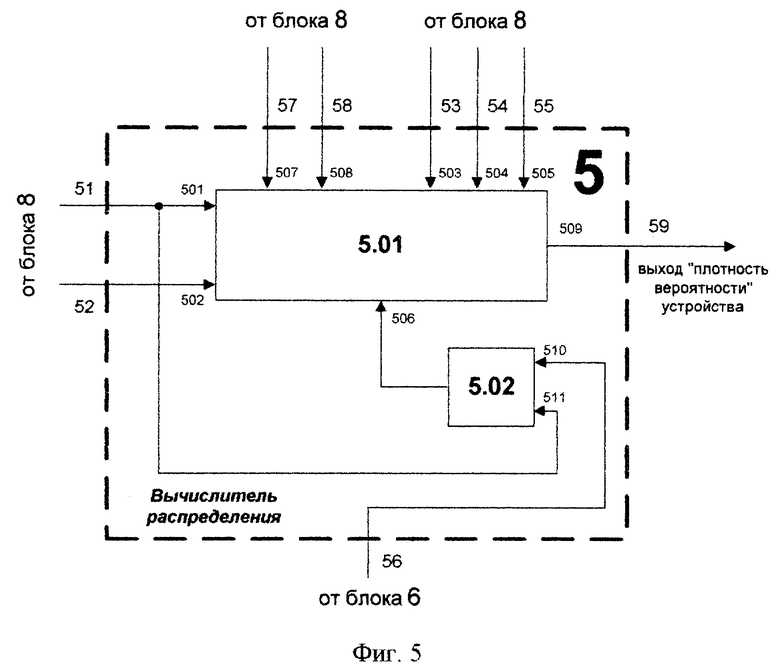

на фиг.5 - структурная схема вычислителя распределения;

на фиг.6 - структурная схема блока анализа интенсивности;

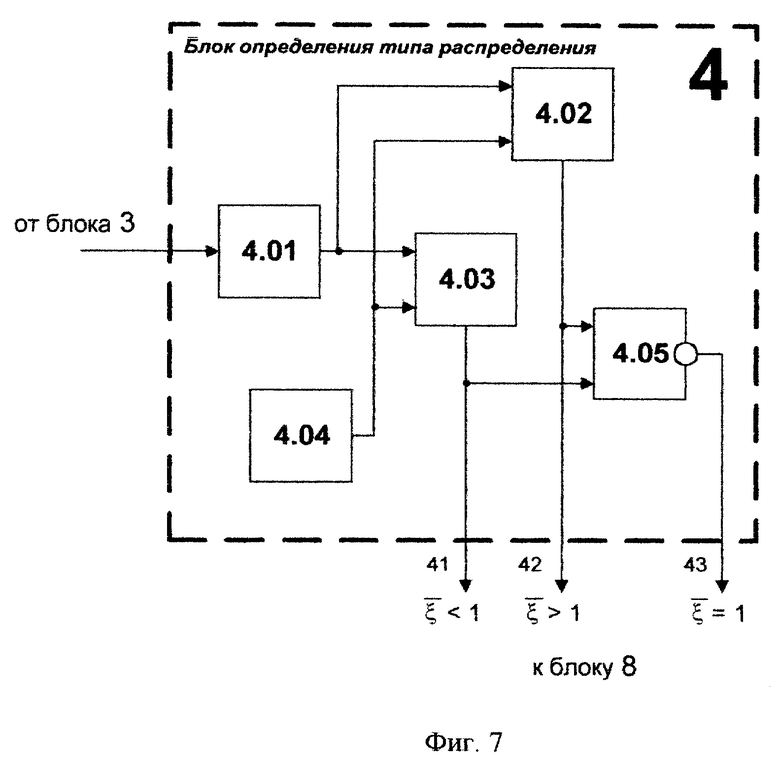

на фиг.7 - структурная схема блока определения типа распределения;

на фиг.8 - структурная схема блока вычисления параметров;

на фиг.9 - структурная схема блока управления.

Устройство для параметрической оценки закона распределения потоков сообщений, изображенное на фиг.1, состоит из входного усилителя 1, на вход которого подана бинарная импульсная последовательность, блока вычисления параметров 2, блока вычисления средних арифметических значений 3, блока определения типа распределения 4, вычислителя распределения 5, блока управления 6, блока анализа интенсивности 7 и вычислителя математического ожидания и дисперсии 8.

Тактовый выход 61 блока управления 6 подключен к тактовому входу 56 вычислителя распределения 5, обнуляющий 62 и управляющий 63 выходы блока управления 6 соединены соответственно с обнуляющим 22 и управляющим 23 входами блока вычисления параметров 2, информационный вход 21 которого соединен с выходом входного усилителя 1, первый информационный выход 24 блока вычисления параметров 2 подключен к первому информационному входу 31 блока вычисления средних арифметических значений 3, второй информационный выход 25 блока вычисления параметров 2 подключен к входу 71 блока анализа интенсивности 7 и ко второму информационному входу 32 блока вычисления средних арифметических значений 3.

Первый информационный выход 33 блока вычисления средних арифметических значений 3 соединен со входом блока определения типа распределения 4 и с первым информационным входом 80 вычислителя математического ожидания и дисперсии 8, второй информационный выход 34 блока вычисления средних арифметических значений 3 подключен ко второму информационному входу 81 вычислителя математического ожидания и дисперсии 8. Управляющий выход 72 блока анализа интенсивности 7 подключен к управляющему входу 35 блока вычисления средних арифметических значений 3.

Первый 41, второй 42 и третий 43 модификационные выходы блока определения типа распределения 4 подключены соответственно к первому 821, второму 822 и третьему 823 модификационным входам вычислителя математического ожидания и дисперсии 8, первый 841 и второй 842 параметрические входы которого соединены соответственно с первым 73 и вторым 74 параметрическими выходами блока анализа интенсивности 7. Первый 831, второй 832 и третий 833 модификационные выходы вычислителя математического ожидания и дисперсии 8 подключены соответственно к первому 53, второму 54 и третьему 55 модификационным входам вычислителя распределения 5, первый 51 и второй 52 информационные входы которого соединены соответственно с первым 86 и вторым 87 информационными выходами вычислителя математического ожидания и дисперсии 8.

Первый 851 и второй 852 параметрические выходы вычислителя математического ожидания и дисперсии 8 подключены соответственно к первому 57 и второму 58 параметрическим входам вычислителя распределения 5. Первый 88 и второй 89 главные выходы вычислителя математического ожидания и дисперсии 8 являются соответственно выходами "математическое ожидание" и "дисперсия" устройства. Выход 59 вычислителя распределения 5 является выходом "плотность вероятности" устройства.

Вычислитель математического ожидания и дисперсии 8 (фиг.2) предназначен для получения оценочных значений математического ожидания (M[u

Запрещающие входы первого 8.01, второго 8.02 и третьего 8.03 элементов ЗАПРЕТ являются соответственно первым 821, вторым 822 и третьим 823 модификационными входами и первым 831, вторым 832 и третьим 833 модификационными выходами вычислителя математического ожидания и дисперсии 8, а запрещающий вход третьего элемента ЗАПРЕТ 8.03 дополнительно подключен к запрещающему входу оконечного элемента ЗАПРЕТ 8.30, первый вход делителя математического ожидания 8.06 подключен ко второму входу сумматора-умножителя 8.08, первому и второму входам умножителя соотношений длин 8.09, второму входу делителя неоднородного потока 8.11, второму входу вычислителя произведения 8.20, первому входу промежуточного сумматора 8.21 и является первым информационным входом 80 и первым информационным выходом 86 вычислителя математического ожидания и дисперсии 8.

Разрешающий вход первого элемента ЗАПРЕТ 8.01 подключен к разрешающим входам второго 8.02 и третьего 8.03 элементов ЗАПРЕТ и является вторым информационным входом 81 и вторым информационным выходом 87 вычислителя математического ожидания и дисперсии 8. Первый вход сумматора неоднородного потока 8.10 соединен с входами первичного 8.13 и вторичного 8.14 ПЗУ, вторым входом сумматора первичной интенсивности 8.15, вторым входом умножителя первичной интенсивности 8.16 и является первым параметрическим входом 841 и первым параметрическим выходом 851 вычислителя математического ожидания и дисперсии 8. Первый вход делителя неоднородного потока 8.11 соединен с первым входом умножителя значений степени 8.28, n входами, где n≥40, первичного преобразователя степени 8.17 и является вторым параметрическим входом 842 и вторым параметрическим выходом 852 вычислителя математического ожидания и дисперсии 8.

Выход первого элемента ЗАПРЕТ 8.01 подключен к первому входу сумматора-умножителя 8.08 и к второму входу первичного электронного ключа 8.04, выход второго элемента ЗАПРЕТ 8.02 соединен с первыми входами первичного 8.04 и вторичного 8.05 электронных ключей, выход сумматора-умножителя 8.08 подключен ко второму входу вторичного электронного ключа 8.05, выход которого соединен со вторым входом делителя дисперсии 8.07, первый вход которого подключен к выходу умножителя соотношений длин 8.09. Выход делителя неоднородного потока 8.11 подключен ко второму входу сумматора неоднородного потока 8.10, выход первичного ПЗУ 8.13 соединен с первым входом сумматора первичной интенсивности 8.15, вторым входом промежуточного сумматора 8.21 и вторым входом сумматора 8.23, первый вход которого подключен к выходу промежуточного умножителя 8.22, выход сумматора первичной интенсивности 8.15 соединен с первым входом умножителя первичной интенсивности 8.16, первым входом вычислителя произведения 8.20 и вторым входом промежуточного умножителя 8.22, первый вход которого подключен к выходу промежуточного сумматора 8.21.

Выход умножителя первичной интенсивности 8.16 соединен с первым входом умножителя первого порядка 8.27, второй вход которого подключен к n выходам первичного преобразователя степени 8.17, разрешающий вход которого соединен с разрешающим входом вторичного преобразователя степени 8.18, вторым входом умножителя значений степени 8.28 и выходом вторичного ПЗУ 8.14, выход вычислителя произведения 8.20 подключен к n входам вторичного преобразователя степени 8.18 и к первому входу умножителя вторичной интенсивности 8.19, второй вход которого соединен с n выходами вторичного преобразователя степени 8.18. Выход умножителя вторичной интенсивности 8.19 подключен ко второму входу умножителя второго порядка 8.29, первый вход которого соединен с выходом умножителя значений степени 8.28, выход умножителя второго порядка 8.29 подключен ко второму входу предварительного умножителя 8.24, первый вход которого соединен с выходом сумматора 8.23, выход предварительного умножителя 8.24 подключен ко второму входу предварительного сумматора 8.25, первый вход которого соединен с выходом умножителя первого порядка 8.27.

Выход предварительного сумматора 8.25 подключен ко второму входу оконечного сумматора 8.26, первый вход которого соединен с выходом граничного умножителя 8.12, выход первичного электронного ключа 8.04 подключен ко второму входу делителя математического ожидания 8.06. Выход сумматора неоднородного потока 8.10 соединен с первым и вторым входами граничного умножителя 8.12, выходом третьего элемента ЗАПРЕТ 8.03, разрешающим входом оконечного элемента ЗАПРЕТ 8.30, выходом делителя математического ожидания 8.06 и является первым главным выходом 88 вычислителя математического ожидания и дисперсии 8. Выход делителя дисперсии 8.07 соединен с выходом оконечного элемента ЗАПРЕТ 8.30, выходом оконечного сумматора 8.26 и является вторым главным выходом 89 вычислителя математического ожидания и дисперсии 8.

Первый 8.01, второй 8.02, третий 8.03 элементы ЗАПРЕТ и оконечный элемент ЗАПРЕТ 8.30 могут быть технически реализованы, как показано в [6, стр.24, рис. 1.5 (д, е)]. Первичный 8.04 и вторичный 8.05 электронные ключи технически могут быть реализованы в виде ключевой схемы на биполярном транзисторе (полупроводникового ключа), как показано в [7, стр.136-137, рис.4.1 (а)]. Делитель математического ожидания 8.06, делитель дисперсии 8.07 и делитель неоднородного потока 8.11 могут быть реализованы в виде счетчика-делителя, как показано в [6, стр.175-182, рис 5.46 (б)]. Сумматор-умножитель 8.08 может быть технически реализован в виде обычного арифметико-логического устройства (АЛУ) в соответствии с описанным в [8, стр.158-170]. Умножитель соотношений длин 8.09, граничный умножитель 8.12, умножитель первичной интенсивности 8.16, умножитель вторичной интенсивности 8.19, вычислитель произведения 8.20, промежуточный умножитель 8.22, предварительный умножитель 8.24, умножитель первого порядка 8.27, умножитель значений степени 8.28 и умножитель второго порядка 8.29 могут быть технически реализованы в виде типового умножителя, как показано в [9, стр.181-184, рис.5.27].

Сумматор неоднородного потока 8.10, сумматор первичной интенсивности 8.15, сумматор 8.23 и предварительный сумматор 8.25 могут быть технически реализованы на базе одноразрядного сумматора, описанного в [9, стр.173-175, рис 5.16 (а)]. Первичное 8.13 и вторичное 8.14 ПЗУ могут быть реализованы в виде типового полупроводникового ПЗУ, описанного в [7, стр.260-261, рис. 7.10] . Промежуточный сумматор 8.21 и оконечный сумматор 8.26 могут быть технически реализованы в виде разностного преобразователя, как показано в [10, стр.182-186, рис.6.1.2(а)].

Первичный преобразователь степени 8.17 вычислителя математического ожидания и дисперсии 8 (фиг.3) аналогичен вторичному преобразователю степени 8.18 вычислителя математического ожидания и дисперсии 8, предназначен для вычисления значений  (вторичный преобразователь степени 8.18 предназначен для вычисления значений

(вторичный преобразователь степени 8.18 предназначен для вычисления значений  в соответствии с выражением (11) и представляет собой однократно программируемое ПЗУ с одним разрешающим входом, на который с выхода вторичного ПЗУ 8.14 поступает значение е (е= 2,71828), n входами и n выходами, где n≥40. На n входов поступают значения показателя степени (λ2), совпадение значений сигнала на j-ом входе, где j=0, 1, 2, 3,..., n, со значениями показателя степени (λ2, но со знаком "минус"), хранящимися в j-ой ячейке памяти ПЗУ, инициирует выдачу с j-го выхода первичного преобразователя степени 8.17 запрограммированного значения

в соответствии с выражением (11) и представляет собой однократно программируемое ПЗУ с одним разрешающим входом, на который с выхода вторичного ПЗУ 8.14 поступает значение е (е= 2,71828), n входами и n выходами, где n≥40. На n входов поступают значения показателя степени (λ2), совпадение значений сигнала на j-ом входе, где j=0, 1, 2, 3,..., n, со значениями показателя степени (λ2, но со знаком "минус"), хранящимися в j-ой ячейке памяти ПЗУ, инициирует выдачу с j-го выхода первичного преобразователя степени 8.17 запрограммированного значения

Первичный 8.17 и вторичный 8.18 преобразователи степени могут быть технически реализованы на основе однократно программируемого ПЗУ серии 115 (например, К115ПР6), как показано в [11, стр.172, рис.1.126].

Блок вычисления средних арифметических значений 3 (фиг.4) предназначен для получения численных значений усредненных за интервал наблюдения параметров потока  и состоит из счетчика-делителя значений длительности 3.01, счетчика-делителя значений интенсивности 3.02 и элемента ЗАПРЕТ 3.03. Вход счетчика-делителя значений длительности 3.01 является первым информационным входом 31 блока вычисления средних арифметических значений 3, выход счетчика-делителя значений длительности 3.01 является первым информационным выходом 33 блока 3.

и состоит из счетчика-делителя значений длительности 3.01, счетчика-делителя значений интенсивности 3.02 и элемента ЗАПРЕТ 3.03. Вход счетчика-делителя значений длительности 3.01 является первым информационным входом 31 блока вычисления средних арифметических значений 3, выход счетчика-делителя значений длительности 3.01 является первым информационным выходом 33 блока 3.

Вход счетчика-делителя значений интенсивности 3.02 является вторым информационным входом 32 блока вычисления средних арифметических значений 3, выход счетчика-делителя значений интенсивности 3.02 подключен к разрешающему входу элемента ЗАПРЕТ 3.03. Запрещающий вход элемента ЗАПРЕТ 3.03 является управляющим входом 35 блока вычисления средних арифметических значений 3, выход элемента ЗАПРЕТ 3.03 является вторым информационным выходом 34 блока 3. Счетчик-делитель значений длительности 3.01 и счетчик-делитель значений интенсивности 3.02 могут быть технически реализованы в виде счетчика-делителя с переменным коэффициентом деления, работающего как суммирующий двоичный, как показано в [6, стр.181-182, рис.5.47]. Элемент ЗАПРЕТ 3.03 может быть реализован в соответствии с описанным в [6, стр.24, рис.1.5 (д, е)].

Вычислитель распределения 5, представленный на фиг.5, предназначен для получения оценочных значений плотности вероятности в соответствии с выражениями (1, 3, 6, 9) и состоит из арифметико-логического устройства 5.01 и элемента И 5.02. Первый 501 и второй 502 информационные входы арифметико-логического устройства 5.01 являются соответственно первым 51 и вторым 52 информационными входами вычислителя распределения 5. Первый 503, второй 504 и третий 505 модификационные входы арифметико-логического устройства 5.01 являются соответственно первым 53, вторым 54 и третьим 55 модификационными входами вычислителя распределения 5. Первый 507 и второй 508 параметрические входы арифметико-логического устройства 5.01 являются соответственно первым 57 и вторым 58 параметрическими входами вычислителя распределения 5. Первый вход 510 элемента И 5.02 является тактовым входом 56 вычислителя распределения 5, выход элемента И 5.02 подключен к тактовому входу 506 арифметико-логического устройства 5.01. Второй вход 511 элемента И 5.02 соединен с первым информационным входом 51 вычислителя распределения 5, выход 509 арифметико-логического устройства 5.01 является выходом 59 вычислителя распределения 5. Арифметико-логическое устройство 5.01 может быть технически реализовано в виде обычного арифметико-логического устройства (АЛУ), описанного в [8, стр.158-170]. Элемент И 5.02 может быть реализован в соответствии с описанным в [6, стр.13-14, рис.1.2].

Блок анализа интенсивности 7 (фиг.6) предназначен для текущего оценивания и сравнения предыдущего (λ1) и последующего (λ2) значений отсчетов параметра λc входного потока и состоит из схемы сравнения 7.01, оперативного запоминающего устройства 7.02, первичного элемента И 7.03 и вторичного элемента И 7.04. Информационный вход 701 схемы сравнения 7.01, вход оперативного запоминающего устройства 7.02 и информационный вход 706 вторичного элемента И 7.04 параллельно соединены друг с другом, а их общий вход является входом 71 блока анализа интенсивности 7, вспомогательный выход 707 оперативного запоминающего устройства 7.02 соединен с вспомогательным входом 702 схемы сравнения 7.01, выход которой соединен с сигнальными входами 703 и 705 первичного 7.03 и вторичного 7.04 элементов И соответственно и является управляющим выходом 72 блока анализа интенсивности 7.

Выходы первичного 7.03 и вторичного 7.04 элементов И являются соответственно первым 73 и вторым 74 параметрическими выходами блока анализа интенсивности 7, информационный выход 708 оперативного запоминающего устройства 7.02 подключен к информационному входу 704 первичного элемента И 7.03. Схема сравнения 7.01 может быть технически реализована в виде узла сравнения (цифрового компаратора), как показано в [6, стр.149-152, рис.5.19)]. Оперативное запоминающее устройство (ОЗУ) 7.02 реализуется в виде регистра хранения в соответствии с описанием, представленным в работе [6, стр.156-158, рис. 5.27] . Первичный 7.03 и вторичный 7.04 элементы И реализуются в виде стандартных элементов И, как показано в [6, стр.13-14, рис.1.2].

Блок определения типа распределения 4, входящий в общую структурную схему, предназначен для осуществления процедуры сравнения значений параметра длительности  с единичным порогом и принятия решения о принадлежности однородного входного потока к одной из трех модификаций, описываемых выражениями (1, 3, 6). Схема блока определения типа распределения 4 известна, описана (например, в патенте РФ 2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.7 данного описания. Блок определения типа распределения 4 содержит цифроаналоговый преобразователь (ЦАП) 4.01, два компаратора 4.02, 4.03, генератор порогового напряжения 4.04, элемент ИЛИ-НЕ 4.05. При этом вход цифроаналогового преобразователя 4.01 соединен с первым информационным выходом 33 блока вычисления средних арифметических значений 3, выход цифроаналогового преобразователя 4.01 соединен с первыми входами компараторов 4.02 и 4.03, вторые входы которых подключены к выходу генератора порогового напряжения 4.04, выходы компараторов являются первым 41 и вторым 42 модификационными выходами блока 4, соединены с первым и вторым входами элемента ИЛИ-НЕ 4.05 и с первым 821 и вторым 822 модификационными входами вычислителя математического ожидания и дисперсии 8, выход элемента ИЛИ-НЕ 4.05 является третьим модификационным выходом 43 блока 4 и подключен к третьему модификационному входу 823 вычислителя математического ожидания и дисперсии 8.

с единичным порогом и принятия решения о принадлежности однородного входного потока к одной из трех модификаций, описываемых выражениями (1, 3, 6). Схема блока определения типа распределения 4 известна, описана (например, в патенте РФ 2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.7 данного описания. Блок определения типа распределения 4 содержит цифроаналоговый преобразователь (ЦАП) 4.01, два компаратора 4.02, 4.03, генератор порогового напряжения 4.04, элемент ИЛИ-НЕ 4.05. При этом вход цифроаналогового преобразователя 4.01 соединен с первым информационным выходом 33 блока вычисления средних арифметических значений 3, выход цифроаналогового преобразователя 4.01 соединен с первыми входами компараторов 4.02 и 4.03, вторые входы которых подключены к выходу генератора порогового напряжения 4.04, выходы компараторов являются первым 41 и вторым 42 модификационными выходами блока 4, соединены с первым и вторым входами элемента ИЛИ-НЕ 4.05 и с первым 821 и вторым 822 модификационными входами вычислителя математического ожидания и дисперсии 8, выход элемента ИЛИ-НЕ 4.05 является третьим модификационным выходом 43 блока 4 и подключен к третьему модификационному входу 823 вычислителя математического ожидания и дисперсии 8.

Входной усилитель 1, входящий в общую структурную схему, предназначен для осуществления процедуры усиления, нормировки по амплитуде и длительности входного потока - бинарной импульсной последовательности. Входной усилитель 1 может быть технически реализован в виде триггера Шмитта, как показано в [6, стр.117-119, рис.4.12 (а)].

Блок вычисления параметров 2, входящий в общую структурную схему, предназначен для определения текущих значений параметров λc и ξ. Его схема известна, описана (например, в патенте РФ 2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.8 данного описания. Блок вычисления параметров 2 содержит дешифратор заголовков пакетов 2.01, обнаружитель пауз 2.02, счетчик информационной длины МПС 2.03, счетчик сообщений 2.04, вычислитель соотношения информационных длин пакетов и сообщений 2.05. При этом вход 21 дешифратора заголовков пакетов, являющийся входом блока 2, параллельно подключен к первому входу счетчика информационной длины МПС сообщений 2.03 и к входу обнаружителя пауз 2.02, выход дешифратора заголовков пакетов 2.01 соединен со вторым входом счетчика информационной длины МПС сообщений 2.03. Выход обнаружителя пауз 2.02 подключен к третьему входу счетчика информационной длины МПС сообщений 2.03 и к первому входу счетчика сообщений 2.04, выход счетчика информационной длины МПС сообщений 2.03 подключен к первому входу вычислителя соотношения информационных длин пакетов и сообщений 2.05, второй управляющий вход 23 которого и второй обнуляющий вход 22 счетчика сообщений соединены соответственно с управляющим 63 и обнуляющим 62 выходами блока управления 6, выходы вычислителя 2.05 и счетчика сообщений 2.04 являются первым 24 и вторым 25 информационными выходами блока вычисления параметров 2.

Блок управления 6, входящий в общую структурную схему, предназначен для регулировки интервала наблюдения (tнаб), длины пакета (mп) и количества пакетов (k). Его схема известна, описана (например, в патенте РФ 2165100, 7 G 06 F 17/18, 2001, бюл.10) и представлена на фиг.9 данного описания. Блок управления 6 содержит генератор тактовых импульсов 6.01 и три делителя с переменным коэффициентом деления (ДПКД) 6.02-6.04. При этом выход генератора тактовых импульсов 6.01 параллельно подключен к входам всех трех делителей с переменным коэффициентом деления, выход первого из которых (6.02) является тактовым выходом 61 блока 6 и подключен к тактовому входу 56 вычислителя распределения 5, а выходы 62, 63 двух других делителей с переменным коэффициентом деления 6.04 и 6.03 являются соответственно обнуляющим (62) и управляющим (63) выходами блока 6 и подключены к обнуляющему 22 и управляющему 23 входам блока вычисления параметров 2.

Устройство для параметрической оценки закона распределения потоков сообщений работает следующим образом Исследуемый входной поток МПС пользователей ЦСИО в виде бинарной импульсной последовательности, усиленной и пронормированной по амплитуде и длительности входным усилителем 1, поступает на вход 21 блока вычисления параметров 2, в котором производится определение текущих значений параметров λc и ξ. Блок вычисления параметров 2 может быть реализован в соответствии со схемой, предложенной на фиг.8. Вычисление в блоке 2 текущих значений параметров λc и ξ происходит следующим образом. Дешифратор 2.01 анализирует поступающую на вход блока вычисления параметров 2 импульсную последовательность и при обнаружении в ней признака начала информационной части пакета запускает счетчик 2.03, моменты завершения счета определяются моментами обнаружения дешифратором окончания информационной части пакета. Моменты поступления значений информационной длины сообщения mс в вычислитель соотношений информационных длин 2.05 и обнуления счетчика 2.03 определяются моментами появления импульсов на выходе обнаружителя пауз 2.02, фиксирующего окончание сообщения. В вычислителе соотношений информационных длин пакетов и сообщений 2.05 определяются значения ξ=mп/mс для фиксированной длины пакетов, принятых в ЦСИО и устанавливаемых блоком управления 6, подачей на управляющий вход 23 блока 2.05 импульсов, количество которых соответствует значению mс. Значение интенсивности λc определяется счетчиком 2.04 по импульсам с выхода обнаружителя пауз 2.02 за интервал времени, определяемый блоком 6 управления, посредством подачи импульсов с частотой fнаб на обнуляющий вход 22 счетчика 2.04.

Значения ξ и λc в параллельном коде поступают соответственно с информационных выходов 24 и 25 блока вычисления параметров 2 на информационные входы 31 и 32 блока вычисления средних арифметических значений 3. Блок вычисления средних арифметических значений 3 может быть реализован по схеме, представленной на фиг.4.

В случае, когда имеет место однородный (несмешанный) поток МПС пользователей ЦСИО, когда источники выдают сообщения регулярно, расчет численных значений усредненных за интервал наблюдения параметров потока  происходит следующим образом. Значения параметра ξ в виде бинарной последовательности поступают на первый информационный вход 31 блока 3, а затем на вход счетчика-делителя значений длительности 3.01, производящего арифметическую операцию суммирования последовательно поступающих значений ξ и деление полученной суммы на количество отсчетов. На выходе счетчика-делителя значений длительности 3.01 и на первом информационном выходе 33 блока вычисления средних арифметических значений 3 в двоичном параллельном коде получаем значение параметра

происходит следующим образом. Значения параметра ξ в виде бинарной последовательности поступают на первый информационный вход 31 блока 3, а затем на вход счетчика-делителя значений длительности 3.01, производящего арифметическую операцию суммирования последовательно поступающих значений ξ и деление полученной суммы на количество отсчетов. На выходе счетчика-делителя значений длительности 3.01 и на первом информационном выходе 33 блока вычисления средних арифметических значений 3 в двоичном параллельном коде получаем значение параметра  усредненного за интервал наблюдения.

усредненного за интервал наблюдения.

Значения параметра λc в виде бинарной последовательности поступают на второй информационный вход 32 блока 3, а затем на вход счетчика-делителя значений интенсивности 3.02, производящего арифметическую операцию суммирования последовательно поступающих значений λc и деление полученной суммы на количество отсчетов. На выходе счетчика-делителя значений интенсивности 3.02 и на разрешающем входе элемента ЗАПРЕТ 3.03 в двоичном параллельном коде имеем значение параметра  усредненного за интервал наблюдения. На второй информационный выход 34 блока 3 с выхода элемента ЗАПРЕТ 3.03 значение

усредненного за интервал наблюдения. На второй информационный выход 34 блока 3 с выхода элемента ЗАПРЕТ 3.03 значение  попадает лишь в том случае, если в данный момент на управляющий вход 35 блока 3 и на запрещающий вход элемента ЗАПРЕТ 3.03 не подан в двоичном параллельном коде сигнал с управляющего выхода 72 блока анализа интенсивности 7. В противном случае на второй информационный выход 34 блока 3 с выхода элемента ЗАПРЕТ 3.03 значение параметра

попадает лишь в том случае, если в данный момент на управляющий вход 35 блока 3 и на запрещающий вход элемента ЗАПРЕТ 3.03 не подан в двоичном параллельном коде сигнал с управляющего выхода 72 блока анализа интенсивности 7. В противном случае на второй информационный выход 34 блока 3 с выхода элемента ЗАПРЕТ 3.03 значение параметра  не подается. Интервал наблюдения для расчета параметров

не подается. Интервал наблюдения для расчета параметров  устанавливается блоком управления 6 в зависимости от требуемой точности.

устанавливается блоком управления 6 в зависимости от требуемой точности.

Блок управления 6 может быть реализован по схеме, предложенной на фиг.9. Формирование управляющих импульсных последовательностей осуществляется установкой на элементах группы делителей с переменным коэффициентом деления (ДПКД) соответствующих коэффициентов деления импульсной последовательности, поступающей с выхода генератора 6.01. Установкой коэффициента элемента 6.03 определяется значение tнаб=1/fнаб, установкой коэффициента элемента 6.04 определяется длина пакета, принятая в данный момент в ЦСИО (mп), установкой коэффициента элемента 6.02 определяется необходимое для расчета выражений (1, 3, 6, 9) количество пакетов (k).

Когда на первом 33 и на втором 34 информационных выходах блока 3 имеем одновременно значения параметров  соответственно, значение

соответственно, значение  с первого информационного выхода 33 блока 3 подается на вход блока определения типа распределения 4 и на первый информационный вход 80 вычислителя математического ожидания и дисперсии 8. В блоке определения типа распределения 4 происходит сравнение значения

с первого информационного выхода 33 блока 3 подается на вход блока определения типа распределения 4 и на первый информационный вход 80 вычислителя математического ожидания и дисперсии 8. В блоке определения типа распределения 4 происходит сравнение значения  с единичным порогом. Блок определения типа распределения 4 может быть реализован по схеме, предложенной на фиг.7. Определение типа распределения потока МПС осуществляется следующим образом. Значения

с единичным порогом. Блок определения типа распределения 4 может быть реализован по схеме, предложенной на фиг.7. Определение типа распределения потока МПС осуществляется следующим образом. Значения  поступающие с первого информационного выхода 33 блока 3 в двоичном параллельном коде, в ЦАП 4.01 преобразуются в аналоговое напряжение, которое на компараторах 4.02, 4.03 сравнивается с пороговым напряжением, вырабатываемым генератором порогового напряжения 4.04. Значение порогового напряжения соответствует единичному значению

поступающие с первого информационного выхода 33 блока 3 в двоичном параллельном коде, в ЦАП 4.01 преобразуются в аналоговое напряжение, которое на компараторах 4.02, 4.03 сравнивается с пороговым напряжением, вырабатываемым генератором порогового напряжения 4.04. Значение порогового напряжения соответствует единичному значению

На выходе 42 компаратора 4.02 появляется сигнал логической единицы в случае превышения значения  единичного значения, которая поступает на второй модификационный вход 822 вычислителя математического ожидания и дисперсии 8, в обратном случае появление логической единицы происходит на выходе 41 компаратора 4.03, которая поступает на первый модификационный вход 821 вычислителя математического ожидания и дисперсии 8. При наличии логических нулей на выходах компараторов 4.02 и 4.03 принимается решение о том, что

единичного значения, которая поступает на второй модификационный вход 822 вычислителя математического ожидания и дисперсии 8, в обратном случае появление логической единицы происходит на выходе 41 компаратора 4.03, которая поступает на первый модификационный вход 821 вычислителя математического ожидания и дисперсии 8. При наличии логических нулей на выходах компараторов 4.02 и 4.03 принимается решение о том, что  =1, об этом свидетельствует наличие логической единицы на выходе 43 элемента ИЛИ-НЕ 4.05 и поступление этой логической единицы на третий модификационный вход 823 вычислителя математического ожидания и дисперсии 8. Вычислитель математического ожидания и дисперсии 8 может быть технически реализован по схеме, предложенной на фиг.2.

=1, об этом свидетельствует наличие логической единицы на выходе 43 элемента ИЛИ-НЕ 4.05 и поступление этой логической единицы на третий модификационный вход 823 вычислителя математического ожидания и дисперсии 8. Вычислитель математического ожидания и дисперсии 8 может быть технически реализован по схеме, предложенной на фиг.2.

Таким образом, по результатам сравнения, путем подачи управляющего импульса на один из трех модификационных входов 821-823 вычислителя математического ожидания и дисперсии 8, принимается решение о вычислении математического ожидания (M[u поступающих соответственно с первого 33 и второго 34 информационных выходов блока 3 на первый 80 и второй 81 информационные входы вычислителя математического ожидания и дисперсии 8. При этом со второго информационного входа 81 вычислителя математического ожидания и дисперсии 8 значения параметра

поступающих соответственно с первого 33 и второго 34 информационных выходов блока 3 на первый 80 и второй 81 информационные входы вычислителя математического ожидания и дисперсии 8. При этом со второго информационного входа 81 вычислителя математического ожидания и дисперсии 8 значения параметра  в двоичном коде поступают на второй информационный выход 87 вычислителя математического ожидания и дисперсии 8 и на разрешающие входы первого 8.01, второго 8.02 и третьего 8.03 элементов ЗАПРЕТ.

в двоичном коде поступают на второй информационный выход 87 вычислителя математического ожидания и дисперсии 8 и на разрешающие входы первого 8.01, второго 8.02 и третьего 8.03 элементов ЗАПРЕТ.

С одного из модификационных входов (821, 822 или 823 - в зависимости от результата, полученного в блоке 4) на соответствующий модификационный выход (831, 832 или 833) блока 8 и на запрещающий вход соответствующего элемента ЗАПРЕТ (8.01, 8.02 или 8.03) поступает логическая единица, инициируя открытие данного элемента ЗАПРЕТ и выдачу с его выхода значений  В зависимости от того, какой из элементов ЗАПРЕТ (8.01, 8.02 или 8.03) открыт, происходит дальнейшее вычисление математического ожидания и дисперсии конкретного типа однородного потока: если открыт элемент ЗАПРЕТ 8.03, поток признан простым и вычисления происходят в соответствии с выражением (2); если открыт элемент ЗАПРЕТ 8.01, поток признан сложным и вычисления происходят в соответствии с выражениями (4, 5); если открыт элемент ЗАПРЕТ 8.02, поток признан прореженным и вычисления происходят в соответствии с выражениями (7, 8).

В зависимости от того, какой из элементов ЗАПРЕТ (8.01, 8.02 или 8.03) открыт, происходит дальнейшее вычисление математического ожидания и дисперсии конкретного типа однородного потока: если открыт элемент ЗАПРЕТ 8.03, поток признан простым и вычисления происходят в соответствии с выражением (2); если открыт элемент ЗАПРЕТ 8.01, поток признан сложным и вычисления происходят в соответствии с выражениями (4, 5); если открыт элемент ЗАПРЕТ 8.02, поток признан прореженным и вычисления происходят в соответствии с выражениями (7, 8).

Появление значений  на выходе третьего элемента ЗАПРЕТ 8.03 означает, что в соответствии с выражением (2) математическое ожидание M[u

на выходе третьего элемента ЗАПРЕТ 8.03 означает, что в соответствии с выражением (2) математическое ожидание M[u (как значение математического ожидания M[u

(как значение математического ожидания M[u (как значение дисперсии D[u

(как значение дисперсии D[u

Появление значений  на выходе первого элемента ЗАПРЕТ 8.01 означает, что поток МПС признан блоком 4 сложным и вычисления производятся в соответствии с выражениями (4) - получение математического ожидания M[u

на выходе первого элемента ЗАПРЕТ 8.01 означает, что поток МПС признан блоком 4 сложным и вычисления производятся в соответствии с выражениями (4) - получение математического ожидания M[u в двоичном коде поступает на второй вход первичного электронного ключа 8.04, который, как и вторичный электронный ключ 8.05, в случае появления сигнала на одном (любом) из своих входов транслирует данный сигнал на выход электронного ключа. С выхода первичного электронного ключа 8.04 значения интенсивности

в двоичном коде поступает на второй вход первичного электронного ключа 8.04, который, как и вторичный электронный ключ 8.05, в случае появления сигнала на одном (любом) из своих входов транслирует данный сигнал на выход электронного ключа. С выхода первичного электронного ключа 8.04 значения интенсивности  в двоичном коде поступают на второй вход делителя математического ожидания 8.06, на первый вход которого с первого информационного входа 80 блока 8 подается в двоичном коде значение

в двоичном коде поступают на второй вход делителя математического ожидания 8.06, на первый вход которого с первого информационного входа 80 блока 8 подается в двоичном коде значение  В делителе математического ожидания 8.06 осуществляется процедура вычисления математического ожидания M[u

В делителе математического ожидания 8.06 осуществляется процедура вычисления математического ожидания M[u

M[u В сумматоре-умножителе 8.08 осуществляется процедура вычисления промежуточного значения

В сумматоре-умножителе 8.08 осуществляется процедура вычисления промежуточного значения  которое в двоичном коде поступает на второй вход вторичного электронного ключа 8.05 и, в соответствии с алгоритмом работы электронного ключа, на выход вторичного электронного ключа 8.05, а затем на второй вход делителя дисперсии 8.07. С первого информационного входа 80 блока 8 на первый и второй входы умножителя соотношений длин 8.09 подается в двоичном коле значение

которое в двоичном коде поступает на второй вход вторичного электронного ключа 8.05 и, в соответствии с алгоритмом работы электронного ключа, на выход вторичного электронного ключа 8.05, а затем на второй вход делителя дисперсии 8.07. С первого информационного входа 80 блока 8 на первый и второй входы умножителя соотношений длин 8.09 подается в двоичном коле значение  умножитель соотношений длин 8.09 осуществляет промежуточную процедуру возведения в квадрат

умножитель соотношений длин 8.09 осуществляет промежуточную процедуру возведения в квадрат  . С выхода умножителя соотношений длин 8.09 полученное значение

. С выхода умножителя соотношений длин 8.09 полученное значение  поступает на первый вход делителя дисперсии 8.07, который осуществляет окончательное вычисление дисперсии D[u

поступает на первый вход делителя дисперсии 8.07, который осуществляет окончательное вычисление дисперсии D[u

Появление значений  выходе второго элемента ЗАПРЕТ 8.02 означает, что поток МПС признан блоком 4 прореженным и вычисления производятся в соответствии с выражениями (7) - получение математического ожидания M[u

выходе второго элемента ЗАПРЕТ 8.02 означает, что поток МПС признан блоком 4 прореженным и вычисления производятся в соответствии с выражениями (7) - получение математического ожидания M[u в двоичном коде поступает на первый вход первичного электронного ключа 8.04. С выхода первичного электронного ключа 8.04 значения

в двоичном коде поступает на первый вход первичного электронного ключа 8.04. С выхода первичного электронного ключа 8.04 значения  в двоичном коде поступают на второй вход делителя математического ожидания 8.06, на первый вход которого с первого информационного входа 80 блока 8 подается в двоичном коде значение

в двоичном коде поступают на второй вход делителя математического ожидания 8.06, на первый вход которого с первого информационного входа 80 блока 8 подается в двоичном коде значение  В делителе математического ожидания 8.06 осуществляется процедура вычисления математического ожидания M[u

В делителе математического ожидания 8.06 осуществляется процедура вычисления математического ожидания M[u

Кроме того, с выхода элемента ЗАПРЕТ 8.02 значение интенсивности в двоичном коде поступает на первый вход вторичного электронного ключа 8.05, с выхода которого значение  поступает на второй вход делителя дисперсии 8.07, на первый вход которою с выхода умножителя соотношений длин поступает значение

поступает на второй вход делителя дисперсии 8.07, на первый вход которою с выхода умножителя соотношений длин поступает значение  Делитель дисперсии 8.07 осуществляет окончательное вычисление дисперсии D[u

Делитель дисперсии 8.07 осуществляет окончательное вычисление дисперсии D[u

Таким образом, по результатам сравнения, произведенного в блоке 4, путем подачи управляющего импульса на один из трех модификационных входов (821, 822 или 823) вычислителя математического ожидания и дисперсии 8, принимается решение о вычислении математического ожидания и дисперсии одной из разновидностей потоков МПС (простой, сложный или прореженный поток МПС).

Кроме того, тот же управляющий импульс поступает с одного из модификационных выходов (831, 832 или 833) вычислителя математического ожидания и дисперсии 8 на один из трех модификационных входов (53, 54 или 55) вычислителя распределения 5, где принимается решение о вычислении одного из аналитических выражений (1, 3 или 6) по значениям параметров  , поступающих с первого 86 и второго 87 информационных выходов блока 8 на первый 51 и второй 52 информационные входы вычислителя распределения 5. Вычисления могут быть проведены для различных значений количества пакетов (k), выбор значений осуществляется блоком управления 6 путем подачи на тактовый вход 56 блока 5 и на первый вход 510 элемента И 5.02 импульсов, количество которых соответствует заданному значению количества пакетов. Поступление на второй вход 511 элемента И 5.02 импульсов с первого информационного входа 51 блока 5 обеспечивает появление на выходе элемента И 5.02 управляющего сигнала, количество импульсов которого соответствует заданному значению количества пакетов. Данный сигнал, поступая на тактовый вход 506 арифметико-логического устройства 5.01, инициирует начало процедуры вычисления. Вычисленные значения плотности вероятности однородного потока МПС с выхода 59 вычислителя распределения 5 подаются в двоичном коде на выход "плотность вероятности" устройства.

, поступающих с первого 86 и второго 87 информационных выходов блока 8 на первый 51 и второй 52 информационные входы вычислителя распределения 5. Вычисления могут быть проведены для различных значений количества пакетов (k), выбор значений осуществляется блоком управления 6 путем подачи на тактовый вход 56 блока 5 и на первый вход 510 элемента И 5.02 импульсов, количество которых соответствует заданному значению количества пакетов. Поступление на второй вход 511 элемента И 5.02 импульсов с первого информационного входа 51 блока 5 обеспечивает появление на выходе элемента И 5.02 управляющего сигнала, количество импульсов которого соответствует заданному значению количества пакетов. Данный сигнал, поступая на тактовый вход 506 арифметико-логического устройства 5.01, инициирует начало процедуры вычисления. Вычисленные значения плотности вероятности однородного потока МПС с выхода 59 вычислителя распределения 5 подаются в двоичном коде на выход "плотность вероятности" устройства.

В случае, когда имеет место неоднородный (смешанный) поток МПС пользователей ЦСИО, когда источники смешанного типа выдают сообщения нерегулярно - одиночными ИСП или пачками ИСП с длинами, распределенными по геометрическому закону, расчет численных значений усредненного за интервал наблюдения параметра потока  происходит в блоке 3 так, как описано выше, а расчет численных значений параметра λc, характеризующего интенсивность потока, происходит следующим образом. Значения параметра λc в виде бинарной последовательности поступают на второй информационный вход 32 блока 3 для вычисления усредненного за интервал наблюдения параметра потока

происходит в блоке 3 так, как описано выше, а расчет численных значений параметра λc, характеризующего интенсивность потока, происходит следующим образом. Значения параметра λc в виде бинарной последовательности поступают на второй информационный вход 32 блока 3 для вычисления усредненного за интервал наблюдения параметра потока  и на вход 71 блока анализа интенсивности 7. Значения параметра λc поступают параллельно на информационный вход 701 схемы сравнения 7.01 блока 7, на вход ОЗУ 7.02 блока 7 и на информационный вход 706 вторичного элемента И 7.04 блока 7.

и на вход 71 блока анализа интенсивности 7. Значения параметра λc поступают параллельно на информационный вход 701 схемы сравнения 7.01 блока 7, на вход ОЗУ 7.02 блока 7 и на информационный вход 706 вторичного элемента И 7.04 блока 7.

В ОЗУ 7.02 хранится значение параметра λc на предыдущем шаге - значение λ1. С вспомогательного выхода 707 ОЗУ 7.02 значение λ1 поступает на вспомогательный вход 702 схемы сравнения 7.01, которая сравнивает значение предыдущего отсчета параметра (λ1) со значением последующего отсчета (λ2) - значением, поступившим на информационный вход 701 схемы сравнения 7.01. Сравнение производится по двум критериям:  Если значения отсчетов равны (λ1 = λ2), это подтверждает, что на входе устройства мы имеем однородный (несмешанный) поток МПС, а значит, схема сравнения 7.01 не выдает сигнал на управляющий выход 72 блока 7 и на сигнальные входы элементов И 7.03 и 7.04. Это значит, что на управляющий вход 35 блока 3 и на запрещающий вход элемента ЗАПРЕТ 3.03 блока 3 с выхода 72 блока 7 сигнал не поступает, следовательно, на выходе элемента ЗАПРЕТ 3.03 и на втором информационном выходе 34 блока 3 в двоичном параллельном коде имеем значение параметра

Если значения отсчетов равны (λ1 = λ2), это подтверждает, что на входе устройства мы имеем однородный (несмешанный) поток МПС, а значит, схема сравнения 7.01 не выдает сигнал на управляющий выход 72 блока 7 и на сигнальные входы элементов И 7.03 и 7.04. Это значит, что на управляющий вход 35 блока 3 и на запрещающий вход элемента ЗАПРЕТ 3.03 блока 3 с выхода 72 блока 7 сигнал не поступает, следовательно, на выходе элемента ЗАПРЕТ 3.03 и на втором информационном выходе 34 блока 3 в двоичном параллельном коде имеем значение параметра  и дальнейший расчет математического ожидания, дисперсии и плотности вероятности потоков сообщений происходит так, как описано выше.

и дальнейший расчет математического ожидания, дисперсии и плотности вероятности потоков сообщений происходит так, как описано выше.

Если значения отсчетов не равны (λ1≠λ2), это подтверждает, что на входе устройства мы имеем неоднородный (смешанный) поток МПС, а значит, схема сравнения 7.01 выдает сигнал на управляющий выход 72 блока 7 и на сигнальные входы элементов И 7.03 и 7.04. Сигнал с управляющего выхода 72 блока 7 поступает на управляющий вход 35 блока 3 и на запрещающий вход элемента ЗАПРЕТ 3.03, запирая его выход и не позволяя выдавать значения  на второй информационный вход 81 блока 8. С информационного выхода 708 ОЗУ 7.02 значение параметра λ1 поступает на информационный вход 704 первичного элемента И 7.03, а в ОЗУ записывается значение нового параметра. На информационном входе 706 вторичного элемента И 7.04 имеем значение λ2. Сигнал с выхода схемы сравнения 7.01, поступая на сигнальные входы 703 и 705 первичного и вторичного элементов И (7.03 и 7.04) соответственно, открывает эти устройства, позволяя получать на их выходах, а значит, и на первом 73 и втором 74 параметрических выходах блока 7 значения параметра λ1 и λ2 соответственно.

на второй информационный вход 81 блока 8. С информационного выхода 708 ОЗУ 7.02 значение параметра λ1 поступает на информационный вход 704 первичного элемента И 7.03, а в ОЗУ записывается значение нового параметра. На информационном входе 706 вторичного элемента И 7.04 имеем значение λ2. Сигнал с выхода схемы сравнения 7.01, поступая на сигнальные входы 703 и 705 первичного и вторичного элементов И (7.03 и 7.04) соответственно, открывает эти устройства, позволяя получать на их выходах, а значит, и на первом 73 и втором 74 параметрических выходах блока 7 значения параметра λ1 и λ2 соответственно.

Значения параметра λ1 и λ2 поступают соответственно на первый 841 и второй 842 параметрические входы вычислителя математического ожидания и дисперсии 8, в котором осуществляется вычисление математического ожидания Μ[uп] и дисперсии D[uп] неоднородного (смешанного) потока МПС на основе выражений (10) и (11) соответственно, причем наличие управляющего импульса на любом из трех модификационных входов 821-823 вычислителя математического ожидания и дисперсии 8 в этом случае роли не играет.

Значение параметра λ1 с первого параметрического выхода 73 блока 7 поступает на первый параметрический вход 841 блока 8, на первый вход сумматора неоднородного потока 8.10, на входы первичного 8.13 и вторичного 8.14 ПЗУ, на второй вход сумматора первичной интенсивности 8.15, на второй вход умножителя первичной интенсивности 8.16 и на первый параметрический выход 851 вычислителя математического ожидания и дисперсии 8. Значение параметра λ2 со второго параметрического выхода 74 блока 7 поступает на второй параметрический вход 842 блока 8, на первый вход делителя неоднородного потока 8.11, на первый вход умножителя значений степени 8.28, на n входов, где n≥40, первичного преобразователя степени 8.17 и на второй параметрический выход 852 вычислителя математического ожидания и дисперсии 8.

Вычисление математического ожидания Μ[uп] неоднородного (смешанного) потока МПС в вычислителе математического ожидания и дисперсии 8 происходит следующим образом. На второй вход делителя неоднородного потока 8.11 с первого информационною входа 80 блока 8 поступает в двоичном коде значение  делитель неоднородного потока 8.11 на основании значений

делитель неоднородного потока 8.11 на основании значений  производит промежуточное вычисление

производит промежуточное вычисление  полученное значение поступает на второй вход сумматора неоднородного потока 8.10, в котором производится окончательное вычисление значений математического ожидания неоднородного (смешанного) потока МПС Μ[uп] в соответствии с выражением (10). С выхода сумматора неоднородного потока 8.10 полученное значение математического ожидания неоднородного потока МПС Μ[uп] в двоичном коде поступает на первый и второй входы граничного умножителя 8.12, на первый главный выход 88 вычислителя математического ожидания и дисперсии 8 и на выход "математическое ожидание" устройства.

полученное значение поступает на второй вход сумматора неоднородного потока 8.10, в котором производится окончательное вычисление значений математического ожидания неоднородного (смешанного) потока МПС Μ[uп] в соответствии с выражением (10). С выхода сумматора неоднородного потока 8.10 полученное значение математического ожидания неоднородного потока МПС Μ[uп] в двоичном коде поступает на первый и второй входы граничного умножителя 8.12, на первый главный выход 88 вычислителя математического ожидания и дисперсии 8 и на выход "математическое ожидание" устройства.

Вычисление дисперсии D[uп] неоднородного (смешанного) потока МПС в вычислителе математического ожидания и дисперсии 8 происходит следующим образом. Значение параметра λ1, поступающее на входы первичного 8.13 и вторичного 8.14 ПЗУ, является для данных ПЗУ сигналом считывания, причем в первичном ПЗУ 8.13 хранится и подается на выход при получении сигнала считывания (λ1) значение 1 (единица), а во вторичном ПЗУ 8.14 хранится и подается на выход при получении сигнала считывания (λ1) значение числа е (е=2,71828). При получении сигнала считывания на своем входе первичный ПЗУ 8.13 выдает значение 1 (единица) на первый вход сумматора первичной интенсивности 8.15, на второй вход промежуточного сумматора 8.21 и на второй вход сумматора 8.23. Сумматор первичной интенсивности 8.15 осуществляет процедуру сложения (1+λ1), полученный результат с выхода сумматора первичной интенсивности 8.15 в двоичном коде поступает на первый вход умножителя первичной интенсивности 8.16, где осуществляется процедура вычисления в соответствии с выражением λ1(1+λ1), а также на первый вход вычислителя произведения 8.20 и на второй вход промежуточного умножителя 8.22.

Полученные значения λ1(1+λ1), с выхода умножителя первичной интенсивности 8.16 в двоичном коде поступают на первый вход умножителя первого порядка 8.27, на второй вход которого с n выходов, где n≥40, первичного преобразователя степени 8.17 поступает значение  вычисление которого осуществляется в первичном преобразователе степени 8.17. Первичный 8.17 и вторичный 8.18 преобразователи степени могут быть реализованы в виде однократно программируемых ПЗУ в соответствии со схемой, предложенной на фиг.3.

вычисление которого осуществляется в первичном преобразователе степени 8.17. Первичный 8.17 и вторичный 8.18 преобразователи степени могут быть реализованы в виде однократно программируемых ПЗУ в соответствии со схемой, предложенной на фиг.3.

Вычисление значений  в первичном преобразователе степени 8.17 происходит следующим образом. На разрешающий вход блока 8.17 с выхода вторичного ПЗУ 8.14 поступает значение е (е=2,71828), на n входов блока 8.17, где n≥40, поступают значения показателя степени λ2, причем совпадение значений сигнала на j-ом входе, где j=0, 1, 2, 3,..., n, со значениями показателя степени (λ2, но со знаком "минус"), хранящимися в j-ой ячейке памяти ПЗУ, инициирует выдачу с j-го выхода первичного преобразователя степени 8.17 запрограммированного значения

в первичном преобразователе степени 8.17 происходит следующим образом. На разрешающий вход блока 8.17 с выхода вторичного ПЗУ 8.14 поступает значение е (е=2,71828), на n входов блока 8.17, где n≥40, поступают значения показателя степени λ2, причем совпадение значений сигнала на j-ом входе, где j=0, 1, 2, 3,..., n, со значениями показателя степени (λ2, но со знаком "минус"), хранящимися в j-ой ячейке памяти ПЗУ, инициирует выдачу с j-го выхода первичного преобразователя степени 8.17 запрограммированного значения  . Умножитель первого порядка 8.27 осуществляет процедуру умножения полученных в блоках 8.16 и 8.17 значений. С выхода умножителя первого порядка 8.27 полученные значения

. Умножитель первого порядка 8.27 осуществляет процедуру умножения полученных в блоках 8.16 и 8.17 значений. С выхода умножителя первого порядка 8.27 полученные значения  в двоичном коде поступают на первый вход предварительного сумматора 8.25.

в двоичном коде поступают на первый вход предварительного сумматора 8.25.

Вычислитель произведения 8.20 на основании полученных значений  осуществляет вычисление значений

осуществляет вычисление значений  которые в двоичном коде подаются на первый вход умножителя вторичной интенсивности 8.19 и на n входов, где n≥40, вторичного преобразователя степени 8.18, осуществляющего в соответствии с изложенным выше алгоритмом процедуру вычисления значений

которые в двоичном коде подаются на первый вход умножителя вторичной интенсивности 8.19 и на n входов, где n≥40, вторичного преобразователя степени 8.18, осуществляющего в соответствии с изложенным выше алгоритмом процедуру вычисления значений  - промежуточных значений, необходимых для вычисления выражения (11).

- промежуточных значений, необходимых для вычисления выражения (11).

С n выходов, где n≥40, вторичного преобразователя степени 8.18 полученные значения в двоичном коде поступают на второй вход умножителя вторичной интенсивности 8.19, с выхода которого полученные значения произведения

поступают в двоичном коде на второй вход умножителя второго порядка 8.29, на первый вход которого поступают значения произведения (λ2e), полученные в умножителе значений степени 8.28. Умножитель второго порядка 8.29 реализует вычисление промежуточного выражения

в соответствии с выражением (11). С выхода умножителя второго порядка 8.29 полученные значения произведения

в двоичном коде поступают на второй вход предварительного умножителя 8.24, на первый вход которого с выхода сумматора 8.23 поступают в двоичном коде численные значения, полученные на основе реализации в сумматоре 8.23 выражения

На первый вход сумматора 8.23 поступают в двоичном коде численные значения, полученные на основе реализации в промежуточном умножителе 8.22 выражения  На первый вход промежуточного умножителя 8.22 поступают в двоичном коде численные значения, полученные на основе реализации в промежуточном сумматоре 8.21 выражения

На первый вход промежуточного умножителя 8.22 поступают в двоичном коде численные значения, полученные на основе реализации в промежуточном сумматоре 8.21 выражения  на второй вход промежуточного умножителя 8.22 подано с выхода блока 8.15 значение (1+λ1). На вторые входы промежуточного сумматора 8.21 и сумматора 8.23 с выхода первичного ПЗУ 8.13 подано значение 1 (единица).

на второй вход промежуточного умножителя 8.22 подано с выхода блока 8.15 значение (1+λ1). На вторые входы промежуточного сумматора 8.21 и сумматора 8.23 с выхода первичного ПЗУ 8.13 подано значение 1 (единица).

В предварительном умножителе 8.24 вычисляется произведение значений суммы

и произведения

полученных в блоках 8.23 и 8.29 соответственно. Полученные значения произведения с выхода предварительного

умножителя 8.24 поступают в двоичном коде на второй вход предварительного сумматора 8.25, где происходит сложение значений произведения

и произведения

полученных в блоках 8.29 и 8.24 соответственно. С выхода предварительного сумматора 8.25 полученные значения в двоичном коде поступают на второй вход оконечного сумматора 8.26, на первый вход которого с выхода граничного умножителя 8.12 поступают значения возведенного в квадрат математического ожидания неоднородного потока МПС

В оконечном сумматоре 8.26 осуществляется окончательное вычисление дисперсии неоднородного потока МПС в соответствии с выражением (11). С выхода оконечного сумматора 8.26 полученное значение дисперсии неоднородного потока МПС D[uп] в двоичном коде поступает на второй главный выход 89 вычислителя математического ожидания и дисперсии 8 и на выход "дисперсия" устройства.

Кроме того, значения параметров λ1 и λ2 с первого 851 и второго 852 параметрических выходов вычислителя математического ожидания и дисперсии 8 поступают соответственно на первый 57 и второй 58 параметрические входы вычислителя распределения 5, а затем на первый 507 и второй 508 параметрические входы арифметико-логического устройства 5.01, которое вычисляет значения плотности вероятности неоднородного (смешанного) потока МПС в соответствии с аналитическим выражением (9), причем наличие управляющего импульса на любом из трех модификационных входов 53-55 вычислителя распределения 5 в этом случае роли не играет. Вычисленные значения плотности вероятности неоднородного (смешанного) потока МПС с выхода 59 вычислителя распределений 5 подаются в двоичном коде на выход "плотность вероятности" устройства.

В итоге, на первом главном выходе 88 блока 8 и на выходе "математическое ожидание" устройства имеем записанные в двоичном коде значения математического ожидания либо однородного простого M[u

Таким образом, анализ принципа работы заявляемого устройства для параметрической опенки закона распределения потоков сообщений показывает очевидность того факта, что наряду с сохраненными возможностями оценивания плотности вероятности как однородных (несмешанных), так и неоднородных (смешанных) потоков сообщений устройство способно производить текущую оценку математического ожидания и дисперсии числа ИСП, поступающих в ЦСИО за период наблюдения, - ключевых параметров, необходимых для определения вероятностно-временных характеристик потоков МПС, циркулирующих в ЦСИО. Данное устройство позволяет получать в динамике оценочные значения основных параметров закона распределения - математического ожидания, дисперсии и плотности вероятности разнородных (однородных и неоднородных) потоков МПС, циркулирующих в ЦСИО, что существенно расширяет область применения устройства, расширяет функциональные возможности аппаратуры, где заявленное устройство для параметрической оценки закона распределения потоков сообщений будет использовано.

Источники информации

1. Лебедев А.Н., Куприянов М.С., Недосекин Д.Д. и др. Вероятностные методы в инженерных задачах. Справочник. - СПб.: Энергоатомиздат, 2000. - 333 с.

2. Выгодский М.Я. Справочник по высшей математике. - М.: Джангар, 2000. - 864 с.

3. Советов Б.Я., Яковлев С.А. Построение сетей интегрального обслуживания. - Л.: Машиностроение, 1990. - 332 с.

4. Овчаров Л.А. Прикладные задачи теории массового обслуживания. - М.: Машиностроение, 1969. - 324 с.

5. Советов Б.Я., Рухман Е.Л., Яковлев С.А. Системы передачи информации от терминалов к ЦВМ. - Л.: изд. Ленингр. ун-та, 1978. - 240 с.

6. Гусев В.В., Лебедев О.Н., Сидоров А.М. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1996. - 247 с.

7. Миловзоров В.П. Элементы информационных систем. - М.: Высшая школа, 1989. - 440 с.

8. Дроздов Е.А., Комарницкий В.А., Пятибратов А.П. Электронно-вычислительные машины Единой системы. - М.: Машиностроение, 1981.

9. Фролкин В. Т. , Попов Л.Н. Импульсные и цифровые устройства. - М.: Радио и связь, 1992. - 335 с.

10. Алексеенко А. Г. Основы микросхемотехники. - М.: Советское радио, 1977. - 408 с.

11. Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. - 352 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 1999 |

|

RU2165100C2 |

| УСТРОЙСТВО ДЛЯ ПАРАМЕТРИЧЕСКОЙ ОЦЕНКИ ЗАКОНА РАСПРЕДЕЛЕНИЯ ПОТОКОВ СООБЩЕНИЙ | 2005 |

|

RU2279125C1 |