00

а 41

Од

сл

1

Изобретение относится к вычисли тельной технике и может быть использовано в цифровых системах передачи информации, использующих сверточный код и содержащих декодер Витерби.

Цель изобретения - упрощение устройства.

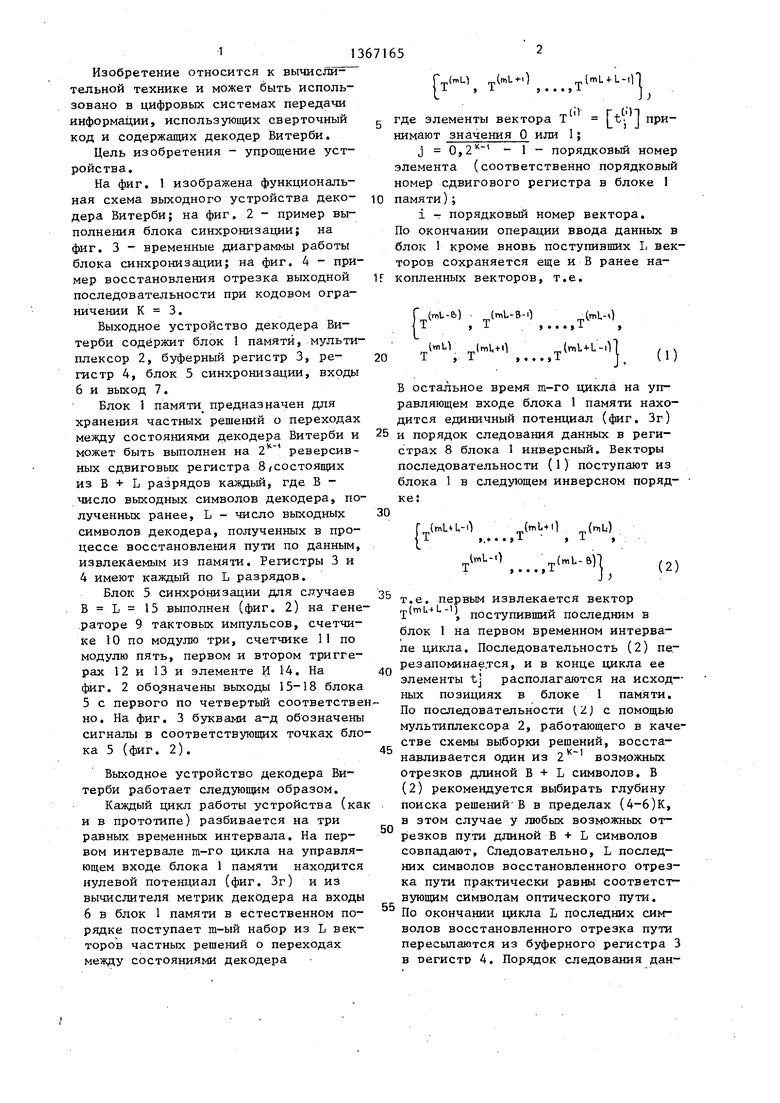

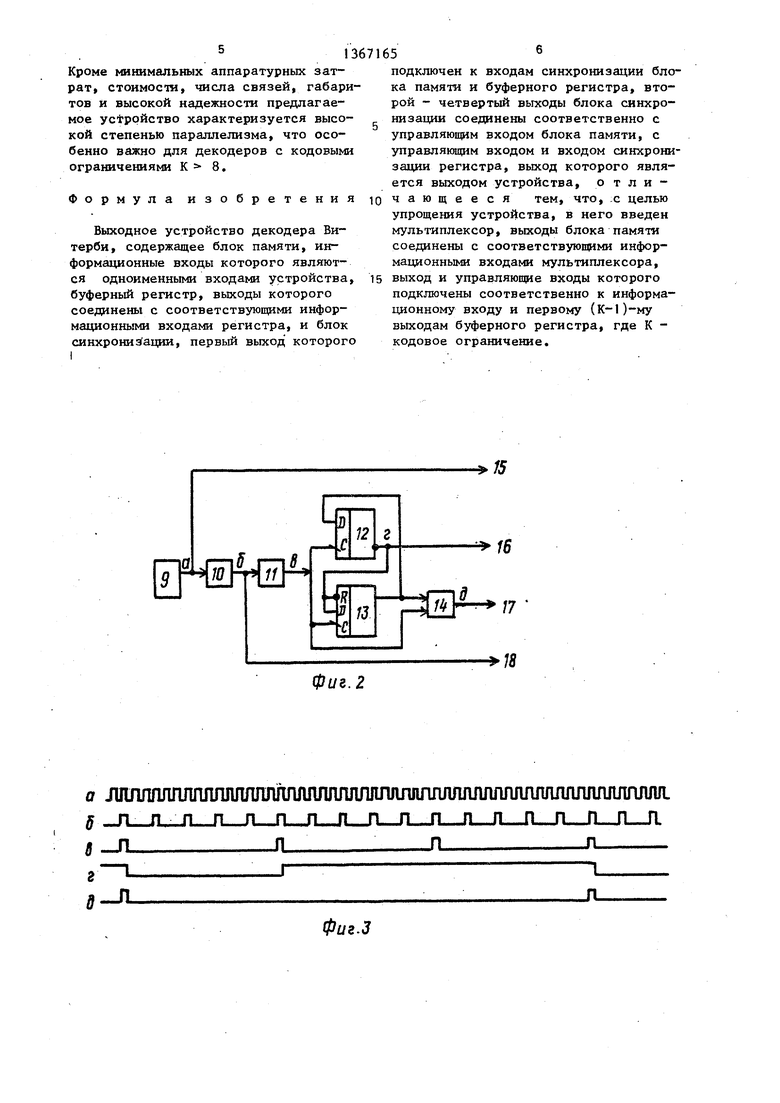

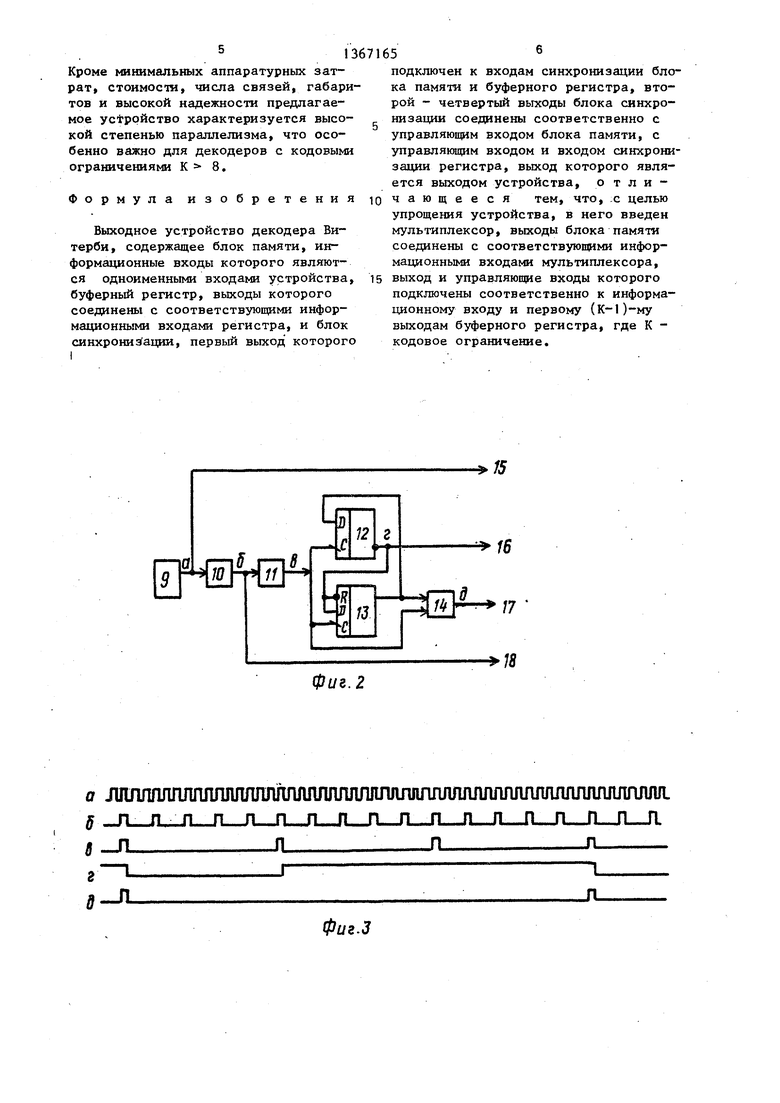

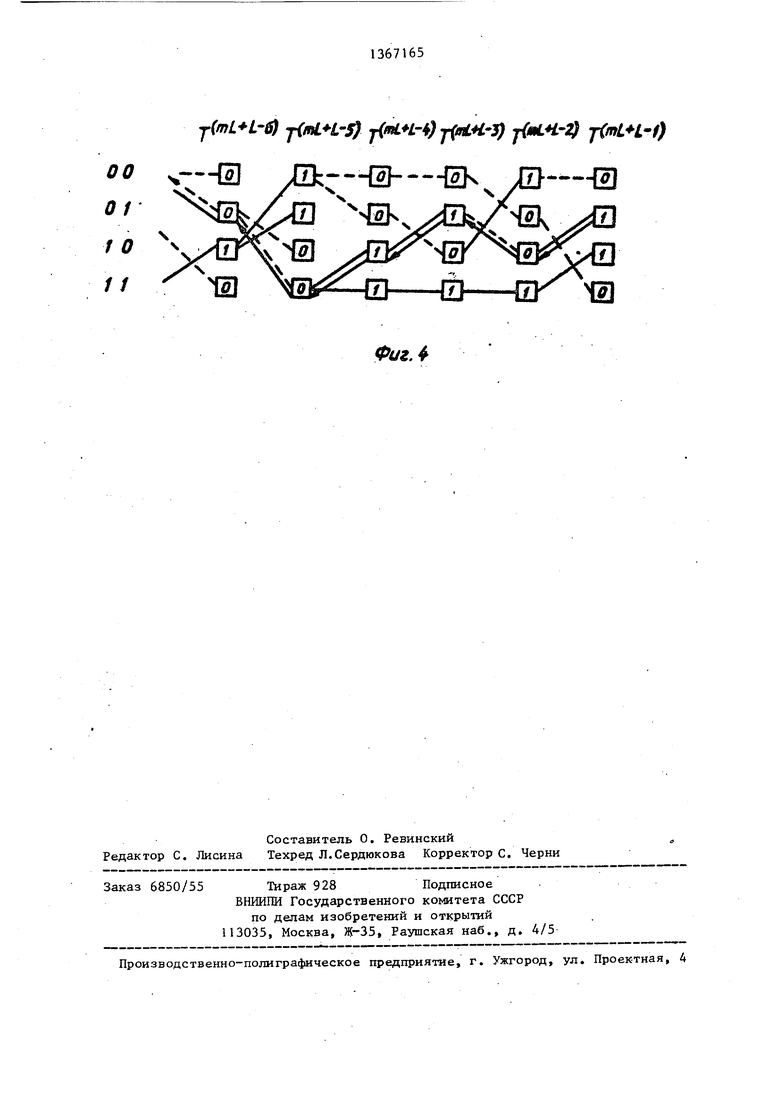

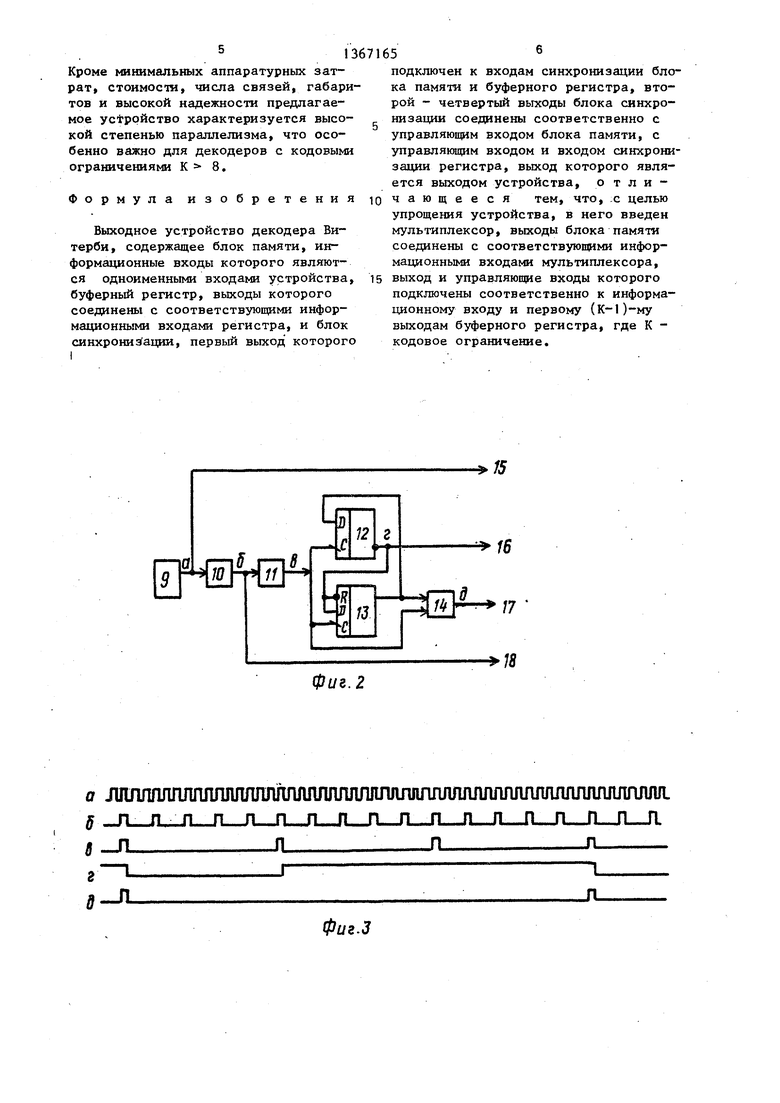

На фиг. 1 изображена функциональная схема выходного устройства декодера Витерби; на фиг. 2 - пример выполнения блока синхронизации; на фиг. 3 - временные диаграммы работы блока синхронизации; на фиг. 4 - пример восстановления отрезка выходной последовательности при кодовом ограничении К 3.

Выходное устройство декодера Витерби содержит блок 1 памяти, мультиплексор 2, буферный регистр 3, регистр 4, блок 5 синхронизации, входы 6 и выход 7.

БЛОК 1 памяти предназначен для хранения частных решений о перехода между состояниями декодера Витерби и может быть выполнен на 2 реверсивных сдвиговых регистра 8/состоящих из В + L разрядов каждый, где В - число выходных символов декодера, плученных ранее, L - число выходных символов декодера, полученных в процессе восстановления пути по данным извлекаемым из памяти. Регистры 3 и

4имеют каждый по L разрядов.

Блок 5 синхронизации для случаев В L 15 выполнен (фиг. 2) на генраторе 9 тактовых импульсов, счетчике 10 по модулю три, счетчике 11 по модулю пять, первом и втором триггерах 12 и 13 и элементе И 14. На фиг. 2 обозначены выходы 15-18 блок

5с первого по четвертый соответств но. На фиг. 3 буквами а-д обозначен сигналы в соответствующих точках блка 5 (фиг. 2).

Выходное устройство декодера Витерби работает следующим образом.

Каждый цикл работы устройства (ка и в прототипе) разбивается на три равных временных интервала. На первом интервале т-го цикла на управляющем входе блока 1 памяти находится нулевой потенциал (фиг. Зг) и из вычислителя метрик декодера на входы 6 в блок 1 памяти в естественном порядке поступает т-ый набор из L векторов частных решений о переходах между состояниями декодера

(«ц ) (mL4-L- ,i ,...,1

,

n

пригде элементы вектора Т нимают значения О или 1;

j 0, - 1 - порядковый номер элемента (соответственно порядковый номер сдвигового регистра в блоке 1 памяти);

i - порядковьй номер вектора. По окончании операции ввода данных в блок 1 кроме вновь поступивших L векторов сохраняется еще и В ранее накопленных векторов, т.е.

(mi-e,}

(ml-B-0 „(mlM) .

(niLV

(ml + O

I « ) X

(mL-t-L - 1.

(1)

в остальное время m-ro цикла на управляющем входе блока 1 памяти находится единичный потенциал (фиг. Зг) 25 и порядок следования данных в регистрах 8 блока 1 инверсный. Векторы последовательности (1) поступают из блока 1 в следующем инверсном порядке;

( -L L-il(mL4i (ц.)

.

UL-.) (mL-6 1 , . . . , 1

,

5

т.е. первым извлекается вектор т , поступивший последним в блок 1 на первом временном интервале цикла. Последовательность (2) пе- резапоминае.тся, и в конце цикла ее элементы t располагаются на исходных позициях в блоке 1 памяти. По последовательности (2) с помощью мультиплексора 2, работающего в каче45

стве схемы выборки решений, восста1 K-t

50

55

навливается один из 2 возможных отрезков длиной В + L символов. В (2) рекомендуется выбирать глубину поиска решений В в пределах (4-6)К, в этом случае у любых возможных отрезков пути длиной В + L символов совпадают. Следовательно, L последних символов восстановленного отрезка пути практически равны соответствующим символам оптического пути. По окончании цикла L последних символов восстановленного отрезка пути пересьтаются из буферного регистра 3 в регистр 4. Порядок следования данных в регистре 4 - инверсный по отношению к буферному регистру 3.

В устройстве для адресации содержимого блока 1 памяти ирпользуется содержимое первых К-1 разрядов буферного регистра 3. Такая возможность частичного совмещения функций адресации памяти решений и упорядочения результатов следует из определения частных решений. Действительно, согласно алгоритму (2) независимо от номера итерации частные решения с порядковыми номерами 2 j и 2 J + 1

поступаюш 1м в буферный регистр 3 на i-OM шаге, следующий разряд адреса равен частному решению, поступившему в буферный регистр 3 на (i-l)-OM шаге, и т.д. Таким образом, адрес содержимого блока I равен содержимому первых К-1 разрядов буферного регистра 3.

Процедура восстановления выходной последовательности декодера при кодовом ограничении К 3 иллюстрируется численным примером, представленным на фиг. 4. Здесь в квадратах ука

| название | год | авторы | номер документа |

|---|---|---|---|

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ РТСМ | 2008 |

|

RU2390930C2 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1425680A2 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛИРОВАНИЯ И ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ | 1996 |

|

RU2172566C2 |

| Устройство для декодирования блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1543552A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ, КОДИРОВАННЫХ В РАЗНЫХ ФОРМАТАХ | 1996 |

|

RU2171548C2 |

| УСТРОЙСТВО ПРИЕМА ИНФОРМАЦИИ ИЗ КАНАЛА | 1998 |

|

RU2137320C1 |

Изобретение относится к вычислительной технике. Его использование в цифровых системах передачи информации сверточным кодом, содержащих декодер Витерби, обеспечивает упрощение устройства. Выходное устройство декодера Витерби содерямт блок 1 памяти, буферный и выходной регистры 3, 4 и блок 5 синхронизации. Благодаря введению мультиплексора 2 частично совмещаются функции адресации памяти решений и упорядочения выходных символов, что и позволяет упростить устройство. 4 ил. с (Л

Из (3) следует, частное решение t,;, ) равно нулю

единице к-7.

(либо tjj,, )

если предпочтительнее j-e (2 + + j)-e состояние декодера. Иначе: значение частного решения (либо 7 ) равно старшему разряду двоичного представления порядкового номера предпочтительного состояния декодера. Если на i-OM шаге процедуры восстановления выходной последова- тельности декодера прочитанное из

(mL+L- i)

блока 1 значение t

равно нулю (единице), то очередной символ должен быть равен нулю (единице соответственно), т.е. совпадает с частln

HBiM решением t

а адрес содер- 50

яммого блока 1 памяти на (1+1)-ом

.„M/fnl

шаге должен стать равным о и р

+ 2

k-г

В предлагаемом устройстве, в отличие от прототипа, функции адресации памяти решений и упорядочет1Я выходных символов частично совмещены. При условии L К-1, которое выполняется

соответственно). Значит, стар- практаке, не требуется отдельного

блока памяти для формирования адреса памяти решений, как в прототипе, годаря чему и упрощается устройство.

ший разряд двоичного представления

lmL4Ul):

адреса равен частному решению и совпадает с очередным символом.

35

40

Из примера видно, что старший (младший) разряд (1 + 1)-го адреса памяти решения совпадает с 1-ым ((i- 1)-ым соответственно) символом выходной последовательности. Так, третий, четвертый, пятый и шестой адреса равны

45

13

Кроме минимальных аппаратурных затрат, стоимости, числа связей, габаритов и высокой надежности предлагаемое устройство характеризуется высокой степенью параллелизма, что особенно важно для декодеров с кодовыми ограничениями К 8.

Формула изобретения

Выходное устройство декодера Ви- терби, содержащее блок памяти, информационные входы которого являются одноименными входами устройства, буферный регистр, выходы которого соединены с соответствующими информационными входами регистра, и блок синхрониэ(ации, первый выход которого I

0

Фиг.2

а JшnпплJгпnшlШlЛЛЛjflnnшшлял lлш Jlшшшu

gППП п

в

JL

Фиг.З

56

подключен к входам синхронизации блока памяти и буферного регистра, второй - четвертый выходы блока синхронизации соединены соответственно с управляющим входом блока памяти, с управлякшщм входом и входом синхронизации регистра, выход которого является выходом устройства, отличающееся тем, что, с целью упрощения устройства, в него введен мультиплексор, выходы блока памяти соединены с соответствующими информационными входами мультиплексора, выход и управляющие входы которого подключены соответственно к информационному входу и первому (К-1)-му выходам буферного регистра, где К - кодовое ограничение.

п

j( j mL4 ff j{mL4 ) ) -jimL -l)

00 01 f 0

11

Фиг. 4

| Некоторые вопросы теории кодирования, /Под ред | |||

| Э | |||

| Л | |||

| Блоха и М | |||

| С | |||

| Шнскера | |||

| М.: Мир, 1970, с | |||

| Рогульчатое веретено | 1922 |

|

SU142A1 |

| Витерби А | |||

| Д | |||

| Смура Дя | |||

| К | |||

| Принципы цифровой связи и кодирования | |||

| М.: Радио и связь, 1982 | |||

| Патент США № 3789360, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

Авторы

Даты

1988-01-15—Публикация

1985-11-04—Подача