Изобретение относится к области вычислительной техники, а именно к вычислительным системам на основе микропроцессоров с динамической памятью.

Известен контроллер памяти, контролирующий кэшируемую динамическую память, который использует схему транслятора адреса, меняющую местами младшие адреса тега физического адреса данных в подсистеме памяти микропроцессорной системы таким образом, чтобы при обращении к основной динамической младший бит тега соответствовал биту банка для системы динамической памяти, состоящей из двух банков. Это делается с целью снижения количества последовательных обращений в один и тот же банк памяти при обращении к данным с соседними внутренними физическими адресами (Патент US 10457609, кл. G06F 12/08, опубл. 2008).

Известна также схема индексирования банков, меняющая местами биты адреса внутренней физической памяти таким образом, чтобы повысить частоту последовательного попадания в страницы основной динамической памяти. В этой схеме предпочтительно использовать для перестановки младшие биты адреса тега. (Патент US 6070227, кл. G06F 12/00, опубл. 2004).

Наиболее близким по технической сути и достигаемому результату является устройство обработки информации, включающее динамическую память более чем с одним банком динамической памяти, буфер адреса, первую адресную шину, вторую адресную шину, связанную с выходом буфера адреса и с адресным входом динамической памяти (Патент US 7159067 В2, кл. G06F 12/12, опубл. 13.05.2004).

Недостатком описанного выше устройства является низкая производительность и недостаточная универсальность микропроцессора при работе с динамической памятью, сложность процесса отладки микропроцессорной системы.

Технический результат, ожидаемый от использования изобретения, заключается в увеличении производительности и универсальности микропроцессора при работе с динамической памятью, а также упрощении процесса отладки микропроцессорной системы.

Указанный технический эффект достигается тем, что в устройстве обработки информации, включающем динамическую память более чем с одним банком динамической памяти, буфер адреса, первую адресную шину, вторую адресную шину, связанную с выходом буфера адреса и с адресным входом динамической памяти, устройство дополнительно имеет блок центрального процессора с шиной управления перезагрузкой, кэш-память с шиной конфигурации кэш-памяти, схему управления, конфигурационный регистр, анализатор конфигурации с шиной управления мультиплексорами, мультиплексоры адреса с шиной конфигурации мультиплексоров, причем шина управления мультиплексорами связана с выходом управления мультиплексорами конфигурационного регистра и с входом анализатора конфигурации, а шина конфигурации мультиплексоров связана с выходом анализатора конфигурации и управляющим входом мультиплексоров адреса, при этом первая адресная шина связана с адресным выходом блока центрального процессора, с адресным входом кэш-памяти и с входом мультиплексоров адреса, а также тем, что шина конфигурации кэш-памяти связана с выходом конфигурации кэш-памяти конфигурационного регистра и с входом управления конфигурацией кэш-памяти, и тем, что шина управления перезагрузкой связана с выходом управления перезагрузкой схемы управления и с входом перезагрузки блока центрального процессора для управления очисткой основной динамической памяти и кэш-памяти при смене конфигурации мультиплексоров адреса.

Наличие схемы управления, связанной с блоком центрального процессора, позволяет принудительно перезагружать микропроцессорную систему, очищая основную динамическую память и кэш-память при смене конфигурации устройства обработки информации без отключения устройства, что увеличивает универсальность микропроцессора при работе с динамической памятью.

Конфигурационный регистр, связанный с кэш-памятью, и анализатор конфигурации, связанный с конфигурационным регистром, а также мультиплексоры адреса, связанные управляющей шиной конфигурации мультиплексоров с анализатором конфигурации, позволяют изменять конфигурацию устройства обработки информации, в частности задавать конфигурацию мультиплексоров адреса таким образом, чтобы адресное пространство внутренней физической памяти и основной динамической памяти совпадали, что приводит к упрощению процесса отладки микропроцессорной системы.

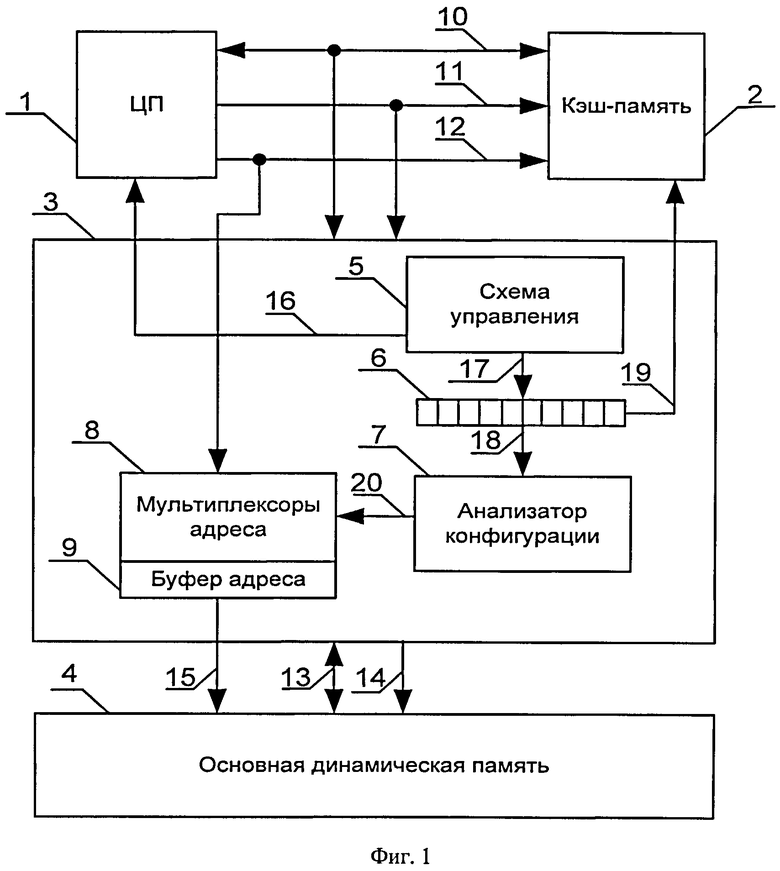

Изобретение поясняется фиг.1, где представлена блок-схема устройства обработки информации.

Устройство обработки информации состоит из блока центрального процессора 1, кэш-памяти 2, универсального контроллера динамической памяти 3, основной динамической памяти 4. Универсальный контроллер динамической памяти 3 содержит схему управления 5, конфигурационный регистр 6, анализатор конфигурации 7, мультиплексоры адреса 8 и буфер адреса 9.

Блок центрального процессора 1 связан с кэш-памятью 2 и универсальным контроллером динамической памяти 3 внутренней шиной команд 10, внутренней шиной данных 11 и внутренней шиной адреса 12. Универсальный контроллер динамической памяти 3 связан с основной динамической памятью 4 внешней шиной команд 13, внешней шиной данных 14 и внешней шиной адреса 15. Схема управления 5 связана с блоком центральных процессоров 1 шиной управления перезагрузкой 16 и с конфигурационным регистром шиной записи конфигурации 17. Конфигурационный регистр 6 связан с анализатором конфигурации 7 шиной конфигурации мультиплексоров 18 и с кэш-памятью 2 шиной конфигурации кэш-памяти 19. Анализатор конфигурации 7 связан с мультиплексорами адреса 8 шиной управления мультиплексорами 20.

Устройство работает следующим образом. Реконфигурация параметров работы микропроцессорной системы с кэш-памятью 2, или основной памятью 4 осуществляется с помощью схемы управления 5 пользователем. Задается набор данных, записываемых с помощью шины записи конфигурации 17 в конфигурационный регистр 6, а также при необходимости принудительной очистки основной динамической памяти 4 и кэш-памяти 2 с помощью шины управления перезагрузкой 16 отдается команда блоку центрального процессора 1 на перезагрузку микропроцессорной системы и, таким образом, очистку основной динамической памяти 4 и кэш-памяти 2. По шине конфигурации мультиплексоров 18 данные, записанные в конфигурационный регистр 6, передаются в анализатор конфигурации 7, который с помощью шины управления мультиплексорами 20 формирует конфигурацию мультиплексоров адреса 8.

Преобразование команд внутренней шины команд 10 в команды внешней шины команд 13, а также преобразование данных внутренней шины данных 11 в данные внешней шины данных 14 осуществляется контроллером динамической памяти 3.

Внутренняя шина адреса 12 преобразовывается во внешнюю шину адресам 15 с помощью мультиплексоров адреса 8 и буфера адреса 9. Адрес на внутренней шине адреса 12 состоит из двух частей - индекса и тега. Индекс определяет адрес области в кэш-памяти 2, содержащей данные. Тег определяет признак данных в кэш-памяти 2.

Изменения в адресе на внутренней шине адреса 12 для преобразования его в адрес на внешней шине адреса 15 вносятся следующим образом: происходит перестановка местами разрядов на внутренней шине адреса 12, относящихся к области индекса и к области тега. Перестановка осуществляется таким образом, чтобы при локальных обращениях с разным индексом, а также при доступе к основной динамической памяти 4 во время операции обратной записи, где индекс совпадает, но тэги отличаются, в соседних обращениях с высокой долей вероятности адресовались разные банки основной динамической памяти 4. Это позволяет снизить количество последовательных обращений в один банк основной динамической памяти 4, которые требуют дополнительной команды предзаряда банка и таким образом снижают быстродействие подсистемы динамической памяти, используемой в микропроцессорных системах.

В случае отключения функции перестановки битов адреса с помощью мультиплексоров адреса 8 и буфера адреса 9 внешняя шина адреса 15 совпадает с внутренней шиной адреса 12.

Таким образом, применение мультиплексоров адреса 8, не использующих логических выражений для вычисления битов адреса позволяет повысить скорость обмена данными между кэш-памятью 2 и основной памятью микропроцессора 4 (и как следствие, увеличить производительность подсистемы памяти) при различных конфигурациях подсистемы памяти микропроцессорной системы, а также упрощает анализ используемого пространства адресов при отладке подсистемы памяти и при использовании низкоуровневых языков программирования, так как использует для преобразования внутренней шины адреса 12 во внешнюю шину адреса 15 перестановку битов внутренней шины адреса 12 с использованием мультиплексоров адреса 8 и буфер адреса 9.

В процессе отладки подсистемы динамической памяти возможно задание конфигурации мультиплексоров адреса 8 с помощью шины управления мультиплексорами 20 таким образом, чтобы адрес на внутренней шине адреса 12 соответствовал адресу на внешней шине адреса 15, что упрощает процесс отладки.

В процессе эксплуатации микропроцессорной системы с помощью шины управления перезагрузкой 16 возможно задание блоку центрального процессора 1 схемой управления 5 команды на перезагрузку микропроцессорной системы и, таким образом, очистку данных в основной динамической памяти 4 и кэш-памяти 2, что позволяет без отключения устройства обработки информации и микропроцессорной системы изменять конфигурацию подсистемы памяти, что делает микропроцессор более универсальным, позволяя смену элементов подсистемы памяти в процессе эксплуатации.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО БУФЕРИЗАЦИИ ПОТОКОВ ДАННЫХ, СЧИТЫВАЕМЫХ ИЗ ОЗУ | 2011 |

|

RU2475817C1 |

| ПОДСИСТЕМА ПАМЯТИ ЯДРА МИКРОПРОЦЕССОРА | 2011 |

|

RU2475822C1 |

| МИКРОПРОЦЕССОР ГИБРИДНЫЙ | 2007 |

|

RU2359315C2 |

| УСТРОЙСТВО ДИНАМИЧЕСКОГО ПРЕДСКАЗАНИЯ КОМАНД УСЛОВНОГО ПЕРЕХОДА МИКРОПРОЦЕССОРА | 2012 |

|

RU2503996C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| ИЗМЕРИТЕЛЬНОЕ СРЕДСТВО ДЛЯ ФУНКЦИЙ АДАПТЕРА | 2010 |

|

RU2523194C2 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| СПОСОБ ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ И УСТРОЙСТВО ЗАПОЛНЕНИЯ КЭШ-ПАМЯТИ КОМАНД И ВЫДАЧИ КОМАНД НА ВЫПОЛНЕНИЕ | 2014 |

|

RU2592465C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

Изобретение относится к вычислительным системам на основе микропроцессоров с динамической памятью. Техническим результатом является увеличение производительности микропроцессора при работе с динамической памятью и в упрощении процесса отладки микропроцессорной системы. Устройство обработки информации содержит динамическую память более чем с одним банком динамической памяти, буфер адреса, первую адресную шину, вторую адресную шипу, связанную с выходом буфера адреса и с адресным входом динамической памяти, блок центрального процессора с шиной управления перезагрузкой, кэш-память с шиной конфигурации кэш-памяти, схему управления, конфигурационный регистр, анализатор конфигурации с шиной управления мультиплексорами, мультиплексоры адреса с шиной конфигурации мультиплексоров. 2 з.п. ф-лы, 1 ил.

1. Устройство обработки информации, включающее динамическую память более чем с одним банком динамической памяти, буфер адреса, первую адресную шину, вторую адресную шину, связанную с выходом буфера адреса и с адресным входом динамической памяти, отличающееся тем, что устройство дополнительно имеет блок центрального процессора с шиной управления перезагрузкой, кэш-память с шиной конфигурации кэш-памяти, схему управления, конфигурационный регистр, анализатор конфигурации с шиной управления мультиплексорами, мультиплексоры адреса с шиной конфигурации мультиплексоров, причем шина управления мультиплексорами связана с выходом управления мультиплексорами конфигурационного регистра и с входом анализатора конфигурации, а шина конфигурации мультиплексоров связана с выходом анализатора конфигурации и управляющим входом мультиплексоров адреса, при этом первая адресная шина связана с адресным выходом блока центрального процессора, с адресным входом кэш-памяти и с входом мультиплексоров адреса.

2. Устройство по п.1, отличающееся тем, что шина конфигурации кэш-памяти связана с выходом конфигурации кэш-памяти конфигурационного регистра и с входом управления конфигурацией кэш-памяти.

3. Устройство по п.1, отличающееся тем, что шина управления перезагрузкой связана с выходом управления перезагрузкой схемы управления очисткой основной динамической памяти и кэш-памяти при смене конфигурации мультиплексоров адреса.

| US 2004093458 A1, 13.05.2004 | |||

| СПОСОБ И УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 2006 |

|

RU2346320C2 |

| ВЫРАВНИВАНИЕ СЕТЕВОЙ НАГРУЗКИ С ПОМОЩЬЮ УПРАВЛЕНИЯ СОЕДИНЕНИЕМ | 2004 |

|

RU2387002C2 |

| US 6070227 A, 30.05.2000. | |||

Авторы

Даты

2013-04-27—Публикация

2011-12-08—Подача