Изобретение относится к автоматике и может быть использовано для построения дискретных устройств повышенной надежности.

Целью изобретения является повышение устойчивости работы устройства при одновременном расширении функциональных возможностей.

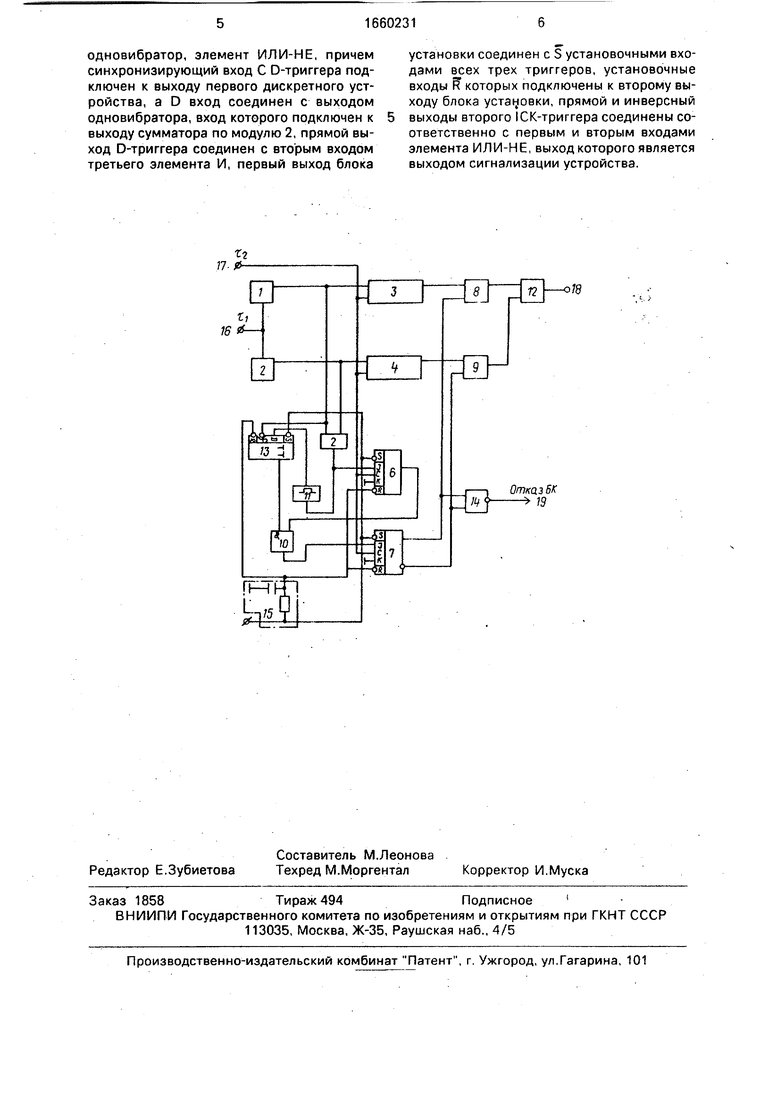

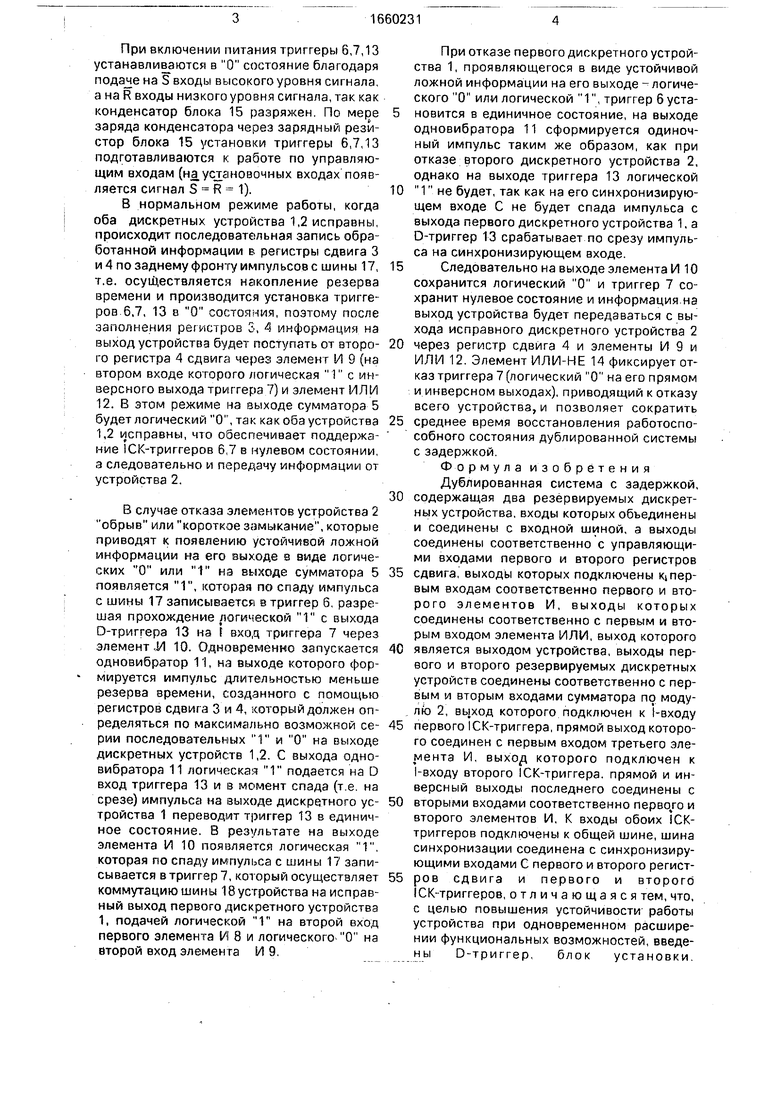

На чертеже приведена схема дублированной системы с задержкой.

Дублированная система с задержкой содержит два резервированных устройства 1,2, два регистра сдвига 3,4, сумматор 5 по модулю 2, два 1СК-триггера 6,7, три элемента И 8 - 10, одновибратор 11, элемент ИЛИ 12, D-триггер 13, элемент ИЛИ-НЕ 14, блок установки 15, вход 16 дискретных устройств, шину 17 синхронизации, выходные шины 18, 19.

В качестве D-триггера могут быть использованы синхронные триггеры, переключающиеся на срезе тактового импульса

Назначение вводимых элементов:

одновибратор 11 - для формирования импульса в случае отказа одного из дискретных устройств 1-го или 2-го,

блок установки 15 - для установки триггеров в О состояния и может содержать конденсатор и зарядный резистор;

D-триггер 13 - для формирования логической 1 при отказе второго дискретного устройства 2 и логического О при отказе первого дискретного устройства 1;

элемент ИЛИ-НЕ 14 - для сигнализации отказа второго ICK-триггера 7 (логического О на его прямом и инверсном выходе), приводящего к отказу всего устройства.

Дублированная система с задержкой работает следующим образом

о

ю со

При включении питания триггеры 6,7,13 устанавливаются в О состояние благодаря подаче на S входы высокого уровня сигнала, а на R входы низкого уровня сигнала, так как конденсатор блока 15 разряжен. По мере заряда конденсатора через зарядный резистор блока 15 установки триггеры 6,7,13 подготавливаются к работе по управляющим входам (на.установочных входах появляется сигнал S R 1).

В нормальном режиме работы, когда оба дискретных устройства 1,2 исправны, происходит последовательная запись обработанной информации в регистры сдвига 3 и4 по заднему фронту импульсов с шины 17, т.е. осуществляется накопление резерва времени и производится установка триггеров 6,7, 13 в О состояния, поэтому после заполнения регистров 3, 4 информация на выход устройства будет поступать от второго регистра 4 сдвига через элемент И 9 (на втором входе которого логическая 1 с инверсного выхода триггера 7) и элемент ИЛИ 12. В этом режиме на выходе сумматора 5 будет логический О, так как оба устройства 1,2 исправны, что обеспечивает поддержание 1СК-триггеров 6,7 в нулевом состоянии, а следовательно и передачу информации от устройства 2.

В случае отказа элементов устройства 2 обрыв или короткое замыкание, которые приводят к появлению устойчивой ложной информации на его выходе в виде логических О или 1 на выходе сумматора 5 появляется 1, которая поспаду импульса с шины 17 записывается в триггер 6, разрешая прохождение логической 1 с выхода О-триггера 13 на I вход триггера 7 через элемент-И 10. Одновременно запускается одновибратор 11, на выходе которого формируется импульс длительностью меньше резерва времени, созданного с помощью регистров сдвига 3 и 4, который должен определяться по максимально возможной серии последовательных 1 и О на выходе дискретных устройств 1,2. С выхода одно- вибратора 11 логическая 1 подается на D вход триггера 13 и в момент спада (т е. на срезе) импульса на выходе дискретного устройства 1 переводит триггер 13 в единичное состояние. В результате на выходе элемента И 10 появляется логическая 1, которая по спаду импульса с шины 17 записывается в триггер 7, который осуществляет коммутацию шины 18 устройства на исправный выход первого дискретного устройства 1, подачей логической 1 на второй вход первого элемента И 8 и логического О на второй вход элемен га И 9.

При отказе первого дискретного устройства 1, проявляющегося в виде устойчивой ложной информации на его выходе -логического О или логической 1, триггер бустановится в единичное состояние, на выходе одновибратора 11 сформируется одиночный импульс таким же образом, как при отказе второго дискретного устройства 2, однако на выходе триггера 13 логической

0 1 не будет, так как на его синхронизирующем входе С не будет спада импульса с выхода первого дискретного устройства 1, а D-триггер 13 срабатывает по срезу импульса на синхронизирующем входе.

5 Следовательно на выходе элемента И 10 сохранится логический О и триггер 7 сохранит нулевое состояние и информация на выход устройства будет передаваться с выхода исправного дискретного устройства 2

0 через регистр сдвига 4 и элементы И 9 и ИЛИ 12. Элемент ИЛИ-НЕ 14 фиксирует отказ триггера 7 (логический О на его прямом и инверсном выходах), приводящий к отказу всего устройства, и позволяет сократить

5 среднее время восстановления работоспособного состояния дублированной системы с задержкой.

Формула изобретения Дублированная система с задержкой,

0 содержащая два резервируемых дискретных устройства, входы которых объединены и соединены с входной шиной, а выходы соединены соответственно с управляющими входами первого и второго регистров

5 сдвига, выходы которых подключены первым входам соответственно первого и вто- рого элементов И, выходы которых соединены соответственно с первым и вторым входом элемента ИЛИ, выход которого

0 является выходом устройства, выходы первого и второго резервируемых дискретных устройств соединены соответственно с первым и вторым входами сумматора по модулю 2, выход которого подключен к 1-входу

5 первого ICK-триггера, прямой выход которого соединен с первым входом третьего элемента И, выход которого подключен к 1-входу второго ICK-триггера. прямой и инверсный выходы последнего соединены с

0 вторыми входами соответственно первого и второго элементов И, К входы обоих СК- триггеров подключены к общей шине, шина синхронизации соединена с синхронизирующими входами С первого и второго регист5 ров сдвига и первого и второго ICK-триггеров, отличающаяся тем, что, с целью повышения устойчивости работы устройства при одновременном расширении функциональных возможностей, введены D-триггер, блок установки

одновибратор, элемент ИЛИ-НЕ, причем синхронизирующий вход С D-триггера подключен к выходу первого дискретного устройства, a D вход соединен с выходом одновибратора, вход которого подключен к выходу сумматора по модулю 2, прямой выход D-триггера соединен с вторым входом третьего элемента И, первый выход блока

установки соединен с S установочными входами всех трех триггеров, установочные входы F которых подключены к второму выходу блока установки, прямой и инверсный выходы второго ICK-триггера соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, выход которого является выходом сигнализации устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДУБЛИРОВАННАЯ СИСТЕМА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 1999 |

|

RU2153786C1 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Устройство для контроля регистра сдвига | 1980 |

|

SU911530A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| Устройство для контроля лоических блоков | 1986 |

|

SU1453409A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1288700A1 |

| Устройство для функционального контроля вычислительных машин | 1983 |

|

SU1134943A1 |

| Кодовый трансмиттер | 1985 |

|

SU1339883A1 |

| Устройство для контроля логических блоков | 1983 |

|

SU1142837A1 |

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

Изобретение относится к автоматике и может быть использовано для построения дискретных устройств повышенной надежности. Цель изобретения - повышение устойчивости работы устройства при одновременном расширении функциональных возможностей - достигается введением D-триггера 13, блока установки 15, одновибратора 11, элемента ИЛИ-НЕ 14. Устройство также содержит резервированные устройства 1, 2, регистры 3, 4 сдвига, сумматор 5 по модулю 2, ICK-триггера 6, 7, элементы И 8 - 10, элемент ИЛИ 12, вход 16 дискретных устройств, шину 17 синхронизации, выходные шины 18, 19. 1 ил.

| Кейджан Г.А | |||

| Прогнозирование надежности микроэлектронной аппаратуры на основе БИС - М.: Радио и связь, 1987, с | |||

| Способ образования азокрасителей на волокнах | 1918 |

|

SU152A1 |

| Авторское свидетельство СССР № 1538758, кл | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1991-06-30—Публикация

1989-04-03—Подача