Изобретение относится к средствам вычислительной техники, предназначено для получения собственных значений путем приведения исходной матрицы к специальной форме и может быть использовано для решения задач цифровой обработки сигналов и изображений в специализированных вычислительных системах, работающих в режиме реального времени.

Известно устройство для определения модуля трехмерного вектора, содержащее первый, второй и третий регистры, первый, второй и третий сумматоры-вычитатели, первый и второй коммутаторы, первый дешифратор знака операндов и вход номера итерации, причем информационные выходы первого, второго и третьего сумматоров-вычитателей соединены с информационными входами соответственно первого, второго и третьего регистров, управляющие входы первого и второго коммутаторов соединены с входом номера итерации устройства, и обеспечивающее определение модуля трехмерного вектора (А.с. 1142830, Мкл. G 06 F 7/544, 1985).

Недостатком данного устройства является наличие входа номера итерации, что требует подключения внешних схем управления и усложняет управление устройством.

Наиболее близким к изобретению является устройство для определения модуля трехмерного вектора, содержащее три регистра, три коммутатора, блок изменения знака, дешифратор, три арифметических блока, два сумматора-вычитателя и блок памяти констант, причем первый и второй входы первого вычитателя i-го арифметического блока (i = 1, 3) являются первым и вторым информационными входами i-го арифметического блока, выход первого сумматора-вычитателя i-го арифметического блока соединен с первым входом второго сумматора-вычитателя блока, выход которого является выходом i-го арифметического блока, пятый информационный вход которого соединен с вторым входом второго сумматора-вычитателя блока, управляющие входы первого и второго сумматоров-вычитателей блока являются первым и вторым знаковыми входами i-го арифметического блока, первый выход первого регистра соединен с первым информационным входом первого арифметического блока, второй и пятый информационные входы которого соединены соответственно с первым выходом первого коммутатора и первым выходом третьего коммутатора, выход первого арифметического блока соединен с первым информационным входом первого регистра, вторые выходы первого, второго и третьего регистров соединены соответственно с информационными входами первого, второго и третьего коммутаторов, выход второго арифметического блока соединен с информационным входом блока изменения знака, первый выход третьего коммутатора соединен с вторым информационным входом третьего арифметического блока (А.с. 2040039, Мкл. G 06 F 7/544, 1995).

Недостатком данного устройства является наличие арифметических блоков, выполняющих преобразование отдельных компонент вектора, что не обеспечивает решения задачи вычисления собственных значений матриц и ограничивает область применения устройства.

Данные устройства имеют невысокий технический уровень, обусловленный наличием арифметических блоков, которые предназначены для обработки отдельных компонент трехмерных векторов, тем самым не могут обеспечить параллельной обработки компонент матрицы, что приводит к увеличению времени нахождения собственных значений, снижению производительности и увеличению аппаратурных затрат при решении задач цифровой обработки сигналов и изображений.

В этой связи важнейшей задачей является создание нового устройства для вычисления собственных значений матриц с новым блоком преобразования матрицы для параллельной обработки ее компонентов. Блок преобразования матрицы осуществляет последовательные преобразования исходной матрицы с фиксированными аргументами, что позволяет выполнить эти преобразования за один такт с любой наперед заданной точностью. Полученные в результате преобразования значения используются для обновления компонент преобразуемой матрицы.

Техническим результатом заявленного устройства является расширение функциональных возможностей при решении задач, требующих нахождения собственных значений большого числа матриц в реальном масштабе времени, а именно возможность нахождения собственных значений матриц в виде единой макрооперации за счет введения нового блока преобразования матрицы. Это позволяет повысить производительность при решении задач цифровой обработки сигналов и упрощает управление устройством.

Сущность изобретения заключается в том, что в устройство для вычисления собственных значений матриц, содержащее четыре регистра, четыре коммутатора, блок памяти констант и блок управления, причем выходы первого, второго, третьего и четвертого регистров соединены соответственно с информационными входами первого, второго, третьего и четвертого коммутаторов, вход и выход блока управления соединены соответственно с входом начала вычисления и выходом завершения вычисления, управляющие входы первого, второго, третьего и четвертого регистров соединены с первым управляющим выходом блока управления, выход номера итерации которого соединен с входом блока памяти констант, выход которого соединен с управляющими входами первого, второго, третьего и четвертого коммутаторов, введен блок преобразования матрицы, первый и двенадцатый информационные входы которого соединены соответственно с первым и вторым выходами четвертого коммутатора, второй и четвертый информационные входы блока преобразования матрицы соединены соответственно с первым и вторым выходами первого коммутатора, одиннадцатый, девятый, пятый и третий информационные входы блока преобразования матрицы соединены соответственно с выходами первого, второго, третьего и четвертого регистров, восьмой и шестой информационные входы блока преобразования матрицы соединены соответственно с первым и вторым выходами второго коммутатора, седьмой и десятый информационные входы блока преобразования матрицы соединены соответственно с первым и вторым выходами третьего коммутатора, первый и второй управляющие входы блока преобразования матрицы соединены соответственно с вторым и третьим управляющими выходами блока управления, первый, второй, третий и четвертый выходы блока преобразования матрицы соединены соответственно с информационными входами четвертого, третьего, второго и первого регистров.

Блок преобразования матрицы содержит три вычитателя, семь сумматоров-вычитателей и три элемента сложения по модулю два, причем первый и второй информационные входы блока преобразования матрицы соединены соответственно с первым и вторым входами первого вычитателя, выход которого соединен с первыми входами первого, второго и третьего элементов сложения по модулю два и с вторыми информационными входами пятого и шестого сумматоров-вычитателей, третий и четвертый информационные входы блока преобразования матрицы соединены соответственно с первым и вторым информационными входами первого сумматора-вычитателя, выход которого соединен с первым информационным входом четвертого сумматора-вычитателя, пятый и шестой информационные входы блока преобразования матрицы соединены соответственно с первым и вторым входами второго вычитателя, выход которого соединен с первым информационным входом пятого сумматора-вычитателя, седьмой и восьмой информационные входы блока преобразования матрицы соединены соответственно с первым и вторым информационными входами второго сумматора-вычитателя, выход которого соединен с вторыми входами первого, второго и третьего элементов сложения по модулю два и с вторыми информационными входами четвертого и седьмого сумматоров-вычитателей, девятый и десятый информационные входы блока преобразования матрицы соединены соответственно с первым и вторым входами третьего вычитателя, выход которого соединен с первым информационным входом шестого сумматора-вычитателя, одиннадцатый и двенадцатый информационные входы блока преобразования матрицы соединены соответственно с первым и вторым информационными входами третьего сумматора-вычитателя, выход которого соединен с первым информационным входом седьмого сумматора-вычитателя, первый управляющий вход блока преобразования матрицы соединен с управляющими входами первого, второго и третьего сумматоров-вычитателей и с третьим входом второго элемента сложения по модулю два, второй управляющий вход блока преобразования матрицы соединен с третьим входом третьего элемента сложения по модулю два, выход первого элемента сложения но модулю два соединен с управляющим входом пятого сумматора-вычитателя, выход второго элемента сложения по модулю два соединен с управляющим входом четвертого сумматора-вычитателя, выход третьего элемента сложения по модулю два соединен с управляющими входами шестого и седьмого сумматоров-вычитателей, выход четвертого, пятого, шестого и седьмого сумматоров-вычитателей соединены соответственно с первым, вторым, третьим и четвертым выходами блока преобразования матрицы.

Блок управления содержит генератор импульсов, два элемента И, два триггера, счетчик и два дешифратора, причем вход начала вычисления блока управления соединен с входом установки первого триггера и инвертирующим входом первого элемента И, выход которого соединен с входом сброса первого триггера, инверсный выход которого соединен с выходом завершения вычисления блока управления, прямой выход первого триггера соединен с вторым входом второго элемента И, выход генератора импульсов соединен с первым входом второго элемента И, выход которого соединен с первым управляющим выходом блока управления и входом счетчика, выход которого соединен с выходом номера итерации блока управления и входами первого и второго дешифраторов, выход первого дешифратора соединен с входом установки второго триггера, выход второго дешифратора соединен с неинвертирующим входом первого элемента И и входом сброса второго триггера, прямой и инверсный выходы которого соединены соответственно с вторым и третьим управляющими выходами блока управления.

Проведенный заявителем анализ уровня техники, включающий поиск по патентам и научно-техническим источникам информации и выявление источников, содержащих сведения об аналогах заявленного решения, позволил установить, что заявителем не обнаружен аналог, характеризующийся признаками, идентичными всем существенным признакам заявленного изобретения. Определение из перечня выявленных аналогов прототипа как наиболее близкого решения по совокупности признаков позволило выявить совокупность существенных по отношению к усматриваемому заявителем техническому результату отличительных признаков в заявленном объекте, изложенных в формуле изобретения.

Следовательно, заявленное требование соответствует требованию "новизна" по действующему законодательству.

Для проверки соответствия заявленного изобретения требованию "изобретательского уровня" заявитель провел дополнительный поиск известных решений с целью выявления признаков, совпадающих с отличными от прототипа признаками заявленного изобретения, результаты которого показывают, что заявленное изобретение для специалиста не следует из известного уровня техники.

Следовательно, заявленное изобретение соответствует требованию "изобретательский уровень".

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - схема блока преобразования матрицы; на фиг. 3 - схема блока управления.

Устройство для вычисления собственных значений матриц (фиг. 1) содержит с первого по четвертый регистры 1-4, с первого по четвертый коммутаторы 5-8, блок 9 преобразования матрицы, блок 10 памяти констант, блок 11 управления, а также вход 12 начала вычисления и выход 13 завершения вычисления.

Блок преобразования матрицы (фиг. 2) содержит первый вычитатель 14, первый сумматор-вычитатель 15, второй вычитатель 16, второй сумматор-вычитатель 17, третий вычитатель 18, третий сумматор-вычитатель 19, с первого по третий элементы 20-22 сложения по модулю два, с пятого по седьмой сумматоры-вычитатели 23-26, а также с первого по двенадцатый входы 27-38 информационные, первый и второй входы 39-40 управляющие и с первого по четвертый выходы 41-44 информационные.

Первый 27 и второй 28 информационные входы блока 9 преобразовать матрицы соединены соответственно с первым и вторым входами первого вычитателя 14, выход которого соединен с первыми входами первого 20, второго 21 и третьего 22 элементов сложения по модулю два и с вторыми информационными входами пятого 24 и шестого 25 сумматоров-вычитателей. Третий 29 и четвертый 30 информационные входы блока 9 преобразования матрицы соединены соответственно с первым и вторым информационными входами первого сумматора-вычитателя 15, выход которого соединен с первым информационным входом четвертого сумматора-вычитателя 23. Пятый 31 и шестой 32 информационные входы блока 9 преобразования матрицы соединены соответственно с первым и вторым входами второго вычитателя 16, выход которого соединен с первым информационным входом пятого сумматора-вычитателя 24. Седьмой 33 и восьмой 34 информационные входы блока 9 преобразования матрицы соединены соответственно с первым и вторым информационными входами второго сумматора-вычитателя 17, выход которого соединен с вторыми входами первого 20, второго 21 и третьего 22 элементов сложения по модулю два и с вторыми информационными входами четвертого 23 и седьмого 26 сумматоров-вычитателей. Девятый 35 и десятый 36 информационные входы блока 9 преобразования матрицы соединены соответственно с первым и вторым входами третьего вычитателя 18, выход которого соединен с первым информационным входом шестого сумматора-вычитателя 25. Одиннадцатый 37 и двенадцатый 38 информационные входы блока 9 преобразования матрицы соединены соответственно с первым и вторым информационными входами третьего сумматора-вычитателя 19, выход которого соединен с первым информационным входом седьмого сумматора-вычитателя 26. Первый управляющий вход 39 блока 9 преобразования матрицы соединен с управляющими входами первого 15, второго 17 и третьего 19 сумматоров-вычитателей и с третьим входом второго элемента 21 сложения по модулю два. Второй управляющий вход 40 блока 9 преобразования матрицы соединен с третьим входом третьего элемента 22 сложения по модулю два. Выход первого элемента 20 сложения по модулю два соединен с управляющим входом пятого сумматора-вычитателя 24. Выход второго элемента 21 сложения по модулю два соединен с управляющим входом четвертого сумматора-вычитателя 23. Выход третьего элемента 22 сложения по модулю два соединен с управляющими входами шестого 25 и седьмого 26 сумматоров-вычитателей. Выходы четвертого 23, пятого 24, шестого 25 и седьмого 26 сумматоров-вычитателей соединены соответственно с первым 41, вторым 42, третьим 43 и четвертым 44 выходами блока 9 преобразования матрицы.

Блок управления (фиг. 3) состоит из генератора 45 импульсов, первого элемента И 46, первого триггера 47, второго элемента И 48, счетчика 49, первого и второго дешифраторов 50 и 51, второго триггера 52. Кроме того, имеются первый выход 53 управляющий, выход 54 номера итерации, второй и третий выходы 55 и 56 управляющие, вход 12 начала вычисления и выход 13 завершения вычисления.

Вход 12 начала вычисления соединен с входом установки первого триггера 47 и инвертирующим входом первого элемента И 46, выход которого соединен с входом сброса первого триггера 47, инверсный выход которого соединен с выходом 13 завершения вычисления. Прямой выход первого триггера 47 соединен с вторым входом второго элемента И 48. Выход генератора 45 импульсов соединен с первым входом второго элемента И 48, выход которого соединен с первым управляющим выходом 53 блока 11 управления и входом счетчика 49, выход которого соединен с выходом 54 номера итерации блока 11 управления и входами первого 50 и второго 51 дешифраторов. Выход первого дешифратора 50 соединен с входом установки второго триггера 52. Выход второго дешифратора 51 соединен с неинвертирующим входом первого элемента И 46 и входом сброса второго триггера 52, прямой и инверсный выходы которого соединены соответственно с вторым 55 и третьим 56 управляющими выходами блока 11 управления.

Выход первого регистра 1 (фиг. 1) соединен с одиннадцатым информационным входом блока 9 преобразования матрицы и информационным входом первого коммутатора 5, первый и второй выходы которого соединены соответственно со вторым и четвертым информационными входами блока 9 преобразования матрицы. Выход второго регистра 2 соединен с девятым информационным входом блока 9 преобразования матрицы и информационным входом второго коммутатора 6. первый и второй выходы которого соединены соответственно с восьмым и шестым информационными входами блока 9 преобразования матрицы. Выход третьего регистра 3 соединен с пятым информационным входом блока 9 преобразования матрицы и информационным входом третьего коммутатора 7, первый и второй выходы которого соединены соответственно с седьмым и десятым информационными входами блока 9 преобразования матрицы. Выход четвертого регистра 4 соединен с третьим информационным входом блока 9 преобразования матрицы и информационным входом четвертою коммутатора 8, первый и второй выходы которого соединены соответственно с первым и двенадцатым информационными входами блока 9 преобразования матрицы. Четвертый, третий, второй и первый выходы блока 9 преобразования матрицы соединены соответственно с информационными входами первого, второго, третьего и четвертого регистров 1-4, управляющие входы которых соединены с первым управляющим выходом блока 11 управления. Выход номера итерации блока 11 управления соединен со входом блока 10 памяти констант, выход которого соединен с управляющими входами первого, второго, третьего и четвертого коммутаторов 5-8. Второй и третий управляющие выходы блока 11 управления соединены соответственно с первым и вторым управляющими входами блока 9 преобразования матрицы.

Предложенное устройство выполняет последовательные преобразования исходной матрицы с фиксированными аргументами, что позволяет привести матрицу к одному из специальных видов, а именно диагональному или блочно-диагональному, и получить ее собственные значения с любой наперед заданной точностью.

Устройство функционирует следующим образом.

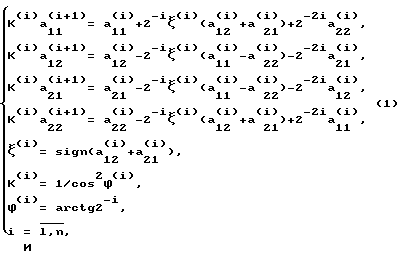

Работа устройства выражается зависимостями

Вычисление собственных значений матрицы производится последовательно но зависимостям (1) и (2).

Начальными значениями являются компоненты исходной матрицы, собственные значения которой необходимо получить.

Перед началом итерационного процесса в регистры 1, 2, 3 и 4 соответственно асинхронно заносятся компоненты а22, а21, a12 и a11 исходной матрицы (фиг. 1). После этого необходимо сформировать импульс на входе 12 начала вычисления. С началом очередной итерации с выхода номера итерации блока 11 управления подается сигнал на блок 10 памяти констант, с выхода которого параметр i зависимостей (1) и (2) поступает на управляющие входы коммутаторов 5, 6, 7 и 8, настраивая их таким образом, чтобы с их первого выхода снималось число (а22, а21, a12 и a11 соответственно), сдвинутое на i разрядов в сторону младших разрядов, а с второго - на 2i разрядов в сторону младших разрядов. Таким образом, на информационные входы с первого по двенадцатый блока 9 преобразования матрицы подаются a11(i)2-i, a22(i)2-i, a11(i), a22(i)2-2i, a12(i), a21(i)2-2i, a12(i)2-i, a21(i)2-i, a21(i), a12(i)2-2i, a22(i) и a11(i)2-2i, а с выходов с первого по четвертый получают a11(i+1), a12(i+1), a21(i+1) и a22(i+1), которые записываются в регистры 4, 3, 2 и 1 соответственно. Второй и третий управляющие выходы блока 11 управления подаются соответственно на первый и второй управляющие входы блока 9 преобразования матрицы и настраивают его на paбoту по зависимостям (1) или (2). После выполнения всех итераций матрица обращается в диагональную или блочно-диагональную форму, ее компоненты содержат искомые собственные значения, а на выходе 13 завершения вычисления устанавливается активный высокий уровень. Вычисленные собственные значения хранятся в регистрах 1-4.

Блок 9 преобразования матрицы функционирует следующим образом (фиг. 2).

На выходах первого вычитателя 14, первого сумматора-вычитателя 15, второго вычитателя 16, второго сумматора-вычитателя 17, третьего вычитателя 18 и третьего сумматора-вычитателя 19 получают соответственно (a11(i) - a22(i))2-i, (a11(i) + τ a22(i)2-2i), (a12(i) - a21(i)2-2i), (a12(i) + τ a21(i))2-i), (a21(i) - a12(i)2-2i) и (a22(i) + τ a11(i))2-2i), где τ = 1 или τ = -1 в зависимости от подаваемого на первый управляющий вход 39 значения. При τ = 1 происходит вычисление по зависимости (1), а при τ = -1 - по зависимости (2). Подаваемое на второй управляющий вход 40 значение всегда противоположно значению на первом управляющем входе 39. На выходах с первого по третий элементов 20, 21 и 22 сложения по модулю два формируются соответственно ξ(i),τξ(i) и -τξ(i), которые настраивают с четвертого по седьмой сумматоры-вычитатели 23, 24, 25 и 26 таким образом, что на их выходах получают a11(i+1), a12(i+1), a21(i+1) и a22(i+1).

Блок 11 управления функционирует следующим образом (фиг. 3).

Сначала первый 47 и второй 52 триггеры сброшены. Подачей импульса на вход 12 начала вычисления устанавливается первый триггер 47, и его прямой выход разрешает прохождение тактовых импульсов от генератора 45 импульсов через второй элемент И 48. Тактовые импульсы увеличивают значение счетчика на 1. Значение счетчика является номером итерации и поступает на выход 54 номера итерации. Первый 50 и второй 51 дешифраторы проверяют итерацию па равенство первым итерациям зависимостей (1) и (2) соответственно, устанавливая и сбрасывая второй триггер 52, прямой и инверсный выходы которого являются соответственно вторым 55 и третьим 56 управляющими выходами блока 11 управления. После выполнения последней итерации счетчик 49 сбрасывается. Это приводит к срабатыванию второго дешифратора 51 и инициирует сброс первого триггера 47, что, в свою очередь, приводит к запрещению передачи тактовых импульсов от генератора 45 импульсов на вход счетчика 49 через второй элемент И 48. Инверсный выход первого триггера является выходом 13 завершения вычисления, который устанавливается до начала следующего вычисления. Вычисление собственных значений завершено.

Таким образом, вышеизложенное свидетельствует о выполнении при использовании заявленного устройства следующих совокупных условий:

- устройство для вычисления собственных значений матриц, воплощающее заявленное изобретение при его осуществлении, предназначено для применения в системах цифровой обработки сигналов и изображений для вычисления собственных значений матриц, тем самым расширяя функциональные возможности при решении задач, требующих нахождения собственных значений большого числа матриц в реальном масштабе времени;

- для заявленного изобретения в том виде, как оно охарактеризовано в формуле изобретения, подтверждена возможность его осуществления в соответствии с описанием и предлагаемым чертежом;

- устройство для вычисления собственных значений матриц, воплощающее заявленное изобретение при его осуществлении, способно обеспечить достижение усматриваемого заявителем технического результата.

Следовательно, заявленное изобретение соответствует требованию "промышленная применимость".

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СКОЛЬЗЯЩЕГО СПЕКТРА | 1998 |

|

RU2125291C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| Устройство для вычисления модуля трехмерного вектора | 1989 |

|

SU1672442A1 |

| Процессор цифровой обработки сигналов | 1990 |

|

SU1789991A1 |

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| Устройство для цифровой обработки сигналов | 1985 |

|

SU1336028A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ КООРДИНАТ | 1991 |

|

RU2007749C1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ КОДОВ РИДА-СОЛОМОНА | 2010 |

|

RU2441318C1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях для решения задач, содержащих цифровую обработку сигналов и изображений. Техническим результатом заявленного изобретения является расширение функциональных возможностей при решении задач цифровой обработки сигналов и изображений за счет получения собственных значений матриц в виде единой макрооперации. Для этого заявленное устройство содержит регистры, коммутаторы, блок преобразования матрицы, блок памяти констант и блок управления. 2 з.п. ф-лы, 3 ил.

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ МОДУЛЯ ТРЕХМЕРНОГО ВЕКТОРА | 1993 |

|

RU2040039C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (N X N)-МАТРИЦЫ | 1992 |

|

RU2012050C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СОБСТВЕННЫХ ЗНАЧЕНИЙ (n n) МАТРИЦЫ | 1993 |

|

RU2117987C1 |

| SU 1790787 A3, 23.01.1993 | |||

| Цифровой функциональный преобразователь | 1980 |

|

SU991419A2 |

| US 4918527 A, 17.04.1990 US 5274832 A, 28.12.1993. | |||

Авторы

Даты

2001-06-10—Публикация

2000-01-05—Подача