Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине.

Известно вычислительное устройство, содержащее блок центрального процессора, регистр флагов [1]

В известном устройстве при выполнении инструкций единственного командного потока, содержащего как арифметико-логические, так и не арифметико-логические команды, в каждый момент времени задействованы либо арифметико-логические узлы блока центрального процессора, либо вспомогательные узлы вычислительной системы, не входящие в состав блока центрального процессора, либо и те и другие одновременно.

Причиной низкой производительности известного устройства является простой арифметико-логических узлов блока центрального процессора при выполнении вычислительной системой не арифметико-логических команд (загрузки операндов из памяти и др.).

Задачей изобретения является создание устройства, позволяющего за счет одновременного анализа содержимого нескольких командных потоков минимизировать простой арифметико-логических узлов блока центрального процессора, повысив вероятность присутствия в каждом такте работы вычислительного устройства арифметико-логической команды, ожидающей выполнения.

В результате, созданное устройство обладает более высокой производительностью за счет того, что повышается вероятность присутствия арифметико-логической инструкции хотя бы в одном командном потоке в каждом такте работы вычислительного устройства, и, как следствие, увеличивается загрузка арифметико-логических узлов блока центрального процессора.

Сущность изобретения состоит в том, что вычислительное устройство с чередующимся обслуживанием нескольких командных потоков, содержащее блок центрального процессора, регистр флагов, отличается тем, что в него введены (N-1) регистров флагов, блок выбора задания, причем вход заданий устройства является входом заданий блока выбора задания, вход запросов устройства является входом запросов блока выбора задания, синхровход устройства является синхровходом блока центрального процессора и синхровходом всех регистров флагов, выход данных блока центрального процессора является выходом данных устройства, выход флагов блока центрального процессора соединен с входами информационными всех регистров флагов, выходы информационные всех регистров флагов соединены с входом флагов блока выбора задания, выход задания блока выбора задания соединен с входом задания блока центрального процессора, выход флагов блока выбора задания соединен с входом флагов блока центрального процессора, выход разрешения блока выбора задания соединен с входами разрешения всех регистров флагов и является выходом устройства, в результате чего повышается вероятность присутствия арифметико-логической инструкции хотя бы в одном командном потоке в каждом такте работы вычислительного устройства, и, как следствие, увеличивается загрузка арифметико-логических узлов блока центрального процессора.

Введение в устройство (N-1) регистров флагов позволяет единственному блоку центрального процессора чередовать обслуживание нескольких командных потоков, не нарушая причинно-следственной связи между исполняемыми в рамках этих командных потоков инструкциями.

Введение в устройство блока выбора задания позволяет за счет одновременного анализа содержимого несколько командных потоков в каждом такте работы вычислительного устройства повысить общую загрузку арифметико-логических узлов блока центрального процессора.

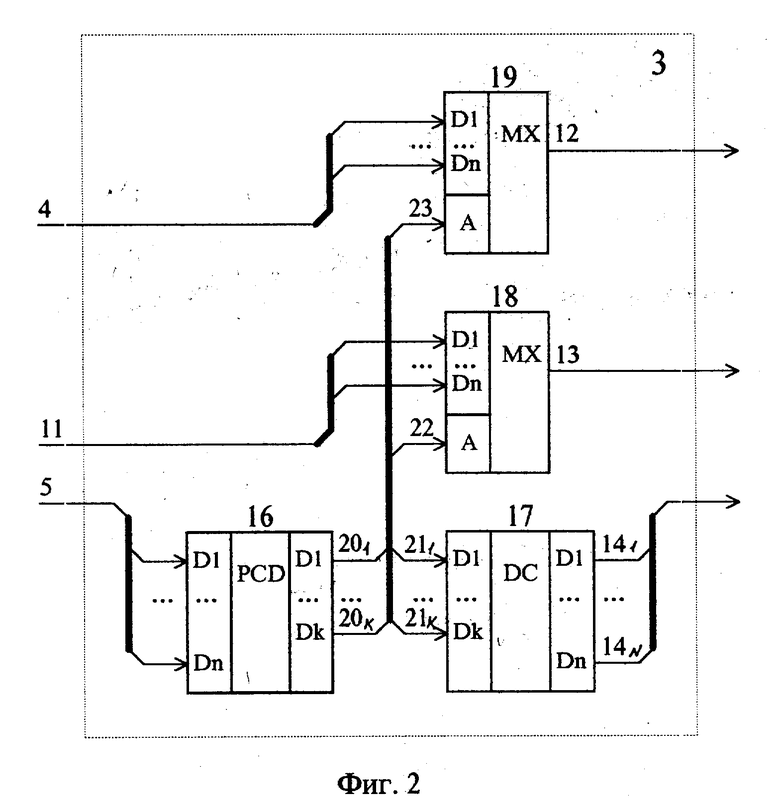

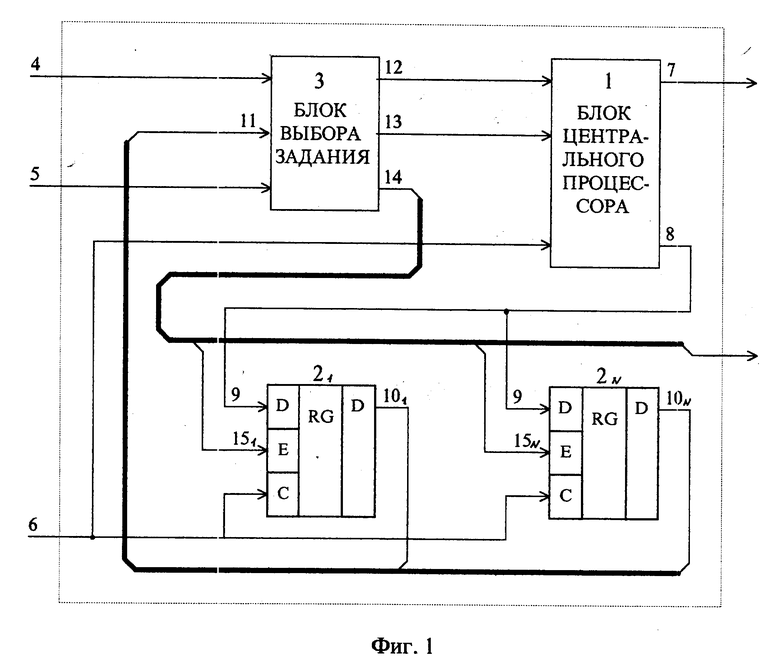

На фиг.1 представлена структурная схема вычислительного устройства с чередующимся обслуживанием нескольких командных потоков; на фиг.2 пример реализации блока выбора задания.

На фиг. 1 представлены блок 1 центрального процессора, N регистров 2 флагов, блок 3 выбора задания. Вход заданий устройства является входом 4 заданий блока 3 выбора задания, вход запросов устройства является входом 5 запросов блока 3 выбора задания, синхровход устройства является синхровходом 6 блока 1 центрального процессора и синхровходом всех регистров 2 флагов, выход 7 данных блока 1 центрального процессора является выходом данных устройства, выход 8 флагов блока 1 центрального процессора соединен с входами 9 информационными всех регистров 2 флагов, выходы 10 информационные всех регистров 2 флагов соединены с входом 11 флагов блока 3 выбора задания, выход 12 задания блока 3 выбора задания соединен с входом задания блока 1 центрального процессора, выход 13 флагов блока 3 выбора задания соединен с входом флагов блока 1 центрального процессора, выход 14 разрешения блока 3 выбора задания соединен с входами 15 разрешения всех регистров 2 флагов и является выходом устройства.

На фиг.2 показаны шифратор 16 приоритетный, дешифратор 17, мультиплексор 18 флагов, мультиплексор 19 заданий. Вход 4 заданий блока 3 выбора задания является входом информационным мультиплексора 19 заданий, вход 5 запросов блока 3 выбора задания является входом информационным шифратора 16 приоритетного, вход 11 флагов блока 3 выбора задания является входом информационным мультиплексора 18 флагов. Выход 12 информационный мультиплексора 19 заданий является выходом задания блока 3 выбора задания, выход 13 информационный мультиплексора 18 флагов является выходом флагов блока 3 выбора задания, выход 14 информационный дешифратора 17 является выходом разрешения блока 3 выбора задания, выход 20 информационный шифратора 16 приоритетного соединен с входом 21 информационным дешифратора 17, входом 22 адреса мультиплексора 18 флагов, входом 23 адреса мультиплексора 19 заданий.

Работа вычислительного устройства с чередующимся обслуживанием нескольких командных потоков (фиг.1) заключается в выполнении последовательности поступающих в устройство команд над поступающими в устройство операндами.

Входные задания поступают на вход 4 заданий устройства. Вход 4 заданий устройства представляет собой магистраль, состоящую из N шин заданий. С каждой шиной заданий связан свой командный поток, относящийся к отдельному вычислительному процессу, в результате чего задания из соседних шин заданий никаким образом не связаны друг с другом. Не является существенным, как конкретно формируются поступающие в вычислительное устройство задания, поэтому соответствующие цепи и устройства не показаны. Каждое входящее в устройство задание содержит в своем составе код операции команды с относящимся к нему операндом. Разрядность кода операции команды выбирается исходя из размера системы команд конкретно реализуемого вычислительного устройства и равна Log2 от этого количества (ближайшему целому сверху от Log2 от этого количества в случае неравенства нулю дробной части Log2 от этого количества). Разрядность, относящегося к коду операции команды операнда, определяется характеристиками используемого в вычислительном устройстве блока 1 центрального процессора.

Одновременно с входными заданиями на вход 5 запросов устройства поступают N одноразрядных сигналов запроса на обслуживание, каждый из которых связан с одной из шин заданий в магистрали входа 4 заданий устройства. Присутствие логической "1" на одноразрядном сигнале запроса на обслуживание свидетельствует о присутствии в текущий момент времени входного задания на соответствующей этому одноразрядному сигналу шине заданий входа 4 заданий устройства. Не является существенным, как конкретно формируются поступающие в вычислительное устройство запросы на обслуживание, поэтому соответствующие цепи и устройства не показаны.

На синхровход 6 устройства подаются синхроимпульсы от внешнего источника синхросигналов. Не является существенным, как конкретно формируются синхроимпульсы, поэтому соответствующие цепи и источник синхросигналов не показаны.

С входа 4 заданий устройства задания, входа 5 запросов устройства запросы на обслуживание поступают на вход заданий, вход запросов блока 3 выбора задания соответственно.

Внутри блока 3 выбора задания в соответствии с присутствующими на входе 5 запросов запросами на обслуживание (предполагается, что задания, принадлежащие различным шинам заданий входа 4 заданий, имеют различные приоритеты на обслуживание) осуществляется выбор задания, выполнение которого будет произведено в следующем такте работы вычислительного устройства. Выбранное задание однозначно определяет один из N вычислительных процессов, которому в следующем такте работы устройства будет выделен вычислительный ресурс блока 1 центрального процессора (конкретная реализация блока 1 центрального процессора не является существенной [1,2]). При этом на N-разрядном выходе 14 разрешения блока 3 выбора задания в логическую "1" устанавливается одноразрядный сигнал, ответственный за выбранное задание (остальные одноразрядные сигналы устанавливаются в логический "0").

Для обеспечения корректности получаемых в ходе вычислений результатов, каждый из N вычислительных процессов работает со своим регистром 2 флагов. Каждый из N регистров 2 флагов функционирует независимо от остальных N-1 регистров 2 флагов, входящих в вычислительное устройство с чередующимся обслуживанием нескольких командных потоков, при этом конкретная реализация регистров 2 флагов не является существенной [1] На вход 11 флагов блока 3 выбора задания с выходов 10 информационных поступает содержимое N регистров 2 флагов. Выбор задания в блоке 3 выбора задания однозначно определяет регистр 2 флагов, содержимое которого будет учтено при проведении вычислений в следующем такте работы вычислительного устройства. С выхода 12 задания задание, выхода 13 флагов флаги поступают на вход задания, вход флагов блока 1 центрального процессора соответственно. Таким образом, в блоке 1 центрального процессора имеется вся информация для выполнения очередной команды в следующем такте работы вычислительного устройства, задаваемом синхроимпульсами, поступающими на синхровход 6 блока 1 центрального процессора с синхровхода устройства.

После выполнения вычислительным устройством очередного задания, с выхода 8 флагов блока 1 центрального процессора измененные значения флагов подаются на входы 9 информационные всех регистров 2 флагов. Одновременно с этим, с выхода 14 разрешения блока 3 выбора задания N одноразрядных сигналов разрешения поступают на одноразрядные входы 15 разрешения N регистров 2 флагов, однозначно выбирая единственный регистр 2 флагов, в который и будет осуществлена запись измененных значений флагов с приходом на синхровход 6 регистров 2 флагов синхроимпульсов с синхровхода устройства.

На выход данных устройства поступает обработанный операнд с выхода 7 данных блока 1 центрального процессора. Не является существенным, куда конкретно затем поступает обработанный операнд, поэтому соответствующие цепи и устройства не показаны. Для однозначного определения вычислительного процесса, к которому относится этот операнд, на выход устройства подаются N одноразрядных сигналов с выхода 14 разрешения блока 3 выбора задания. Не является существенным, куда конкретно подаются сигналы с выхода устройства, поэтому соответствующие цепи и устройства не показаны.

Работа блока 3 выбора задания (фиг.2) заключается в выборе задания, выполнение которого будет произведено в следующем такте работы вычислительного устройства, определении регистра флагов, содержимое которого будет учтено при проведении вычислений в следующем такте работы вычислительного устройства, формировании N сигналов разрешения, обеспечивающих запись измененных значений флагов в регистр флагов того вычислительного процесса, к которому относится задание, выполнение которого будет произведено в следующем такте работы вычислительного устройства.

С входа 5 запросов блока 3 выбора задания равное или меньшее N число запросов на обработку заданий поступает на вход информационный шифратора 16 приоритетного. С выхода 20 информационного шифратора 16 приоритетного снимается двоичный код, разрядности Log2(N), младшего не равного логическому "0" сигнала входа 5 информационного шифратора 16 приоритетного. С выхода 20 информационного шифратора 16 приоритетного двоичный код поступает на вход 21 информационный дешифратора 17, с N-разрядного выхода 14 информационного которого снимается сигнал с установленной логической "1" лишь в разряде, соответствующем младшему не равному логическому "0" сигналу входа 5 информационного дешифратора 16 приоритетного. С выхода 14 информационного дешифратора 17 N-разрядный сигнал разрешения поступает на выход разрешения блока 3 выбора задания.

С выхода 20 информационного шифратора 16 приоритетного двоичный код поступает также на вход 22 адреса мультиплексора 18 флагов, где определяет содержимое какого из N регистров 2 флагов, приходящее с входа 11 флагов блока 3 выбора задания на вход информационный мультиплексора 18 флагов, поступит с выхода 13 информационного мультиплексора 18 флагов на выход флагов блока 3 выбора задания.

С выхода 20 информационного шифратора 16 приоритетного двоичный код поступает также на вход 23 адреса мультиплексора 19 заданий, где определяет задание какой из N шин заданий, приходящее со входа 4 заданий блока 3 выбора задания на вход информационный мультиплексора 19 заданий, поступит с выхода 12 информационного мультиплексора 19 заданий на выход задания блока 3 выбора задания.

Источники информации:

1. Каган Б. М. Сташин В.В. "Микропроцессоры в цифровых системах" М. Энергия, 1979, 27 с.

2. Каган Б.М. "Электронные вычислительные машины и системы". М. Энергоатомиздат, 1985, 552 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ И ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2099780C1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство микропрограммного управления | 1987 |

|

SU1539776A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине. Целью изобретения является повышение производительности вычислительного устройства. Указанная цель достигается тем, что вычислительное устройство содержит: блок центрального процессора, N регистров флагов, блок выбора задания. Сущность изобретения: за счет одновременного анализа содержимого нескольких командных потоков повышается вероятность присутствия арифметико-логической инструкции хотя бы в одном командном потоке в каждом такте работы вычислительного устройства и, как следствие, увеличивается загрузка арифметико-логических узлов блока центрального процессора. 2 ил.

Вычислительное устройство с чередующимся обслуживанием нескольких командных потоков, содержащее блок центрального процессора, регистр флагов, отличающееся тем, что в него введены N 1 регистров флагов, блок выбора задания, причем вход заданий устройства является входом заданий блока выбора задания, вход запросов устройства является входом запросов блока выбора задания, синхровход устройства является синхровходом блока центрального процессора и синхровходом всех регистров флагов, выход данных блока центрального процессора является выходом данных устройства, выход флагов блока центрального процессора соединен с входами информационными всех регистров флагов, выходы информационные всех регистров флагов соединены с входом флагов блока выбора задания, выход заданий блока выбора задания соединен с входом задания блока центрального процессора, выход флагов блока выбора задания соединен с входом флагов блока центрального процессора, выход разрешения блока выбора задания соединен с входами разрешения всех регистров флагов и является выходом устройства.

| Каган Б.М., Сташин В.В | |||

| Микропроцессоры в цифровых системах | |||

| - М.: Энергия, 1979, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1998-01-10—Публикация

1995-12-04—Подача