Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине.

Известно вычислительное устройство, содержащее блок центрального процессора, блок микропрограммного управления, включающий в себя регистр команд и регистр адреса микрокоманд, блок постоянной памяти микропрограмм, включающий в себя регистр микрокоманд, регистр флагов [1]

В известном устройстве код выполняемый микрооперации поступает параллельно на все арифметико-логические (вычислительные) секции, входящие в состав блока центрального процессора. Код микрооперации дешифруется в каждой арифметико-логической секции, определяя настройку всего процессорного блока на выполнение одной микрооперации.

Причиной низкой производительности известного устройства является необходимость настройки одновременно всех арифметико-логических секций процессорного блока на обработку операндов, разрядность которых составляет половину, четверть и т.д. от длины операнда, для которого существует возможность его единовременной обработки процессорным блоком; при наличии одного командного потока невозможно полностью использовать весь вычислительный ресурс центрального процессора, если текущей выполняемой команде необходима его половина, четверть и т.д.

Задачей изобретения является создание устройства, позволяющего за счет раздельного микропрограммного управления арифметико-логическими секциями, входящими в состав процессорного блока, выделять для обработки операндов, из нескольких приоритетных командных потоков, число секций, суммарная разрядность которых в точности соответствует разрядности этих операндов, а также осуществлять обработку операндов из нескольких приоритетных командных потоков одновременно в случае, когда оставшийся после выделения командному потоку с максимальным приоритетом неиспользованный вычислительный ресурс центрального процессора может быть использован командными потоками с меньшими приоритетами. В результате созданное устройство обладает более высокой производительностью за счет того, что арифметико-логические секции, входящие в состав процессорного блока, управляются микропрограммно независимо друг от друга, позволяя тем самым выделять для обработки операндов из нескольких приоритетных командных потоков число секций, суммарная разрядность которых в точности соответствует разрядности этих операндов, а также осуществлять обработку операндов из нескольких приоритетных командных потоков одновременно в случае, когда оставшийся после выделения командному потоку с максимальным приоритетом неиспользуемый вычислительный ресурс центрального процессора может быть использован командными потоками с меньшими приоритетами.

Сущность изобретения состоит в том, что модульное вычислительное устройство с раздельным микропрограммным управлением арифметико-логическими секциями и чередующимся обслуживанием несколько командных потоков, содержащее блок центрального процессора, блок микропрограммного управления, блок постоянной памяти микропрограмм, регистр флагов, отличается тем, что в него введены (N-1) микропрограммного управления, (K-1) регистров флагов, блок формирования заданий, причем синхровход устройства является синхровходом блока формирования заданий и синхровходами всех регистров флагов, вход операндов устройства является входом операндов блока формирования заданий, вход команд устройства является входом команд блока формирования заданий, выход данных блока центрального процессора является выходом данных устройства, выход блока формирования заданий является выходом управления устройства, выход признаков блока центрального процессора соединен с первыми группами входов признаков всех блоков микропрограммного управления, выход флагов блока центрального процессора соединен с входом флагов блока формирования заданий, первые группы выходов признаков всех блоков микропрограммного управления соединены с входом признаков блока центрального процессора, вторые группы выходов признаков всех блоков микропрограммного управления соединены с входом занятости блока формирования заданий, выходы адреса микрокоманд всех блоков микропрограммного управления соединены с входом адресов микрокоманд блока N-портовой постоянной памяти микропрограмм, выход микроопераций блока N-портовой постоянной памяти микропрограмм соединен с входом микроопераций блока центрального процессора, выход управления адресом блока N-портовой постоянной памяти микропрограмм соединен с входами управления адресом всех блоков микропрограммного управления, выходы информационные всех регистров флагов соединены с входом информационным блока формирования заданий, выход операндов блока формирования заданий соединен с входом операндов блока центрального процессора, выход флагов блока формирования заданий соединен с входом флагов блока центрального процессора, выход команд блока формирования заданий соединен с входами команд всех блоков микропрограммного управления, выход признаков блока формирования заданий соединен со вторыми группами входов признаков всех блоков микропрограммного управления, выход разрешения блока формирования заданий соединен с входами разрешения всех регистров флагов, выход информационный блока формирования заданий соединен с входами информационными всех регистров флагов, в результате чего арифметико-логические вычислительные секции, входящие в состав процессорного блока, управляются микропрограммно независимо друг от друга, позволяя тем самым выделять для обработки операндов из нескольких приоритетных командных потоков число секций, суммарная разрядность которых в точности соответствует разрядности этих операндов, а также осуществлять обработку операндов из нескольких приоритетных командных потоков одновременно в случае, когда оставшийся после выделения командному потоку с максимальным приоритетом неиспользованный вычислительный ресурс центрального процессора может быть использован командными потоками с меньшими приоритетами.

Введение в устройство (N-1) блоков микропрограммного управления позволяет обеспечить раздельное микропрограммное управления N арифметико-логическими секциями, входящими в состав процессорного блока.

Использование в устройстве блока N-портовой постоянной памяти микропрограмм позволяет обеспечить бесконфликтную адресацию постоянной памяти микропрограмм со стороны N блоков микропрограммного управления и параллельную выдачу микроопераций на N регистров микрокоманд для независимого управления N арифметико-логическими секциями в составе блока центрального процессора.

Введение в устройство (K-1) регистров флагов позволяет обеспечить бесконфликтную обработку инструкций из K командных потоков единым вычислительным ресурсом процессорного блока.

Введение в устройство блока формирования заданий позволяет обеспечить загрузку всех арифметико-логических секций процессорного блока с максимально возможным коэффициентом их использования для конкретного случая выполняемых операций и форматов обрабатываемых операндов.

Блок формирования заданий содержит узел выбора заданий, узел вывода флагов, N мультиплексоров операндов, N мультиплексоров команд, причем синхровход блока формирования заданий является синхровходом узла вывода флагов, вход операндов блока формирования заданий является входами информационными всех мультиплексоров операндов, вход команд блока формирования заданий является входом запросов узла выбора заданий и вторыми группами входов информационных всех мультиплексоров команд, вход флагов блока формирования заданий является входом информационным узла вывода флагов, вход занятости блока формирования заданий является входом занятости узла выбора заданий и входом занятости узла вывода флагов, вход информационный блока формирования заданий является первыми группами входов информационных всех мультиплексоров команд, выход запросов узла выбора заданий соединен с входом запросов узла вывода флагов и является выходом блока формирования заданий, выходы информационные всех мультиплексоров операндов являются выходом операндов блока формирования заданий, первая группа выходов информационных всех мультиплексоров команд является выходом флагов блока формирования заданий, вторая группа выходов информационных всех мультиплексоров команд является выходом команд блока формирования заданий, выход признаков узла выбора заданий является выходом признаков блока формирования заданий, выход разрешения узла вывода флагов является выходом разрешения блока формирования заданий, выход информационный узла вывода флагов является выходом информационным блока формирования заданий, выход адреса операндов узла выбора заданий соединен с входами адреса всех мультиплексоров операндов, выход адреса команд узла выбора заданий соединен с входами адреса всех мультиплексоров команд и входом адреса узла вывода флагов.

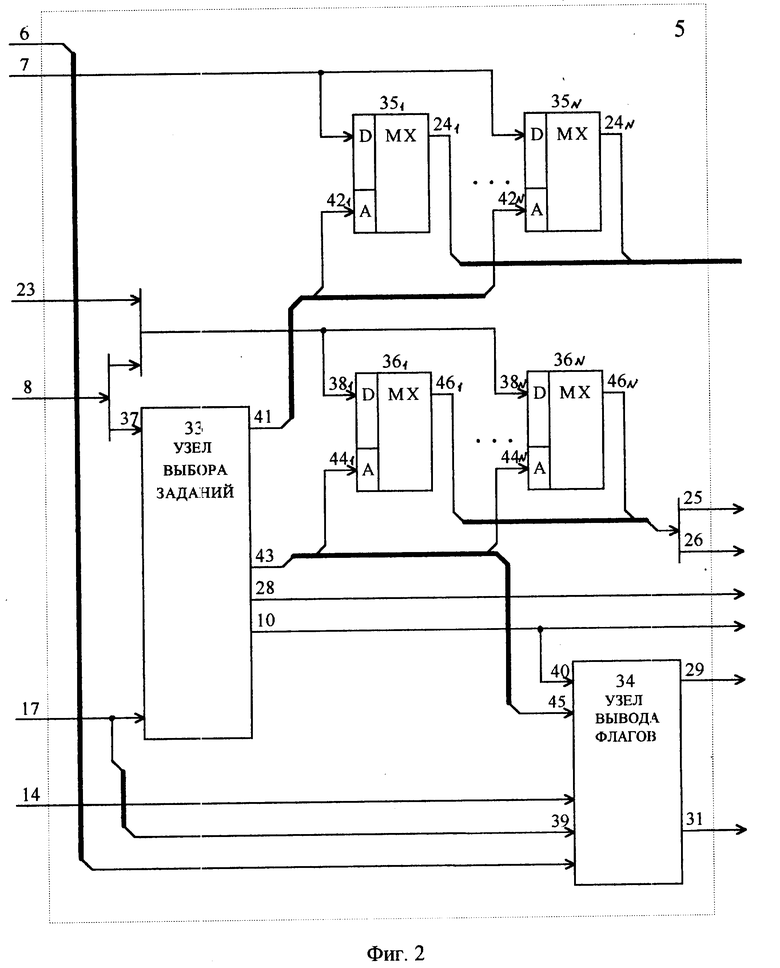

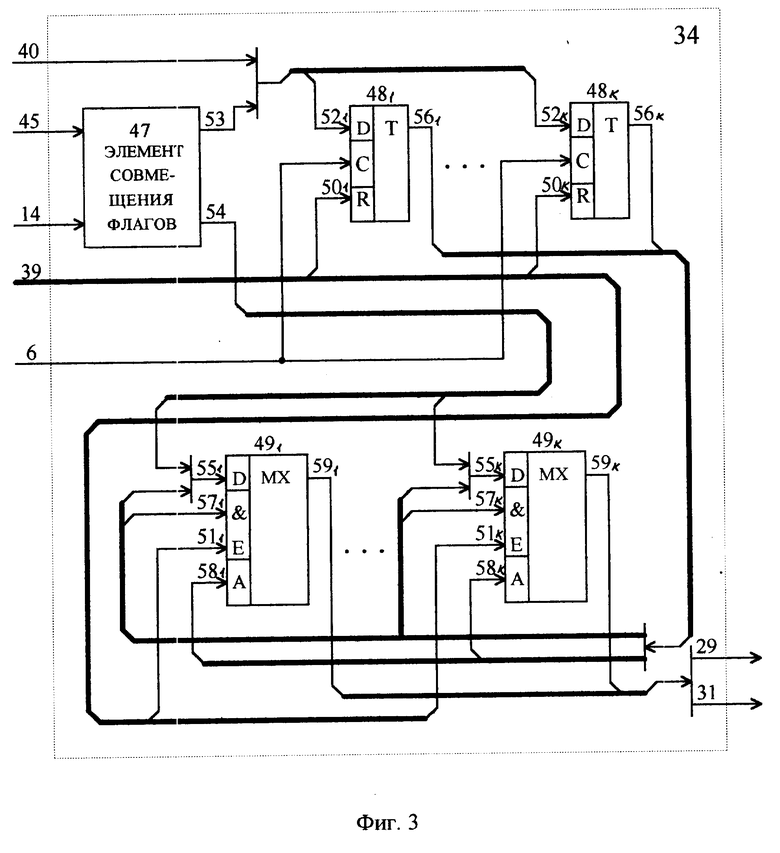

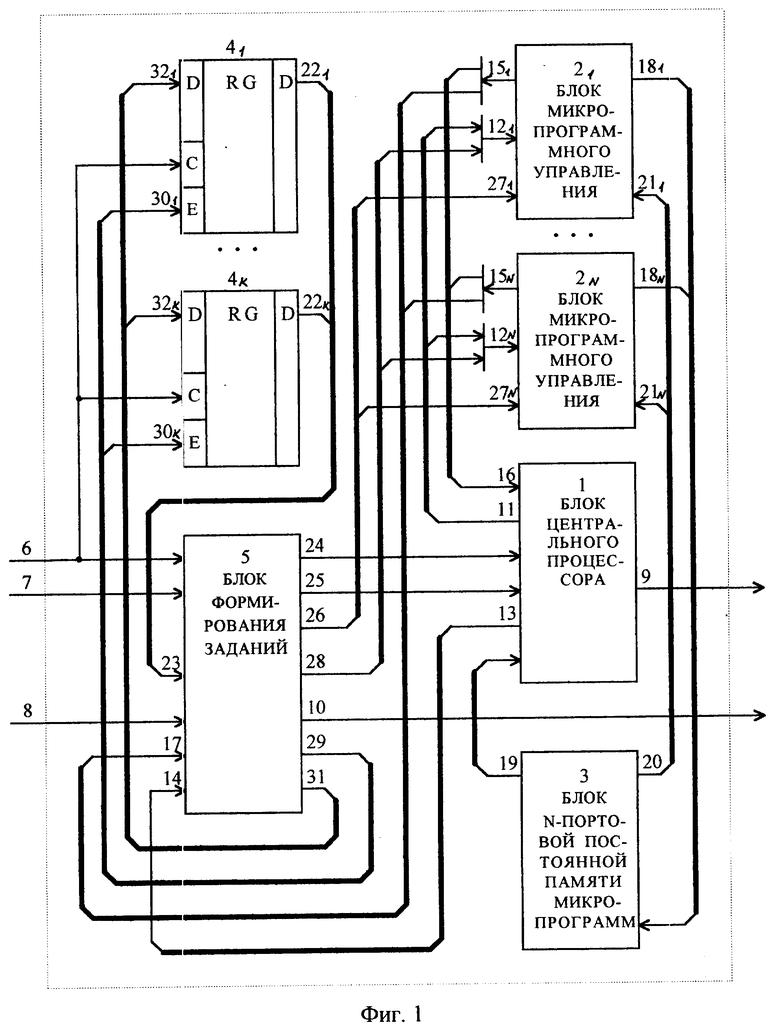

На фиг. 1 представлена структурная блок-схема модульного вычислительного устройства с раздельным микропрограммным управлением арифметико-логическими секциями и чередующимся обслуживанием нескольких командных потоков; на фиг. 2 схема блока формирования заданий; на фиг. 3 пример реализации узла вывода флагов.

На фиг. 1 обозначены блок центрального процессора 1, N блоков микропрограммного управления 2, блок N-портовой постоянной памяти микропрограмм 3, K регистров флагов 4, блок формирования заданий 5. Синхровход устройства является синхровходом 6 блока формирования заданий 5 и синхровходами всех регистров флагов 4. Вход операндов устройства является входом 7 операндов блока формирования заданий 5. Вход команд устройства является входом 8 команд блока формирования заданий 5. Выход 9 данных блока центрального процессора 1 формируется из N выходных операндов (частей операндов) и является выходом данных устройства. Выход 10 блока формирования заданий 5 формируется из K сигналов, разрешающих поступление на соответствующие входы операндов и команд устройства очередных заданий из приоритетных потоков заданий и является выходом управления устройств. Выход 11 признаков блока центрального процессора 1 формируется из выходных признаков всех вычислительных секций блока центрального процессора 1 и соединен с первыми группами входов 12 признаков всех блоков микропрограммного управления 2. Выход 13 флагов блока центрального процессора 1 формируется из значений флагов от N вычислительных секций и соединен с входом 14 флагов блока формирования заданий 5. Первые группы выходов 15 признаков всех блоков микропрограммного управления 2 формируются из входных признаков N вычислительных секций блока центрального процессора 1 и соединены с входом 16 признаков блока центрального процессора 1. Вторые группы выходов 15 признаков всех блоков микропрограммного управления 2 формируются из признаков занятости вычислительных секций блока центрального процессора 1 в следующем такте работы вычислительного устройства и соединены с входом 17 занятости блока формирования заданий 5. Выходы 18 адреса микрокоманд всех блоков микропрограммного управления 2 формируются из адресов микрокоманд и соединены с входом адресов микрокоманд блока N-портовой постоянной памяти микропрограмм 3. Выход 19 микроопераций блока N-портовой постоянной памяти микропрограмм 3 формируется из N микрокоманд и соединен с входом микроопераций блока центрального процессора 1. Выход 20 управления адресом блока N-портовой постоянной памяти микропрограмм 3 формируется из N групп управления адресом и соединен с входами 21 управления адресом всех блоков микропрограммного управления 2. Выходы 22 информационные всех регистров флагов 4 соединены с входом 23 информационным блоком формирования заданий 5. Выход 24 операндов блока формирования заданий 5 формируется из N секционных операндов для N секций блока центрального процессора 1 и соединен с входом операндов блока центрального процессора 1. Выход 25 флагов блока формирования заданий 5 формируется из значений флагов для N вычислительных секций и соединен с входом флагов блока центрального процессора 1. Выход 26 команд блока формирования заданий 5 формируется из N секционных кодов операций команд и соединен с входами 27 команд всех блоков микропрограммного управления 2. Выход 28 признаков блока формирования заданий 5 формируется из N секционных признаков для управления N секциями блока центрального процессора 1 и соединен со вторыми группами входов 12 признаков всех блоков микропрограммного управления 2. Выход 29 разрешения блока формирования заданий 5 формируется из K сигналов разрешения записи во все регистры флагов 4 и соединен с входами 30 разрешения всех регистров флагов 4. Выход 31 информационный блока формирования заданий 5 соединен с входами 32 информационными всех регистров флагов 4.

На фиг. 2 обозначены узел выбора заданий 33, узел вывода флагов 34, N мультиплексоров операндов 35, N мультиплексоров команд 36. Синхровход блока формирования заданий 5 является синхровходом 6 узла вывода флагов 34. Вход операндов блока формирования заданий 5 является входами 7 информационными всех мультиплексоров операндов 35. Вход 8 команд блока формирования заданий 5 является входом 37 запросов узла выбора заданий 33 и вторыми группами входов 38 информационных всех мультиплексоров команд 36. Вход флагов блока формирования заданий 5 является входом 14 информационным узла вывода флагов 34. Вход занятости блока формирования заданий 5 является входом занятости 17 узла выбора заданий 33 и входом 39 занятости узла вывода флагов 34. Вход 23 информационный блока формирования заданий 5 является первыми группами входов 38 информационных всех мультиплексоров команд 36. Выход 10 запросов узла выбора заданий 33 формируется из K сигналов запросов на поступление в устройство очередных заданий из приоритетных потоков заданий и соединен с входом 40 запросов узла вывода флагов 34 и является выходом блока формирования заданий 5. Выходы 24 информационные всех мультиплексоров операндов 35 формируется из N секционных операндов для N вычислительных секций блока центрального процессора 1 и являются выходом операндов блока формирования заданий 5. Первая группа выходов 46 информационных всех мультиплексоров команд 36 формируется из N регистров флагов для N вычислительных секций блока центрального процессора 1 и является выходом 25 флагов блока формирования заданий 5. Вторая группа выходов 46 информационных всех мультиплексоров команд 36 формируется из N секционных команд для N блоков микропрограммного управления 2 и является выходом 26 команд блока формирования заданий 5. Выход 28 признаков узла выбора заданий 33 формируется из N секционных признаков для управления N вычислительными секциями блока центрального процессора 1 и является выходом признаков блока формирования заданий 5. Выход 29 разрешения узла вывода флагов 34 формируется из K сигналов разрешения записи во все регистры флагов 4 и является выходом разрешения блока формирования заданий 5. Выход 31 информационный узла вывода флагов 34 формируется из значений флагов для K регистров флагов 4 и является выходом информационным блока формирования заданий 5. Выход 41 адреса операндов узла выбора заданий 33 формируется из N адресов и соединен с входами 42 адреса всех мультиплексоров операндов 35. Выход 43 адреса команд узла выбора заданий 33 формируется из N адресов и соединен с входами 44 адреса всех мультиплексоров команд 36 и входом 45 адреса узла вывода флагов 34.

На фиг. 3 обозначены элемент совмещения флагов 47, K триггеров 48, K мультиплексоров флагов 49. Синхровход 6 узла вывода флагов 34 является синхровходами всех триггеров 48. Вход 14 информационный узла вывода флагов 34 является входом информационным элемента совмещения флагов 47. Вход 39 занятости узла вывода флагов 34 является входами 50 синхронного сброса всех триггеров 48 и вторыми входами 51 разрешения всех мультиплексоров флагов 49. Вход 40 запросов узла вывода флагов 34 является первой группой входов 52 информационных всех триггеров 48. Вход 45 адреса узла вывода флагов 34 является входом адреса элемента совмещения флагов 47. Выход 53 адреса элемента совмещения флагов 47 формируется из K адресов и соединен со вторыми группами входов 52 информационных всех триггеров 48. Выход 54 информационный элемента совмещения флагов 47 формируется из K совмещенных значений флагов от N вычислительных секций и соединен с первыми группами входов 55 информационных всех мультиплексоров флагов 49. Первые группы выходов 56 информационных всех триггеров 48 формируется из K сигналов разрешения записи во все регистры флагов 4 и соединены со вторыми группами входов 55 информационных всех мультиплексоров флагов 49 и первыми входами 57 разрешения всех мультиплексоров флагов 49. Вторые группы выходов 56 информационных всех триггеров 48 формируются из K адресов для всех регистров флагов 4 и соединены с входами 58 адреса всех мультиплексоров флагов 49. Первые группы выходов 59 информационных всех мультиплексоров флагов 49 формируются из K сигналов разрешения записи во все регистры флагов 4 и являются выходом 29 разрешения узла вывода флагов 34. Вторые группы выходов 59 информационных всех мультиплексоров флагов 49 формируются из K адресов для всех регистров флагов 4 и являются выходом 31 информационным узла вывода флагов 34.

Работа вычислительного устройства с раздельным микропрограммным управлением арифметико-логическими секциями и чередующимся обслуживанием нескольких командных потоков (фиг. 1) заключается в выполнении последовательностей поступающих в устройство команд, относящихся к K потокам заданий, над поступающими в устройство и относящимися к ним операндами.

На вход 7 операндов устройства подаются K входных операндов. Каждый входной операнд состоит из N равных групп разрядности m по числу вычислительных секций в блоке центрального процессора 1. Блок центрального процессора 1 вычислительного устройства взят без изменений из состава модульного микропроцессора с микропрограммным управлением [1] Он содержит N идентичных по выполняемым функциям арифметико-логических вычислительных секций. Каждый из входов и выходов блока центрального процессора 1 состоит из N групп. Каждая группа входов и выходов блока центрального процессора 1 соединена с одной из N входящих в блок центрального процессора 1 вычислительных секций. Минимальная разрядность каждого из поступающих в устройство входных операндов равна разрядности m одной вычислительной секции, входящей в состав блока центрального процессора 1, а максимальная суммарной разрядности N вычислительных секций, т. е. m•N бит (в случае, когда разрядность входных операндов меньше максимальной разрядности операндов, каждый из входных операндов поступает в вычислительное устройство, прижатый к правому краю разрядной сетки). Не является существенным, как конкретно формируются поступающие в устройство операнды, поэтому соответствующие цепи и устройства не показаны. Каждый из операндов поступает на вход 7 операндов устройства одновременно с командой, к которой он относится.

На вход 8 команд устройства поступают K входных команд. Не является существенным, как конкретно формируются поступающие в устройство команды, поэтому соответствующие цепи и устройства не показаны. Каждая из поступающих в вычислительное устройство команд состоит из двух групп: группа кода операции команды; группы, определяющей количество арифметико-логических секций блока центрального процессора 1, требуемых для обработки относящегося к команде операнда. Разрядность группы кода операции команды выбирается исходя из размера системы команд конкретно реализуемого вычислительного устройства и равна Log2 от этого количества (ближайшему целому сверху от Log2 от этого количества в случае неравенства нулю дробной части Log2 от этого количества). Разрядность группы, определяющей количество арифметико-логических секций блока центрального процессора 1, требуемых для обработки относящегося к команде операнда, равна Log2(N) (ближайшему целому сверху от Log2(N) в случае неравенства нулю дробной части Log2(N)).

На синхровход 6 устройства подаются синхроимпульсы от внешнего источника синхросигналов. Не является существенным, как конкретно формируются синхроимпульсы, поэтому соответствующие цепи и источник синхросигналов не показаны.

С входа операндов устройства операнда, входа команд устройства команды, синхровхода устройства синхроимпульсы поступают на вход 7 операндов, вход 8 команд, синхровход 6 блока формирования заданий 5, соответственно.

Внутри блока формирования заданий 5 осуществляется формирование секционных заданий для N вычислительных секций блока центрального процессора 1. Секционные задания составляются определенным образом из команд, поступающих на вход 8 команд блока формирования заданий 5, операндов, относящихся к этим командам и поступающих на вход 7 операндов блока формирования заданий 5 и значений регистров флагов, относящихся и K потокам заданий, из которых попали в вычислительное устройство текущие команды с относящимися к ним операндами. Значения регистров флагов поступают с выходов 22 информационных всех регистров флагов 4 на вход 23 информационный блока формирования заданий 5. Потоки заданий (командные потоки) вычислительного устройства имеют различные приоритеты на обслуживание. Присвоение конкретным командным потокам конкретных значений приоритетов зависит от конкретной реализации вычислительного устройства. При любом распределении приоритетов по командным потокам первым, при наличии требуемого для его обслуживания вычислительного ресурса, обслуживается командный поток с максимальным приоритетом. В случае, если после выделения вычислительного ресурса командному потоку с наивысшим приоритетом остался неиспользованный вычислительный ресурс, то, в зависимости от требований командного потока с меньшим приоритетом, оставшийся вычислительный ресурс выделяется ему. И так далее, до полного исчерпания вычислительного ресурса, имеющегося в следующем такте работы вычислительного устройства. О возможности поступления в вычислительное устройство нового задания из какого-либо командного потока сигнализирует установление в логическую "1" соответствующего этому командному потоку одноразрядного сигнала в K-разрядном выходе 10 блока формирования заданий 5, который является выходом управления устройства. Не является существенным, куда конкретно подаются сигналы с выхода управления устройства, поэтому соответствующие цепи и устройства не показаны.

Для формирования заданий из поступающих в устройство команд, с относящимися к ним операндами и соответствующими значениями флагов, необходимо, чтобы в блоке центрального процессора 1 было бы свободным в следующем такте работы вычислительного устройства такое количество арифметико-логических секций, которое требуется для выполнения заданий из приоритетных потоков заданий. О занятости в следующем такте работы вычислительного устройства арифметико-логических секций блока центрального процессора 1 сигнализируют N одноразрядных сигналов, поступающих на вход 17 занятости блока формирования заданий 5 со вторых групп выходов 15 признаков всех блоков микропрограммного управления 2 (от каждого из N блоков микропрограммного управления 2 поступает одноразрядный сигнал о занятости (логическая "1") в следующем такте работы вычислительного устройства управляемой им арифметико-логической секции в блоке центрального процессора 1).

На основе информации о занятости вычислительных секций в следующем такте работы вычислительного устройства и информации о требуемом количестве вычислительных секций заданиям из приоритетных потоков заданий (обработка операнда, относящегося к команде из одного командного потока, может потребовать от одной до N вычислительных секций, в зависимости от формата этого операнда), в блоке формирования заданий 5 принимается решение о формировании секционных заданий и выдаче их на выполнение в блоке центрального процессора 1. При этом для каждой из вычислительных секций, которые будут заняты в следующем такте работы вычислительного устройства выдаваемыми заданиями, формируется свое секционное задание. Каждое секционное задание состоит из четырех составляющих: секционного операнда, секционного кода операции команды, секционного признака, значений регистра флагов, относящегося к командному потоку, из которого попала в вычислительное устройство текущая команда с относящимся к ней операндом. Разрядность секционного операнда равна разрядности одной вычислительной секции m. Разрядность секционного кода операции команды повторяет разрядность группы кода операции поступающей в вычислительное устройство команды. Разрядность секционного признака равна Log2(N) (ближайшему целому сверху от Log2(N) в случае неравенства нулю дробной части Log2(N). Разрядность содержимого регистра флагов зависит от разрядности регистров флагов 4, которая совпадает с разрядностью единственного регистра флагов модульного микропроцессора с микропрограммным управлением (конкретная реализация регистров флагов 4 не является существенной). Секционные операнды с выхода 24 операндов, значения регистра флагов, относящегося к соответствующему командному потоку, с выхода 25 флагов блока формирования заданий 5 поступают через вход операндов, вход флагов блока центрального процессора 1 на соответствующие арифметико-логические секции. Одновременно с этим секционные коды операций команд с выхода 26 команд блока формирования заданий 5 поступают на входы 27 команд соответствующих блоков микропрограммного управления 2. В то же время секционные признаки с выхода 28 признаков блока формирования заданий 5 поступают на вторые группы входов 12 признаков соответствующих блоков микропрограммного управления 2.

Каждый из N блоков микропрограммного управления 2 работает независимо от остальных (N-1) блоков микропрограммного управления 2, входящих в модульное вычислительное устройство, и независимо осуществляет микропрограммное управление относящейся к нему арифметико-логической секцией в составе блока центрального процессора 1, при этом конкретная реализация блоков микропрограммного управления 2 не является существенной.

В процессе микропрограммного управления работой вычислительного устройства секционные коды операций команд, поступившие на входы 27 команд соответствующих блоков микропрограммного управления 2, преобразуются в этих блоках в адреса первых микрокоманд, определяющих начала последовательностей микрокоманд, выполнение которых приведет к выполнению поступивших в соответствующие блоки микропрограммного управления 2 секционных кодов операций команд. Затем адреса первых микрокоманд, в общем случае текущих, поступают через выходы 18 адреса микрокоманд соответствующих блоков микропрограммного управления 2 на вход адресов микрокоманд блока N-портовой постоянной памяти микропрограмм 3.

Блок N-портовой постоянной памяти микропрограмм 3 вычислительного устройства содержит память микропрограмм, полностью повторяющую память микропрограмм блока постоянной памяти микропрограмм модульного микропроцессора с микропрограммным управлением. Число входных портов в блоке N-портовой постоянной памяти микропрограмм 3 равно N, что позволяет всем блокам программного управления 2 независимо друг от друга обращаться к памяти микропрограмм блока N-портовой постоянной памяти микропрограмм 3 без возникновения конфликтных ситуаций между ними. При этом разрядность каждого из входных портов блока N-портовой постоянной памяти микропрограмм 3 совпадает с разрядностью единственного входного порта в блоке постоянной памяти микропрограмм модульного микропроцессора с микропрограммным управлением. Через каждый из N регистров микрокоманд блока N-портовой постоянной памяти микропрограмм 3, разрядность каждого из которых совпадает с разрядностью единственного регистра микрокоманд блока постоянной памяти микропрограмм модульного микропроцессора с микропрограммным управлением, осуществляется независимая настройка каждой из N арифметико-логических секций, входящих в состав блока центрального процессора 1, на выполнение своей микрокоманды. Через каждый из N портов выхода управления адресом блока N-портовой постоянной памяти микропрограмм 3, разрядность каждого из которых совпадает с разрядностью единственного выхода управления адресом блока постоянной памяти микропрограмм модульного микропроцессора с микропрограммным управлением, осуществляется независимая передача признаков управления адресом N блокам микропрограммного управления 2. Конкретная реализация блока N-портовой постоянной памяти микропрограмм 3 не является существенной.

В блоке N-портовой постоянной памяти микропрограмм 3 происходит преобразование адресов текущих микропрограмм в адресуемые ими текущие микрокоманды и информацию для формирования адресов следующих микрокоманд, в рамках выполнения поступивших в соответствующие блоки микропрограммного управления 2 секционных кодов операций команд. Микрокоманды через выход 19 микроопераций блока N-портовой постоянной памяти микропрограмм 3 поступают через вход микроопераций блока центрального процессора 1 на соответствующие вычислительные секции. Одновременно с этим с первых групп выходов 15 признаков соответствующих блоков микропрограммного управления 2 на вход 16 признаков блока центрального процессора 1 поступают признаки, однозначно настраивающие соответствующие вычислительные секции на реализацию конкретных микрокоманд. Совместно с информацией для формирования адресов, поступающей с выхода 20 управления адресом блока N-портовой постоянной памяти микропрограмм 3 на входы 21 управления адресом соответствующих блоков микропрограммного управления 2, в процессе выработки адресов следующих микроопераций (в рамках выполнения текущих секционных кодов операций команд) участвуют также признаки, поступающие от соответствующих вычислительных секций (после выполнения ими текущих микрокоманд) с выхода 11 признаков блока центрального процессора 1 на первые группы входов 12 признаков соответствующих блоков микропрограммного управления. Процесс в рамках каждого из N блоков микропрограммного управления 2 повторяется до тех пор, пока не будут выполнены все микрокоманды, выполнение которых определяет выполнение поступившего в этот блок микропрограммного управления 2 секционного кода операции команды.

На вход 14 флагов блока формирования заданий 5 поступают значения флагов, относящиеся к N вычислительным секциям блока центрального процессора 1. В блоке формирования заданий 5 происходит совмещение значений флагов, поступивших от нескольких вычислительных секций блока центрального процессора 1 в том случае, если эти вычислительные секции обрабатывали относящийся к одному командному потоку операнд, разрядность которого превышает разрядность одной вычислительной секции. С выхода 31 информационного блока формирования заданий 5 совмещенные значения флагов поступают на входы 32 информационные K регистров флагов 4, подтверждение записи значений флагов в которые осуществляется K одноразрядными сигналами разрешения записи, поступающими с выхода 29 разрешения блока формирования заданий 5 на входы 30 разрешения всех регистров флагов 4.

На выход данных устройства поступают операнды с выхода 9 данных блока центрального процессора 1. Не является существенным, куда конкретно затем поступают выходные данные, поэтому соответствующие цепи и устройства не показаны.

Работа блока формирования заданий 5 (фиг.2) заключается в выяснении возможности обработки одного (нескольких) операндов, относящихся в разным командным потокам, одновременно, формировании секционных заданий из поступивших в вычислительное устройство команд с относящимися к ним операндами и значениями регистров флагов, выдаче сформированных секционных заданий на выполнение, совмещение значений секционных флагов от нескольких вычислительных секций блока центрального процессора 1 после обработки операндов, разрядность которых превышает разрядность одной вычислительной секции m, обеспечении записи в регистры флагов 4 обновленных значений флагов.

Со второй группы входа 8 команд блока формирования заданий 5 запросы на обслуживание текущих команд из K потоков заданий, определяющие количество арифметико-логических секций блока центрального процессора 1, требуемых для обработки относящихся к командам операндов, поступают на вход 37 запросов узла выбора заданий 33. Одновременно с этим с выхода 17 занятости блока формирования заданий 5 на вход занятости узла выбора заданий 33 поступают N одноразрядных сигналов занятости вычислительных секций блока центрального процессора 1 в следующем такте работы вычислительного устройства.

Работа узла выбора заданий 33 заключается в анализе занятости N арифметико-логических секций в следующем такте работы вычислительного устройства, выборе для выполнения в блоке центрального процессора 1 потоков заданий, команды из которых будут обработаны в следующем такте работы вычислительного устройства, выработке управляющих сигналов, определяющих формирование до N секционных заданий для вычислительных секций блока центрального процессора 1 одновременно, в зависимости от требуемого командам количества вычислительных секций.

С выхода 41 адреса операнда узла выбора заданий 33 адреса, определяющие распределение в общем случае N операндов (частей операндов) заданий, которые будут обработаны в следующем такте работы вычислительного устройства, поступают на входы 42 адреса мультиплексоров операндов 35. Разрядность входа 42 адреса мультиплексора операндов 35 равна Log2(N•K) (ближайшему целому сверху от Log2(N•K) в случае неравенства нулю дробной части Log2(N•K). Одновременно с этим с входа 7 операндов блока формирования заданий 5 каждый из операндов, относящийся к текущим командам из K потоков заданий, поступает на входы информационные всех мультиплексоров операндов 35. В результате прохождения через мультиплексоры операндов 35 операнды (части операндов), относящиеся к тем командам, которые будут выполнены в следующем такте работы вычислительного устройства, располагаются в формируемых секционных заданиях для вычислительных секций, выделенных для обработки этих операндов.

С выходов 24 информационных N мультиплексоров операндов 35 секционные операнды, распределенные по вычислительным секциям, в которых они будут обработаны в следующем такте работы вычислительного устройства, поступают на выход операндов блока формирования заданий 5.

С выхода 43 адреса команд узла выбора заданий 33 адреса, определяющие расположение команд из K потоков заданий по вычислительным секциям блока центрального процессора 1 в следующем такте работы вычислительного устройства, и относящихся к потокам заданий этих команд значений регистров флагов, поступающих на входы 44 адреса соответствующих мультиплексоров команд 36 и на вход 45 адреса узла вывода флагов 34. Разрядность входа 44 адреса мультиплексора команд 36 равна Log2(K) (ближайшему целому сверху от Log2(K) в случае неравенства нулю дробной части Log2(K). Разрядность входа 45 адреса узла вывода флагов 34 равна N•Log2(K) (N, умноженное на ближайшее целое сверху от Log2(K) в случае неравенства нулю дробной части Log2(K)). Одновременно с этим с входа 23 информационного блока формирования заданий 5 на первые группы входов 38 информационных всех мультиплексоров команд 36 поступают значения флагов, относящиеся в общем случае к K потокам заданий, из регистров флагов 4; с первой группы входа 8 команд блока формирования заданий 5 на вторые группы входов 38 информационных всех мультиплексоров команд 36 поступают команды в общем случае из K потоков заданий. В результате прохождения через мультиплексоры команд 36, команды и значения флагов, относящиеся к тем потокам заданий, из которых будут выполнены команды в следующем такте работы вычислительного устройства, располагаются в соответствующих формируемых секционных заданиях.

С первой группы выходов 46 информационных N мультиплексоров команд 36, значения регистров флагов для N вычислительных секций блока центрального процессора 1, распределенные по вычислительным секциям, в которых они будут использованы в следующем такте работы вычислительного устройства, поступают на выход 25 флагов блока формирования заданий 5. Со второй группы выходов 46 информационных N мультиплексоров команд 36 секционные команды для N вычислительных секций блока центрального процессора 1, распределенные по вычислительным секциям, в которых они будут выполнены в следующем такте работы вычислительного устройства, поступают на выход 26 команд блока формирования заданий 5.

С выхода 28 признаков узла выбора заданий 33 признаки для N блоков микропрограммного управления 2 поступают на выход признаков блока формирования заданий 5. С выхода 10 запросов узла выбора заданий 33, K одноразрядных запросов на поступление в вычислительное устройство новых заданий из соответствующих потоков заданий подаются на выход блока формирования заданий 5 и вход 40 запросов узла вывода флагов 34.

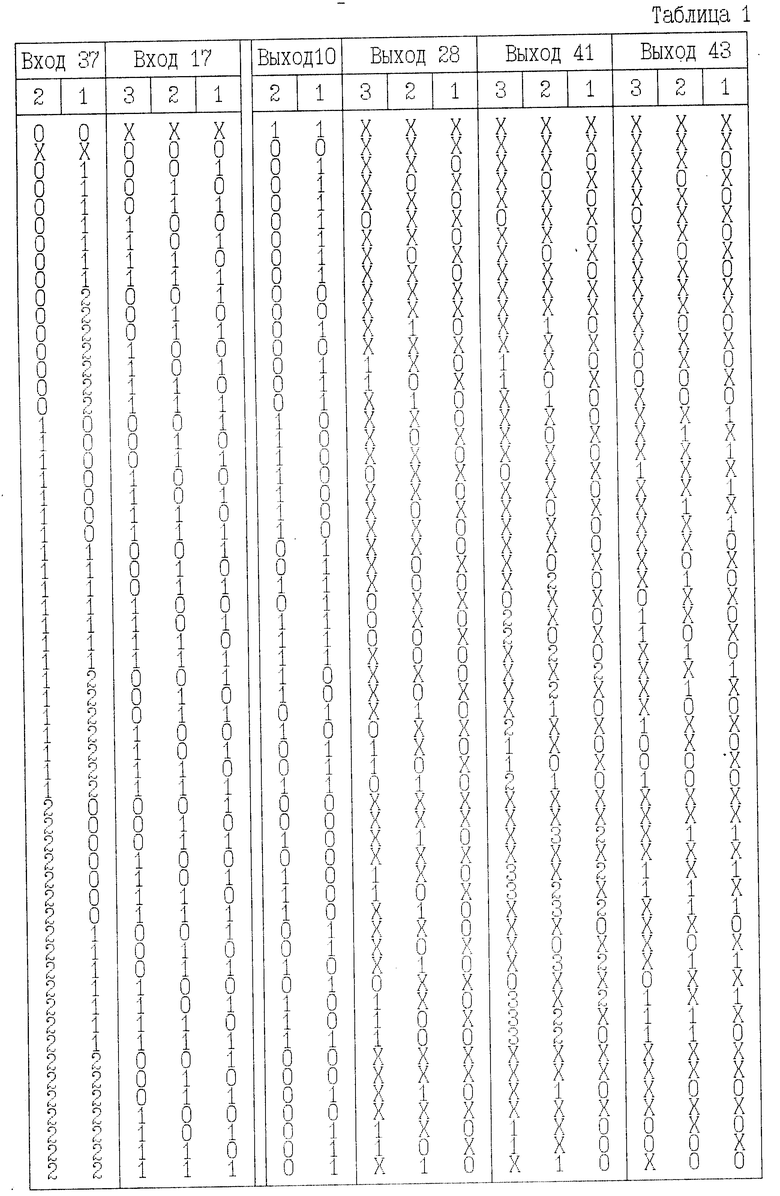

Табл. 1 задает пример закона функционирования узла выбора заданий 33 для случая, когда число вычислительных секций N равно трем и число входных командных потоков K равно двум. В табл.1 приняты следующие обозначения: 0 - логический ноль; 1 логическая единица; X конкретное логическое значение сигнала не является существенным.

Возможные значения i-ого компонента входа 37 запросов узла выбора заданий 33:

0 команда из i-ого потока заданий не требуются вычислительные секции блока центрального процессора 1;

1 для обработки операнда из i-ого потока заданий необходима одна вычислительная секция блок центрального процессора 1;

2 для обработки операнда из i-ого потока заданий необходимы две вычислительные секции блока центрального процессора 1.

Возможные значений i-ого компонента входа 17 занятости узла выбора заданий 33:

0 i-ая вычислительная секция блока центрального процессора 1 будет свободна в следующем такте работы вычислительного устройства;

1 i-ая вычислительная секция блока центрального процессора 1 будет занята в следующем такте работы вычислительного устройства.

Возможные значения i-ого компонента выхода 10 запросов операндов узла выбора заданий 33:

0 вычислительное устройство не может принять для обработки следующее задание из i-ого потока заданий;

1 вычислительное устройство может принять для обработки следующее задание из i-ого потока заданий.

Возможные значения i-ого компонента выхода 28 признаков узла выбора заданий 33:

0 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать первую часть операнда разрядности m;

1 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать вторую часть операнда разрядности m.

Возможные значения i-ого компонента выхода 41 адреса операндов узла выбора заданий 33:

0 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать первую часть операнда, относящегося к команде из первого потока заданий;

1 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать вторую часть операнда, относящегося в команде из первого потока заданий;

2 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать первую часть операнда, относящегося к команде из второго потока заданий;

3 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет обрабатывать вторую часть операнда, относящегося к команде из второго потока заданий.

Возможные значения i-ого компонента выхода 43 адреса команд узла выбора заданий 33:

0 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет выполнять команду из первого потока заданий;

1 i-ая вычислительная секция блока центрального процессора 1 в следующем такте работы вычислительного устройства будет выполнять команду из второго потока заданий.

После обработки в блоке центрального процессора 1 операндов, разрядность которых превышает разрядность одной вычислительной секции m, необходимо совместить значения флагов от нескольких вычислительных секций, обрабатывающих операнд из одного потока заданий. Для этого, дополнительно к информации, поступившей на вход 40 запросов, вход 45 адреса, вход 39 занятости узла вывода флагов 34, с входа 14 флагов формирования заданий 5 значения флагов, сформированные после работы N вычислительных секций блока центрального процессора 1, поступают на вход информационного узла вывода флагов 34. С синхровхода 6 блока формирования заданий 5 синхроимпульсы поступают на синхровход узла вывода флагов 34.

Работа узла вывода флагов 34 заключается в совмещении значений флагов, являющихся результатом работы вычислительных секций блока центрального процессора 1, которые обрабатывали операнды, разрядность которых превышает разрядность одной вычислительной секции m; в сохранении, до момента окончания обработки операндов в блоке центрального процессора 1, сигналов разрешения записи совмещенных значений флагов в регистры флагов 4.

С входа 45 адреса узла вывода флагов 34 N адресов, определяющие расположение команд из K потоков заданий по вычислительным секциям блока центрального процессора 1 в следующем такте работы вычислительного устройства и относящихся к потокам заданий этих команд значений регистров флагов, поступают на вход адреса элемента совмещения флагов 47.

Работа элемента совмещения флагов 47 заключается в совмещении значений флагов, являющихся результатом работы вычислительных секций блока центрального процессора 1, которые обрабатывали операнды, разрядность которых превышает разрядность одной вычислительной секции m (если разрядность операнда равна разрядности одной вычислительной секции, то соответствующие ей значения флагов изменениям не подвергаются).

С выхода 53 адреса элемента совмещения флагов 47 K адресов, определяющие, в какие регистры флагов 4 будут записаны значения сформированных в блоке центрального процессора 1 флагов после работы N вычислительных секций, поступают на вторые группы входов 52 информационных всех триггеров 48. Разрядность выхода 53 адреса элемента совмещения флагов 47 равна Log2(K) (ближайшему целому сверху от Log2(K) в случае неравенства нулю дробной части Log2(K)). Одновременно с этим с входа 40 запросов узла вывода флагов 34 на первые группы входов 52 информационных триггеров 48 поступают сигналы разрешения записи информации в регистры флагов 4. С приходом с синхровхода 6 узла вывода флагов 34 синхроимпульсов на синхровходы всех триггеров 48, производится запись информации в триггеры 48.

Сохранение сигналов разрешения записи в регистры флагов 4 и адресов регистров флагов 4, в которые будет производиться запись информации, производится в триггерах 48 в момент (t) поступления секционных заданий в блок центрального процессора 1 на выполнение. В блоке центрального процессора 1 обработка операндов может занимать более одного такта работы вычислительного устройства, поэтому сформированные адреса и сигналы разрешения записи потребуются в момент (t+i), когда обработка операндов будет полностью завершена и, соответственно, будут сформированы новые значения флагов. До этого момента (t+i) вся информация сохраняется в триггерах 48. В момент (t+i) с входа 14 информационного узла вывода флагов 34 значения флагов, сформированные после работы N вычислительных секций блока центрального процессора 1, поступают на вход информационного элемент совмещения флагов 47.

С выхода 54 информационного элемента совмещения флагов 47 в момент (t+i) совмещенные значения флагов поступают на первые группы входов 55 информационных всех мультиплексоров флагов 49. Одновременно с этим с выходов 56 информационных всех триггеров 48 адреса в общем случае для всех регистров флагов 4 поступают на входы адреса 58 всех мультиплексоров флагов 49, а сигналы разрешения для регистров флагов 4 на вторые группы входов 55 информационных всех мультиплексоров 49 и первые входы 57 разрешения всех мультиплексоров флагов 49. Одновременно с этим с входа 39 занятости узла вывода флагов 34 сигналы, показывающие занятость вычислительных секций в следующем такте работы вычислительного устройства, поступают на вторые входы 51 разрешения всех мультиплексоров флагов 49, что обеспечивает прохождение информации с входов 55 информационных соответствующих мультиплексоров флагов 49 на их выходы (установка i-ого одноразрядного сигнала 39 занятости, связанного с i-ой вычислительной секцией, из логического 0 в логическую 1, соответствует окончанию обработки операнда (части операнда) данной вычислительной секцией и ее освобождению в следующем такте работы вычислительного устройства). Одновременно с этим поступая на входы 50 синхронного сброса в общем случае всех триггеров 48, сигналы о занятости вычислительных секций в следующем такте работы вычислительного устройства сбросят с приходом синхроимпульсов на синхровходы всех триггеров 48, те триггеры 48, информация из которых попала на выходы 59 информационные соответствующих мультиплексоров флагов 49.

С первой группы выходов 59 информационных всех мультиплексоров флагов 49 K одноразрядных сигналов разрешения записи в регистры флагов 4 через выход 29 разрешения узла вывода флагов 34, поступают на выход разрешения блока формирования заданий 5. Со второй группы выходов 59 информационных всех мультиплексоров флагов 49 совмещенные значения флагов, относящиеся в общем случае к K потокам заданий через выход 31 информационный узла вывода флагов 34 поступают на выход информационный блока формирования заданий 5.

Табл. 2 задает пример закона функционирования элемента совмещения флагов 47 для случая, когда число вычислительных секций N равно трем и число входных командных потоков K равно двум. В табл.2 приняты следующие обозначения: 0

логический ноль; 1 логическая единица; X конкретное логическое значение сигнала не определено; Fi на вход соответствующего регистра флагов передаются значения флагов, сформированные при работе i-ой вычислительной секции блока центрального процессора 1; Fi#Fj на вход соответствующего регистра флагов передаются совмещенные значения флагов, сформированные при работе i-ой и j-ой вычислительной секции блока центрального процессора 1; ***** не является существенным какая конкретная операция выполняется.

Возможные значения i-ого компонента входа 45 адреса элемента совмещения флагов 47:

0 в i-ой вычислительной секции блока центрального процессора 1 обрабатывался операнд (часть операнда) из первого потока заданий;

1 в i-ой вычислительной секции блока центрального процессора 1 обрабатывался операнд (часть операнда) из второго потока заданий.

Возможные значения компоненты выхода 53 адреса элемента совмещения флагов 47:

0 в i-ый регистр флагов 4 должны быть помещены значения флагов, сформированные после обработки вычислительными секциями блока центрального процессора 1 операнда из первого потока заданий;

1 в i-ый регистр флагов 4 должны быть помещены значения флагов, сформированные после обработки вычислительными секциями блока центрального процессора 1 операнда из второго потока заданий.

Конкретная реализация операций совмещения значений флагов от работы нескольких вычислительных секций зависит от используемых в конкретной реализации вычислительного устройства флагов, а также форматов операндов (например, совмещенное значение флага нулевого результата устанавливается в логическую 1 лишь в случае, когда в логическую 1 установлены все совмещаемые значения флагов нулевого результата).

| название | год | авторы | номер документа |

|---|---|---|---|

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С ЧЕРЕДУЮЩИМСЯ ОБСЛУЖИВАНИЕМ НЕСКОЛЬКИХ КОМАНДНЫХ ПОТОКОВ | 1995 |

|

RU2101759C1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1559340A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Устройство для сопряжения ЦВМ с накопителями на магнитной ленте | 1985 |

|

SU1288708A1 |

| Мультиплексный канал | 1980 |

|

SU964620A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

Изобретение относится к вычислительной технике и может быть использовано в электронной цифровой вычислительной машине. Целью изобретения является повышение производительности вычислительного устройства. Указанная цель достигается тем, что вычислительное устройство содержит: блок центрального процессора, N блоков микропрограммного управления, блок N-портовой постоянной памяти микропрограмм, K регистров флагов, блок формирования заданий. Сущность изобретения состоит в том, что арифметико-логические секции, входящие в состав процессорного блока, управляются микропрограммно независимо друг от друга, позволяя тем самым выделять для обработки операндов из нескольких приоритетных командных потоков число секций, суммарная разрядность которых в точности соответствует разрядности этих операндов, а также осуществлять обработку операндов из нескольких приоритетных командных потоков одновременно в случае, когда оставшийся после выделения командному потоку с максимальным приоритетом использованный вычислительный ресурс центрального процессора может быть использован командными потоками с меньшими приоритетами. 1 з.п. ф-лы, 2 табл., 3 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Каган Б.М., Сташин В.В | |||

| Микропроцессоры в цифровых системах | |||

| - М.: Энергия, 1979 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Каган Б.М | |||

| Электронные вычислительные машины и системы | |||

| - М.: Энергоатомиздат, 1985 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| International Journal of mini and microcomputers, 1982, v | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Electronic Design, 1986, v | |||

| Нивелир для отсчетов без перемещения наблюдателя при нивелировании из средины | 1921 |

|

SU34A1 |

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Процессор мультиобработки данных | 1975 |

|

SU590745A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1997-12-20—Публикация

1995-12-28—Подача