Изобретение относится к электронно-вычислительной технике и радиотехнике, предназначено для формирования когерентных сигналов с частотной и фазовой модуляцией, может быть использовано в радиолокации, навигации и системах связи.

Известны цифровые синтезаторы частот, содержащие генератор тактовых импульсов, блок задержки, первый и второй регистры памяти, счетчик с предварительной установкой, первый и второй блоки постоянного запоминания, ЦАП, ФНЧ, первый и второй цифровые накопители [1].

Наиболее близким техническим решением (прототипом) к предлагаемому является цифровой синтезатор фазомодулированных сигналов, содержащий эталонный генератор, блок задержки, ждущий мультивибратор, блок постоянного запоминания, первый цифровой накопитель, первый сумматор, второй цифровой накопитель, второй сумматор, преобразователь кодов, ЦАП, ФНЧ, первый регистр памяти, делитель с переменным коэффициентом деления, второй регистр памяти, третий регистр памяти [2].

Однако, известные цифровые синтезаторы не позволяют формировать когерентные сигналы с возможностью управления фазовым сдвигом синтезируемых сигналов.

Технический результат - возможность оперативного управления сдвигом фаз формируемых сигналов - достигается за счет того, что в цифровой синтезатор фазомодулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; ждущий мультивибратор; первый цифровой накопитель; второй цифровой накопитель; преобразователь кодов; сумматор; первый цифроаналоговый преобразователь, выход которого соединен с входом первого фильтра нижних частот, выход последнего является первым аналоговым выходом цифрового синтезатора; второй регистр памяти, выход которого соединен с входом делителя с переменным коэффициентом деления, выход последнего подключен к входу последовательного переноса первого цифрового накопителя; третий регистр памяти, выход которого подключен ко второму входу сумматора; вход ждущего мультивибратора является входом запуска цифрового синтезатора, а его выход подключен к входам установки делителя с переменным коэффициентом деления, первого и второго цифровых накопителей; входы второго и третьего регистров памяти являются вторым и третьим входами цифрового синтезатора; выходы блока задержки подсоединены к тактовым входам делителя с переменным коэффициентом деления, первого и второго цифрового накопителей и первого цифроаналогового преобразователя, причем новым является то, что введены первый регистр памяти, второй цифроаналоговый преобразователь и второй фильтр нижних частот; вход первого регистра памяти является первым цифровым входом цифрового синтезатора, а его выход подключен к входу первого цифрового накопителя; выход первого цифрового накопителя подключен к входу второго цифрового накопителя, старший выходной разряд суммы которого подключен к входу управления инверсией преобразователя кодов, остальные старшие разряды через преобразователь кодов поступают на первый вход сумматора и на информационный вход первого цифроаналогового преобразователя; выход сумматора соединен с входом второго цифроаналогового преобразователя, выход последнего подключен к входу второго фильтра нижних частот, выход которого является вторым аналоговым выходом цифрового синтезатора; выход блока задержки соединен с тактовым входом второго цифроаналогового преобразователя.

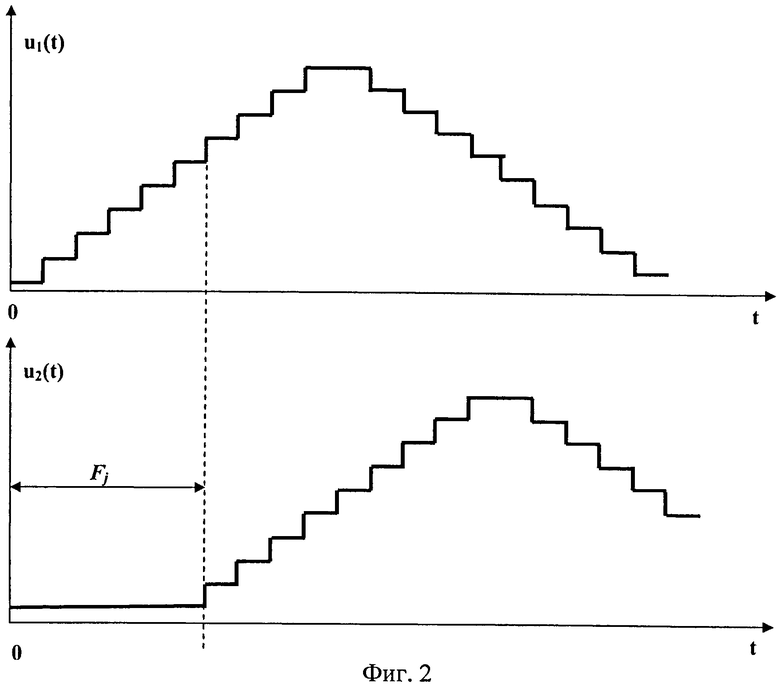

Цифровой синтезатор фазомодулированных сигналов (фиг.1) содержит эталонный генератор 1, блок задержки 2, ждущий мультивибратор 3, первый регистр памяти 4, первый цифровой накопитель 5, второй цифровой накопитель 6, преобразователь кодов 7, сумматор 8, первый цифроаналоговый преобразователь 9, первый фильтр нижних частот 10, второй регистр памяти 11, делитель с переменным коэффициентом деления 12, третий регистр памяти 13, второй цифроаналоговый преобразователь 14, второй фильтр нижних частот 15.

Цифровой синтезатор фазомодулированных сигналов содержит последовательно соединенные эталонный генератор 1 и блок задержки 2; ждущий мультивибратор 3, вход которого является входом запуска цифрового синтезатора; последовательно соединенные первый регистр памяти 4, первый цифровой накопитель 5, второй цифровой накопитель 6, преобразователь кодов 7, первый ЦАП 9, первый фильтр нижних частот 10; выход преобразователя кодов 7 также подключен к первому входу сумматора 8; последовательно соединенные второй регистр памяти 11 и делитель с переменным коэффициентом деления 12, выход которого подключен к входу последовательного переноса первого цифрового накопителя 5; третий регистр памяти 13, выход которого соединен со вторым входом сумматора 8, а выход последнего подключен к информационному входу второго ЦАП 14; выход второго ЦАП 14 подключен к входу второго ФНЧ 15; входы первого, второго и третьего регистров памяти являются цифровыми входами цифрового синтезатора фазомодулированных сигналов, а выходы первого и второго фильтров нижних частот - его аналоговыми выходами; выходы блока задержки подключены к соответствующим тактовым входам делителя с переменным коэффициентом деления 12, первого и второго цифровых накопителей 5 и 6, и первого и второго ЦАП 9 и 14; выход ждущего мультивибратора подключен к входам установки делителя с переменным коэффициентом деления 12, первого и второго цифровых накопителей 5 и 6.

Цифровой синтезатор фазомодулированных сигналов работает следующим образом:

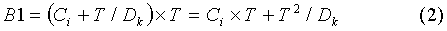

Эталонный генератор 1 вырабатывает сигнал опорной частоты «синусоидальной» формы, который поступает на вход блока задержки 2, формирующий разнесенные во времени последовательности прямоугольных импульсов, которые поступают на тактовые входы делителя с переменным коэффициентом деления 12, первого и второго цифровых накопителей 5 и 6, и первого и второго ЦАП 9 и 14, и служат для синхронизации основных узлов цифрового синтезатора. Пусть в момент времени t0 приходит импульс запуска uзап(t) на вход ждущего мультивибратора 3, тогда по сформированному им импульсу происходит запись кода Ci из первого регистра памяти 4 в первый накопитель 5, a Dk из второго регистра памяти 11 - в делитель с переменным коэффициентом деления 12, также происходит «обнуление» содержимого второго цифрового накопителя 6. Затем с каждым последующим тактовым импульсом в первом цифровом накопителе 5 результат суммирования будет изменяться по формуле

где Dk - коэффициент деления делителя 12,

Т - номер тактового импульса.

Во втором цифровом накопителе 6 результат суммирования будет изменяться по формуле

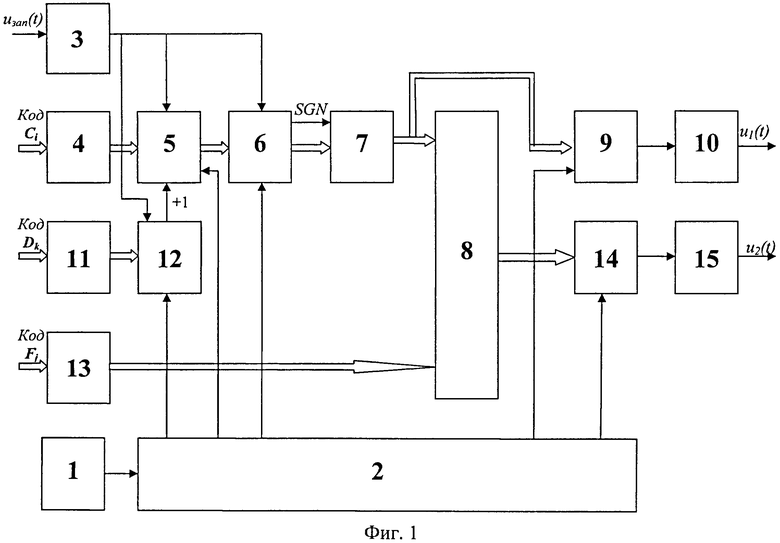

Старший выходной разряд суммы SGN второго цифрового накопителя 6 является знаковым и управляет инверсией преобразователя кодов 7. Если SGN=0, то на ЦАП 9 поступает прямой код суммы, но если SGN=1 - то обратный код суммы. Остальные старшие разряды через преобразователь кодов 7 поступают на информационный вход ЦАП 9 и на первый вход сумматора 8. На выходе первого ЦАП 9 формируется «ступенчатый» сигнал треугольной формы (фиг.2). Первый фильтр нижних частот 10 пропускает только первую гармонику синтезированного сигнала. Если принять, что

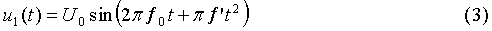

1/Dk=πƒ' - скорость изменения частоты синтезируемого сигнала;

Ci=2πƒ0 - начальная частота синтезируемого сигнала;

U0 - амплитуда выходного сигнала, то на выходе ФНЧ 10 будет присутствовать сигнал, описываемый формулой:

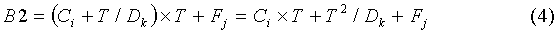

На вход третьего регистра памяти 13 поступает код Fj который будет определять сдвиг фаз формируемых сигналов. Далее код Fj поступает на второй вход сумматора 8, при этом результат суммирования на его выходе будет описываться формулой:

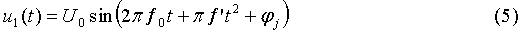

Тогда на выходе второго ЦАП 14 формируется сигнал, свинутый относительно первого ЦАП 9 на величину кода Fj. Тогда на выходе второго ФНЧ 15 формируется сигнал, описываемый формулой:

где φj=Fj - сдвиг фаз формируемых сигналов.

Код Dk определяет скорость изменения частоты синтезируемых сигналов; чем больше код Dk - тем меньше скорость изменения частоты выходного сигнала.

Таким образом, установив код Ci можно выставить начальную частоту формируемого сигнала, изменяя код Fj - управлять сдвигом фаз формируемых сигналов.

Литература

1. Патент РФ №2058659. МКИ H03B 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.1993. Опубл. 20.04.1996. Бюл.№11. - 4 с.

2. Патент РФ №2204196. МПК H03L 7/18. Цифровой синтезатор фазомодулированных сигналов / Рябов И.В., Рябов В.И. Заявл. 13.03.2001. Опубл. 10.05.2003. Бюл. №13. - 4 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2566962C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2014 |

|

RU2580444C1 |

| Цифровой вычислительный синтезатор двухчастотных частотно-модулированных сигналов | 2024 |

|

RU2826705C1 |

| Цифровой вычислительный синтезатор с частотной модуляцией | 2016 |

|

RU2628216C1 |

| Цифровой синтезатор фазоманипулированных сигналов | 2019 |

|

RU2701050C1 |

| Цифровой вычислительный синтезатор частотно-модулированных сигналов | 2019 |

|

RU2718461C1 |

| ЦИФРОВОЙ СИНТЕЗАТОР МНОГОФАЗНЫХ СИГНАЛОВ | 2010 |

|

RU2423782C1 |

| Цифровой вычислительный синтезатор для адаптивных систем связи с ППРЧ | 2020 |

|

RU2757413C1 |

Цифровой синтезатор фазомодулированных сигналов относится к электронно-вычислительной технике и радиотехнике, предназначен для формирования когерентных сигналов с частотной и фазовой модуляцией, может быть использован в радиолокации, навигации и системах связи. Достигаемый технический результат - возможность оперативного управления сдвигом фаз формируемых сигналов. Цифровой синтезатор фазомодулированных сигналов (фиг.1) содержит эталонный генератор 1, блок задержки 2, ждущий мультивибратор 3, первый регистр памяти 4, первый цифровой накопитель 5, второй цифровой накопитель 6, преобразователь кодов 7, сумматор 8, первый цифроаналоговый преобразователь 9, первый фильтр нижних частот 10, второй регистр памяти 11, делитель с переменным коэффициентом деления 12, третий регистр памяти 13, второй цифроаналоговый преобразователь 14, второй фильтр нижних частот 15. 2 ил.

Цифровой синтезатор фазомодулированных сигналов, содержащий последовательно соединенные эталонный генератор и блок задержки; ждущий мультивибратор; первый цифровой накопитель; второй цифровой накопитель; преобразователь кодов; сумматор; первый цифроаналоговый преобразователь, выход которого соединен с входом первого фильтра нижних частот, выход последнего является первым аналоговым выходом цифрового синтезатора; второй регистр памяти, выход которого соединен с входом делителя с переменным коэффициентом деления, выход последнего подключен к входу последовательного переноса первого цифрового накопителя; третий регистр памяти, выход которого подключен ко второму входу сумматора; вход ждущего мультивибратора является входом запуска цифрового синтезатора, а его выход подключен к входам установки делителя с переменным коэффициентом деления, первого и второго цифровых накопителей; входы второго и третьего регистров памяти являются вторым и третьим входами цифрового синтезатора; выходы блока задержки подсоединены к тактовым входам делителя с переменным коэффициентом деления, первого и второго цифровых накопителей и первого цифроаналогового преобразователя, отличающийся тем, что введены первый регистр памяти, второй цифроаналоговый преобразователь и второй фильтр нижних частот; вход первого регистра памяти является первым цифровым входом цифрового синтезатора, а его выход подключен к входу первого цифрового накопителя; выход первого цифрового накопителя подключен к входу второго цифрового накопителя, старший выходной разряд суммы которого подключен к входу управления инверсией преобразователя кодов, остальные старшие разряды через преобразователь кодов поступают на первый вход сумматора и на информационный вход первого цифроаналогового преобразователя; выход сумматора соединен с входом второго цифроаналогового преобразователя, выход последнего подключен к входу второго фильтра нижних частот, выход которого является вторым аналоговым выходом цифрового синтезатора; выход блока задержки соединен с тактовым входом второго цифроаналогового преобразователя.

| ЦИФРОВОЙ СИНТЕЗАТОР ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204196C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО- И ФАЗОМОДУЛИРОВАННЫХ СИГНАЛОВ | 2007 |

|

RU2358384C2 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2001 |

|

RU2204197C2 |

| СПОСОБ ПОЛУЧЕНИЯ ЛЕЧЕБНО-ПРОФИЛАКТИЧЕСКИХСЫВОРОТОК | 0 |

|

SU240934A1 |

| US 20110095830 A1, 28.04.2011. | |||

Авторы

Даты

2013-08-20—Публикация

2012-07-18—Подача