байтов, принятых от каналов, обеспечивается суммирующим блоком 10, коммутатором 11 и регистром 12. Режим ввода/вывода задается демультиплексором 14. Признаки конца массива каналов при вводе выявляются дешифратором 24, и через демультиплексор 15 устанавливаются соответствующие триггеры 18. Триггеры 18 опрашиваются счетчиком 16 и мультиплексором 28, который включает устройство регистрации. Сигт, налы запросов при вводе информации

поступают через входы 2 на триггер 6, который также опрашивается мультиплексором 13. Признаки конца массива каналов при выводе анализируются дешифратором 25, который вместе с дешифратором 24 через элемент ИЛИ-НЕ 26 управляет обнулением ячеек регистра 12. Адреса ячеек блока 20 памяти задаются счетчиками 8, 16 через коммутатор 19 и регистром 12. Ци.клы ввода и вывода информации из блока 20 памяти организуются блоком 17 управления. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Устройство для индикации | 1990 |

|

SU1795511A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА НА БАЗЕ МАТРИЦЫ ПРОЦЕССОРНЫХ ЭЛЕМЕНТОВ | 1998 |

|

RU2117326C1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| Устройство ввода-вывода матричной вычислительной системы | 1987 |

|

SU1529234A1 |

Изобретение относится к вычислительной технике и может быть использовано вГ7многоканальных системах ввода и регистрации информации. Цель изобретения - расширение области применения устройства. Устройство содержит входы 1.1-1.п. 2, 3, 4.1- 4.П, триггеры 5.1-5.П, 6, демультиплексор 7, счетчик 8,'мультиплексор 9, суммирующий блок 10, коммутатор 11, регистр 12. мультиплексор 13, демультиплексоры 14, 15, счетчик 16, блок 17 управления, триггеры 18.1-18.п, коммутатор 19, блок 20 памяти, регистр 21, мультиплексор 22, демультип,- лексор 23, дешифраторы 24, 25, элемент ИЛИ-НЕ 26, выходы 27, 28, вход 29. При вводе информация от каналов по входам 4,1-4.п через мультиплексор 9 подается в блок 20 памяти, запросы на ввод подаются на триггеры 5.1-'5.п. Опрос входов 4.1-4.П и триггеров 5.1-5.П через мультиплексоры 13, 9 производится счетчиком 8. Подсчет числа(/Сс<N <а

Изобретение относится к вычислительной технике и может быть использовано в многоканальных системах ввода и регистрации информации.

Известно устройство для ввода информации, содержащее регистр, коммутатор, блок управления, счетчик, мультиплексор, группу счетчиков, блок памяти.

Данное устройство обеспечивает ввод только однобитовой информации от дискретныхдатчиков, причем режим считывания информации из блока памяти обеспечивается только после накапливания определенного числа битов в приемных.счетчиках, что ограничивает область применения устройства и увеличивает время вывода информации.

Наиболее близким к предлагаемому является устройство для вывода информации, .содержащее блок памяти, коммутатор, первый и второй счетчики, регистр, первый и втррой-дешифраторы. блоки управления.

В известном устройстве ввод информации в параллельных кодах осуществляется только псгодному каналу, а в качестве исполнительного устройства при выводе инфор. мации используется печатающее устройство, что не позволяет применять известноеустройство в многоканальных системах ввода информации с другими устройствами регистрации, ограничивает область его использования.

Цель изобретения - расширение области применения устройства за счет ввода информации от нескольких каналов с независимым выводом ее на регистрирующее устройство.

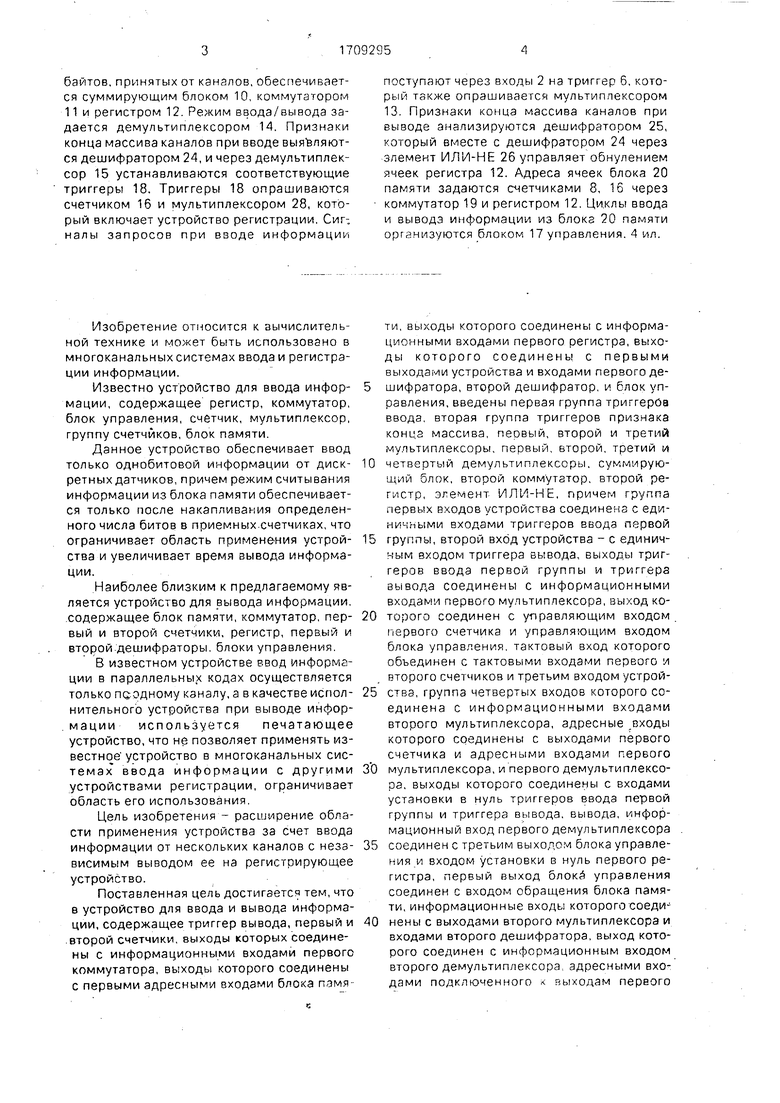

Поставленная цель достигается тем, что в устройство для ввода и вывода информации, содержащее триггер вывода, первый и .второй счетчики, выходы которых соединены с информационными входами первого коммутатора, выходы которого соединены с первыми адресными входами блока , выходы которого соединены с информационными входами первого регистра, выходы которого соединены с первыми выходами устройства и входами первого дешифратора, второй дешифратор, и блок управления, введены первая группа триггеров ввода, вторая группа триггеров признака конца массива, пеовый, второй и третий мультиплексоры, первый, второй, третий и

четвертый демультиплексоры, суммирующий блок, второй коммутатор, второй реri/iCTp, элемент ИЛИ-НЕ, причем группа первых входов устройства соединена с единичными входами триггеров ввода первой

группы, второй вход устройства - с единичным входом триггера вывода, выходы триггеров ввода первой группы и триггера вывода соединены с информационными входами первого мультиплексора, выход которого соединен с управляющим входом первого счетчика и управляющим входом блока управления, тактовый вход которого объединен с тактовыми входами первого и второго счетчиков и третьим входом устройства, группа четвертых входов которого соединена с информационными входами второго мультиплексора, адресные входы которого соединены с выходами первого счетчика и адресными входами первого

мультиплексора, и первого демультиплексора, выходы которого соединены с входами установки в нуль триггеров ввода первой группы и триггера вывода, вывода, информационный вход первого демультиплексора

соединен с третьим выходом блока управления и входом установки в нуль первого регистра, первый выход блоки управления соединен с входом обращения блока памяти, информационные входы которогосоединены с выходами второго мультиплексора и входами второго дешифратора, выход которого соединен с информационным входом второго демультиплексора. адресными входами подключенного к выходам первого

счетчика, а выходами - к единичным входам триггеров признака конца массива второй группы, выходы . которых соединены с информационными входами третьего мультиплексора, адресными входами подключенными к выходам второго счетчика, а выходом- к второму выходу устройства и управляющему входу второго счетчика, пятый вход устройства соединен с информационным входом третьего демультиплексора, адресными входами подключенного к выходам второго счетчика.а выходами - к входам установки в нуль триггеров признака конца массива второй группы, выходы первого и второго дешифраторов соединены соответствен но с первым и вторым входами элемента ,-НЕ, выход которого соединен с первым входом суммирующего блока и с управляющим входом второго коммутатора, входы которого соединены с выходами суммирующего блока, выходы коммутатора соединены с информационными входами второго регистра, управляющие входы записи и чтения которого объединены с выходом первого коммутатора, а тактовый вход второго регистра соединен с вторым выходом блока управления, выходы второго регистра соединены с группой вторых входов суммирующего блока и вторыми адресными входами блока памяти, вход установки режима которого объединены с ул.равляющим входом первого коммутатора, через согласующий резистор - с шиной источника питания и группой выходов четвертого демультиплексора, . адресными входами соединенного с выходами первого счетчика, а информационным входом - с нулевой шиной источника питания.

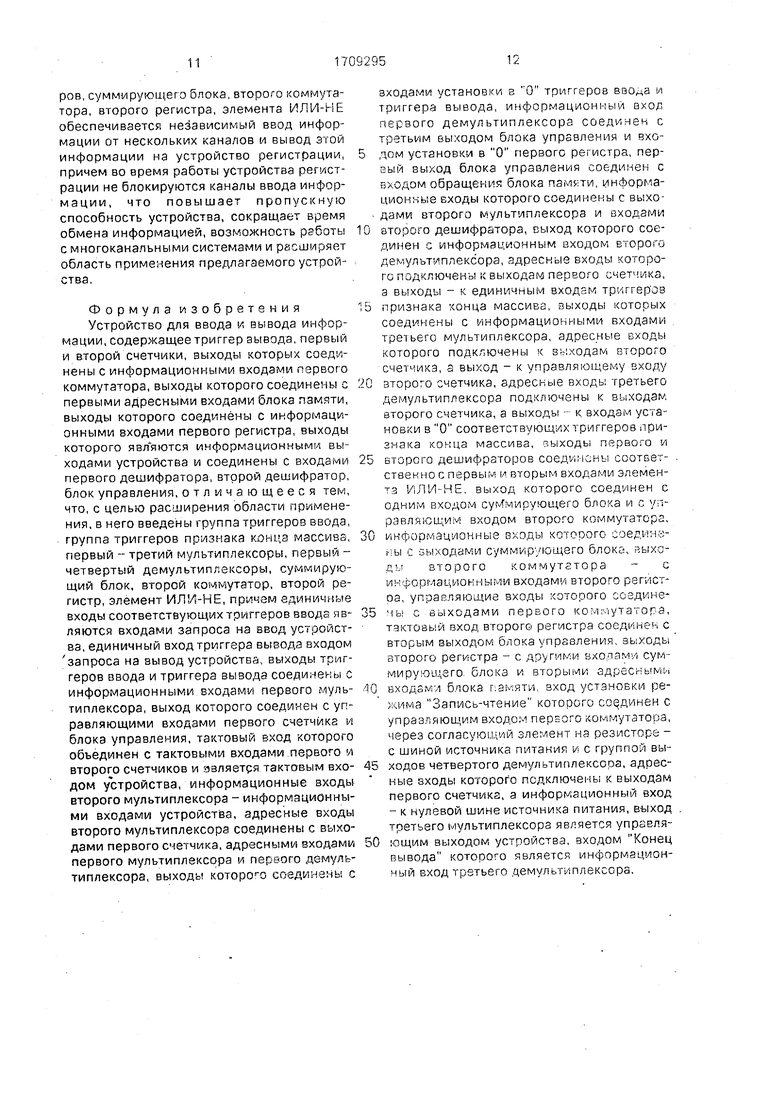

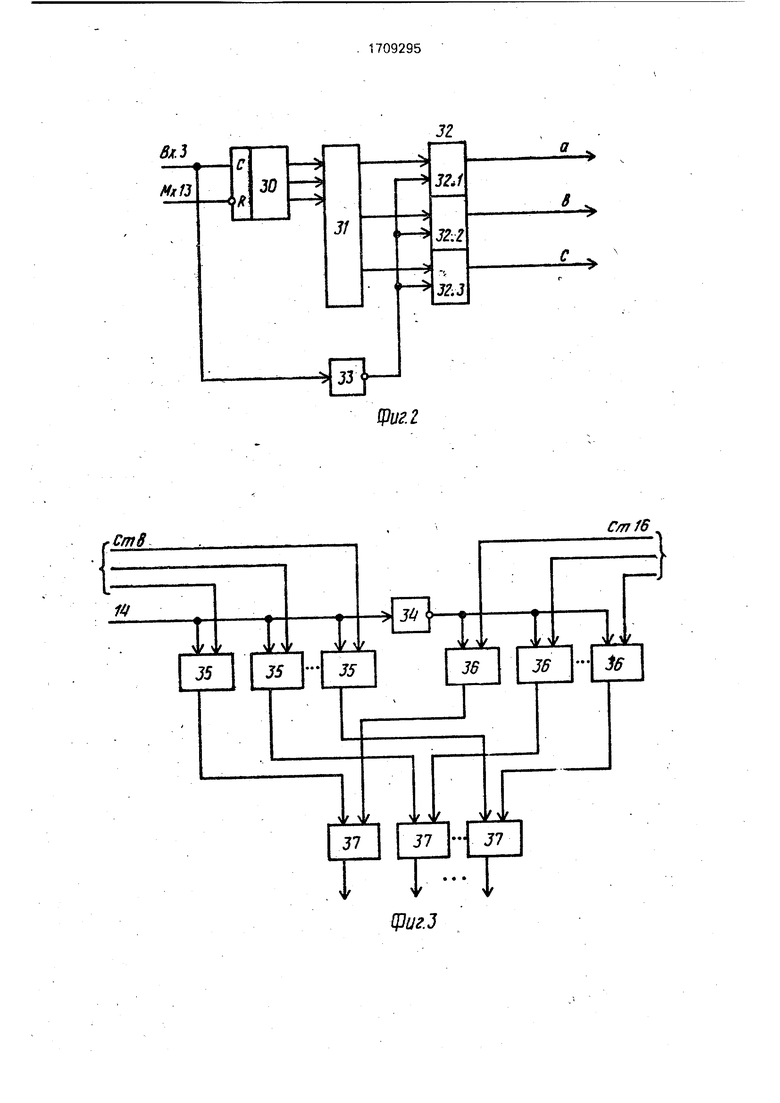

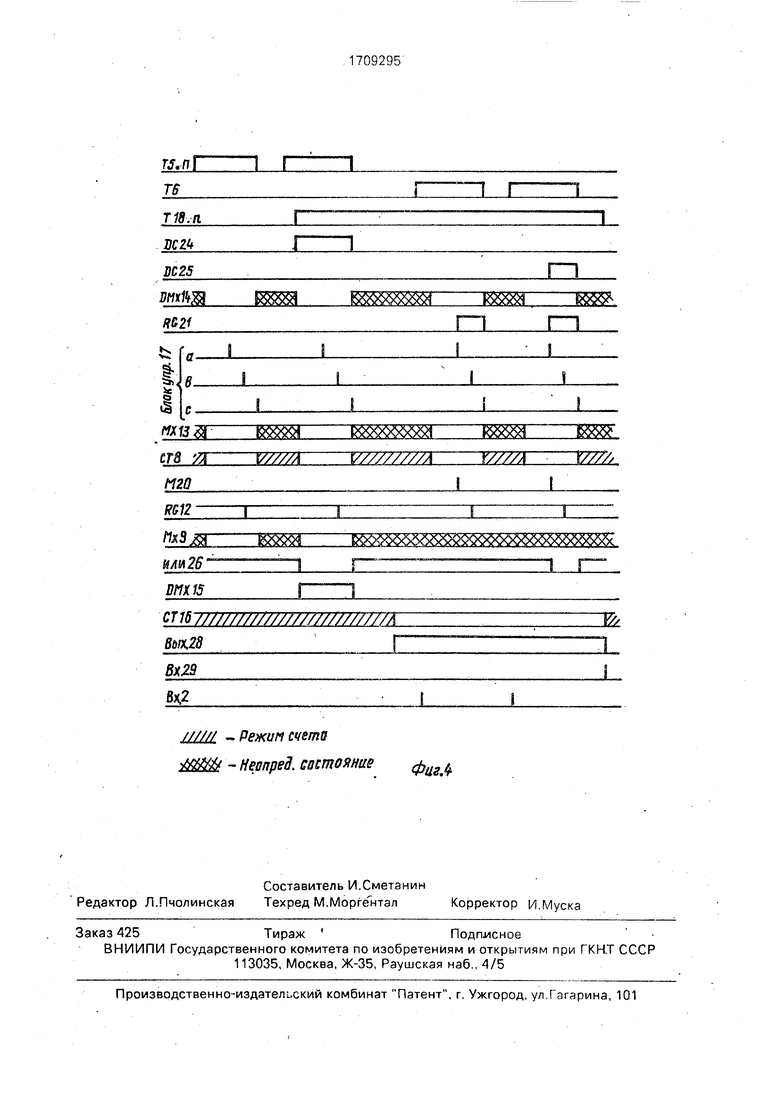

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема коммутатора; на фиг. 4 - временные диаграммы его работы.

Устройство содержит входы 1 запросов на ввод информации, вход 2 запроса на вывод информации, вход тактовый 3, информационные входы 4, группу триггеров 5 ввода, триггер б вывода, первый демультиплексор 7, первый счетчик 8, второй мультиплексор 9, суммирующий блок 10, второй коммутатор 11, второй регистр 12, первый мультиплексор 13, четвертый 14 и второй 15 демультиплексоры, второй счетчик 16, блок 17 управления, группу триггеров 18 признака конца массива, первый коммутатор 19, блок 20 памяти, первый регистр 21, третий мультиплексор 22, третий демультиплексор 23, второй 24 и первый 25 дешифраторы, элемент ИЛИ-НЕ 26, группу информацмонЬ ных выходов27, выход 28.уг:равления и вход 29 окончания вывода.

Блок 17 управления состоит из счетчика 30, дешифратора 31, коммутатора 32 и элемента НЕ 33.

0Коммутатор 19 содержит элементы НЕ

34, И 35 и 36 и ИЛИ 37.

Элементы, входящие в состав устройства, выполнены на микросхемах 564-й серии. Регистр 12 выполнен на многоцелевом регистре 564 ИР 11, каждому каналу соответствует ячейка, адресуемая по входам W при вводе информации в регистри по входам R при Считывании информации из регистра, импульс записи подается на вход С регистра. Триггеры 5 предназначены для фиксирования запросов от каналов при вводе информации, триггер 6 - для фиксирования запросов от регистрирующего устройства. Дешифратор 25 выявляет признак конца

массива (КМ) при вводе информации от каналов, дешифратор 26 - признак конца массива при вводе информации от каналов. Триггеры 18 фиксируют признаки КМ для каждого канала при вводе информации.

0 Блок 20 памяти обеспечивает хранение вводимой информации от каналоз. Суммирующий блок 10, коммутатор 11 и регистр 12 считывают число байтов, вводимых или выводимых устройством для каждого канала.

5 Счетчик 8 с мультиплексором 13 обеспечивает циклический опрос триггеров 5 и 6; счетчик 16 с демультиплексорам 22 - циклический опрос триггеров 18. Демультиплексор 14устанавливает режим ввода или

0. вывода информации. Демультиплексоры 7 и 23 предназначены для установки в нуль соответственно триггеров 5, 6 и 18. Демультиплексор 15 обеспечивает выборку соответствующего из триггеров 18 признака

5 КМ для текущего канала. PervicTp 21 обеспечивает хранение выдаваемых байтов информации. Входы 1 соединены с единичными входами триггеров 5, вход 2-е единичным входом триггера 6. Выходы триггеров 5 и 6

0 соединены с мульт11плексором 13, выход которого соединен с входом блока 17 управления и управляющим входом счетчика S. Тактовые входы, счетчиков 8 и 16 соединены с тактовым входом блока 17 управления и

5 входом 3 устройства. Выходы счетчика 8 соединены с адресными входами мультиплексоров 9 и 13 и демультиплексоров 7, 14 и 15 и коммутатором 19. Выходы мультиплексора 7 соединены с нулевыми входами триггеров 5 и 6. Выходы демультиплексора 14 соединены с согласующим резистором R, входом W/R блока 20 памяти, управляющими входами блока 17 управления и коммутатора 19. Выходы демультиплексора 15

соединены с входами триггеров 18. Выходы счетчика 16 соединены с коммутатором 19, адресными входами мультиплексора 22, демультиплексора 23. Выходы триггеров 18 соединены с входами мультиплексора 22, нулевые входы триггеров 18 - с выходами демультиплексора 23. Выход мультиплексора 22 соединен с выходом 28 и управляющим входом счетчика 16. Вход 29 соединен с D-входом демультиплексора 23. Входы А соединены с мультиплексором 9, выходы которого соединены с D-входами блока 20 памяти и дешифратором 24. Выход дешиф-. ратора 24 соединен с элементом ИЛИ-НЕ 26 и D-входом демультиплексора 15. Выходы коммутатора 19 соединены с адресными входами блока 20 паеС1яти и входами W, R регистра 12. Выходы блока 20 памяти соединены с регистром 21, выходами подключенного к выходам 27 и дешифратору 25. Выход дешифратора 25 соединен с элементом ИЛИ-НЕ 26, выход которого соединен с коммутатором 11 и входом суммирующего блока 10, последовательно включенного с коммутатором 11 и регистром 12. Выходы регистра 12 соединены с другими входами сумматора 10 и адресными входами блока 20 памяти. Первый выход блока 17 соединен с нулевым входом регистра 21, второй выходс управляющим входом блоха 20 памяти, третий выход - с тактовым входом регистра 12, четвертый выход - с D-входом демультиплексора 7.

Устройство работает следующим образом.

В исходном состоянии все элементы памяти, триггеры, регистры, счетчики, входящие в устройство, обнулены (цепи обнуления не показаны). Ввод информации от каналов в параллельных кодах осуществляется по входам 4.1-4.П, г1ри этом по соответствующим входам 1.1-1.П каналы выставляют импульсные сигналы запросов на йвод информации и соответствующие триггеры 5.1-5.П устанавливаются в единичное состояние. При подаче тактовых импульсов на вход 3 устройства счетчик 8 через мультиплексор 13 опрашивает выходы триггеров 5 и 6, а счетчик 16 через мультиплексор 22 - триггеры 18. При опросе, например, сработанного триггера 5.п на выходе мультиплексора 13 формируется сигнал, который останавливает счетчик 8. воздействуя на его управляющий вход, и запускает блок 17 управления. На выходах счетчика 8 формируется адрес п-го канала. При этом информационные входы 4.п через мультиплексор 9 подключаются к D-входам блока 20 памяти. Адрес п-го канала с выходов счетчика 8 подается на адресные входы

демультиплексоров 7, 14 и 15 и входы коммутатора 19. Демультиплексор 7 подключает третий выход блока 17 к нулевому входу триггера 5.п. Демультиплексор 15 подключает выход дешифратора 24 к единичному входу триггера 18.п. У демультиплексора 14 выходы, соответствующие адресам группы триггеров 5, объединены через согласующий резистор R с источником питания и

0 подключаются через демультиплексор14 к нулевой шине этого источника. Поэтому для адресов триггеров 5, т.е. для каналов ввода информации, на выходах демультиплексора 14 устанавливается нулевой потенциальный

5 сигнал, соответствующий режиму ввода информации в блок 20 памяти. Этот сигнал подается на управляющий вxoд.W/R блока 20 памяти и управляющий вход коммутатора 19, который подключает выходы счетчика 8

0 к первым адресным входам блока 20 памяти, на вторые адресные входы которого поступает адрес с выходов регистра 12.

Регистр 12 вместе с суммирующим блоком 10 и коммутатором 11 формируют число

5 байтов для каждого канала информации следующим образом.

При отсутствии сигналов на выходах дешифраторов 24, 25 на выходе элемента ИЛИ-НЕ 26 формируется единичный сигнал,

0 поступающий на вход суммируюиего блока 10 и открывающий коммутатор 11. Суммирующий блок 10 прибавляет единицу к числу, накапливаемому в соответствующей ячейке регистра 12, Указанная ячейка регистра 12

5 адресуется счетчиком 8 в режиме ввода информации по входу регистра 12. Сумма с выходов блока 10 через коммутатор 11 поступает на информационные входы регистра .12 и фиксируется в указанной ячейке

0 сигна.аом, подаваемым на С-вход регистра 12 с выхода Ь блока 17 управления. Эта сумма считывается из указанной ячейки регистра 12, адрес задан счетчиком 8 по входам R регистра 12. Считанная сумма

5 поступает на входы суммирующего блока 10 для модификации в следующих циклах работы блока 17 управления и т.д. Таким образом, при поступлении байтов информации п-го канала в соответствующих циклах блок

0 17 управления производит запись принятого числа байтов в соответствующую ячейку регистра 12. Код этого числа подается на вторые адресные входы блока20 памяти. В начальном положении дл.ч п-го канала

5 на выходах регистра 12 устаноплен нулевой код, соответствующий н /левог- / числу принятых байтов информации m /пниого канала.

В режиме ввода инс|-о мгЧ1и1 блок 17 вырабатывает три упр. сигнала

а, b, с. Сигнал а обеспечивает запись принятого от п-го канала байта информации в блок 20 памяти по адресу, заданному счетчиком 8 (адрес данного канала) и регистром 12 (число принятых байтов от данного канала). Сигнал Ь увеличивает на единицу содержимое ячейки регистра 12, адресованной счетчиком 6. Сигнал с через демультиплексор 7 устанавливает в нуль триггер 5.п. Этим завершается один цмкл вводаинформации. После сброса триггера 5,п снимается сигнал с выхода мультиплексора 13, отключается блок 17 управления и снова включается счетчик 8, и через мультиплексор 13 продолжается циклический опрос триггеров 5 и 6. Устройство работает аналогично при поступлении информации от других каналов и срабатывании других триггеров 5. Таким образом, в блоке 20 памяти в соответствующих зонах памяти накапливаются массивы информации, вводимые от разных каналов. Каждый байт, вводимый от п-го канала, анализируется дешифратором 24. При обнаружений байта признака конца массива (например, символа ), на выходе дешифратора 24 формируется сигнал, который подается на вход демультиНлексора 15 и вход элемента ИЛИНЕ 26. При опросе п-го канала сигнал дешифратора 24 через демультиплексор 15 устанавливает в.единичное состояние триггер 18.п, На выходе элемента ИЛИ-НЕ 26 устанавливается нулевой сигнал, который закрывает коммутатор 11 и на входы регистра 12 подаются нулевые сигналы. При этом в текущем цикле блока 17 управления сигнал Ь устанавливает ячейку п-го канала регистра 12.в нулевое состояние, подготавливая ее для последующего считывания массива данных, принятого от п-го канала. Триггеры 18 непрерывно опрашиваются сигналом от счетчика 16 и мультиплексором 22, При опросе сработанного триггера 18.п на выходе мультиплексора 22 формируется сигнал, который останавливает счетчик 16, и выдается по выходу 28 на пуск регистрирующего устройства, например, перфоратора. Регистрирующее устройство после выхода в режим регистрации подает по входу 2 импульсный сигнал запроса информации и устанавливает в единичное состояние триггер 6. При опросе триггера 6 счетчик 8 формирует адрес, по которому демультиплексор 14 отключает свои выходы от нулевой шины источника питания. На выходах демультиплексора 14 устанавливается единичный потенциальный сигнал, соответствующий режиму вывода информации. Этот сигнал подается на вход W/R блока 20 памяти и переключает через коммутатор 19

первые адресные входы блока 20 памяти к выходам счетчика 16, на выходах которого установлен адрес данного п-го канала. Аналогично описанному включается блок 17 управления, который в режиме вывода даннь1х в одном цикле также формирует управляющие сигналы а, Ь, с. Сигнал а считывает в регистр 21 байт информации из ячейки блока 20 памяти, адресуемой счетчиком 16 и регистром 12. Сигнал Ь увеличивает на единицу содержимое ячейки регистра 12, адресуемой счетчиком 16, т.е. ячейки п-го канала. Сигнал с устанавливает через демультиплексор 7 триггер 6 в нулевое состояние и обнуляет регистр 21. Счетчик 8 продолжает опрос триггеров 5 и 6. Байт информации из регистра 21 через выходы 27 подается в устройство регистрации. После этого регистрирующее устройство снова подает по входу 2 сигнал запроса следующего байта информацию данного пго канала и описанный процесс повторяется.

Каждый байт, выводимый в регистр 21,

5 анализируется дешифратором 25. При обнаружении символа конца массива через элемент ИЛИ-НЕ 26 устанавливается в нуль соответствующая ячейка в регистре 12, аналогично описанному. Регистрирующее устройство, получив символ конца массива, формирует на носителе разделительный участок, отделяющий зарегистрированный массив п-го канала от последующих регистрируемых массивов. После этого регистрирующее устройство по входу 29 выдает сигнал Конец вывода, который через демультиплексор 23, адресуемый счетчиком 16, устанавливает в нуль триггер 18.п. При этом, снимается сигнал с выхода мультиплексора 22, устройство регистрации отключается и снова включается счетчик 16 для опроса триггеров 18. Аналогично работает устройство при наличии признаков концамассива от других каналов, т.е.

5 срабатывании других триггеров 18.

Суммарное время опроса триггеров 5 и

6 с учетом времени цикла блока 17 управления меньше длительности периода между

запросами, выставляемыми по входам 1 устройства, и составляет десятки (сотни) мкс. Так как регистрирующие устройства являются медленно действующими, то период между запросами, поступающими по входу 2 на триггер 6 составляет единицы (десятки)

5 мс. Поэтому за время вывода байтов информации одного канала устройство успевает принять информацию от п-го числгг каналов, В предложенном устройстве за счет введения в него двух групп триггеров,-трех мультиплексоров,четырех демультиплексоров, сумммрующего блока, второго коммутатора, второго регистра, элемента ИЛИ-НЕ обеспечивается независимый ввод информации от нескольких каналов и вывод этой информации на устройство регистрации, причем во время работы устройства регистрации не блокируются каналы ввода информации, что повышает пропускную способность устройства, сокращает время обмена информацией, возможность ргботы с многоканальными системами и расширяет область применения предлагаемого устройства.

Формула изобретения Устройство для ввода к вывода информации, содержащее триггер вывода, первый и второй счетчики, выходы которых соединены с информационными входами первого коммутатора, выходы которого соединены с первыми адресными входами блока памяти, выходы которого соединены с информационными входами первого регистра, выходы которого являются информационными выходами устройства и соединены с входами первого дешифратора, второй ,цешифратор, блок управления, отличающееся тем, что, с целью расширения области применения, в него введены группа триггеров ввода, группа триггеров признака конца массива, первый - третий мультиплексоры, первый четвертый демультиплексоры, суммирующий блок, второй коммутатор, второй регистр, элемент ИЛИ-НЕ, причем единичные входы соответствующих триггеров ввода являются входами запроса на ввод устройства, единичный вход триггера вывода входом запроса на вывод устройства, выходы триггеров ввода и триггера вывода соединены с информационными входами первого мультиплексора, выход которого соединен с управляющими входами первого счетчика и блока управления, тактовый вход которого объединен с тактовыми входами первого и второго счетчиков и эвляетдя тактавым входом устройства, информационные входы второго мультиплексора - информационными входами устройства, адресные входы второго мультиплексора соединены с выходами первого счетчика, адресными входами первого мультиплексора и первого демультиплексора, выходы которо о соединены с

входами устано1зки в О триггеров ввода и триггера вывода, информационный вход первого демультиплексора соединен с третьим выходом блока управления, и входом установки в О первого регистра, первый выход блока управления соединен с входом обращения блока памяти, информационные входы которого соединены с выходами второго мультиплексора и входами

второго дешифратора, выход которого соединен с информационным входом второго демульт /плексора, адресные входы которого подключены к выходам первого счетчика, а выходы - к единичным входам триггеров

признака конца массива, выходы которых соединены с информационными входами третьего мультиплексора, адресные входы которого подключены к вуходам второго счетчика, а выход - к управляющему входу

второго счетчика, адресные входы третьего ,цемультиплексора подключены к выходам второго счетчика, а выходы - к входзм установки в О соответствующих триггеров признака конца массива, С5ыходы первого м

второго дешифраторов соедмманы соответствекно с первым и вторым входами элементз ИЛИ-НЕ, выход которого соединен с одним входом су Тгиирующего блока и с управля ощи 1 входом второго коммутатора,

информационные входы которого соединс;ны с зыходами суммирующего блока, выходи второго коммутатора - с информационными входами второго регистоа, управляющие входы которого сседи не

чы с 8ь ходами первого ком-лутатора, тактовый вход второго регистра соединен с вторым выходом блока управления, выходы второго рег /1стра - с другими входами суммирующего, блока и вторыгии здреснь М 1

входам:/ б.г1ока памяти, вход установки режима Запись-чтение которого соединен с управляющим входо.м первого коммутатора, через согласуюьцмй элемент на резисторе с шиной источника питания и с группой выходов четвертого демультиплексора, адресные входы которого подключены к выходам первого счетчика, а информационный вход - к нулевой шине источника питания, выход третьего мультиплексора является управляющим выходом устройства, вхо,дом Конец вывода которого является информационный вход третьего демультиплексора.

ШЩ Режим cvems

уУ - Нввпред. сотоянаё

| Устройство для ввода информации | 1983 |

|

SU1126945A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-01-30—Публикация

1990-05-31—Подача