Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых допускают распараллеливания на уровне команд.

Известно устройство, микропроцессор IA-64 (см. Шахнович И. Век нынешний и век грядущий. - ж. Электроника: Наука, технология, бизнес, N 6, 1999, стр. 8 - 11), реализующее параллелизм на командном уровне с использованием концепции "длинного командного слова". Устройство состоит из кэш-памяти команд 1-го уровня, кэш-памяти данных 1-го уровня, общей кэш-памяти 2-го и 3-го уровней, устройства управления, файла специализированных регистров: целочисленных, с плавающей запятой, ветвления и предикатов, группы функциональных устройств четырех типов: четыре устройства целочисленной арифметики, два устройства операций с плавающей запятой, три устройства ветвления, одно устройство доступа к памяти данных. Управление функциональными устройствами осуществляется централизованно с использованием длинных командных слов фиксированного размера, каждое из которых содержит три простые команды, определяющие операции трех различных функциональных устройств. Последовательность выполнения простых команд в слове, а также зависимость между словами определяется полем маски, находящимся в слове.

Недостатками данного устройства являются:

дополнительные расходы памяти под программный код, вызываемые фиксированным размером командного слова;

неоптимальное использование функциональных устройств и, как следствие, снижение производительности из-за несбалансированности количества функциональных устройств и количества простых команд в командном слове, специализации функциональных устройств и регистров, несоответствия пропускной способности функционального устройства памяти (максимум одно число за такт) возможностям функциональных устройств целочисленных операций и операций с плавающей запятой.

Известно также устройство, микропроцессор E2K (см. Кузьминский М. Отечественные микропроцессоры: Elbrus 2K - ж. Открытые системы, N 5-6, 1999, стр. 8 - 13), использующее эту же концепцию "длинного командного слова" для реализации параллелизма. Устройство состоит из кэш-памяти 1-го уровня, кэш-памяти данных 1-го уровня, общей кэш-памяти 2-го уровня, буфера предварительной подкачки, устройства управления, файла универсальных регистров и группы однотипных функциональных устройств, построенных на базе арифметико-логических устройств (АЛУ) и объединенных в два кластера. Длина командного слова, управляющего работой функциональных устройств, переменная.

К недостаткам данного устройства можно отнести снижение производительности устройства при дозагрузке кэш-памяти команд 1-го уровня из-за несоответствия скорости выборки команд и скорости его заполнения, а также при широком использовании данных, находящихся в общей кэш-памяти 2-го уровня и/или оперативной памяти.

Наиболее близкой, по технической сущности и достигаемому результату к заявленному устройству, является электронно-вычислительная машина QA-2 (Компьютеры на СБИС, Кн. 1, Пер. с япон. Мотоска Т., Томита С., Танака Х. и др. - М. : Мир, 1988, стр. 65-66, 155 - 158 - прототип). Данное устройство состоит из устройства управления, блока коллективных специализированных регистров, сети коммутации, N однотипных функциональных устройств (в описываемой конкретной реализации прототипа N = 4), построенных на базе универсальных арифметико-логических устройств. Сеть коммутации реализована по принципу "каждый с каждым", имеет N входов, 2N выходов и обеспечивает непосредственное соединение выхода любого арифметико-логического устройства с входами других арифметико-логических устройств.

Управление устройством централизованное. Длинное командное слово, фиксированного размера, содержит четыре поля (простых команд) для управления арифметико-логическими устройствами, поле для обращения к четырем различным банкам основной памяти и поле для управления последовательностью выполнения простых команд. Простые команды содержат информацию о коде выполняемой операции, длине операндов, адресе регистров источников левого и правого операндов арифметико-логического устройства, адресе регистров - получателей.

Недостатками известной ЭВМ являются следующие. Фиксированная длина командного слова приводит к неоптимальному использованию ресурсов памяти, а именно, поле присутствует в командном слове независимо от того, используется или не используется соответствующее ему арифметико-логическое устройство. Отсутствие возможности непосредственного приема арифметико-логическими устройствами данных, поступающих из памяти, так как данные должны быть предварительно занесены в блок коллективных регистров, приводит к снижению производительности устройства.

Задача изобретения - повышение производительности вычислительной системы.

Поставленная задача решается тем, что в предложенной синергической вычислительной системе, содержащей N функциональных блоков, коммутатор "каждый с каждым", имеющий N информационных входов, 2N адресных входов и 2N информационных выходов, согласно изобретению каждый функциональный блок содержит устройство управления, устройство памяти команд и операционное устройство, реализующее двуместные и одноместные операции, а также имеет два информационных входа, два адресных выхода и один информационный выход. Первый информационный вход k-го функционального блока (k = 1, ..., N) соединен с (2k - 1)-м информационным выходом коммутатора, второй информационный вход соединен с 2k-м информационным выходом коммутатора, первый адресный выход соединен с (2k - 1)-м адресным входом коммутатора, второй адресный выход соединен с 2k-м адресным входом коммутатора, информационный выход k-го функционального блока соединен с k-м информационным входом коммутатора.

Информационные входы функционального блока являются информационными входами устройства управления, адресные выходы функционального блока являются соответственно первым и вторым адресными выходами устройства управления, третий адресный выход устройства управления соединен с адресным входом устройства памяти команд, командный вход-выход устройства управления соединен с командным входом-выходом устройства памяти команд, управляющий выход устройства управления соединен с управляющим входом операционного устройства, первый и второй информационные выходы устройства управления соединены соответственно с первым и вторым информационными входами операционного устройства, информационный выход операционного устройства является информационным выходом функционального блока.

Операционное устройство содержит устройство ввода-вывода и/или арифметико-логическое устройство и/или устройство памяти данных, причем первый информационный вход операционного устройства является информационным входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, второй информационный вход операционного устройства является адресным входом устройства ввода-вывода и устройства памяти данных и вторым информационным входом арифметико-логического устройства, управляющий вход операционного устройства является управляющим входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, информационный выход устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных является информационным выходом операционного устройства.

Признаки в указанной взаимосвязи в процессе проведения поиска на новизну не обнаружены, являются существенными и в своей совокупности обеспечивают увеличение производительности системы. Достигается это следующим образом. Ввод в состав синергической вычислительной системы функциональных блоков, реализующих операции ввода-вывода и записи-чтения данных, подключение их к коммутатору таким же образом, как подключены другие блоки системы, позволяет исключить промежуточный информационный носитель в виде файла регистров и соответственно сократить время доступа к данным, а также увеличить, за счет перераспределения блоков внутри системы, поток данных, поступающих на обработку до объема, обеспечивающего максимально возможную загрузку функциональных блоков системы исходя из особенностей алгоритма решаемой задачи и аппаратных ограничений на количество функциональных блоков.

Децентрализация управления в синергической вычислительной системе и, как следствие, включение в структуру функциональных блоков устройства управления и устройства памяти команд, связанных указанным образом, а также распределенное управление коммутатором посредством адресных входов, подсоединенных к адресным выходам устройства управления, позволяет устранить задержки в вычислительном процессе, связанные с дозагрузкой программного кода. Это достигается тем, что в предлагаемой децентрализованной системе резко сокращается длина командного слова. Так, для системы состоящей из 16 функциональных блоков, длина командного слова для подавляющего большинства операций составит 16 разрядов, что в несколько раз меньше, чем длина простой команды у прототипа. Соответственно, исчезает необходимость в кэш-памяти команд. Требуемый темп поступления командных слов может быть реализован, например, методом параллельного доступа, обеспечивающего одновременное считывание последовательности командных слов.

Дополнительно следует также отметить, что унификация внутрисистемных межблочных связей, а также возможность включения в систему разнообразных, по реализуемому набору операций, функциональных блоков, позволяет в условиях конкретного применения для специализированных систем оптимизировать объем аппаратного обеспечения в части габаритно-массовых характеристик и потребляемой мощности.

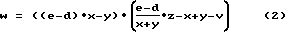

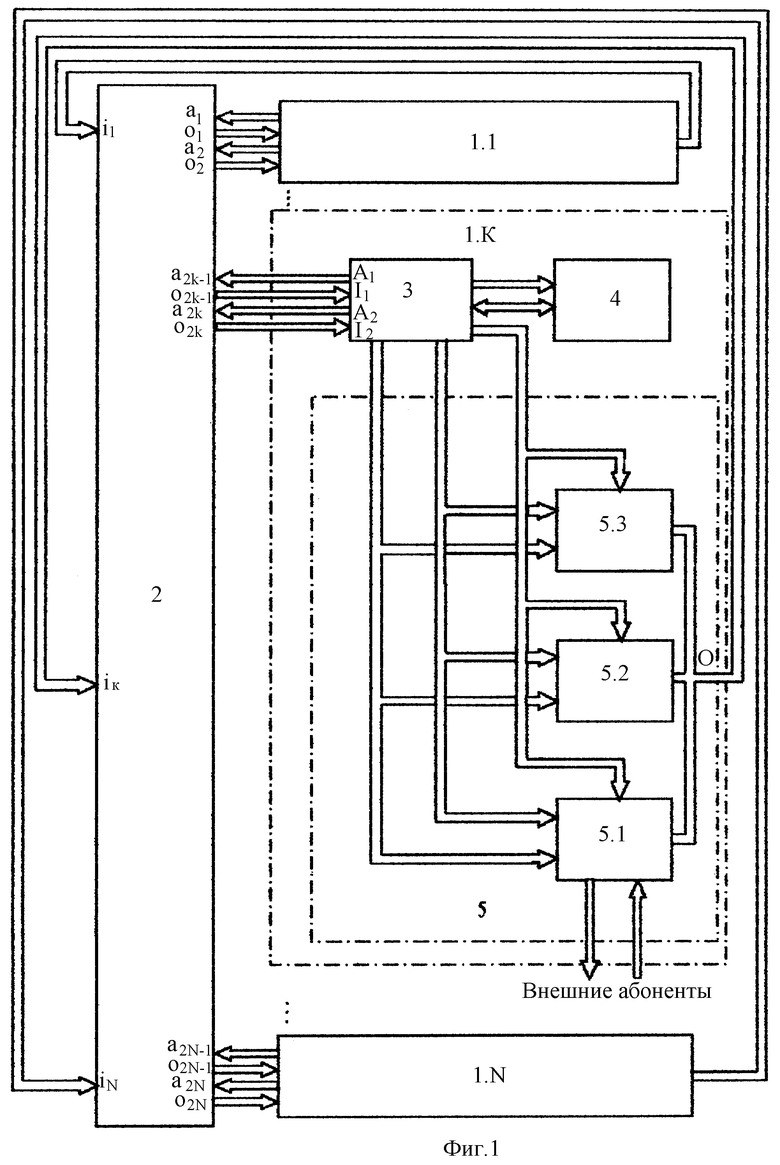

На фиг. 1 представлена структурная схема синергической вычислительной системы; на фиг. 2 - основные форматы командных слов; на фиг. 3 - информационный граф формулы (1) в ярусно-параллельной форме; на фиг. 4 - информационный граф формулы (2) в ярусно-параллельной форме.

Синергическая вычислительная система (фиг. 1) содержит функциональные блоки 1.1, ..., 1.k, ..., 1.N, коммутатор 2 типа "каждый с каждым", имеющий N информационных входов i1, ..., ik, ..., iN, 2N адресных входов a1, a2, ... , a2k-1, a2k, ..., a2N-1, a2N, 2N информационных выходов o1, o2, ..., o2k-1, o2k, . .., o2N-1, o2N. Каждый функциональный блок состоит из устройства управления 3, устройства памяти команд 4 и операционного устройства 5, реализующего двуместные и одноместные операции, а также имеет два информационных входа I1 и I2, два адресных выхода A1 и A2 и один информационный выход O. Информационный вход I1 k-го функционального блока (k = 1, ..., N) соединен с информационным выходом o2k-1 коммутатора, информационный вход I2 соединен с информационным выходом o2k коммутатора. Адресный выход A1 соединен с адресным входом a2k-1 коммутатора, адресный выход A2 соединен с адресным входом a2k коммутатора, информационный выход O k-го функционального блока соединен с информационным входом ik коммутатора. Информационные входы функционального блока являются информационными входами устройства управления 3, адресные выходы функционального блока являются соответственно первым и вторым адресными выходами устройства управления 3, третий адресный выход устройства управления 3 соединен с адресным входом устройства памяти команд 4, командный вход-выход устройства управления 3 соединен с командным входом-выходом устройства памяти команд 4, управляющий выход устройства управления 3 соединен с управляющим входом операционного устройства 5, первый и второй информационные выходы устройства управления соединены, соответственно, с первым и вторым информационными входами операционного устройства 5, информационный выход операционного устройства 5 является информационным выходом функционального блока. Операционное устройство 5 содержит устройство ввода-вывода 5.1 и/или арифметико-логическое устройство 5.2 и/или устройство памяти данных 5.3, причем первый информационный вход операционного устройства 5 является информационным входом устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3, второй информационный вход операционного устройства 5 является адресным входом устройства ввода-вывода 5.1 и устройства памяти данных 5.3 и вторым информационным входом арифметико-логического устройства 5.2, управляющий вход операционного устройства 5 является управляющим входом устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3, информационный выход устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3 является информационным выходом операционного устройства 5.

Синергическая вычислительная система работает следующим образом.

Исходное состояние устройства памяти команд, устройства памяти данных вводится из блоков, реализующих операции ввода-вывода ии представляет собой последовательность соответственно командных слов и слов данных.

Командные слова (фиг. 2) имеют два формата. Первый формат содержит поле кода операции и два поля с адресами аргументов. Второй формат состоит из поля кода операции, поля с адресом аргумента и поля с адресом команды, числа или абонента. Размер поля кода операций определяется номенклатурой операций и должен быть не менее ]log2P[ двоичных разрядов, где P - количество операций. Размер полей с адресами аргумента зависит от количества функциональных блоков и должен быть не менее ]log2N[ каждое. Размер поля с адресом команды, числа или абонента определяется максимальным объемом адресуемой памяти команд или памяти данных, либо числом внешних абонентов.

Разрядность данных определяется конкретной реализацией системы, а именно требованиями к типу, форме и точности представления данных.

Все функциональные блоки синергической вычислительной системы работают параллельно и независимо друг от друга, в соответствии с программами, находящимися в их устройствах памяти команд. Каждая команда реализует двуместную или одноместную операцию, которая выполняется определенное целое количество тактов и, по завершении выполнения, полученный результат поступает в коммутатор 2. Для выполнения очередной команды устройство управления 3 функционального блока выбирает из устройства памяти команд 4 очередное командное слово, распаковывает его, формирует в соответствии с кодом операции управляющие сигналы для операционного устройства 5, выбирает из соответствующих полей адреса аргументов. Адреса A1 и A2 по соответствующим адресным выходам поступают в коммутатор 2.

Коммутатор 2 осуществляет непосредственное соединение первого и второго информационных входов функционального блока с выходами функциональных блоков, номера которых получены коммутатором 2 соответственно по первому и второму адресным входам и обеспечивает передачу информации с выходов функциональных блоков на информационные входы. Полученная информация используется очередной командной в качестве аргументов при реализации операционным устройством 5 двуместной или одноместной операции. Адрес команды, числа или абонента, выбираемый из команд формата 2 обрабатывается непосредственно устройством управления при реализации отдельных команд передачи управления, чтения или записи числа, а также команд ввода-вывода.

Рассмотрим работу синергической вычислительной системы, на примере реализации двух формул:

Информационные графы, описывающие последовательность выполнения операций в формулах и их параллелизм, представлены в виде ярусно-параллельных форм на фиг. 3.4.

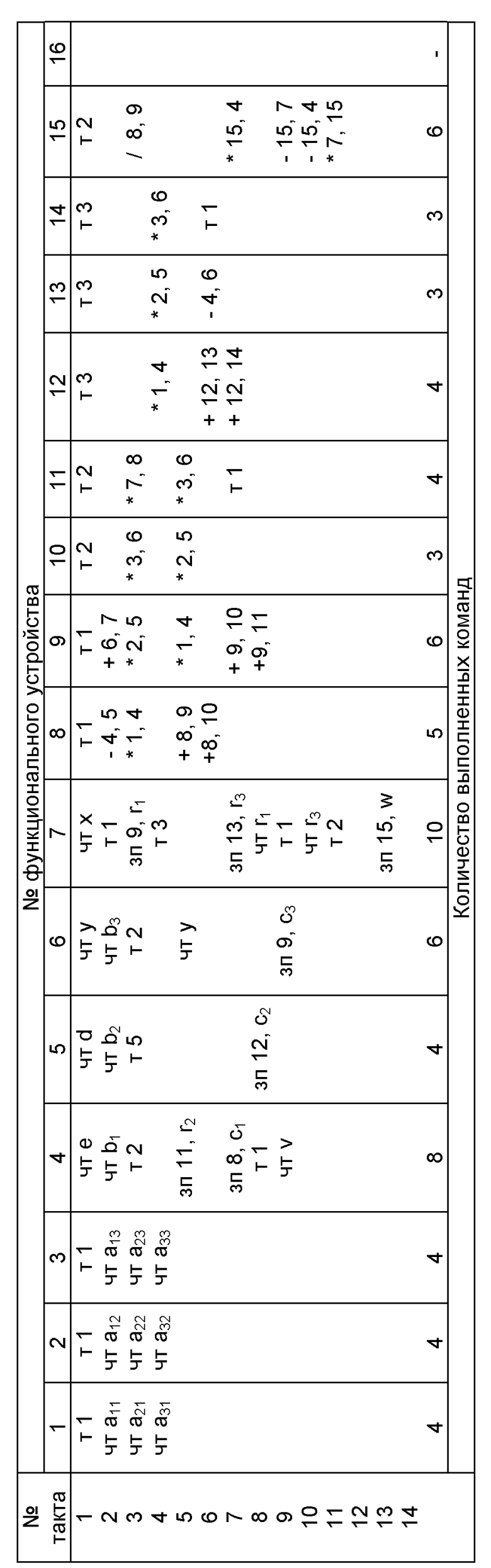

Примем, для определенности, что синергическая вычислительная система имеет 16 функциональных блоков. Из них 7 блоков, с номерами с 1 по 7, в составе операционного устройства имеют только память данных. Блоки с 8 по 15 являются чисто вычислительными, т. е. в составе операционного устройства имеют только арифметико-логическое устройство. Блок 16 является блоком ввода-вывода.

Блоки памяти реализуют команды чтения (чт) и записи (зп) формата 2 и имеют длительность один такт. Команда чтения является одноместной операцией, осуществляющей выборку числа из памяти данных по адресу, заданному в командном слове. Команда записи реализует двуместную операцию, первый аргумент которой это число, поступающее из коммутатора, а второй - адрес по которому осуществляется запись данного числа в память данных, заданный в командном слове.

Вычислительные блоки реализуют команды: сложения (+) и вычитания (-), длительностью 1 такт; умножения (*), длительностью 2 такта; деления (/), длительностью 4 такта. Все команды вычислительного блока имеют первый формат, реализуют двуместные операции, причем вычитаемое и делимое задается в первом адресе.

Для обеспечения согласованного взаимодействия блоков, когда есть необходимость задержать результат выполнения на выходе функционального блока, используется команда "трата" (т) второго формата, сохраняющая состояние блока t тактов. Сохранить результат на один такт можно также, организовав запись в рабочую ячейку памяти данных. Записываемое число, по завершении операции, не только заносится в память данных, но и поступает на выход функционального блока. При выполнении многотактных операций, результат выполнения предыдущей операции сохраняется на выходе функционального блока, до последнего такта текущей операции.

Примем следующую форму записи командных слов:

Формат 1

Формат 2

или

или

где <мнемокоп> - условное обозначение кода операции; <номер> - число от 1 до 16, указывающее номер функционального блока, результаты которого используются в качестве аргумента при выполнении операции; <имя> - наименование аргумента, адрес которого (после трансляции и загрузки программ) будет сформирован в поле адреса числа.

В командах "трата" на месте имен записывается число.

Разместим элементы матрицы (a11, a12, a13, a21, a22, a23, a31, a32, a33) по столбцам в блоках памяти 1-3. Векторы (b1, b2, b3) и (c1, c2, c3) поэлементно в блоках памяти 4-6. Переменные e, z, v в четвертом блоке памяти. Переменные d, y соответственно в пятом и шестом блоках. Переменные x, w в седьмом блоке памяти.

При программировании, для сохранения промежуточных результатов, введем дополнительные операнды, а именно рабочие ячейки r1 и r3 в седьмом функциональном блоке. Для сохранения результата на один такт с одновременным освобождением вычислительного блока, введем фиктивный операнд r2 в четвертом блоке. Запись в эту ячейку производится, но записанный результат далее не используется.

Результаты программирования работы функциональных блоков при вычислении данных формул представлены в таблице.

В последней строке таблицы приведено количество выполненных команд каждым функциональным блоком.

| название | год | авторы | номер документа |

|---|---|---|---|

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2005 |

|

RU2292075C1 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| УСТРОЙСТВО КОММУТАЦИИ | 2008 |

|

RU2410747C2 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1168963A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых допускают распараллеливание на уровне команд. Технический результат заключается в повышении производительности вычислительной системы. Технический результат достигается за счет того, что в синергической вычислительной системе, содержащей N функциональных блоков, коммутатор "каждый с каждым", каждый функциональный блок состоит из устройства управления, устройства памяти команд и операционного устройства, а операционное устройство содержит устройство ввода-вывода, и/или арифметико-логическое устройство/или устройство памяти данных. 4 ил., 1 табл.

Синергическая вычислительная система, содержащая N функциональных блоков, коммутатор "каждый с каждым", имеющий N информационных входов, 2 N адресных входов и 2 N информационных выходов, отличающаяся тем, что каждый функциональный блок состоит из устройства управления, устройства памяти команд и операционного устройства, реализующего двуместные и одноместные операции, а также имеет два информационных входа, два адресных выхода и один информационный выход, причем первый информационный вход k-го функционального блока (k= 1, . . . , N) соединен с (2k-1)-м информационным выходом коммутатора, второй информационный вход соединен с 2k-м информационным выходом коммутатора, первый адресный выход соединен с (2k-1)-м адресным входом коммутатора, второй адресный выход соединен с 2k-м адресным входом коммутатора, информационный выход k-го функционального блока соединен с k-м информационным входом коммутатора, информационные входы функционального блока являются информационными входами устройства управления, адресные выходы функционального блока являются соответственно первым и вторым адресными выходами устройства управления, третий адресный выход устройства управления соединен с адресным входом устройства памяти команд, командный вход-выход устройства управления соединен с командным входом-выходом устройства памяти команд, управляющий выход устройства управления соединен с управляющим входом операционного устройства, первый и второй информационные выходы устройства управления соединены соответственно с первым и вторым информационными входами операционного устройства, информационный выход операционного устройства является информационным выходом функционального блока, а операционное устройство содержит устройство ввода-вывода, и/или арифметико-логическое устройство, и/или устройство памяти данных, причем первый информационный вход операционного устройства является информационным входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, второй информационный вход операционного устройства является адресным входом устройства ввода-вывода и устройства памяти данных и вторым информационным входом арифметико-логического устройства, управляющий вход операционного устройства является управляющим входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, информационный выход устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных является информационным выходом операционного устройства.

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1998 |

|

RU2148857C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

| СПОСОБ ПОЛУЧЕНИЯ ПАРАВОЛЬФРАМАТА АММОНИЯ | 0 |

|

SU171856A1 |

Авторы

Даты

2002-02-10—Публикация

2000-06-13—Подача