Изобретение относится к вычислительной технике и может быть использовано при построении асинхронных синергических вычислительных систем.

Известно устройство, коммутатор асинхронной синергической вычислительной системы (пат. RU №2198422 - прототип), объединяющее N функциональных блоков в систему и обеспечивающее реализацию этими функциональными блоками параллелизма на командном уровне, представленного в виде ярусно-параллельной формы с ограничением на длину информационной связи между ярусами (не более одного яруса).

Указанное устройство является однонаправленным полносвязным коммутатором, размерностью N×2N, обепечивающим передачу N результатов выполнения операций предыдущего яруса в качестве 2N аргументов для выполнения операций следующего яруса.

Все результаты, поступающие в коммутатор, идентифицируются двумя параметрами:

- номером функционального блока, сформировавшего данный результ;

- динамически вычисляемой идентификационной меткой (тегом) яруса, к которому принадлежит данная операция.

Значение тега, при выдаче результата в коммутатор, увеличивается на единицу, и оно становится равным значению тега следующего яруса, операции которого используют поступающие результаты в качестве аргументов.

При декодировании команд очередного яруса, функциональные блоки сообщают коммутатору, какие результаты (от каких функциональных блоков) нужны им в качестве первого и/или второго аргументов. Коммутатор запоминает эти запросы и при поступлении требуемых результатов выдает их соответствующим функциональным блокам.

Указанный коммутатор состоит из N узлов коммутации, каждый из которых осуществляет отбор поступающих результатов для одного конкретного функционального блока. Каждый узел коммутации, в свою очередь, состоит из N устройств выбора, каждое из которых принимает и отбирает результаты, поступающие от одного конкретного функционального блока.

Все устройства выбора однотипные и состоят из блока формирования признаков выбора, памяти признаков выбора и двух буферных блоков FIFO-памяти для первого и второго аргументов.

Блок формирования признаков выбора и память признаков выбора обеспечивают позиционное запоминание значений тегов результатов, которые должны быть отобраны из поступающего потока результатов, сформированных функциональным блоком, связанным с данным устройством выбора. Если значение тега очередного поступившего результата отмечено в памяти признаков выбора как запрошенное, то этот результат записывается в FIFO-память.

Буферные блоки FIFO-памяти обеспечивают буферизацию неравномерного темпа поступления отобранных результатов и их временное хранение до момента выдачи в функциональный блок.

Каждый узел коммутации имеет две выходные информационные шины для передачи, соответственно, значения первого и второго аргументов в функциональный блок. Буферные блоки FIFO-памяти, принадлежащие данному узлу и содержащие первые (вторые) аргументы, поочередно (циклически) получают доступ к соответствующей первой (второй) шине для передачи накопленных значений аргументов, вне зависимости от количества накопленных аргументов.

Недостатком подобной системы обслуживания запросов на доступ к выходной шине является, при небольшом потоке аргументов, возможная непродуктивная задержка при передаче аргументов. Максимальное значение ее может достигать N-1 такт.

К недостаткам данного устройства также можно отнести неоптимальное использование аппаратных ресурсов при реализации FIFO-памяти. А именно, поскольку FIFO-память в данном устройстве нет имеет сигнала переполнения, то ее объем должен обеспечивать хранение максимально возможного количества результатов, которое определяется диапазоном изменения тега. При распределении потоков отобранных результатов, близком к равномерному, реально используемая FIFO-память может иметь объем в N раз меньше.

Задачей настоящего изобретения является повышение производительности синергических вычислительных систем и сокращение аппаратных затрат на реализацию устройства коммутации.

Поставленная задача решается тем, что предложенное устройство коммутации состоит из N однотипных узлов коммутации, каждый из которых имеет N информационных входов, N идентификационных входов результатов, N входов признаков готовности результатов, обеспечивающих прием значений и тегов результатов, а также имеет: 2 адресных входа, 2 входа признаков аргументов, один идентификационный вход аргументов - для приема запросов на результаты; 2 информационных выхода, 2 идентификационных выхода аргументов, 2 выхода признаков готовности аргументов - для передачи отобранных результатов в функциональный блок. Узел коммутации состоит из N однотипных устройств выбора, содержащих регистр логического номера, имеющий размерность ]log2N[ разрядов, блок формирования признаков выбора, память признаков выбора, имеющую размер L двухбитовых слов и два буферных блока FIFO-памяти. Во всех узлах коммутации для k-го устройства выбора (k=1,…, N) k-й информационный вход соединен с первыми информационными входами буферных блоков FIFO-памяти, k-й идентификационный вход результата соединен со вторыми информационными входами буферных блоков FIFO-памяти и адресным входом чтения памяти признаков выбора, k-й вход признака готовности результата соединен с сигнальным входом чтения памяти признаков выбора, а содержимое регистра логического номера равно k. Во всех устройствах выбора k-го узла коммутации первый адресный вход узла коммутации соединен с адресными входами первого аргумента блоков формирования признаков выбора, второй адресный вход узла коммутации соединен с адресными входами второго аргумента блоков формирования признаков выбора, первый вход признаков аргументов соединен с входами признака первого аргумента блоков формирования признаков, второй вход признаков аргументов соединен с входами признака второго аргумента блоков формирования признаков, идентификационный вход аргумента соединен с адресными входами записи памятей признаков выбора. Также во всех устройствах выбора выход регистра логического номера соединен с входом логического номера блока формирования признаков выбора, выход признака наличия аргументов блока формирования признаков выбора соединен с сигнальным входом записи памяти признаков выбора, выходы признаков наличия первого и второго аргументов блоков формирования признаков выбора соединены соответственно с первым и вторым информационными входами памяти признаков выбора, первый информационный выход памяти признаков выбора соединен с сигнальным входом записи первого буферного блока FIFO-памяти, второй информационный выход памяти признаков выбора соединен с сигнальным входом записи второго буферного блока FIFO-памяти. Кроме того, все первые информационные выходы первых буферных блоков FIFO-памяти k-го узла коммутации объединены и являются первым информационным выходом данного узла коммутации, вторые информационные выходы первых буферных блоков FIFO-памяти объединены и являются первым идентификационным выходом аргументов узла коммутации, выходы признаков готовности первых буферных блоков FIFO-памяти объединены и являются первым выходом признаков готовности аргументов узла коммутации. Все первые информационные выходы вторых буферных блоков FIFO-памяти k-го узла коммутации объединены и являются вторым информационным выходом данного узла коммутации, вторые информационные выходы вторых буферных блоков FIFO-памяти объединены и являются вторым идентификационным выходом аргументов узла коммутации, выходы признаков готовности вторых буферных блоков FIFO-памяти объединены и являются вторым выходом признаков готовности аргументов узла коммутации. Согласно изобретению все буферные блоки FIFO-памяти узла коммутации имеют выходной сигнал запроса и входной сигнал разрешения. Каждый узел коммутации имеет два блока арбитража, причем выходные сигналы запроса первых буферных блоков FIFO-памяти являются входными сигналами запроса первого блока арбитража, входные сигналы разрешения первых буферных блоков FIFO-памяти являются выходными сигналами разрешения первого блока арбитража. Выходные сигналы запроса вторых буферных блоков FIFO-памяти являются входными сигналами запроса второго блока арбитража, входные сигналы разрешения вторых буферных блоков FIFO-памяти являются выходными сигналами разрешения второго блока арбитража. При наличии данных в буферных блоках FIFO-памяти они формируют сигналы запроса в блоки арбитража на доступ к соответствующим объединенным выходам коммутатора, а блоки арбитража осуществляют известным способом при поступлении нескольких запросов от буферных блоков FIFO-памяти выбор наиболее приоритетного буферного блока FIFO-памяти и выдачу ему сигнала разрешения на выдачу информации.

Для осуществления второго варианта настоящего изобретения необходимо, чтобы хотя бы один буферный блок FIFO-памяти имел сигнальный выход переполнения. При этом имеющиеся сигнальные выходы переполнения всех буферных блоков FIFO-памяти k-ых устройств выбора всех узлов коммутации объединяются схемами ИЛИ и образуют сигнал запрета приема информации от k-го функционального блока.

Признаки в указанной взаимосвязи в процессе поиска на новизну не обнаружены, являются существенными и, в своей совокупности, обеспечивают увеличения производительности асинхронных синергических вычислительных систем и сокращение аппаратных затрат на их реализацию. Достигается это следующим образом. Отказ от поочередного представления буферным блокам FIFO-памяти доступа к выходам узла коммутации и замена этой схемы на блоки арбитража позволяет сократить время доступа, так как конкурировать за этот ресурс будут только те блоки, которым он необходим. Введение обратной связи (сигнал запрета приема информации) от устройства коммутации к функциональным блокам позволяет существенно, до L раз, сократить объем FIFO-памяти, хотя при этом возможно замедление работы функционального блока из-за занятости FIFO-памяти.

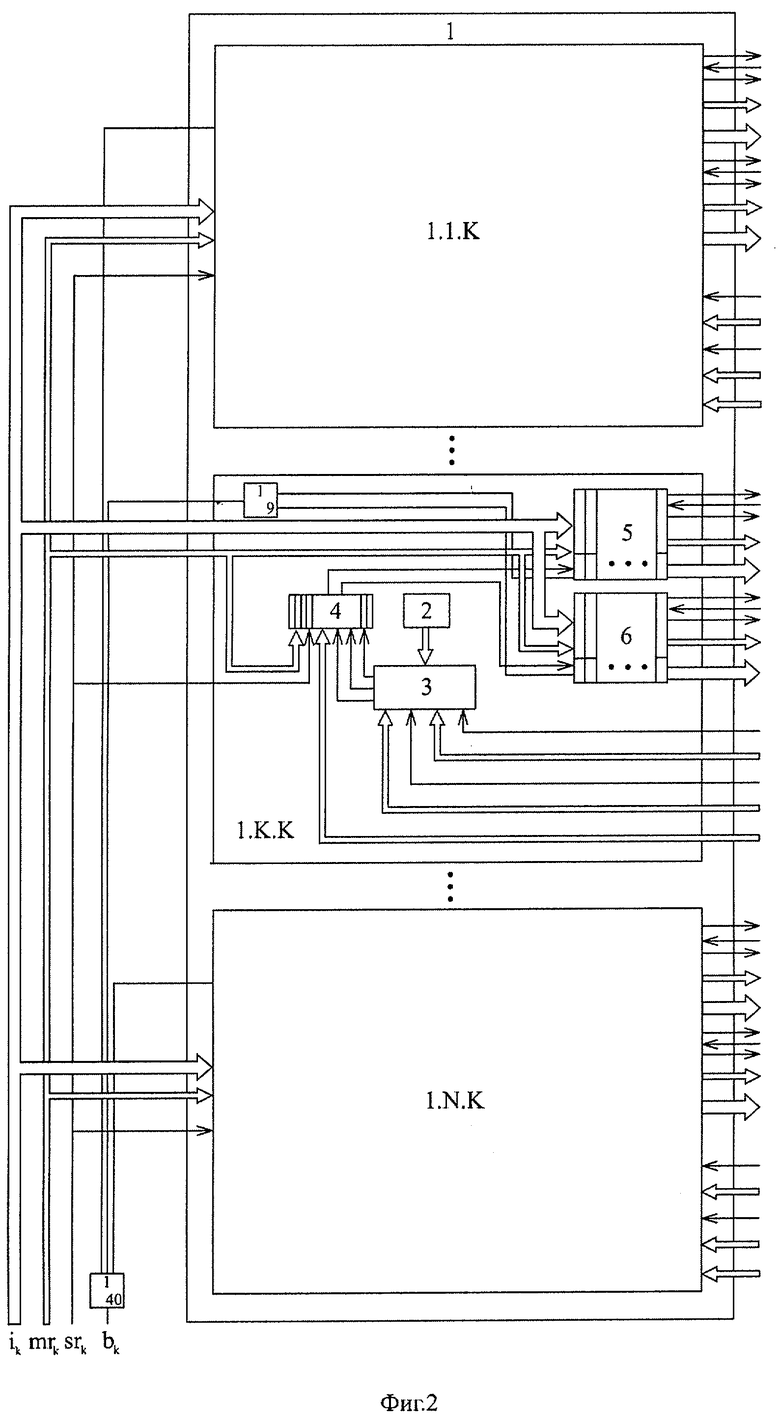

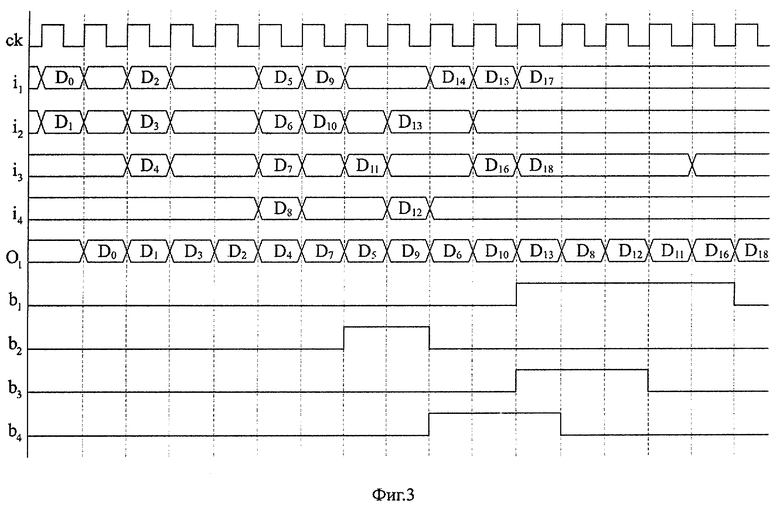

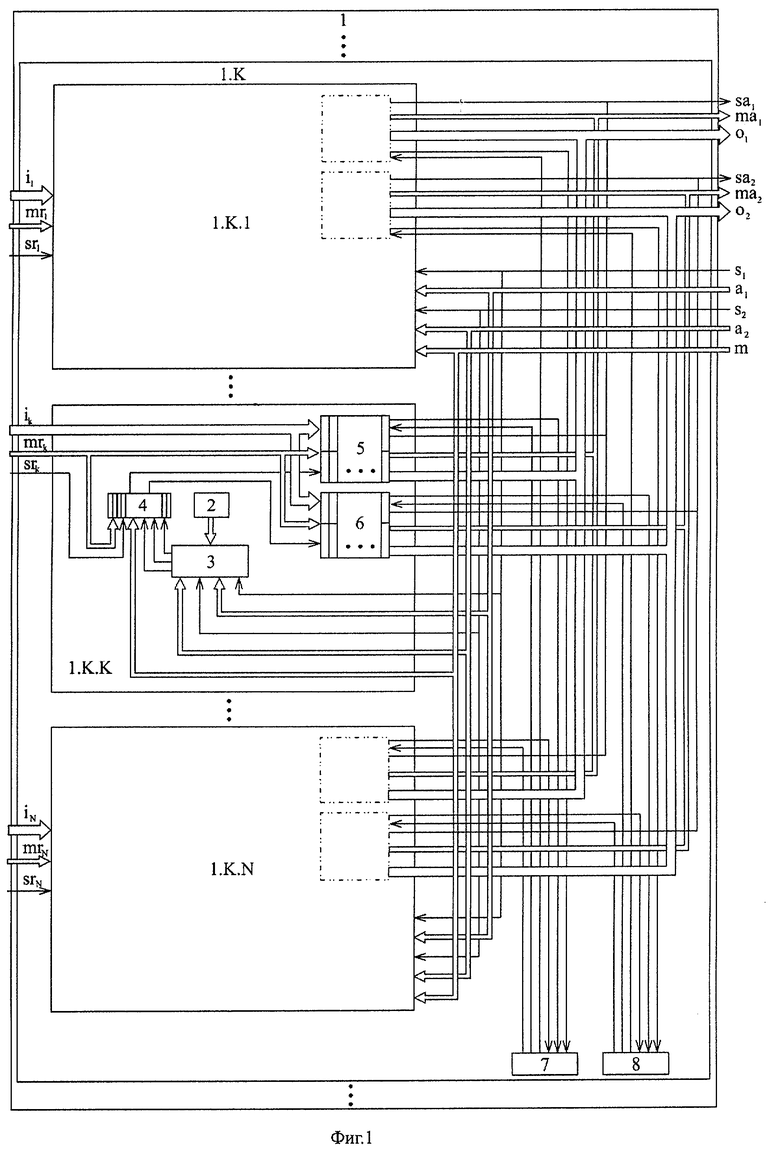

На фиг.1 представлена структурная схема устройства коммутации и узла коммутации; на фиг.2 показано формирование сигнала запрета приема информации; на фиг.3 - временная диаграмма работы узла коммутации.

Устройство коммутации 1 (фиг.1) состоит из N узлов коммутации 1.1, …, 1.К, …, 1.N, каждый из которых имеет N информационных входов i1, i2, …, iN, N идентификационных входов результатов mr1, mr2, …, mrN, N входов признаков готовности результатов sr1, sr2, …, srN, 2 адресных входа a1, а2, 2 входа признаков аргументов s1, s2, один идентификационный вход аргументов m, 2 информационных выхода o1, o2, 2 идентификационных выхода аргументов ma1, mа2, 2 выхода признаков готовности аргументов sa1, sa2. Каждый узел коммутации включает N устройств выбора 1.K.1, …, 1.К.К, …, 1.K.N, содержащих регистр логического номера 2, имеющий размерность ]log2N[ разрядов, блок формирования признаков выбора 3, память признаков выбора 4, имеющую размер двухбитовых L слов, два буферных блока FIFO-памяти 5, 6. Во всех узлах коммутации для k-го устройства выбора k=1, …, N, k-й информационный вход коммутатора ik соединен с первыми информационными входами буферных блоков FIFO-памяти 5, 6, k-й идентификационный вход результата mrk соединен со вторыми информационными входами буферных блоков FIFO-памяти 5, 6 и адресным входом чтения памяти признаков выбора 4, k-й вход признака готовности результата srk соединен с сигнальным входом чтения памяти признаков выбора 4. Во всех устройствах выбора k-го узла коммутации 1.K.1, …, 1.К.К, …, 1.K.N первый адресный вход узла коммутации a1 соединен с адресными входами первого аргумента блоков формирования признаков выбора 3, второй адресный вход узла коммутации а2 соединен с адресными входами второго аргумента блоков формирования признаков выбора 3, первый вход признаков аргументов s1 соединен с входами признака первого аргумента блоков формирования признаков 3, второй вход признаков аргументов s2 соединен с входами признака второго аргумента блоков формирования признаков 3, идентификационный вход аргумента m соединен с адресными входами записи памятей признаков выбора 4. Во всех устройствах выбора 1.K.1, …, 1.К.К, …, 1.K.N выход регистра логического номера 2 соединен с входом логического номера блока формирования признаков выбора 3, выход признака наличия аргументов блока формирования признаков выбора 3 соединен с сигнальным входом записи памяти признаков выбора 4, выходы признаков наличия первого и второго аргументов блоков формирования признаков выбора 3 соединены соответственно с первым и вторым информационными входами памяти признаков выбора 4, первый информационный выход памяти признаков выбора 4 соединен с сигнальным входом записи первого буферного блока FIFO-памяти 5, второй информационный выход памяти признаков выбора 4 соединен с сигнальным входом записи второго буферного блока FIFO-памяти 6. Кроме того, все первые информационные выходы первых буферных блоков FIFO-памяти 5 k-го узла коммутации объединены и являются первым информационным выходом данного узла коммутации o1, вторые информационные выходы первых буферных блоков FIFO-памяти 5 объединены и являются первым идентификационным выходом аргументов узла коммутации ma1, выходы признаков готовности первых буферных блоков FIFO-памяти 5 объединены и являются первым выходом признаков готовности аргументов узла коммутации sa1. Все первые информационные выходы вторых буферных блоков FIFO-памяти k-го узла коммутации 6 объединены и являются вторым информационным выходом данного узла коммутации o2, вторые информационные выходы вторых буферных блоков FIFO-памяти 6 объединены и являются вторым идентификационным выходом аргументов узла коммутации ma2, выходы признаков готовности вторых буферных блоков FIFO-памяти 6 объединены и являются вторым выходом признаков готовности аргументов узла коммутации sa2. Все буферные блоки FIFO-памяти узла коммутации 5, 6 имеют выходной сигнал запроса и входной сигнал разрешения, а узел коммутации имеет два блока арбитража 7, 8, причем выходные сигналы запроса первых буферных блоков FIFO-памяти 5 являются входными сигналами запроса первого блока арбитража 7, входные сигналы разрешения первых буферных блоков FIFO-памяти 5 являются выходными сигналами разрешения первого блока арбитража 7 данного узла коммутации. Выходные сигналы запроса вторых буферных блоков FIFO-памяти 6 являются входными сигналами запроса второго блока арбитража 8, входные сигналы разрешения вторых буферных блоков FIFO-памяти 6 являются выходными сигналами разрешения второго блока арбитража 8 данного узла коммутации.

На фиг.2 показана реализация второго варианта изобретения, при котором хотя бы один буферный блок FIFO-памяти 5, 6 имеет сигнальный выход переполнения, причем имеющиеся сигнальные выходы переполнения всех буферных блоков FIFO-памяти k-ых устройств выбора всех узлов коммутации объединены схемами ИЛИ 9, 10 и образуют сигнал запрета приема информации bk от k-го функционального блока.

На фиг.3 приведена временная диаграмма функционирования узла коммутации для приема результатов от четырех функциональных блоков. Объем блоков FIFO-памяти - 2 результата. Арбитраж осуществляется по времени запроса. Первыми получают доступ те блоки выбора, которые раньше выставили запрос. Если запросы выставлены одновременно, то доступ получает блок выбора с наименьшим номером.

| название | год | авторы | номер документа |

|---|---|---|---|

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1995 |

|

RU2110089C1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| КОММУТАТОР LINK-ПОРТОВ | 2009 |

|

RU2405196C1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств коммутации в синергических вычислительных системах. Техническим результатом является повышение производительности синергических вычислительных систем и сокращение аппаратных затрат на их реализацию. Устройство содержит N однотипных узлов коммутации, каждый из которых состоит из двух блоков арбитража и N однотипных устройств выбора, содержащих регистр логического номера, блок формирования признаков выбора, память признаков выбора, два буферных блока FIFO-памяти. 1 з.п. ф-лы, 3 ил.

1. Устройство коммутации, состоящее из N однотипных узлов коммутации, каждый из которых имеет N информационных входов, N идентификационных входов результатов, N входов признаков готовности результатов, 2 адресных входа, 2 входа признаков аргументов, один идентификационный вход аргументов, 2 информационных выхода, 2 идентификационных выхода аргументов, 2 выхода признаков готовности аргументов, каждый узел коммутации состоит из N однотипных устройств выбора, содержащих регистр логического номера, размерностью ]log2N[ разрядов, блок формирования признаков выбора, память признаков выбора, имеющую размер L двухбитовых слов, два буферных блока FIFO-памяти, причем во всех узлах коммутации для k-го устройства выбора (k=1, …, N), k-й информационный вход соединен с первыми информационными входами буферных блоков FIFO-памяти, k-й идентификационный вход результата соединен со вторыми информационными входами буферных блоков FIFO-памяти и адресным входом чтения памяти признаков выбора, k-й вход признака готовности результата соединен с сигнальным входом чтения памяти признаков выбора, а во всех устройствах выбора k-го узла коммутации первый адресный вход узла коммутации соединен с адресными входами первого аргумента блоков формирования признаков выбора, второй адресный вход узла коммутации соединен с адресными входами второго аргумента блоков формирования признаков выбора, первый вход признаков аргументов соединен с входами признака первого аргумента блоков формирования признаков, второй вход признаков аргументов соединен с входами признака второго аргумента блоков формирования признаков, идентификационный вход аргумента соединен с адресными входами записи памятей признаков выбора, а также во всех устройствах выбора выход регистра логического номера соединен с входом логического номера блока формирования признаков выбора, выход признака наличия аргументов блока формирования признаков выбора соединен с сигнальным входом записи памяти признаков выбора, выходы признаков наличия первого и второго аргументов блоков формирования признаков выбора соединены, соответственно, с первым и вторым информационными входами памяти признаков выбора, первый информационный выход памяти признаков выбора соединен с сигнальным входом записи первого буферного блока FIFO-памяти, второй информационный выход памяти признаков выбора соединен с сигнальным входом записи второго буферного блока FIFO-памяти, кроме того, все первые информационные выходы первых буферных блоков FIFO-памяти k-го узла коммутации объединены и являются первым информационным выходом данного узла коммутации, вторые информационные выходы первых буферных блоков FIFO-памяти объединены и являются первым идентификационным выходом аргументов узла коммутации, выходы признаков готовности первых буферных блоков FIFO-памяти объединены и являются первым выходом признаков готовности аргументов узла коммутации, все первые информационные выходы вторых буферных блоков FIFO-памяти k-го узла коммутации объединены и являются вторым информационным выходом данного узла коммутации, вторые информационные выходы вторых буферных блоков FIFO-памяти объединены и являются вторым идентификационным выходом аргументов узла коммутации, выходы признаков готовности вторых буферных блоков FIFO-памяти объединены и являются вторым выходом признаков готовности аргументов узла коммутации, отличающееся тем, что все буферные блоки FIFO-памяти узла коммутации имеют выходной сигнал запроса и входной сигнал разрешения, а каждый узел коммутации имеет два блока арбитража, причем выходные сигналы запроса первых буферных блоков FIFO-памяти k-го узла коммутации являются входными сигналами запроса первого блока арбитража данного узла коммутации, входные сигналы разрешения первых буферных блоков FIFO-памяти являются выходными сигналами разрешения первого блока арбитража, выходные сигналы запроса вторых буферных блоков FIFO-памяти являются входными сигналами запроса второго блока арбитража, входные сигналы разрешения вторых буферных блоков FIFO-памяти являются выходными сигналами разрешения второго блока арбитража, причем при наличии данных в буферных блоках FIFO-памяти они формируют сигналы запроса в блоки арбитража на доступ к соответствующим объединенным выходам коммутатора, а блоки арбитража осуществляют известным способом при поступлении нескольких запросов от буферных блоков FIFO-памяти выбор наиболее приоритетного буферного блока FIFO-памяти и выдачу ему сигнала разрешения на выдачу информации.

2. Устройство по п.1, отличающееся тем, что хотя бы один буферный блок FIFO-памяти имеет сигнальный выход переполнения, причем имеющиеся сигнальные выходы переполнения всех буферных блоков FIFO-памяти k-х устройств выбора всех узлов коммутации объединены схемой ИЛИ и образуют сигнал запрета приема информации от k-го функционального блока.

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| УСТРОЙСТВО ДЛЯ КОММУТАЦИИ ПАКЕТОВ ИНФОРМАЦИИ | 1994 |

|

RU2075778C1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для обеспечения жидкостного контакта биологического объекта с отводящими электродами при измерении биоэлектрических потенциалов | 1984 |

|

SU1193607A2 |

Авторы

Даты

2011-01-27—Публикация

2008-04-18—Подача