Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых допускают распараллеливание на уровне команд.

Известно устройство, микропроцессор IA-64 (см. Шахнович И. Век нынешний и век грядущий. - ж. Электроника: Наука, Технология, Бизнес, 1999, 6, стр. 8-11), реализующее параллелизм на командном уровне с использованием концепции "длинного командного слова". Устройство состоит из кэш-памяти команд 1-го уровня, кэш-памяти данных 1-го уровня, общей кэш-памяти 2-го и 3-го уровней, устройства управления, файла специализированных регистров: целочисленных, с плавающей запятой, ветвления и предикатов, группы функциональных устройств четырех типов: четыре устройства целочисленной арифметики, два устройства операций с плавающей запятой, три устройства ветвления, одно устройство доступа к памяти данных. Управление функциональными устройствами осуществляется централизовано с использованием длинных командных слов фиксированного размера, каждое из которых содержит три простые команды, определяющие операции трех различных функциональных устройств. Последовательность выполнения простых команд в слове, а также зависимость между словами определяется полем маски, находящимся в слове.

Недостатками данного устройства являются:

дополнительные расходы памяти под программный код, вызываемые фиксированным размером командного слова;

неоптимальное использование функциональных устройств и, как следствие, снижение производительности из-за несбалансированности количества функциональных устройств и количества простых команд в командном слове, специализации функциональных устройств и регистров, несоответствия пропускной способности функционального устройства памяти (максимум одно число за такт) возможностям функциональных устройств целочисленных операций и операций с плавающей запятой.

Известно также устройство, микропроцессор Е2К (см. Кузьминский М. Отечественные микропроцессоры: Elbrus 2K. - ж. Открытые системы, 1999, 5-6, стр. 8-13), использующее эту же концепцию "длинного командного слова" для реализации параллелизма. Устройство состоит из кэш-памяти команд 1-го уровня, кэш-памяти данных 1-го уровня, общей кэш-памяти 2-го уровня, буфера предварительной подкачки, устройства управления, файла универсальных регистров и группы однотипных функциональных устройств, построенных на базе арифметико-логических устройств (АЛУ) и объединенных в два кластера. Длина командного слова, управляющего работой функциональных устройств, переменная.

К недостаткам данного устройства можно отнести снижение производительности устройства при дозагрузке кэш-памяти команд 1-го уровня из-за несоответствия скорости выборки команд и скорости его заполнения, а также при широком использовании данных, находящихся в общей кэш-памяти 2-го уровня и/или оперативной памяти.

Известным является также устройство, мультискалярный микропроцессор Kin (см. Корнеев В., Киселев А. Современные микропроцессоры. М., Нолидж, 2000 г. , стр.75-76), в основе которого лежит реализация параллелизма на уровне базисных блоков. При этом, под базисным блоком понимается последовательность команд преобразования данных в регистрах и памяти, завершающаяся командой перехода. Микропроцессор состоит из набора функциональных блоков различного назначения: интерпретации команд перехода, интерпретации арифметических, логических команд и команд сдвига, выполнения команд обращения к памяти. Обмен данными между функциональными блоками выполняется в асинхронном режиме через FIFO очереди. Каждый блок выбирает из входной очереди элементы по мере их поступления, производит заданные действия и помещает результат в выходную очередь. При такой организации поток команд распространяется между блоками как поток пакетов, содержащих в себе тэги и другую необходимую информацию для управления функциональными блоками.

Процесс выборки и декодирования команд централизован, при этом выбранные и декодированные команды очередного базисного блока размещаются в кэш-памяти декодированных команд. Каждая команда при размещении получает уникальный динамический тэг. После устранения в блоках переименования регистров лишних WAR и WAW зависимостей между командами, команды поступают в блок организации внеочередного исполнения.

Из блока внеочередного исполнения команды передаются в резервирующие станции, в которых они ожидают готовности операндов для начала своего исполнения.

Команды с готовыми операндами посылаются резервирующими станциями для исполнения в функциональные блоки, результаты работы которых передаются снова в резервирующие станции, в блок внеочередного исполнения команд и, в случае команд перехода, в блок предвыборки команд.

Недостатками данного устройства являются

сложная логика поддержки внеочередного выполнения команд и аппаратной проверки наличия взаимозависимостей между командами, увеличивающая непроизводительные временные затраты и объем аппаратной поддержки динамического распараллеливания;

эффективность распараллеливания практически ограничивается уровнем линейных участков (базисных блоков), так как распараллеливание внутри базисного блока выполняется динамически путем исследования программного кода на стадии исполнения и, следовательно, не имеет достаточных временных ресурсов для анализа и оптимизации информационных связей между командами;

высокий уровень непроизводительных потерь, вызываемый жадной предвыборкой команд, при неверной оценке направления перехода.

Наиболее близкой по технической сущности и достигаемому результату к заявленному устройству, является электронно-вычислительная машина QA-2 (Компьютеры на СБИС, Кн.1, Пер. с япон. Мотоска Т., Томита С., Танака X. и др. - М. Мир, 1988, стр.65-66, 155-158 - прототип). Данное устройство состоит из устройства управления, блока коллективных специализированных регистров, сети коммутации, N однотипных функциональных устройств (в описываемой конкретной реализации прототипа N=4), построенных на базе универсальных арифметико-логических устройств. Сеть коммутации реализована по принципу "каждый с каждым", имеет N входов, 2N выходов и обеспечивает непосредственное соединение выхода любого арифметико-логического устройства с входами других арифметико-логических устройств.

Управление устройством централизованное. Длинное командное слово фиксированного размера содержит четыре поля (простых команд) для управления арифметико-логическими устройствами, поле для обращения к четырем различным банкам основной памяти и поле для управления последовательностью выполнения простых команд. Простые команды содержат информацию о коде выполняемой операции, длине операндов, адресе регистров источников левого и правого операндов арифметико-логического устройства, адресе регистров-получателей.

Недостатками известной ЭВМ являются следующие. Фиксированная длина командного слова приводит к неоптимальному использованию ресурсов памяти, а именно, поле присутствует в командном слове независимо от того, используется или не используется соответствующее ему арифметико-логическое устройство. К снижению производительности приводит отсутствие возможности непосредственного приема арифметико-логическими устройствами данных, поступающих из памяти, так как данные должны быть предварительно занесены в блок коллективных регистров, а также задание в одном командном слове операций с различной длительностью. В последнем случае короткие операции ждут выполнения самой длинной.

Задача изобретения - повышение производительности вычислительной системы.

Поставленная задача решается тем, что в предложенной асинхронной синергической вычислительной системе, содержащей N функциональных блоков, коммутатор "каждый с каждым", имеющий N информационных входов, 2N адресных входов и 2N информационных выходов, согласно изобретению каждый функциональный блок состоит из устройства управления, устройства памяти команд и операционного устройства, реализующего двуместные и одноместные операции, а также имеет два идентификационных входа аргументов, два входа признаков готовности аргументов, два информационных входа, идентификационный выход аргументов, два выхода признаков аргументов, два адресных выхода, идентификационный выход результата, выход признака результата, информационный выход, выход логического номера, N входов признаков разрешения выбора команд, выход признака разрешения выбора команд. В коммутатор дополнительно введены N идентификационных входов результатов, N входов признаков готовности результатов, N идентификационных входов аргументов, 2N входов признаков аргументов, N входов логических номеров, 2N идентификационных выходов аргументов, 2N выходов признаков готовности аргументов. Первый и второй идентификационные входы аргументов k-го функционального блока (k=1,...,N) соединены соответственно с (2k-1)-м и 2k-м идентификационными выходами аргументов коммутатора. Первый и второй входы признаков готовности аргументов соединены соответственно с (2k-1)-м и 2k-м выходами признаков готовности аргументов коммутатора, а первый и второй информационные входы соединены соответственно с (2k-1)-м и 2k-м информационными выходами коммутатора. Идентификационный выход аргумента соединен с k-м идентификационным входом аргументов коммутатора. Первый и второй выходы признаков аргументов соединены соответственно с (2k-1)-м и 2k-м входами признаков аргументов коммутатора, а первый и второй адресные выходы соединены соответственно с (2k-1)-м и 2k-м адресными входами коммутатора. Идентификационный выход результата соединен с k-м идентификационным входом результатов коммутатора, выход признака готовности результата соединен с k-м входом признаков готовности результатов коммутатора, а информационный выход функционального блока соединен с k-м информационным входом коммутатора. Выход признака разрешения выбора команд соединен с k-м входом признаков разрешения выбора команд всех функциональных блоков. Идентификационные входы аргументов, входы признаков готовности аргументов и информационные входы функционального блока являются соответствующими входами устройства управления. Идентификационный выход аргументов, выходы признаков аргументов и адресные выходы функционального блока являются соответствующими выходами устройства управления, третий адресный выход которого соединен с адресным входом устройства памяти команд. Командный вход-выход устройства управления соединен с командным входом-выходом устройства памяти команд, а идентификационный и управляющий выходы устройства управления соединены соответственно с идентификационным и управляющим входами операционного устройства. Первый и второй информационные выходы устройства управления соединены соответственно с первым и вторым информационными входами операционного устройства. Идентификационный выход результата, выход признака результата и информационный выход операционного устройства являются соответствующими выходами функционального блока. Выход логического номера, N входов признаков разрешения выбора команд и выход признака разрешения выбора команд функционального блока являются соответствующими выходами и входами устройства управления. Устройство управления состоит из блока выбора команд, блока дешифрации команд, блока формирования исполняемой команды, блока управления исполнением команд, блока разрешения выбора команд, регистра информационной связности, имеющего размерность N разрядов, памяти занятых меток, памяти готовности аргументов, буферной памяти кода операции, буферной памяти первого аргумента и буферной памяти второго аргумента, имеющих размер L слов. Адресный выход блока выбора команд является третьим адресным выходом устройства управления, командный выход блока выбора команд является командным выходом устройства управления, первый идентификационный выход блока выбора команд соединен с адресным входом чтения памяти занятых меток. Вход признака занятости метки блока выбора команд соединен с информационным выходом памяти занятых меток, второй идентификационный выход блока выбора команд соединен с идентификационным входом блока дешифрации команд и адресным входом записи памяти занятых меток, а выход признака занятости метки блока выбора команд соединен с информационным входом памяти занятых меток. Управляющий вход блока выбора команд соединен с управляющим выходом блока дешифрации команд, информационный вход блока выбора команд соединен с третьим информационным выходом блока управления исполнением команд, а выход признака разрешения выбора команд блока выбора команд является соответствующим выходом устройства управления. Командный вход блока дешифрации команд является командным входом устройства управления, а идентификационный выход аргументов, выходы признаков аргументов, адресные выходы данного блока являются соответствующими выходами устройства управления. Информационно-управляющий выход блока дешифрации команд соединен с информационно-управляющим входом блока формирования исполняемой команды, идентификационные входы аргументов, входы признаков готовности аргументов и информационные входы которого являются соответствующими входами устройства управления. Первый идентификационный выход блока формирования исполняемой команды соединен с адресным входом памяти готовности аргументов, второй, третий и четвертый идентификационные выходы блока формирования исполняемой команды соединены соответственно с адресными входами записи буферной памяти кода операции, буферной памяти первого аргумента и буферной памяти второго аргумента. Первый информационный вход-выход блока формирования исполняемой команды соединен с информационным входом-выходом памяти готовности аргументов, второй, третий и четвертый информационные выходы блока формирования исполняемой команды соединены соответственно с информационными входами записи буферной памяти кода операции, буферной памяти первого аргумента и буферной памяти второго аргумента. Выход признака готовности команды блока формирования исполняемой команды соединен с входом признака готовности команды блока управления исполнением команды. Пятый идентификационный выход блока формирования исполняемой команды соединен с идентификационным входом блока управления исполнением команды, первый, второй и третий идентификационные выходы которого соединены соответственно с адресными входами чтения буферной памяти кода операции, буферной памяти первого аргумента и буферной памяти второго аргумента, а первый, второй и третий информационные входы данного блока соединены соответственно с информационными выходами чтения буферной памяти кода операции, буферной памяти первого аргумента и буферной памяти второго аргумента. Выход логического номера блока управления исполнением команд является соответствующим выходом устройства управления. Четвертый идентификационный выход блока управления исполнением команд соединен с адресным входом записи памяти занятых меток, а выход признака занятости метки блока управления исполнением команд соединен с информационным входом памяти занятых меток. Выход установки информационной связности блока управления исполнением команд соединен с входом регистра информационной связности. Пятый идентификационный выход блока управления исполнением команд является идентификационным выходом устройства управления, управляющий выход, первый и второй информационные выходы блока управления исполнением команд являются соответствующими выходами устройства управления. Выход регистра информационной связности соединен с входом информационной связности блока разрешения выбора команд, выход признака разрешения которого соединен с входом признака разрешения блока выбора команд. N входов признаков разрешения выбора команд блока разрешения выбора команд являются соответствующими входами устройства управления. Коммутатор состоит из N узлов коммутации, каждый из которых включает N устройств выбора, содержащих регистр логического номера, имеющий разрядность ] log2N[ разрядов, блок формирования признаков выбора, память признаков выбора, имеющей размер L слов, два буферных блока FIFO-памяти. Во всех узлах коммутации для k-го устройства выбора (k=1,....N), k-й информационный вход коммутатора соединен с первыми информационными входами буферных блоков FIFO-памяти, k-й идентификационный вход результата соединен со вторыми информационными входами буферных блоков FIFO-памяти и адресным входом чтения памяти признаков выбора, k-й вход признака готовности результата соединен с сигнальным входом чтения памяти признаков выбора. Во всех устройствах выбора k-го узла коммутации (k=1,...,N) (2k-1)-й адресный вход коммутатора соединен с адресными входами первого аргумента блоков формирования признаков выбора, 2k-й адресный вход коммутатора соединен с адресными входами второго аргумента блоков формирования признаков выбора, (2k-1)-й вход признаков аргументов соединен с входами признака первого аргумента блоков формирования признаков, 2k-й вход признаков аргументов соединен с входами признака второго аргумента блоков формирования признаков, k-й вход логического номера соединен с входами регистров логического номера, k-й идентификационный вход аргумента соединен с адресными входами записи памятей признаков выбора. Для всех устройств выбора выход регистра логического номера соединен с входом логического номера блока формирования признаков выбора, выход признака наличия аргументов блока формирования признаков выбора соединен с сигнальным входом записи памяти признаков выбора, выход признаков первого и второго аргументов соединены соответственно с первым и вторым информационными входами памяти признаков выбора. Первый информационный выход памяти признаков выбора соединен с сигнальным входом записи первого буферного блока FIFO-памяти, второй информационный выход памяти признаков выбора соединен с сигнальным входом записи второго буферного блока FIFO-памяти. Все первые буферные блоки FIFO-памяти k-го узла коммутации связаны последовательно сигнальным входом чтения в кольцо, причем первые информационные выходы первых буферных блоков FIFO-памяти объединены и являются (2k-1)-м информационным выходом коммутатора. Вторые информационные выходы первых буферных блоков FIFO-памяти объединены и являются (2k-1)-м идентификационным выходом аргументов коммутатора, выходы признаков готовности первых буферных блоков FIFO-памяти объединены и являются (2k-1)-м выходом признаков готовности аргументов коммутатора. Все вторые буферные блоки FIFO-памяти k-го узла коммутации также связаны последовательно сигнальным входом чтения в кольцо, причем первые информационные выходы вторых буферных блоков FIFO-памяти объединены и являются 2k-м информационным выходом коммутатора. Вторые информационные выходы вторых буферных блоков FIFO-памяти объединены и являются 2k-м идентификационным выходом аргументов коммутатора, выходы признаков готовности вторых буферных блоков FIFO-памяти объединены и являются 2k-м выходом признаков готовности аргументов коммутатора.

Кроме того, согласно изобретению, в зависимости от условий его использования, операционное устройство может содержать устройство ввода-вывода и/или арифметико-логическое устройство и/или устройство памяти данных, причем первый информационный вход операционного устройства является информационным входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, второй информационный вход операционного устройства является адресным входом устройства ввода-вывода и устройства памяти данных и вторым информационным входом арифметико-логического устройства, идентификационный и управляющий входы операционного устройства являются, соответственно, идентификационным и управляющим входами устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных. Идентификационный выход результата, выход признака результата и информационный выход устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных являются, соответственно, идентификационным выходом результата, выходом признака результата и информационным выходом операционного устройства.

Признаки в указанной взаимосвязи в процессе проведения поиска на новизну не обнаружены, являются существенными и в своей совокупности обеспечивают увеличение производительности системы. Достигается это следующим образом. Ввод в состав асинхронной синергической вычислительной системы функциональных блоков, реализующих операции ввода-вывода и записи-чтения данных, подключение их к коммутатору таким же образом, как подключены другие блоки системы, позволяет исключить промежуточный информационный носитель в виде файла регистров и, соответственно, сократить время доступа к данным, а также увеличить за счет перераспределения блоков внутри системы поток данных, поступающих на обработку до объема, обеспечивающего максимально возможную загрузку функциональных блоков системы исходя из особенностей алгоритма решаемой задачи и аппаратных ограничений на количество функциональных блоков. Децентрализация управления в асинхронной синергической вычислительной системе и, как следствие, включение в структуру функциональных блоков устройства управления и устройства памяти команд, связанных указанным образом, а также распределенное управление коммутатором посредством адресных входов, подсоединенных к адресным выходам устройства управления, позволяет устранить задержки в вычислительном процессе, связанные с дозагрузкой программного кода. Это достигается тем, что в предлагаемой децентрализованной системе резко сокращается длина командного слова. Так, для системы, состоящей из 16 функциональных блоков, длина командного слова для подавляющего большинства операций составит 16 разрядов, что в несколько раз меньше, чем длина простой команды у прототипа. Соответственно, исчезает необходимость в кэш-памяти команд. Требуемый темп поступления командных слов может быть реализован, например, методом параллельного доступа, обеспечивающего одновременное считывание последовательности командных слов.

Ввод идентификационных меток для команд, аргументов и результатов вычисления, буферизация передачи информации между параллельно протекающими процессами в системе, ввод сигнальных признаков готовности результатов, аргументов и команд позволяют организовать асинхронный режим исполнения команд, обеспечивающий выдачу и прием результатов сразу по завершении операции и реализацию операций по готовности аргументов. Управление исполнением команд от потока данных (по готовности аргументов) дает возможность исключить время выполнения команд, как один из параметров, при решении задачи распараллеливания в процессе компиляции программ, а также сокращает простой функциональных блоков.

Дополнительно следует также отметить, что унификация внутрисистемных межблочных связей, а также возможность включения в систему разнообразных, по реализуемому набору операций, функциональных блоков, позволяет в условиях конкретного применения для специализированных систем оптимизировать объем аппаратного обеспечения в части габаритно-массовых характеристик и потребляемой мощности. Ввод в состав устройства управления регистра информационной связности обеспечивает возможность организации параллельного и независимого выполнения нескольких информационно несвязанных задач, а ввод в коммутатор регистров логического номера создает основу для эффективного решения задачи реконфигурации системы при отказе отдельных функциональных блоков и задачи резервирования.

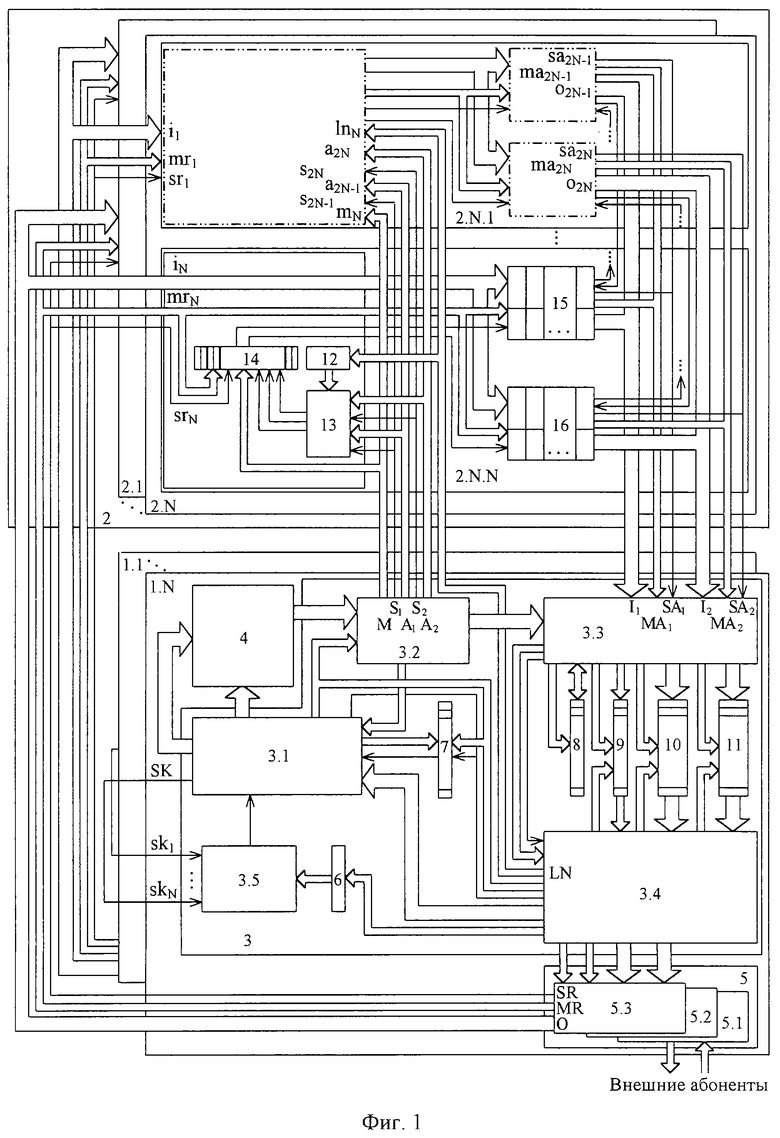

На фиг. 1 представлена структурная схема асинхронной синергической вычислительной системы; на фиг.2 - основные форматы командных слов; на фиг.3 - информационный граф формулы (1) в ярусно-параллельной форме; на фиг.4 - информационный граф формулы (2) в ярусно-параллельной форме.

Асинхронная синергическая вычислительная система (фиг. 1) содержит функциональные блоки 1.1,..,1.N, коммутатор 2 типа "каждый с каждым", имеющий N информационных входов i1,...,iN, 2N адресных входов a1, a2,...,a2N-1, a2N и 2N информационных выходов o1, o2,...,o2N-1, o2N (на фиг.1 показаны связи для N-го функционального блока). Каждый функциональный блок состоит из устройства управления 3, устройства памяти команд 4 и операционного устройства 5, реализующего двуместные и одноместные операции, а также имеет два идентификационных входа аргументов МА1 и МА2, два входа признаков готовности аргументов SA1 и SA2, два информационных входа I1 и I2, идентификационный выход аргументов М, два выхода признаков аргументов S1 и S2, два адресных выхода A1 и А2, идентификационный выход результата MR, выход признака результата SR, информационный выход О, выход логического номера LN, N входов признаков разрешения выбора команд sk1,..., skN, выход признаков разрешения выбора команд SK. Коммутатор также имеет N идентификационных входов результатов mr1, ..., mrN, N входов признаков готовности результатов sr1,..., srN, N идентификационных входов аргументов m1,...,mN, 2N входов признаков аргументов s1, s2,...,s2N-1, s2N, N входов логических номеров ln1,...,lnN, 2N идентификационных выходов аргументов ma1, ma2,..., ma2N-1, ma2N, 2N выходов признаков готовности аргументов sa1, sa2,...,sa2N-1, sa2N. Первый и второй идентификационные входы аргументов MA1 и МА2 k-го функционального блока (k= 1,...,N) соединены соответственно с (2k-1)-м и 2k-м идентификационными выходами аргументов коммутатора ma2N-1 и ma2N, первый и второй входы признаков готовности аргументов SA1 и SA2 соединены соответственно с (2k-1)-м и 2k-м выходами признаков готовности аргументов коммутатора sa2N-1 и sa2N, первый и второй информационные входы I1 и I2 соединены соответственно с (2k-1)-м и 2k-м информационными выходами o2N-1 и o2N коммутатора. Идентификационный выход аргумента М соединен с k-м идентификационным входом аргументов коммутатора mN, первый и второй выходы признаков аргументов S1 и S2 соединены соответственно с (2k-1)-м и 2k-м входами признаков аргументов коммутатора s2N-1 и s2N, первый и второй адресные выходы A1 и А2 соединены соответственно с (2k-1)-м и 2k-м адресными входами коммутатора a2N-1 и a2N. Идентификационный выход результата MR соединен с k-м идентификационным входом результатов коммутатора mrN, выход признака готовности результата SR соединен с k-м входом признаков готовности результатов коммутатора sr1, информационный выход функционального блока О соединен с k-м информационным входом коммутатора iN. Выход признака разрешения выбора команд SK соединен с k-м входом признаков разрешения выбора команд skN всех функциональных блоков. Идентификационные входы аргументов MA1 и МА2, входы признаков готовности аргументов SA1 и SA2 и информационные входы I1 и I2 функционального блока являются соответствующими входами устройства управления 3. Идентификационный выход аргументов М, выходы признаков аргументов S1 и S2, а также адресные выходы функционального блока А1 и А2 являются соответствующими выходами устройства управления 3, третий адресный выход устройства управления 3 соединен с адресным входом устройства памяти команд 4. Командный вход-выход устройства управления 3 соединен с командным входом-выходом устройства памяти команд 4, идентификационный и управляющий выходы устройства управления 3 соединены соответственно с идентификационным и управляющим входами операционного устройства 5. Первый и второй информационные выходы устройства управления 3 соединены соответственно с первым и вторым информационными входами операционного устройства 5, идентификационный выход результата MR, выход признака результата SR и информационный выход О операционного устройства 5 являются соответствующими выходами функционального блока. Выход логического номера LN, N входов признаков разрешения выбора команд sk1,..., и skN и выход признака разрешения выбора команд SK функционального блока являются соответствующими выходами и входами устройства управления 3. Устройство управления состоит из блока выбора команд 3.1, блока дешифрации команд 3.2, блока формирования исполняемой команды 3.3, блока управления исполнением команд 3.4, блока разрешения выбора команд 3.5, регистра информационной связности 6, памяти занятых меток 7, памяти готовности аргументов 8, буферной памяти кода операции 9, буферной памяти первого аргумента 10, буферной памяти второго аргумента 11. Адресный выход блока выбора команд 3.1 является третьим адресным выходом устройства управления 3, командный выход блока выбора команд 3.1 является командным выходом устройства управления 3. Первый идентификационный выход блока выбора команд 3.1 соединен с адресным входом чтения памяти занятых меток 7, вход признака занятости метки блока выбора команд 3.1 соединен с информационным выходом памяти занятых меток 7. Второй идентификационный выход блока выбора команд 3.1 соединен с идентификационным входом блока дешифрации команд 3.2 и адресным входом записи памяти занятых меток 7, выход признака занятости метки блока выбора команд 3.1 соединен с информационным входом памяти занятых меток 7. Управляющий вход блока выбора команд 3.1 соединен с управляющим выходом блока дешифрации команд 3.2, информационный вход блока выбора команд 3.1 соединен с третьим информационным выходом блока управления исполнением команд 3.4, выход признака разрешения выбора команд SK блока выбора команд 3.1. является выходом устройства управления 3. Командный вход блока дешифрации команд 3.2 является командным входом устройства управления 3, идентификационный выход аргументов блока дешифрации команд 3.2 является идентификационным выходом аргументов М устройства управления 3, выход признака первого аргумента, первый адресный выход, выход признака второго аргумента и второй адресный выход блока дешифрации команд 3.2 являются, соответственно, выходами S1, А1, S2, А2 устройства управления 3, информационно-управляющий выход блока дешифрации команд 3.2 соединен с информационно-управляющим входом блока формирования исполняемой команды 3.3. Идентификационные входы аргументов, входы признаков готовности аргументов и информационные входы блока формирования исполняемой команды 3.3 являются, соответственно, входами MA1, MA2, SA1, SA2, I1, I2 устройства управления 3. Первый идентификационный выход блока формирования исполняемой команды 3.3 соединен с адресным входом памяти готовности аргументов 8. Второй, третий и четвертый идентификационные выходы блока формирования исполняемой команды 3.3 соединены соответственно с адресными входами записи буферной памяти кода операции 9, буферной памяти первого аргумента 10 и буферной памяти второго аргумента 11. Первый информационный вход-выход блока формирования исполняемой команды 3.3 соединен с информационным входом-выходом памяти готовности аргументов 8. Второй, третий и четвертый информационные выходы данного блока соединены соответственно с информационными входами записи буферной памяти кода операции 9, буферной памяти первого аргумента 10 и буферной памяти второго аргумента 11. Выход признака готовности команды блока формирования исполняемой команды 3.3 соединен с входом признака готовности команды блока управления исполнением команды 3.4. Пятый идентификационный выход блока формирования исполняемой команды 3.3 соединен с идентификационным входом блока управления исполнением команды 3.4, первый, второй и третий идентификационные выходы соединены соответственно с адресными входами чтения буферной памяти кода операции 9, буферной памяти первого аргумента 10 и буферной памяти второго аргумента 11. Первый, второй и третий информационные входы блока управления исполнением команд 3.4 соединены соответственно с информационными выходами чтения буферной памяти кода операции 9, буферной памяти первого аргумента 10 и буферной памяти второго аргумента 11. Выход логического номера блока управления исполнением команд 3.4 является выходом LN устройства управления. Четвертый идентификационный выход блока управления исполнением команд 3.4 соединен с адресным входом записи памяти занятых меток 7, выход признака занятости метки блока управления исполнением команд 3.4 соединен с информационным входом памяти занятых меток 7. Выход установки информационной связности блока управления исполнением команд 3.4 соединен с входом регистра информационной связности 6. Пятый идентификационный выход блока управления исполнением команд 3.4 является идентификационным выходом устройства управления 3. Управляющий выход блока управления исполнением команд 3.4 является управляющим выходом устройства управления 3. Первый и второй информационные выходы блока управления исполнением команд 3.4 являются, соответственно, первым и вторым информационными выходами устройства управления 3. Выход регистра информационной связности 6 соединен с входом информационной связности блока разрешения выбора команд 3.5, выход признака разрешения которого соединен с входом признака разрешения блока выбора команд 3.1. N входов признаков разрешения выбора команд блока разрешения выбора команд 3.5 являются входами sk1,..., skN устройства управления 3. Операционное устройство 5 содержит устройство ввода-вывода 5.1 и/или арифметико-логическое устройство 5.2 /или устройство памяти данных 5.3. Первый информационный вход операционного устройства 5 является информационным входом устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3. Второй информационный вход операционного устройства 5 является адресным входом устройства ввода-вывода 5.1 и устройства памяти данных 5.3 и вторым информационным входом арифметико-логического устройства 5.2. Идентификационный и управляющий входы операционного устройства 5 являются, соответственно, идентификационным и управляющим входами устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3. Идентификационный выход результата, выход признака результата и информационный выход устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3 являются, соответственно, идентификационным выходом результата MR, выходом признака результата SR и информационным выходом О операционного устройства 5. Коммутатор 2 состоит из N узлов коммутации 2.1,...,2.N каждый из которых включает N устройств выбора 2.N.1,...,2.N.N, содержащих регистр логического номера 12, блок формирования признаков выбора 13, память признаков выбора 14, два буферных блока FIFO-памяти 15 и 16. Во всех узлах коммутации для k-го устройства выбора 2.N.N, k-й информационный вход коммутатора iN соединен с первыми информационными входами буферных блоков FIFO-памяти 15 и 16, k-й идентификационный вход результата mrN соединен со вторыми информационными входами буферных блоков FIFO-памяти 15 и 16 и адресным входом чтения памяти признаков выбора 14, k-й вход признака готовности результата srN является сигнальным входом чтения памяти признаков выбора 14. Во всех устройствах выбора k-го узла коммутации 2N, (2k-1)-й адресный вход коммутатора a2N-1 соединен с адресными входами первого аргумента блоков формирования признаков выбора 13, 2k-й адресный вход коммутатора a2N соединен с адресными входами второго аргумента блоков формирования признаков выбора 13, (2k-1)-й вход признаков аргументов s2N-1 соединен с входами признака первого аргумента блоков формирования признаков 13, 2k-й вход признаков аргументов s2N соединен с входами признака второго аргумента блоков формирования признаков 13, k-й вход логического номера lnN соединен с входами регистров логического номера 12, k-й идентификационный вход аргумента mN соединен с адресными входами записи памятей признаков выбора 14. Для всех устройств выбора 2.1.1, ...,2.N.N выход регистра логического номера 12 соединен с входом логического номера блока формирования признаков выбора 13, выход признака наличия аргументов блока формирования признаков выбора 13 соединен с сигнальным входом записи памяти признаков выбора 14, выходы признаков наличия первого и второго аргументов блока формирования признаков выбора 13 соединены соответственно с первым и вторым информационными входами памяти признаков выбора 14. Первый информационный выход памяти признаков выбора 14 соединен с сигнальным входом записи первого буферного блока FIFO-памяти 15, второй информационный выход памяти признаков выбора 14 соединен с сигнальным входом записи второго буферного блока FIFO-памяти 16. Все первые буферные блоки FIFO-памяти 15 k-го узла коммутации 2.N связаны последовательно сигнальным входом чтения в кольцо, причем первые информационные выходы первых буферных блоков FIFO-памяти 15 объединены и являются (2k-1)-м информационным выходом коммутатора o2N-1. Вторые информационные выходы первых буферных блоков FIFO-памяти 15 объединены и являются (2k-1)-м идентификационным выходом аргументов ma2N-1 коммутатора, выходы признаков готовности первых буферных блоков FIFO-памяти 15 объединены и являются (2k-1)-м выходом признаков готовности аргументов sa2N-1 коммутатора. Все вторые буферные блоки FIFO-памяти 16 k-го узла коммутации 2. N также связаны последовательно сигнальным входом чтения в кольцо, причем первые информационные выходы вторых буферных блоков FIFO-памяти 16 объединены и являются 2k-м информационным выходом коммутатора o2N. Вторые информационные выходы вторых буферных блоков FIFO-памяти 16 объединены и являются 2k-м идентификационным выходом аргументов ma2N коммутатора, выходы признаков готовности вторых буферных блоков FIFO-памяти 16 объединены и являются 2k-м выходом признаков готовности аргументов sa2N коммутатора.

Синергическая вычислительная система работает следующим образом.

Исходное состояние устройства памяти команд, устройства памяти данных вводится из блоков, реализующих операции ввода-вывода, и представляет собой последовательность, соответственно, командных слов и слов данных.

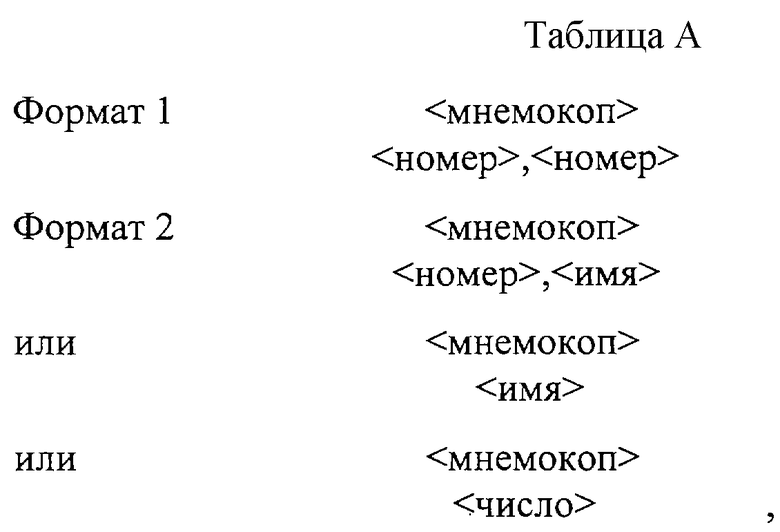

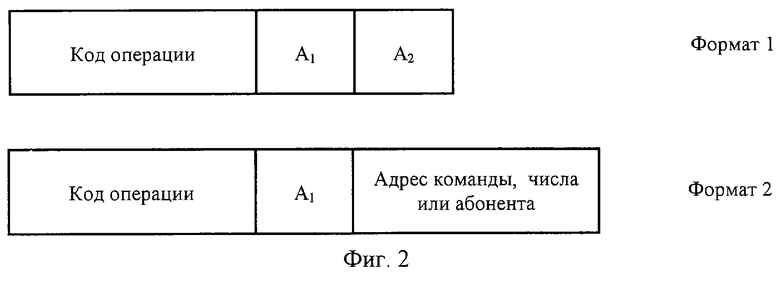

Командные слова (фиг. 2) имеют два основных формата. Первый формат содержит поле кода операции и два поля с адресами аргументов. Второй формат состоит из поля кода операции, поля с адресом аргумента и поля с адресом команды, числа или абонента. Размер поля кода операций определяется номенклатурой операций и должен быть не менее ]log2P[ двоичных разрядов, где Р - количество операций. Размер полей с адресами аргументов зависит от количества функциональных блоков и должен быть не менее ]log2N[ каждое. Размер поля с адресом команды, числа или абонента определяется максимальным объемом адресуемой памяти команд или памяти данных, либо числом внешних абонентов.

Разрядность данных определяется конкретной реализацией системы, а именно требованиями к типу, форме и точности представления данных.

Конкретными условиями применения определяется и состав операционных устройств функциональных блоков, а именно требованиями к количеству и скорости каналов ввода/вывода, требованиями к объему хранимых данных и скорости их обработки. В зависимости от этих требований асинхронная синергическая вычислительная система может иметь суммарно в составе операционных устройств до N устройств ввода/вывода и/или до N арифметико-логических устройств и/или до N устройств памяти данных. При этом объединение устройства ввода-вывода и/или арифметико-логического устройства и/или устройства памяти данных в одно операционное устройство выполняется согласно изобретению, а соединение между собой указанных устройств может быть выполнено любым известным способом.

Все функциональные блоки синергической вычислительной системы работают параллельно и независимо друг от друга, в соответствии с программами, находящимися в их устройствах памяти команд. Каждая команда реализует двуместную или одноместную операцию, которая выполняется определенное целое количество тактов, и по завершении выполнения полученный результат поступает в коммутатор.

Выполнение команды в системе включает пять последовательных стадий.

Первая заключается в выборе командного слова, дешифрации кода операции, формировании (при необходимости, в зависимости от выполняемой операции) памяти признаков выбора и формировании заготовки командного слова, включающей запись соответствующих признаков в память готовности аргументов и буферную память кода операции.

Вторая стадия предназначена для приема результатов выполнения предшествующих операций и записи их в соответствующие буферные блоки FIFO-памяти, как аргументов для выполняемых операций.

Третья стадия обеспечивает считывание аргументов из FIFO-памяти и запись их в буферную память первого или второго аргумента.

Четвертая стадия заключается в выборе подготовленных команд из буферной памяти кода операции, буферной памяти первого и второго аргументов и выдаче их на исполнение.

Пятая стадия - это собственно выполнение операции.

Длительность выполнения каждой стадии переменная. Одновременно в каждом функциональном блоке на различных стадиях выполнения может находиться до L команд. При этом, синхронизирован только запуск команд на выполнение (первая стадия). Все остальные стадии выполняются не синхронно, в зависимости от готовности результатов, аргументов, команд.

Адреса первых выполняемых команд задаются аппаратно или программно после ввода исполняемых команд, при этом исходное состояние функциональных блоков 1.1,...,1.N и коммутатора 2 асинхронной синергической системы следующее:

память занятых меток 7, память признаков выбора 14 и буферные блоки FIFO-памяти 15 и 16 обнулены;

признаки готовности результатов SR, признаки готовности аргументов SA1 и SA2 и признаки готовности команд находятся в состоянии "не готов", то есть равны нулю;

состояние регистра информационной связности 6 нулевое;

состояние признака разрешения выбора команд SK нулевое, что соответствует признаку "разрешено";

состояние регистра логического номера 12, памяти готовности аргументов 8, буферной памяти кода операции 9, буферной памяти первого аргумента 10 и буферной памяти второго аргумента 11 произвольное.

Для идентификации команд, аргументов и результатов вычислений в асинхронной синергической вычислительной системе в блоках выбора команд 3.1 формируются идентификационные метки, исходное состояние которых нулевое.

Выбор очередной команды блоком выбора команд 3.1 начинается с проверки признака разрешения, поступающего от блока разрешения выбора команд 3.5. Если признак разрешения равен единице ("запрещено"), то блок выбора команд 3.1 будет находиться в состоянии ожидания до тех пор, пока значение признака не станет равным нулю ("разрешено"), после чего блок выбора команд 3.1 проверяет занятость идентификационной метки. Для этого блок выбора команд 3.1 считывает из памяти занятых меток 7 слово, находящееся по адресу, значение которого равно значению идентификационной метки. Если содержимое данного слова нулевое (признак "метка свободна"), то блок выборки команд 3.1 выдает адрес команды в устройство памяти команд 4, записывает в память занятых меток 7 по адресу, равному значению идентификационной метки ненулевое слово (признак "метка занята") и выдает по второму идентификационному выходу значение метки в блок дешифрации команд 3.2. Если при считывании содержимое слова ненулевое (признак "метка занята"), то блок выбора команд формирует признак разрешения выбора команд SK равным единице и переходит в состояние ожидания до тех пор, пока метка не освободится, после чего признак разрешения выбора команд SK устанавливается равным нулю, и процесс выбора команд начинается заново с проверки признака разрешения.

После выдачи адреса команды в устройство памяти команд 4, записи признака занятости метки и выдачи значения метки в блок дешифрации команд 3.2, блок выбора команд 3.1 формирует новое значение адреса команды и новое значение идентификационной метки путем прибавления единицы к старым значениям, при этом сложение при вычислении нового значения метки осуществляется по модулю L.

Блок дешифрации команд 3.2 принимает командное слово из устройства памяти команд 4, распаковывает его и анализирует код операции. Если для выполнения данной команды требуется один или два аргумента из коммутатора 2, то блок дешифрации команд 3.2 формирует и передает в коммутатор 2, соответственно, значение идентификационной метки по выходу М, одно или два значения признаков аргументов S1 и S2 и одно или два значения адресов A1 и А2. Значение идентификационной метки берется то, которое поступило из блока выбора команд 3.1, значения адресов берутся из командного слова, а значения признаков аргументов формируются следующим образом: если команда использует какой-либо аргумент, то значение соответствующего признака равно единице ("аргумент используется"), в противном случае значение равно нулю ("аргумент не используется"). Если для выполнения команды требуется выбрать еще одно командное слово (формат 2) в качестве адреса данных (команд, внешнего устройства) из устройства памяти команд 4, то информация об этом поступает в блок выбора команд 3.1 по управляющему входу. В этом случае блок выбора команд 3.1 организует чтение дополнительного командного слова, при этом идентификационная метка не изменяется, а на время чтения формируется признак разрешения выбора команд SK равным единице, то есть выбор командных слов для других функциональных блоков запрещается.

Идентификационная метка, код операции и адрес данных (команды, внешнего устройства) по информационно-управляющему выходу передаются в блок формирования исполняемой команды 5.3. Используя значение идентификационной метки как адрес, блок формирования исполняемой команды 5.3 обнуляет соответствующее слово памяти готовности аргументов 8, записывает в буферную память кода операции 9 полученный код операции и, при необходимости, в буферную память второго аргумента 11 адрес данных (команд, внешнего устройства), а в память готовности аргументов 8 - признак готовности второго аргумента. Значения аргументов, поступающих от других функциональных блоков, записываются при получении признаков готовности аргументов SA1 и SA2 равными единице ("аргумент готов"). В этом случае значения идентификационных меток, поступивших по входам MA1 и МА2 используются, соответственно, в качестве адреса для записи значений аргументов I1 и I2 в буферную память первого аргумента 10 и буферную память второго аргумента 11. Так как система асинхронна, то значения аргументов могут поступать не одновременно. Параллельно с записью значений аргументов в память готовности аргументов 8 заносятся признаки готовности аргументов. Запись признаков осуществляется следующим образом. По адресу, значение которого определяется значением идентификационной метки, читается слово из памяти готовности аргументов 8. В соответствующие разряды этого слова вносится признак готовности первого или второго аргумента (ненулевые разряды), после чего выполняется проверка на наличие готовности двух аргументов. Сформированное слово записывается обратно в память готовности аргументов 8, при этом, если при проверке определено, что готовы оба аргумента, то формируется признак готовности команды, значение идентификационной метки, равное значению последнего записанного аргумента, и эти данные по выходу признака готовности команды и по пятому идентификационному выходу передаются в блок управления исполнением команды 3.4. Данный блок считывает по адресу, равному значению идентификационной метки, код операции из буферной памяти кода операции 9, значение первого аргумента из буферной памяти первого аргумента 10 и значение второго аргумента из буферной памяти второго аргумента 11. Записывает по этому же адресу в память занятых меток 7 признак занятости метки, равной нулю ("метка свободна"), и анализирует код операции. Если поступившая команда не требует использования устройства памяти данных 5.3, арифметико-логического устройства 5.2 или устройства ввода-вывода 5.1, то есть если она не формирует результат, поступающий в коммутатор 2, то эту команду выполняет сам блок управления исполнением команд 3.4. В частности, это команды формирования логического номера, передачи управления, загрузки устройства памяти команд 4, формирования регистра информационной связности 6. В противном случае блок управления исполнением команд 3.4 формирует новое значение идентификационной метки, складывая полученное с единицей по модулю L и передает новое значение идентификационной метки, значение кода операции и значения первого и второго аргументов в операционное устройство 5 по пятому идентификационному выходу, управляющему выходу и первому и второму информационным выходам, соответственно.

Операционное устройство 5 выполняет поступившую команду и формирует признак готовности результата SR, идентификационную метку результата (идентификационный выход результата MR) и сам результат (информационный выход О).

Если команды не используют общих устройств, то возможно их параллельное выполнение, при этом, если результат формируется на одном и том же такте, то он поступает в коммутатор 2 в порядке поступления команд на исполнение.

Регистр информационной связности 6 имеет N разрядов и содержит информацию о том, какие функциональные блоки должны синхронно выбирать командные слова. Информационно связанные функциональные блоки отмечены единицей в соответствующем разряде, а именно k-й функциональный блок в k-ом разряде. Содержимое регистра информационной связности 6 используется при формировании признака разрешения, поступающего из блока разрешения выбора команд 3.5 в блок выбора команд 3.1. Если хотя бы один i-й разряд регистра информационной связности 6 равен единице и равен ski, то признак разрешения равен единице ("запрещено").

Коммутатор задействован на второй и третьей стадии выполнения команды.

Для реализации второй стадии предварительно формируется память признаков выбора 14. Формирование данной памяти происходит следующим образом. Блок формирования признаков выбора 13 анализирует состояние признаков аргументов s2N-1 и s2N. Если признак первого аргумента s2N-1 равен единице, то сравниваются значения регистра логического номера 12 и значение адреса первого аргумента и a2N-1. Если они равны, то формируется признак наличия первого аргумента, равный единице ("аргумент есть"), иначе значение данного признака устанавливается равным нулю ("аргумента нет"). Аналогично формируется признак наличия второго аргумента. Если хотя бы один из этих признаков не равен нулю, то формируется обобщающий признак наличия аргументов, равный единице ("аргументы есть"), иначе его значение устанавливается равным нулю ("аргументов нет"). Далее, если признак наличия аргументов ненулевой, то в память признаков выбора 14, по адресу, равному значению идентификационной метки, поступившей по идентификационному входу аргумента mN записывается двухразрядное слово, значение разрядов которого соответствует значениям признаков наличия первого и второго аргументов.

Результат выполнения очередной операции, поступающей в коммутатор 2 по информационному входу iN сопровождается признаком готовности результата srN и идентификационной меткой mrN. В устройствах выбора 2.1.N, 2.2.N,...,2.N.N, соответствующих данному информационному входу, из памяти признаков выбора 14 по адресу, значение которого задается идентификационной меткой, по ненулевому признаку готовности результата ("результат готов") выполняется чтение соответствующего слова с одновременным обнулением его содержимого в памяти признаков выбора 14. Первый разряд (первый информационный выход) выбранного слова используется в качестве сигнала записи в первый буферный блок FIFO-памяти 15. Второй разряд - в качестве сигнала записи во второй буферный блок FIFO-памяти 16. Если сигнал записи отличен от нуля, то в соответствующий буферный блок FIFO-памяти будут записаны значения результата, поступившего по информационному входу iN и идентификационной метки, поступившей по идентификационному входу mrN.

Параллельно с процессом записи в буферные блоки FIFO-памяти 15 и 16 из этих блоков считывается ранее записанная информация и передается для формирования командных слов. Процесс чтения организован циклически, отдельно для всех первых буферных блоков FIFO-памяти 15 узла коммутации 2.N и отдельно для всех вторых буферных блоков FIFO-памяти этого же узла. Сигнал чтения передается по кольцу от первого буферного блока FIFO-памяти 15 устройства выбора 2.N.N к первому буферному блоку FIFO-памяти устройства выбора 2.N.N-1 и так далее до устройства выбора 2.N.1, сигнал чтения от которого связан с первым буферным блоком FIFO-памяти 15 устройства выбора 2.N.N.

Очередной первый буферный блок FIFO-памяти, получив сигнал чтения, если не имеет записанной ранее информации, передает этот сигнал следующему блоку. Если информация есть, то он формирует признак готовности аргумента sa2N-1, выбирает значения результата и идентификационной метки и выдает их на информационный выход o2N-1 и на идентификационный выход аргумента ma2N-1, соответственно. Выборка и выдача информации продолжается до тех пор, пока не будет выбрана вся информация, находящаяся в данном блоке, после чего формируется сигнал чтения для следующего блока и т.д.

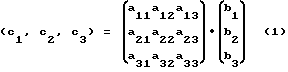

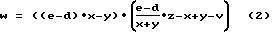

Рассмотрим работу асинхронной синергической вычислительной системы, на примере реализации двух формул

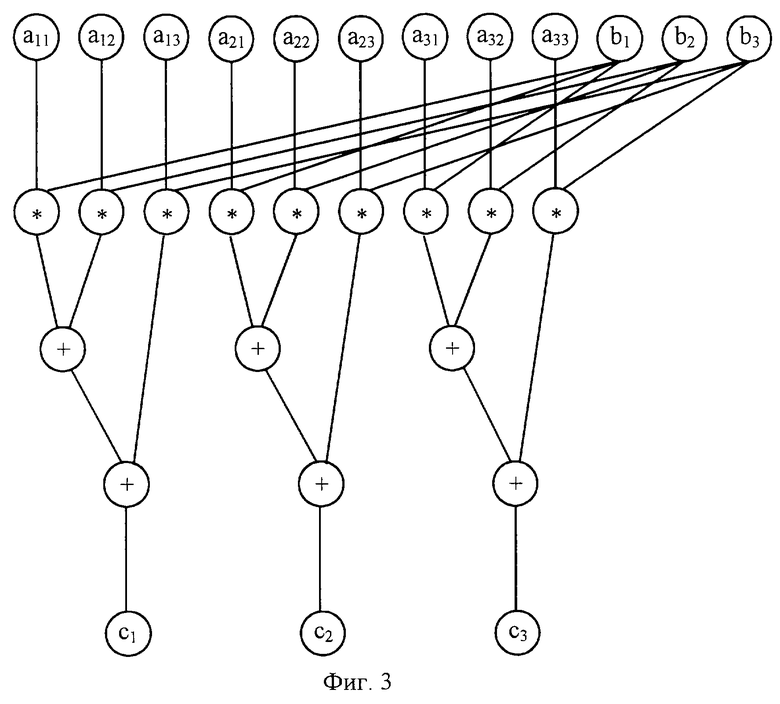

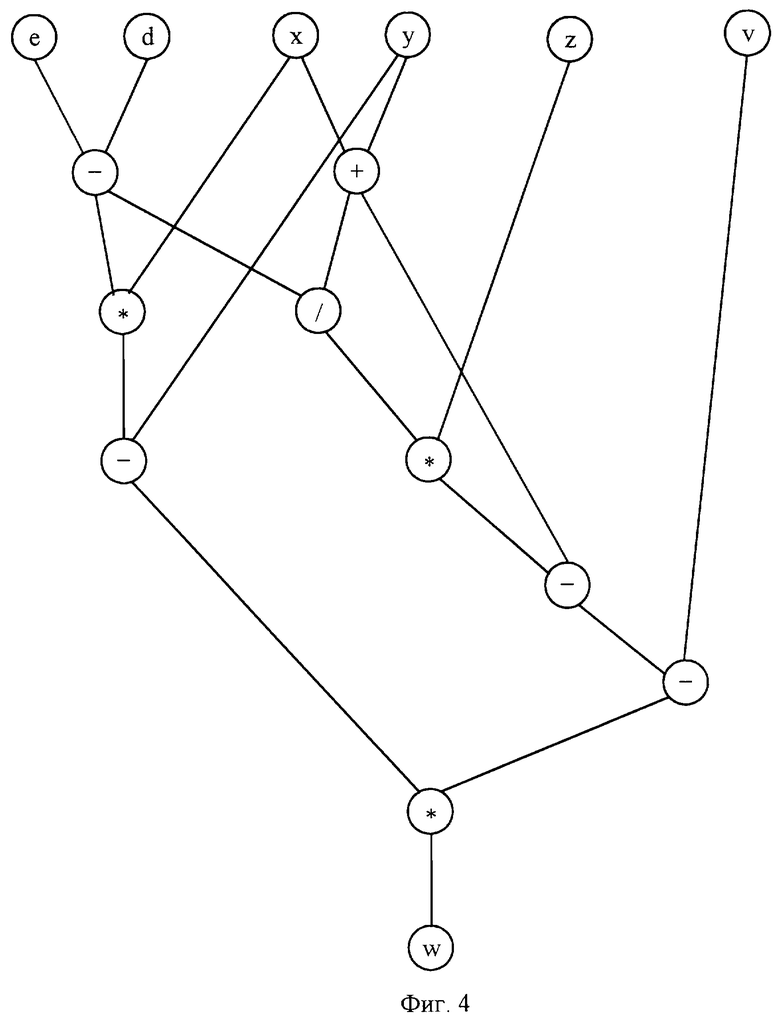

Информационные графы, описывающие последовательность выполнения операций в формулах и их параллелизм, представлены в виде ярусно-параллельных форм на фиг.3 и 4.

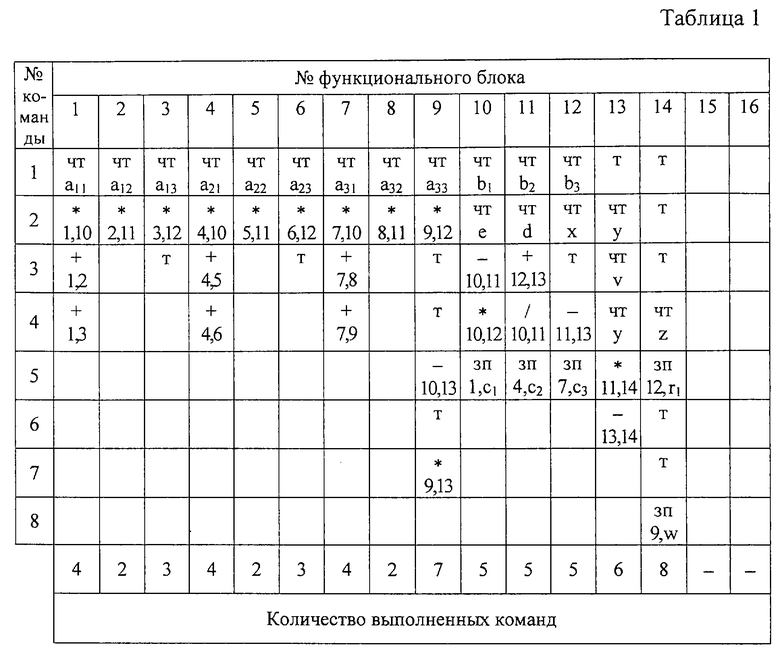

Примем, для определенности, что асинхронная синергическая вычислительная система имеет 16 функциональных блоков. Из них 15 блоков с номерами с 1 по 15 имеют в составе операционного устройства устройство памяти данных и арифметико-логическое устройство. Блок 16 является блоком ввода-вывода.

Устройства памяти данных реализуют команды чтения (чт) и записи (зп) формата 2 и имеют длительность один такт. Команда чтения является одноместной операцией, осуществляющей выборку числа из памяти данных по адресу, заданному в командном слове. Команда записи реализует двуместную операцию, первый аргумент которой это число, поступающее из коммутатора, а второй - адрес по которому осуществляется запись данного числа в память данных, заданный в командном слове.

Арифметико-логические устройства реализуют команды: сложения (+) и вычитания (-), длительностью 1 такт; умножения (•), длительностью 2 такта; деления (/), длительностью 4 такта. Все команды вычислительного блока имеют первый формат, реализуют двуместные операции, причем вычитаемое и делимое задается в первом адресе.

Для обеспечения согласованного взаимодействия блоков, когда есть необходимость задержать результат выполнения на выходе функционального блока, используется команда "трата" (т) первого формата, сохраняющая состояние блока 1 такт. Сохранить результат на один такт можно также, организовав запись в рабочую ячейку памяти данных. Записываемое число по завершении операции не только заносится в память данных, но и поступает на выход функционального блока.

Примем следующую форму записи командных слов (см. табл. А).

где <мнемокоп> - условное обозначение кода операции; <номер> - число от 1 до 16, указывающее номер функционального блока, результаты которого используются в качестве аргумента при выполнении операции; <имя> - наименование аргумента, адрес которого (после трансляции и загрузки программ) будет сформирован в поле адреса числа.

Разместим элементы матрицы (а11, а12, а13, a21, a22, а23, а31 а32, а33) поэлементно в устройствах памяти данных функциональных блоков 1-9. Векторы (b1, b2, b3) и (c1, c2, c3) поэлементно в устройствах памяти данных функциональных блоков 10-12. Переменные е, d, x разместим в памяти данных 10, 11, 12 функциональных блоков, переменные у и v в 13, а переменные z и w в 14 блоках.

При программировании для сохранения промежуточных результатов на один такт, введем дополнительный операнд, а именно рабочую ячейку r1 в 14 функциональном блоке.

Результаты программирования работы функциональных блоков при вычислении формул (1) и (2) представлены в таблице 1.

В последней строке таблицы приведено количество выполненных команд каждым функциональным блоком при вычислении данных формул.

При программировании асинхронной синергической вычислительной системы считается, что все команды выполняются один такт. Реальная длительность выполнения команд учитывается в процессе работы системы. В таблице 2 представлена фактическая временная диаграмма работы системы.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОММУТАЦИИ | 2008 |

|

RU2410747C2 |

| Архитектура параллельной вычислительной системы | 2016 |

|

RU2644535C2 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179333C1 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2005 |

|

RU2292075C1 |

| Векторно-потоковое операционное устройство | 1989 |

|

SU1734100A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ИНФОРМАЦИИ | 1991 |

|

RU2029359C1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения высокопроизводительных вычислительных систем для реализации алгоритмов, допускающих распараллеливание на уровне команд. Техническим результатом является увеличение производительности вычислительной системы. Система содержит N функциональных блоков, каждый из которых содержит блок формирования признаков выбора, память признаков выбора, регистр логического номера, два буферных блока FIFO-памяти и коммутатор типа "каждый с каждым", каждый из которых содержит устройство памяти команд, устройство управления и операционное устройство. 7 з.п. ф-лы, 4 ил., 3 табл.

| МОТОСОКА Т | |||

| и др | |||

| Компьютеры на СБИС, Кн | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| - М.: Мир, 1988, с.65,66, 155-158 | |||

| Резервированная система | 1982 |

|

SU1101827A1 |

| ТРЕХКАНАЛЬНАЯ АСИНХРОННАЯ СИСТЕМА | 1991 |

|

RU2029365C1 |

| УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ДАННЫХ С ИСПОЛЬЗОВАНИЕМ НАБОРОВ КОМАНД | 1995 |

|

RU2137183C1 |

| US 5357617 A, 18.12.1994 | |||

| SU 4200927 A, 29.04.1980. | |||

Авторы

Даты

2003-02-10—Публикация

2000-10-25—Подача