Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем (ВС) для решения задач, алгоритмы которых допускают распараллеливание на уровне команд.

Удовлетворение потребности в вычислительных ресурсах при решении сложных народнохозяйственных задач обеспечивается за счет одновременного снижения стоимости вычислительных средств и построения ВС с большим числом процессоров для достижения высокой и сверхвысокой производительности. Концепция метакомпьютинга, в том числе с привлечением вычислительных ресурсов Internet для решения ресурсоемких задач, принимает все более широкое распространение. В специализированной литературе описано множество алгоритмов, посвященных решению задачи построения высокопроизводительных ВС [1, 2, 3, 4]. Однако общим недостатком приведенных в специализированной литературе алгоритмов, посвященных решению задачи построения высокопроизводительных ВС, является отсутствие описания технической реализации: описание алгоритмов приведено только на концептуальном уровне.

Из литературы также известно высокопроизводительное устройство, микропроцессор IA-64 [5], реализующее параллелизм на командном уровне с использованием концепции "длинного командного слова".

Управление функциональными устройствами в микропроцессоре IA-64 осуществляется централизованно с использованием длинных командных слов фиксированного размера, каждое из которых содержит три простые команды, определяющие операции трех различных функциональных устройств. Последовательность выполнения простых команд в слове, а также зависимость между словами определяется полем маски, находящимся в слове.

Недостатками данного устройства являются: дополнительные расходы памяти под программный код, вызываемые фиксированным размером командного слова; неоптимальное использование функциональных устройств и, как следствие, снижение производительности из-за несбалансированности количества функциональных устройств и количества простых команд в командном слове, специализации функциональных устройств и регистров, несоответствия пропускной способности функционального устройства памяти (максимум одно число за такт) возможностям функциональных устройств целочисленных операций и операций с плавающей запятой.

Известно также устройство, микропроцессор Е2К [6], использующее эту же концепцию "длинного командного слова" для реализации параллелизма. Устройство состоит из кэш-памяти 1-го уровня, кэш-памяти данных 1-го уровня, общей кэш-памяти 2-го уровня, буфера предварительной подкачки, устройства управления, файла универсальных регистров и группы однотипных функциональных устройств, построенных на базе арифметико-логических устройств (АЛУ) и объединенных в два кластера. Длина командного слова, управляющего работой функциональных устройств, переменная.

К недостаткам данного устройства можно отнести снижение производительности устройства при дозагрузке кэш-памяти команд 1-го уровня из-за несоответствия скорости выборки команд и скорости его заполнения, а также при широком использовании данных, находящихся в общей кэш-памяти 2-го уровня и/или оперативной памяти.

Известна также электронно-вычислительная машина QA-2 [7]. Данная ВС состоит из устройства управления, блока коллективных специализированных регистров, сети коммутации, N однотипных функциональных устройств (в описываемой конкретной реализации прототипа N=4), построенных на базе универсальных арифметико-логических устройств. Сеть коммутации реализована по принципу "каждый с каждым", имеет N входов, 2 N выходов и обеспечивает непосредственное соединение выхода любого арифметико-логического устройства с входами других арифметико-логических устройств.

Управление ВС централизованное. Длинное командное слово, фиксированного размера, содержит четыре поля (простых команд) для управления арифметико-логическими устройствами, поле для обращения к четырем различным банкам основной памяти и поле для управления последовательностью выполнения простых команд. Простые команды содержат информацию о коде выполняемой операции, длине операндов, адресе регистров источников левого и правого операндов арифметико-логического устройства, адресе регистров-получателей.

Недостатками известной ВС являются следующие:

- фиксированная длина командного слова приводит к неоптимальному использованию ресурсов памяти, а именно, поле присутствует в командном слове независимо от того, используется или не используется соответствующее ему арифметико-логическое устройство;

- отсутствие возможности непосредственного приема арифметико-логическими устройствами данных, поступающих из памяти, так как данные должны быть предварительно занесены в блок коллективных регистров, приводит к снижению производительности устройства;

- низкая производительность ВС.

Наиболее близкой, по технической сущности и достигаемому результату к заявленному устройству, является синергическая вычислительная система (СВС) [8], являющаяся прототипом заявляемого устройства и содержащая N функциональных блоков, коммутатор "каждый с каждым", имеющий N информационных входов, 2 N адресных входов и 2 N информационных выходов, каждый функциональный блок состоит из устройства управления, устройства памяти команд и операционного устройства, реализующего двуместные и одноместные операции, а также имеет два информационных входа, два адресных выхода и один информационный выход, причем первый информационный вход К-го функционального блока (К=1, ..., N) соединен с (2К-1)-м информационным выходом коммутатора, второй информационный вход соединен с 2К-м информационным выходом коммутатора, первый адресный выход соединен с (2К-1)-м адресным входом коммутатора, второй адресный выход соединен с 2К-м адресным входом коммутатора, информационные входы функционального блока являются информационными входами устройства управления, адресные выходы функционального блока являются соответственно первым и вторым адресными выходами устройства управления, третий адресный выход устройства управления соединен с адресным входом устройства памяти команд, командный вход-выход устройства управления соединен с командным входом-выходом устройства памяти команд, управляющий выход устройства управления соединен с управляющим входом операционного устройства, первый и второй информационные выходы устройства управления соединены с соответственно с первым и вторым информационными входами операционного устройства, информационный выход операционного устройства является информационным выходом функционального блока, а операционное устройство содержит устройство ввода-вывода, и/или арифметико-логическое устройство, и/или устройство памяти данных, причем первый информационный вход операционного устройства является информационным входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, второй информационный вход операционного устройства является адресным входом устройства ввода-вывода и устройства памяти данных и вторым информационным входом арифметико-логического устройства, управляющий вход операционного устройства является управляющим входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, информационный выход устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных является информационным выходом операционного устройства.

Простота межпроцессорных связей, децентрализация управления и возможность оперативного реконфигурирования структуры являются основополагающими принципами построения высокопроизводительных, многопроцессорных, отказоустойчивых ВС.

Первые два принципа реализованы в прототипе. Третий принцип - оперативное реконфигурирование структуры - в рамках известной нерезервированной СВС реализовать невозможно.

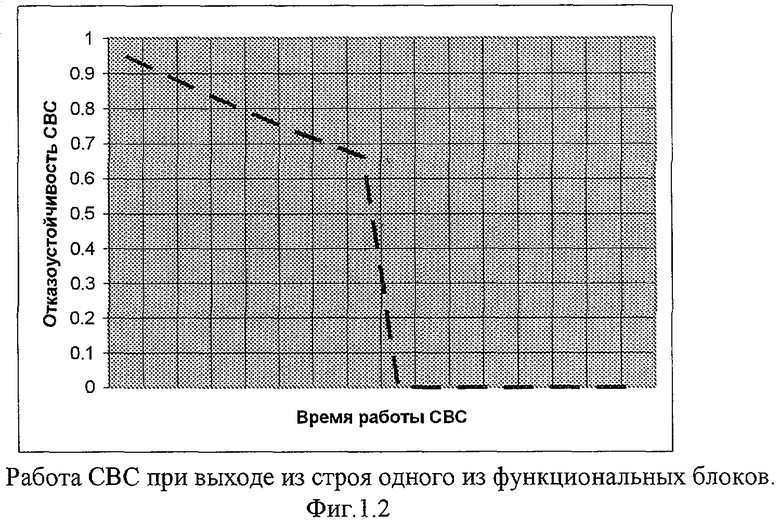

Недостатками известной СВС являются низкая надежность функционирования и отсутствие возможности перепрограммирования хода вычислительного процесса при отказе одного или нескольких функциональных блоков. Действительно, структурный расчет надежности известной СВС показывает, что при отказе одного из N функциональных блоков произойдет отказ всей системы, то есть с точки зрения надежности функционирования известная СВС представляет последовательное соединение функциональных блоков. Вероятность безотказной работы известной СВС равна произведению вероятностей безотказной работы входящих в СВС функциональных блоков.

На фигуре 1 приведены графики зависимости времени безотказной работы известной СВС от количества функциональных блоков и вероятности их безотказной работы.

Анализ фигуры 1 показывает, что с точки зрения надежности функционирования известная СВС работает неэффективно. Известная СВС является невосстанавливаемой.

Поэтому недостатком известной СВС является, по мнению авторов предлагаемого изобретения, низкая надежность работы СВС.

Предлагаемое изобретение направлено на повышение надежности работы СВС путем устранения действия отказа функционального блока и автоматического перевода системы в работоспособное состояние. При этом, безусловно, снижается производительность СВС и эффективность решения задачи.

Для получения технического результата в СВС, содержащую N функциональных блоков, коммутатор "каждый с каждым", имеющий N информационных входов, 2 N адресных входов и 2 N информационных выходов, при этом каждый функциональный блок состоит из устройства управления, устройства памяти команд и операционного устройства, реализующего двуместные и одноместные операции, а также имеет два информационных входа, два адресных выхода и один информационный выход, причем первый информационный вход К-го функционального блока (К=1, ..., N) соединен с (2К-1)-м информационным выходом коммутатора "каждый с каждым", второй информационный вход соединен с 2К-м информационным выходом коммутатора "каждый с каждым", первый адресный выход соединен с (2К-1)-м адресным входом коммутатора "каждый с каждым", второй адресный выход соединен с 2К-м адресным входом коммутатора "каждой с каждым", информационные входы функционального блока являются информационными входами устройства управления, адресные выходы функционального блока являются соответственно первым и вторым адресными выходами устройства управления, третий адресный выход устройства управления соединен с адресным входом устройства памяти команд, командный вход-выход устройства управления соединен с командным входом-выходом устройства памяти команд, управляющий выход устройства управления соединен с управляющим входом операционного устройства, первый и второй информационные выходы устройства управления соединены соответственно с первым и вторым информационными входами операционного устройства, информационный выход операционного устройства является информационным выходом функционального блока, а операционное устройство содержит устройство ввода-вывода, и/или арифметико-логическое устройство, и/или устройство памяти данных, причем первый информационный вход операционного устройства является информационным входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, второй информационный вход операционного устройства является адресным входом устройства ввода-вывода и устройства памяти данных и вторым информационным входом арифметико-логического устройства, управляющий вход операционного устройства является управляющим входом устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных, информационный выход устройства ввода-вывода, арифметико-логического устройства и устройства памяти данных является информационным выходом операционного устройства, введен анализатор ресурсов, имеющий N информационных входов и управляющий вход, N информационных выходов и управляющий выход, причем (1, ..., N) информационные входы анализатора ресурсов соединены соответственно с информационными выходами (1, ..., N) функциональных блоков, информационные выходы (1, ..., N) анализатора ресурсов соединены соответственно с информационными входами (1, ..., N) коммутатора "каждый с каждым", управляющий выход анализатора ресурсов соединен с управляющим входом коммутатора "каждый с каждым", а управляющий вход анализатора ресурсов является входом синергической вычислительной системы, при этом анализатор ресурсов содержит последовательно соединенные регистры первого блока регистров, модули памяти первого блока памяти, элементы блока элементов И, первый счетчик, мультиплексоры первого блока мультиплексоров и модули памяти второго блока памяти, последовательно соединенные регистры второго блока регистров, схему сравнения, устройство управления и мультиплексоры второго блока мультиплексоров, последовательно соединенные синхрогенератор и второй счетчик, а также мультиплексоры третьего блока мультиплексоров, причем первые входы регистров первого блока регистров соединены с информационными входами анализатора ресурсов, вторые входы регистров первого блока регистров соединены со вторым выходом синхрогенератора, вторые информационные входы модулей памяти первого блока памяти соединены с информационными входами анализатора ресурсов, третьи входы модулей памяти первого блока памяти соединены с третьим выходом синхрогенератора, четвертый выход которого соединен с первыми входами регистров второго блока регистров, вторые входы которых соединены с выходами модулей памяти первого блока памяти, выходы регистров первого блока регистров соединены со вторыми, инверсными входами элементов блока элементов И и со вторым входом устройства управления, выход схемы сравнения соединен со вторым входом второго счетчика, выходы которого соединены со вторыми входами мультиплексоров первого блока мультиплексоров, управляющие входы которых соединены с выходом устройства управления, третий вход устройства управления соединен с первым выходом синхрогенератора, четвертый вход устройства управления является входом синергической вычислительной системы, информационные входы мультиплексоров второго блока мультиплексоров соединены с выходами модулей памяти второго блока памяти, выходы мультиплексоров второго блока мультиплексоров соединены со вторыми информационными входами модулей памяти второго блока памяти, выход устройства управления соединен с третьими управляющими входами модулей памяти второго блока памяти и управляющими входами мультиплексоров третьего блока мультиплексоров, информационные входы мультиплексоров третьего блока мультиплексоров соединены с информационными входами анализатора ресурсов, выходы мультиплексоров третьего блока мультиплексоров являются информационными выходами анализатора ресурсов, выход устройства управления является управляющим выходом анализатора ресурсов.

Введенный анализатор ресурсов и связи обеспечивает достижение технического результата: повышение надежности функционирования известной СВС.

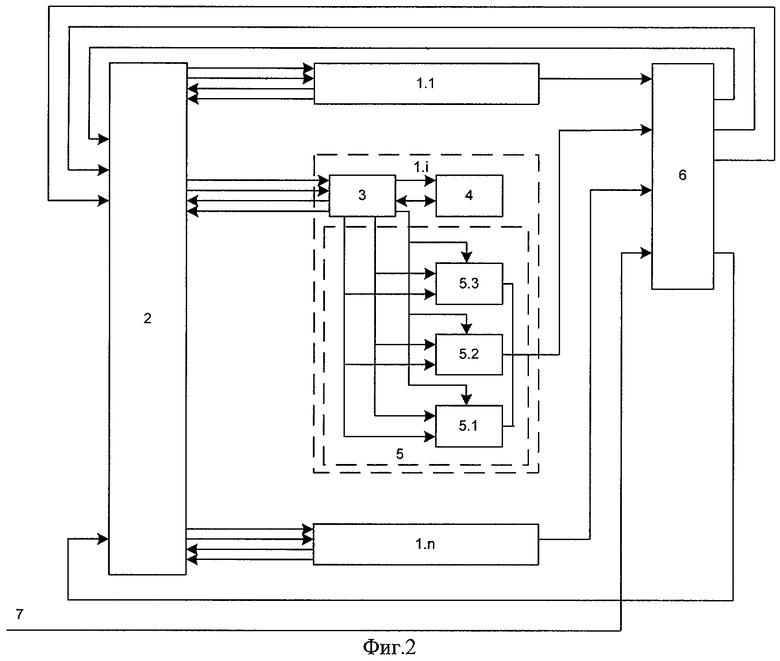

На фигуре 2 приведена структурная схема предлагаемой СВС.

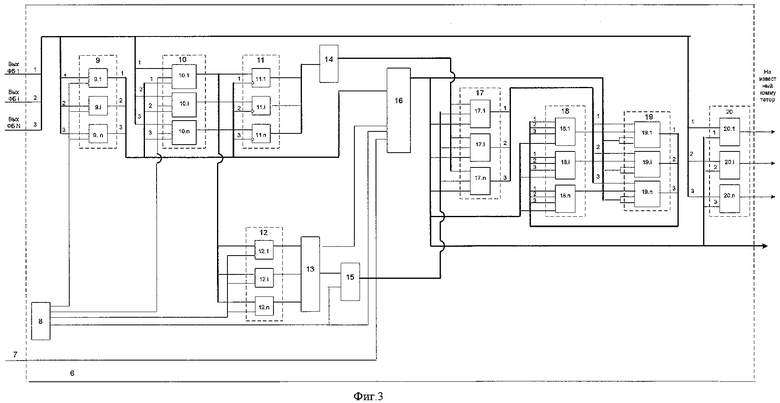

На фигуре 3 приведена структурная схема анализатора ресурсов предлагаемой СВС.

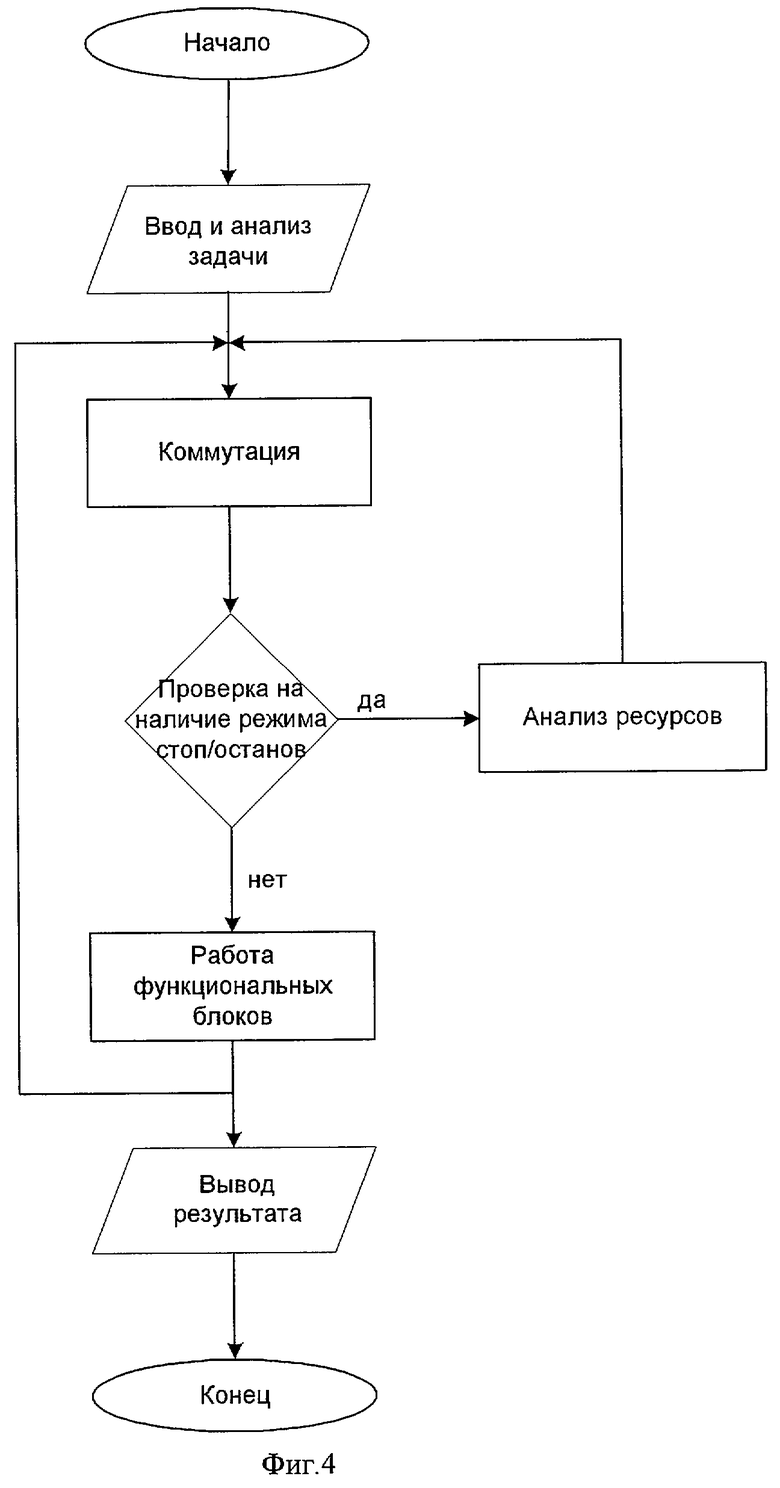

На фигуре 4 приведена блок-схема алгоритма работы предлагаемой СВС.

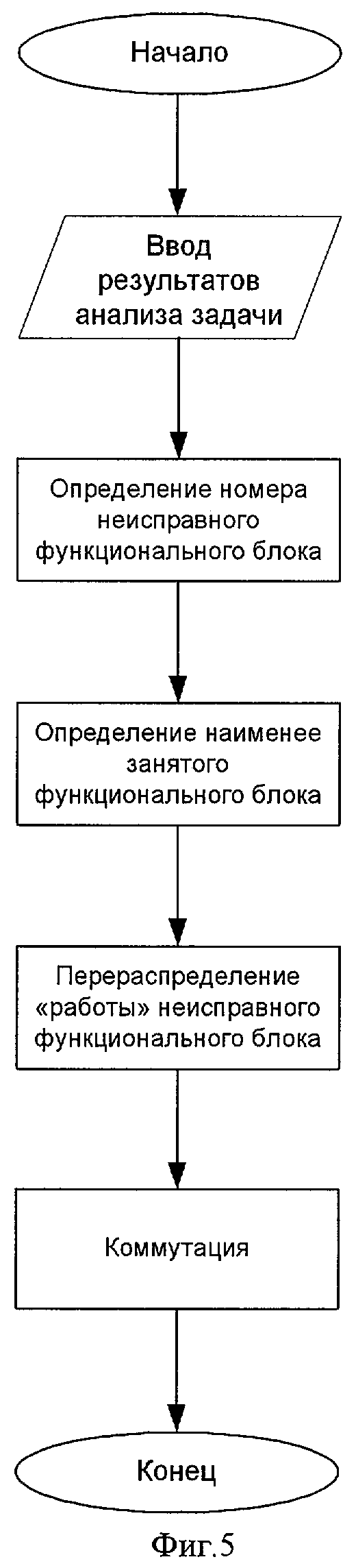

На фигуре 5 приведена блок-схема алгоритма работы анализатора ресурсов предлагаемой СВС.

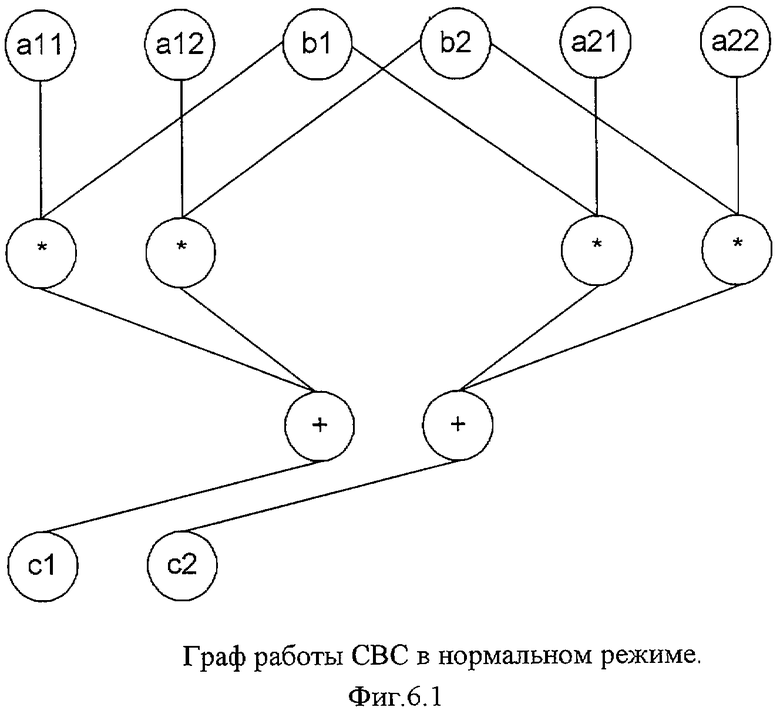

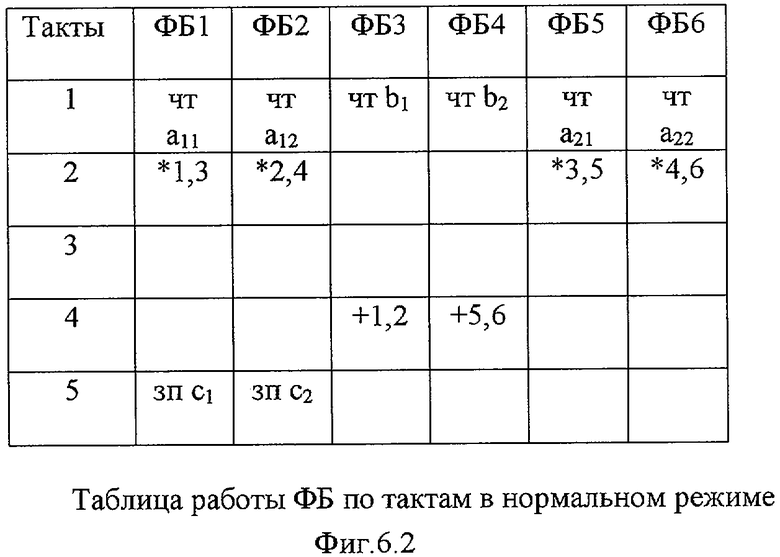

На фигуре 6 приведен граф работы предлагаемой СВС в нормальном режиме функционирования.

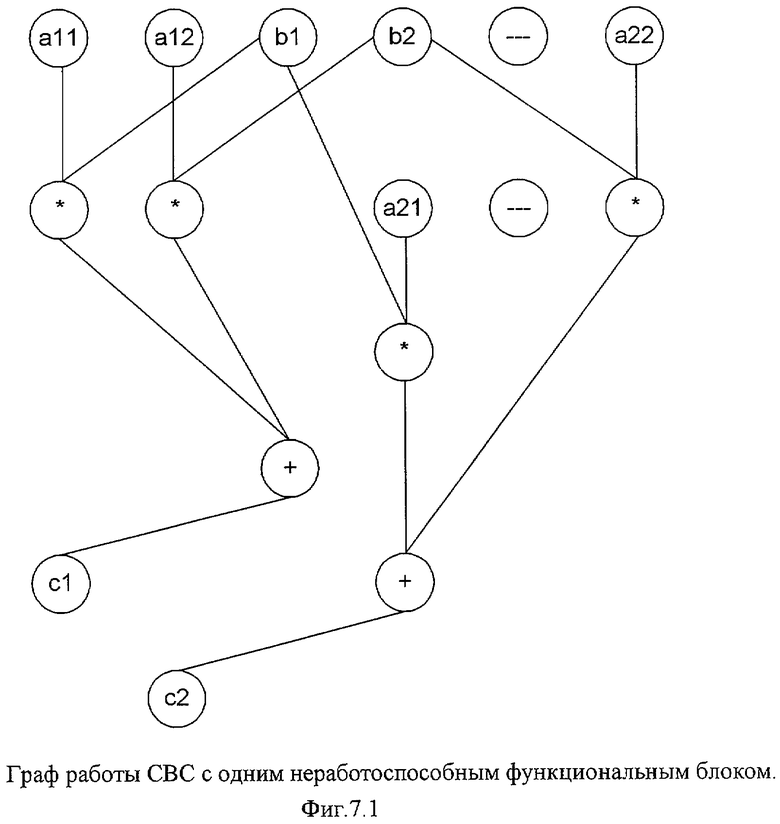

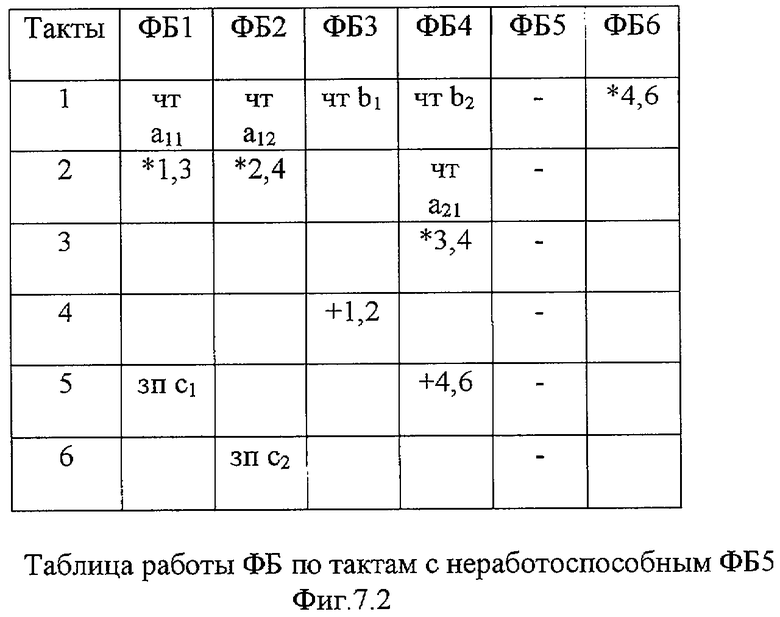

На фигуре 7 приведен граф работы предлагаемой СВС в режиме функционирования с одним неработающим функциональным блоком.

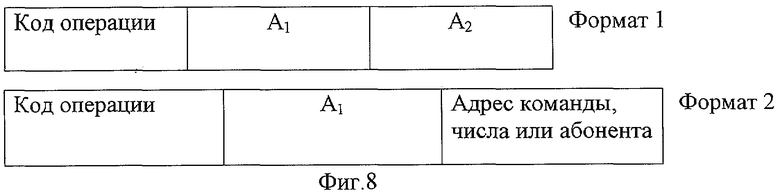

На фигуре 8 приведены форматы команд СВС.

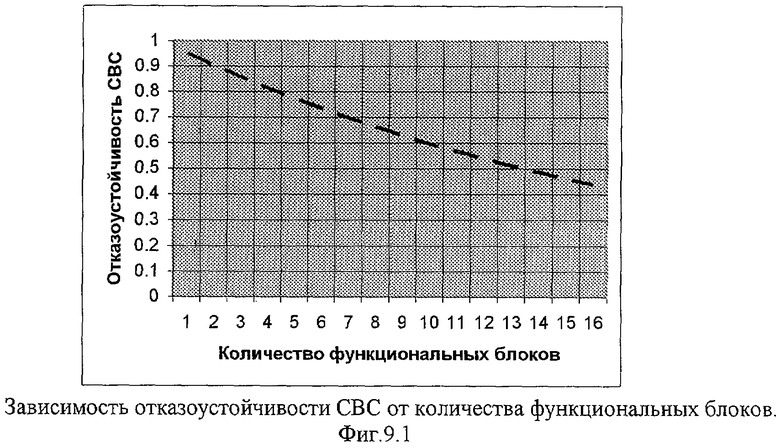

На фигуре 9 приведены графики зависимости безотказной работы предлагаемой СВС от количества неисправных функциональных блоков.

Анализ фигур 2,..., 9 показывает, что при отказе функционального блока предлагаемая СВС сохраняет работоспособность. Действительно, при отказе функционального блока предлагаемая СВС переходит в более напряженный режим работы, в котором, обладая меньшими ресурсами, СВС выполняет заданные, исходные функции. В этом заключается принципиальное отличие предлагаемой СВС от известной СВС. Введение анализатора ресурсов и соответствующих связей позволило реализовать процесс реконфигурации ресурсов СВС.

Предлагаемая СВС (Фиг.2) содержит N функциональных блоков 1.1,..., 1.i,..., 1.n, коммутатор 2 "каждый с каждым", устройство управления 3, устройство памяти команд 4, операционное устройство 5, устройство ввода-вывода 5.1, арифметико-логическое устройство 5.2, устройство памяти данных 5.3, анализатор ресурсов 6, управляющий, вход 7. Коммутатор 2 "каждый с каждым" имеет N информационных входов, 2 N адресных входов и 2 N информационных выходов. Каждый функциональный блок 1.1,..., 1.i,..., 1.n состоит из устройства управления 3, устройства памяти команд 4 и операционного устройства 5, реализующего двуместные и одноместные операции, а также имеет два информационных входа, два адресных выхода и один информационный выход. Операционное устройство 5 содержит устройство ввода-вывода 5.1, и/или арифметико-логическое устройство 5.2, и/или устройство памяти данных 5.3. Первый информационный вход К-го функционального блока 1.k (К=1, ..., N) соединен с (2К-1)-м информационным выходом коммутатора 2 "каждый с каждым". Второй информационный вход К-го функционального блока 1.k (К=1, ..., N) соединен с 2К-м информационным выходом коммутатора 2 "каждый с каждым". Первый адресный выход К-го функционального блока 1.k (К=1, ..., N) соединен с (2К-1)-м адресным входом коммутатора 2 "каждый с каждым". Второй адресный выход К-го функционального блока 1.k (К=1, ..., N) соединен с 2К-м адресным входом коммутатора 2 "каждый с каждым". Информационные входы функционального блока 1.1, ..., 1.i,..., 1.n являются информационными входами устройства управления 3. Адресные выходы функционального блока 1.1, ..., 1.i, ..., 1.n являются соответственно первым и вторым адресными выходами устройства управления 3. Третий адресный выход устройства управления 3 соединен с адресным входом устройства памяти команд 4. Командный вход-выход устройства управления 3 соединен с командным входом-выходом устройства памяти команд 4. Управляющий выход устройства управления 3 соединен с управляющим входом операционного устройства 5. Первый и второй информационные выходы устройства управления 3 соединены соответственно с первым и вторым информационными входами операционного устройства 5. Информационный выход операционного устройства 5 является информационным выходом функционального блока 1.1, ..., 1.i, ..., 1.n. Первый информационный вход операционного устройства 5 является информационным входом устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3. Второй информационный вход операционного устройства 5 является адресным входом устройства ввода-вывода 5.1 и устройства памяти данных 5.3 и вторым информационным входом арифметико-логического устройства 5.2. Управляющий вход операционного устройства 5 является управляющим входом устройства ввода-вывода 5.1, арифметико-логического устройства 5.2 и устройства памяти данных 5.3. Информационный выход устройства ввода-вывода 5.1, арифметико-логического: устройства 5.2 и устройства памяти данных 5.3 является информационным выходом операционного устройства 5. Анализатор ресурсов 6 имеет N информационных входов и управляющий вход, N информационных выходов и управляющий выход. При этом (1, ..., N) информационные входы анализатора ресурсов 6 соединены соответственно с информационными выходами (1, ..., N) функциональных блоков 1.1, ..., 1.i, ..., 1.n. Информационные выходы (1, ..., N) анализатора ресурсов 6 соединены соответственно с информационными входами (1, ..., N) коммутатора 2 "каждый с каждым". Управляющий выход анализатора ресурсов 6 соединен с управляющим входом коммутатора 2 "каждый с каждым". Управляющий вход анализатора ресурсов 6 является входом синергической вычислительной системы.

Анализатор ресурсов 6 предлагаемой СВС (Фиг.3) содержит последовательно соединенные регистры первого блока регистров 9.1, ..., 9.i..., 9.n, модули памяти первого блока памяти 10.1,..., 10.1..., 10.n, элементы блока элементов И 11.1, ..., 11.i..., 11.n, первый счетчик 14, мультиплексоры первого блока мультиплексоров 17.1, ..., 17.i..., 17.n и модули памяти второго блока памяти 19.1,..., 19.i..., 19.n. Анализатор ресурсов 6 предлагаемой СВС содержит последовательно соединенные регистры второго блока регистров 12.1, ..., 12.i..., 12.n, схему сравнения 13, устройство управления 16 и мультиплексоры второго блока, мультиплексоров 18.1, ..., 18.i..., 18.n. Анализатор ресурсов 6 предлагаемой СВС содержит последовательно соединенные синхрогенератор 8 и второй счетчик 15. Анализатор ресурсов 6 предлагаемой СВС содержит мультиплексоры третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n. Первые входы регистров первого блока регистров 9.1, ..., 9.i..., 9.n соединены с информационными входами анализатора ресурсов 6. Вторые входы регистров первого блока регистров 9.1, ..., 9.i..., 9.n соединены со вторым выходом синхрогенератора 8. Вторые, информационные входы модулей памяти первого блока памяти 10.1, ..., 10.i..., 10.n соединены с информационными входами анализатора ресурсов 6, третьи входы модулей памяти первого блока памяти 10.1, ..., 10.i..., 10.n соединены с третьим выходом синхрогенератора 8. Четвертый выход синхрогенератора 8 соединен с первыми входами регистров второго блока регистров 12.1, ..., 12.i..., 12.n, вторые входы которых соединены с выходами модулей памяти первого блока памяти 10.1, ..., 10.i..., 10,n. Выходы регистров первого блока регистров 9.1, ..., 9.i..., 9.n соединены со вторыми, инверсными входами элементов блока элементов И 11.1, ..., 11.i..., 11.n, а также со вторым входом устройства управления 16. Выход схемы сравнения 13 соединен со вторым входом второго счетчика 15. Выходы второго счетчика 15 соединены со вторыми входами мультиплексоров первого блока мультиплексоров 17.1,..., 17.i..., 17.n, управляющие входы которых соединены с выходом устройства управления 16. Третий вход устройства управления 16 соединен с первым выходом синхрогенератора 8, четвертый вход устройства управления 16 является управляющим входом 7 синергической вычислительной системы. Информационные входы мультиплексоров второго блока мультиплексоров 18.1, ..., 18.i..., 18.n соединены с выходами модулей памяти второго блока памяти 19.1, ..., 19.i..., 19.n. Выходы мультиплексоров второго блока мультиплексоров 18.1, ..., 18.i..., 18.n соединены со вторыми информационными входами модулей памяти второго блока памяти 19.1, ..., 19.i..., 19.n. Выход устройства управления 16 соединен с третьими управляющими входами модулей памяти второго блока памяти 19.1, ..., 19.i..., 19.n и управляющими входами мультиплексоров третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n. Информационные входы мультиплексоров третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n соединены с информационными входами анализатора ресурсов 6, а выходы мультиплексоров третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n являются информационными выходами анализатора ресурсов 6. Выход устройства управления 16 является управляющим выходом анализатора ресурсов 6.

Алгоритм работы СВС приведен на фигуре 4 и содержит этапы ввода и анализа задачи, коммутации, проверки на наличие режима "Стоп/Останов", анализа ресурсов в случае наличия режима "Стоп/Останов" и работы функциональных блоков в случае отсутствия режима "Стоп/Останов". В случае отсутствия режима "Стоп/Останов" перекоммутация функциональных блоков 1.1, ..., 1.i,..., 1.n не осуществляется и вычислительный процесс приходит по заранее определенной пользователем программе работы. В случае наличия режима "Стоп/Останов" анализатор ресурсов по алгоритму, приведенному на фигуре 5, осуществляет перекоммутацию функциональных блоков 1.1, ..., 1.i, ..., 1.n. СВС работает следующим образом: сначала пользователь анализирует задачу по критерию связанности (несвязанная, слабосвязанная и сильносвязанная задача) и распределяет ее решение на ряд простых параллельных подзадач для обеспечения децентрализации управления и сокращения длины командного слова.

Соответственно по результатам анализа исходной задачи пользователем осуществляется коммутация ресурсов СВС. Такая организация работы СВС обеспечивает максимально возможную загрузку функциональных блоков 1.1, ..., 1.i, ..., 1.n системы исходя из особенностей алгоритма решаемой задачи и аппаратных ограничений на количество функциональных блоков 1.1, ..., 1.i, ..., 1.n. Наличие в составе функциональных блоков 1.1, ..., 1.i, ..., 1.n устройства управления 3 и устройства памяти команд 4, а также распределенное управление коммутатором 2 "каждый с каждым" посредством адресных входов, подсоединенных к адресным выходам устройства управления 3, позволяет устранить задержки в вычислительном процессе, связанные с дозагрузкой программного кода. Исходное состояние устройства памяти команд 4, устройства памяти данных 5.3 вводится из блоков, реализующих операции ввода-вывода и представляет собой последовательность соответственно командных слов и слов данных.

Командные слова в СВС имеют два формата (см. фигуру 8). Первый формат содержит поле кода операции и два поля с адресами аргументов. Второй формат состоит из поля кода операции, поля с адресом, аргумента и поля с адресом команды, числа или абонента. Размер поля кода операций определяется номенклатурой операций и должен быть не менее ]log2P[ двоичных разрядов, где Р - количество операций. Размер полей с адресами аргумента зависит от количества функциональных блоков 1.1, ..., 1.i, ..., 1.n и должен быть не менее ]log2N[ каждое. Размер поля с адресом команды, числа или абонента определяется максимальным объемом адресуемой памяти команд или памяти данных, либо числом внешних абонентов. Разрядность данных определяется конкретной реализацией системы, а именно требованиями к типу, форме и точности представления данных.

Все функциональные блоки 1.1, ..., 1.i, ..., 1.n СВС работают параллельно и независимо друг от друга, в соответствии с программами, находящимися в их устройствах памяти команд 4. Каждая команда реализует двуместную или одноместную операцию, которая выполняется определенное целое количество тактов и, по завершении выполнения, полученный результат поступает в коммутатор 2 "каждый с каждым". Для выполнения очередной команды устройство управления 3 функционального блока 1.1, ..., 1.i, ..., 1.n выбирает из устройства памяти команд 4 очередное командное слово, распаковывает его, формирует в соответствии с кодом операции управляющие сигналы для операционного устройства 5, выбирает из соответствующих полей адреса аргументов. Адреса A1 и А2 по соответствующим адресным выходам поступают в коммутатор 2 "каждый с каждым".

Коммутатор 2 "каждый с каждым" осуществляет непосредственное соединение первого и второго информационных входов функционального блока 1.1, ..., 1.i, ..., 1.n с выходами функциональных блоков 1.1, ..., 1.i, ..., 1.n, номера которых получены коммутатором 2 "каждый с каждым" соответственно по первому и второму адресным входам и обеспечивает передачу информации с выходов функциональных блоков 1.1, ..., 1.i, ..., 1.n на информационные входы. Полученная информация используется очередной командой в качестве аргументов при реализации операционным устройством 5 двуместной или одноместной операции. Адрес команды, числа или абонента, выбираемый из команд формата 2 обрабатывается непосредственно устройством управления 3 при реализации отдельных команд передачи управления, чтения или записи числа, а также команд ввода-вывода.

Анализатор ресурсов 6 предназначен для организации восстановительных процедур в СВС при наличии режима "Стоп/Останов" в работе функциональных блоков 1.1, ..., 1.i, ..., 1.n. Алгоритм работы анализатора ресурсов 6 приведен на фигуре 5 и содержит этапы:

- ввод результатов анализа задачи. На этом этапе по результатам анализа задачи пользователем в модули памяти второго блока памяти 19.1, ..., 19.i..., 19.n заносится содержимое устройства памяти команд 4 и устройства памяти данных 5.3 с функциональных блоков 1.1, ..., 1.i, ..., 1.n. Этот этап необходим для хранения исходных данных решаемой задачи;

- определение номера неисправного функционального блока 1.1, ..., 1.i, ..., 1.n. На этом этапе при наличии режима "Стоп/Останов" в работе функциональных блоков 1.1, ..., 1.i, ..., 1.n определяется номер неисправного функционального блока 1.1, ..., 1.i, ..., 1.n путем занесения в регистры первого блока регистров 9.1, ..., 9.1..., 9.n содержимого регистра флагов функциональных блоков 1.1, ..., 1.i, ..., 1.n. Сигнал логической единицы во флаге HF свидетельствует о наличии режима "Стоп/Останов" в работе данного функционального блока. Занесение в регистры первого блока регистров 9.1, ..., 9.i..., 9.n содержимого регистра флагов функциональных блоков 1.1, ..., 1.i, ..., 1.n осуществляется с помощью синхрогенератора 8 первым тактом, в конце которого на выходе регистров первого блока регистров 9.1, ..., 9.i..., 9.n фиксируется номер неработоспособного функционального блока. Другими словами, значение 0 флага HF свидетельствует о наличии режима "Стоп/Останов" в работе данного функционального блока. При этом номер регистра первого блока регистров 9.1, ..., 9.i..., 9.n однозначно соответствует номеру функционального блока 1.1, ..., 1.i, ..., 1.n. Таким образом, номер регистра первого блока регистров 9.1, ..., 9.i..., 9.n, в котором зафиксировался 0 флага HF соответствует номеру неработоспособного функционального блока 1.1, ..., 1.i, ..., 1.n. По второму такту синхрогенератора 8 информация с первого блока регистров 1, ..., 9.i..., 9.n подается в модули памяти первого блока памяти 10.1, ..., 10.i..., 10.n на управляющие входы записи. По этим сигналам осуществляется запись информации с функциональных блоков 1.1, ..., 1.i, ..., 1.n (информация представляет собой содержимое функциональных и системных регистров, то есть показывает состояние вычислительного процесса в соответствующем работоспособном функциональном блоке 1.1, ..., 1.i, ..., 1.n в данный момент времени) в модули памяти первого блока памяти 10.1, ..., 10.i..., 10.n.

Очевидно, что в модуль памяти первого блока памяти 10.1, ..., 10.i..., 10.n, соответствующий неработоспособному функциональному блоку 1.1, ..., 1.i, ..., 1.n, информация записываться не будет, так как на входе управления записью в данный момент будет запрещающий запись информации сигнал;

- определение наименее занятого функционального блока 1.1, ..., 1.i, ..., 1.n. После определения номера неисправного функционального блока 1.1, ..., 1.i, ..., 1.n осуществляется определение наименее занятого функционального блока 1.1, ..., 1.i, ..., 1.n, чтобы перераспределить ресурсы СВС с неработоспособного функционального блока 1.1, ..., 1.i, ..., 1.n к наименее занятому функциональному блоку 1.1, ..., 1.i, ..., 1.n. Для этого третьим тактом синхрогенератора 8 информация о содержимом счетчике команд функциональных блоков 1.1, ..., 1.i, ..., 1.n из модулей памяти первого блока памяти 10.1, ..., 10.i..., 10.n поступает на регистры второго блока регистров 12.1, ..., 12.i..., 12.n, схему сравнения 13, элементы блока И 11.1, ..., 11.i..., 11.n. Причем входы элементов блока И 11.1, ..., 11.i..., 11.n, которые маскируют прохождение информации через элементы И, являются инверсными. Это необходимо для того, чтобы на выходе с блока элементов И 11.1, ..., 11.i..., 11.n получить содержимое счетчика команд, или другими словами, адрес только неработоспособного функционального блока в СВС, адреса других функциональных блоков 1.1, ..., 1.i, ..., 1.n, поступающие с регистров первого блока регистров 9.1, ..., 9.i..., 9.n не пройдут через блок элементов И 11.1, ..., 11.i..., 11.n. Четвертым тактом синхрогенератора 8 информация об адресе неисправного функционального блока 1.1, ..., 1.i, ..., 1.n заносится в первый счетчик 14, а информация об адресах исправных функциональных блоков 1.1, ..., 1.i, ..., 1.n заносится в схему сравнения 13. Схема сравнения 13 представляет собой комбинационную логическую схему, на выходе которой получается содержимое счетчика команд наименее занятого функционального блока 1.1, ..., 1.i, ..., 1.n и его адрес в СВС. Содержимое счетчика команд наименее занятого функционального блока 1.1, ..., 1.i, ..., 1.n пятым тактовым импульсом синхрогенератора 8 заносится во второй счетчик 15, а в устройство управления 16 анализатора ресурсов 6 заносится номер наименее занятого функционального блока 1.1, ..., 1.i, ..., 1.n;

- перераспределение ресурсов неработоспособного функционального блока 1.1, ..., 1.i, ..., 1.n наименее загруженному функциональному блоку 1.1, ..., 1.i, ..., 1.n. Для этого устройство управления 16 по полученной информации с первого блока регистров 9.1, ..., 9.i..., 9.n o неработоспособном функциональном блоке 1.1, ..., 1.i, ..., 1.n и по полученной информации со схемы сравнения 13 о наименее занятом функциональном блоке 1.1, ..., 1.i, ..., 1.n формирует управляющие слова для мультиплексоров первого блока мультиплексоров 17.1, ..., 17.i..., 17.n, второго блока мультиплексоров 18.1, ..., 18.i..., 18.n, третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n и модулей памяти второго блока памяти 19.1, ..., 19.i..., 19.n первого блока мультиплексоров 17.1, ..., 17.i..., 17.n осуществляют коммутацию содержимого первого 14 и второго 15 счетчиков на шину адреса модулей памяти второго блока памяти 19.1, ..., 19.i..., 19.n, соответствующего неработоспособному функциональному блоку 1.1, ..., 1.i, ..., 1.n и наименее занятому функциональному блоку 1.1, ..., 1.i, ..., 1.n. Этим действием осуществляется подготовка к приему информации наименее занятым функциональным блоком 1.1, ..., 1.i, ..., 1.n от неработоспособного функционального блока 1.1, ..., 1.i, ..., 1.n. Затем по сформированному управляющему слову мультиплексоры второго блока мультиплексоров 18.1, ..., 18.i..., 18.n, и мультиплексоры третьего блока мультиплексоров 20.1, ..., 20.i..., 20.n соединение выхода модуля памяти второго блока памяти 19.1, ..., 19.i..., 19.n, соответствующего неработоспособному функциональному блоку 1.1, ..., 1.i, ..., 1.n ко входу модуля памяти второго блока памяти 19.1, ..., 19.i..., 19.n, соответствующего наименее занятому функциональному блоку 1.1, ..., 1.i, ..., 1.n. Затем осуществляется запись содержимого модуля памяти второго блока памяти 19.1, ..., 19.i..., 19.n, соответствующего неработоспособному функциональному блоку 1.1, ..., 1.i, ..., 1.n в модуль памяти второго блока памяти 19.1, ..., 19.i..., 19.n, соответствующего наименее занятому функциональному блоку 1.1, ..., 1.i, ..., 1.n. Таким образом анализатором ресурсов произведено перераспределение программы работы функциональных блоков в модулях памяти второго блока памяти 19.1, ..., 19.i..., 19.n;

- перекоммутация (реконфигурация) ресурсов СВС. На этом этапе по сформированному устройством управления 16 анализатора ресурсов 6 управляющему слову осуществляет перекоммутацию функциональных блоков 1.1, ..., 1.i, ..., 1.n СВС.

Работу анализатора ресурсов можно рассмотреть на примере реализации формулы:

Допустим, что СВС состоит из 6 функциональных блоков и все блоки работоспособны, тогда реализация формулы (1) происходит, как показано на фигурах 6.1 и 6.2. Анализатор ресурсов 6 в этом случае осуществляет контроль работы СВС путем проверки на наличие режима Стоп/Останов. При выходе из строя одного из функциональных блоков анализатор ресурсов 6 осуществляет восстановительные процедуры в соответствии с вышеописанным алгоритмом. Например, пятый функциональный блок СВС вышел из строя, тогда реализация формулы (1) будет выглядеть по-другому, так, как представлена на фигуре 7.1 и фигуре 7.2. Как следует из рассмотрения фигуры 7.2 "работу" пятого функционального блока берет на себя четвертый функциональный блок. Работа СВС продолжается, несмотря на выход из строя одного из функциональных блоков.

Таким образом, предлагаемая СВС при сохранении достоинств прототипа является восстанавливаемой и сохраняющей работоспособность при отказе функциональных блоков. Фигура 9 наглядно демонстрирует это.

Источники информации

1. Архитектура компьютерных систем и сетей: Учеб. Пособие / Т.П.Барановская, В.И.Лойко, М.И.Семенов, А.И.Трубилин; Под ред. В.И.Лойко. - М.: Финансы и статистика, 2003. - 256 с.;

2. Головкин Б.А. Вычислительные системы с большим числом процессоров. - М.: Радио и связь, 1995. - 320 с.;

3. Евреинов Э.В. Однородные вычислительные системы, структуры и среды. - М.: Радио и связь, 1981. - 208 с.;

4. Вопросы кибернетики. Отказоустойчивые многомашинные и многопроцессорные вычислительные системы. Под ред. И.В.Прангишвили, Э.М.Мамедли. - М.: Изд-во АН СССР, 1989. - 196 с.;

5. Шахнович И. Век нынешний и век грядущий. // Электроника: Наука, технология, бизнес, N 6,: 1999, стр.8-11;

6. Кузьминский М. Отечественные микропроцессоры: Elbrus 2K. //Открытые системы, N 5-6, 1999, стр.8-13;

7. Компьютеры на СБИС. Кн.1, Пер. с япон. // Мотоска Т., Томита С., Танака X. и др. - М.: Мир, 1988, стр.65-66, 155-158;

8. Патент РФ 2179333, G 06 F 15/173. Синергическая вычислительная система / Н.В.Стрельцов // 13.06.2000.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179333C1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| АСИНХРОННАЯ СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2198422C2 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| СИСТЕМА ОБРАБОТКИ ДАННЫХ | 1987 |

|

SU1487702A1 |

| Арифметическое устройство | 1986 |

|

SU1363186A1 |

| КОНВЕЙЕРНЫЙ ПРОЦЕССОР | 1992 |

|

RU2032215C1 |

| Операционное устройство | 1982 |

|

SU1113805A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных вычислительных систем для решения задач, алгоритмы которых допускают распараллеливание на уровне команд. Техническим результатом является повышение отказоустойчивости вычислительной системы. Устройство содержит N функциональных блоков, коммутатор «каждый с каждым», анализатор ресурсов, состоящий из блоков регистров, блоков памяти, блоков элементов И, счетчиков, блоков мультиплексоров, синхрогенератора, устройства управления, схемы сравнения. 1 з.п. ф-лы, 13 ил.

| СИНЕРГИЧЕСКАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2000 |

|

RU2179333C1 |

| МНОГОПРОЦЕССОРНАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 1993 |

|

RU2054710C1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2001 |

|

RU2202123C2 |

| Резервированная вычислительная система | 1990 |

|

SU1755400A1 |

| Многопроцессорная система | 1989 |

|

SU1735866A1 |

| JP 5324596, 07.12.1993 | |||

| DE 4129614 А1, 19.03.1992. | |||

Авторы

Даты

2007-01-20—Публикация

2005-06-21—Подача