(54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ БУФЕРНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для обработки информации | 1981 |

|

SU993262A1 |

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обработки адресной информации | 1977 |

|

SU744585A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

1

Изобретение относится к области вь чисяителшой техники в может быть использовано при разработке вычаслительнь1х сИ| стем, используемых буферную память.

Извесшо устройство, содержащее груп-ч пы регистров базы, схем сравнения в индексных регистров 111.

Недостатком известного устройства является недостаточная еффектавность памя- ти.,д

Наиболее близким по сущности технй- ческим решением к предложенному являет ся устройство для адресации буферной памяти, содерлмацее группу регистров базы, регистр адреса, первую группу схем сравнения, группу элементов И, группу индеконых регистров, вторую группу схем срйвнения, входной регистр базы, вход котгорого соединен с первым входом устройства, выход входного регистра базы соединш с первыми входами схем сравнения первой группы, вторые входы которых соединеты с выходами соответствующих регистров базы груаспы, выходы схем сравнения пер

вой грусазы соединены с первыми входами элементов И груйпьг 2 .

В этом устройстве соответствие идя ;связь между блоками буферной и оператив .ной памяти устанавливается с помощью адресной памяти, хранящей адреса столикпов по оперативной памяти. Адресная память является прямоадресуемой и таким офазом обусловливает жесткую связь между расположением блока данных в Я1в- ративной и буферной памятях. Эффектвв ность использования буферной памяти су ществеаао зависит от взаимного размещения в оперативней памяти частой прогр лгл, которые одновременно участвуют в вычислительном процессе. Это является осяоЕЮЫм недостатком организации буферной памяти известного устройства и уменьшает во многих случаях его общую провэводитеяьность.

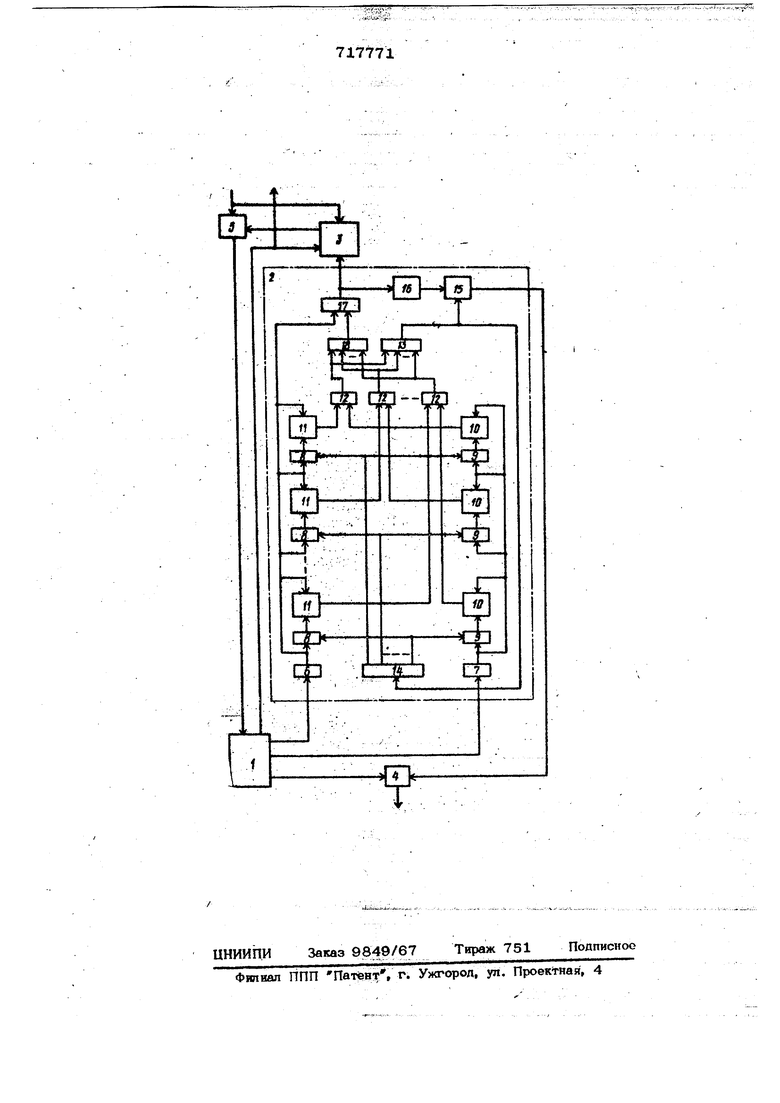

liSenbK) изобретения является повышение коэффиди та использования оборудования. Поставленная цель достигается тем, что в устройство для адресации буферной памяти введены два коммутатора, шифра тор, входной индексный регистр, блок эле ментов ИЛИ, память битов значимости, причем выход входного регистра базы сое- дцне с информационными входами регистров базы группы, выходы схем сравнения второй группы соединены со вторыми входами соответствунзщих элементов И групrtfat, выходы которых соединены с соответ ствувдцими входами шифратора и блока эле ментов ИЛИ, которого соединей с , входами первого и второго коммутаторов, выходы первого коммутатора соединены с управляющими входами соответствующих регистров базы группь и индексных регисугров группы, второй вход устройства че- рез входной индексный регистр соединен с первым входом регистра адреса, йнформационныма входами индексных регистров грутгы и первыми входами схем сравйени второй группы, вторые входы которых сое дйнены с вьосбдами соответствующих индексных регистров группы, выход шифра«ч тора соединён со вТорьтм входом регист- ра ащ)еса, выход которого соединен с первым выходом устройства и через посл довательно соединенные память битов зна чимости к второй коммутатор - со вторым выходом устройства. Блок-схема процессора с устройством адресации буферной памяти приведена на чертеже. Процессор содержит блок 1 обработки данных, устройство 2 для адресации буферной памяти, буферную память 3, блок 4обращения к оперативной памяти, блок 5коммутации. Устройство 2 для адресации буферной пмляти в свою очередь содержит входной индексный регистр 6, входной регистр 7 базы, группу индексных регистров 8, группу регистров 9 базы, группы csteM lO и 11 сравнения, груп пу элементов И 12, блок 13 элементов ИЛИ, коммутатор 14 и 15, память 16 битов а1ачймости, регистр 17 адреса и шифратор 18, Работа усггройства иллюстрируется на йрамёре применения его в многойродессо ной сйбтемё. Такая cjiCTeMa использ;ует оперативную память на ферритовых сердечниках объемом 16 млн. слов, каждое по 8 байтов. Размер буферной памяти, входящей в состав устройства и выполненной на быст рых интегральных схемах, составляет 51 слов. Длин аслова буферной памяти такая Же, как и слова оперативной памяти. Бу ферная память разделена на 32 равны сектора. Программы пользователя и ««арационной системы представпйют собтай совокупность процедур, каждая из которых обладает свойством повторной входимости. Процедуры располагаются в оперативной памяти вплотную друг к другу. Доступ к информационным массивам процедур осу- ществляется через таблицу управляющих слов - дескрипторов, каждый из которых Описывает некоторую логическую область произвольной длины. Дескриптор разДепек на три зоны: база - адрес начала массива некоторой процедуры; количество - величина, определяющая размер массива в словах; защита - величина, в которой позиционно задается возможность различных Видов доступа к процедуре. Доступ к слову, расположенному внутри массива процедуры, осуществляется путем Ойерации индексирования соответствующего дескриптора. Отцность этой операции состоит в следующем. Команды считывания, записи и ветвления вклюлают в себя информацию о расположении дескриптора и смещение - индкес. Из дескриптора выделяется база (24-разрядный адрес с точностью до сяова) и суммиру ётся. с 13-разрядным индексом. Полученныи таким образом, исполнигел ь-. ный адрес идентифицирует расположение .требуемого слова в оперативной памяти. Параллельно с формированием исполнитель НО1Ч5 адреса происходит проверка на выход адресации за предел массива, для индекс сравнивается с количеством, заданным в дескрипторе, а также проверяются соответствующие разряды зоны защиты дескриптора с целью определения корректности обращения к массиву. Исполнительный адрес вырабатьюается в блоке 1 и поступает на «адресный вход блока 4. Массивы или сегменты процедур в оперативной памяти делятся на секторы по 16 слов, начиная с базового адреса cei мента. Последний сектор сеплента может: быть неполным, т.е. содержать менее 16 слов. Любой сектор оперативной пемятп может быть раетлещен в любом секторе буферной памяти. Каждый сектор в оперативной памяти может быть идентифицирован базой процедуры, в которую он входит и индексом сектора, определяемым 0-8 разрядами индекса, который участвует в операции индексировш1ия дескриптора. Соответствие между информацией, раз- мощенной в секторах буферной памяти 3, и секторами оперативной памяти устаншилввается с помощью устройства 2. Региср ры 8 группы и регистры 9 группы делятся на Пары база-индекс, причем каждая пара соответствует опредаленнсму сектоРУ буферной памяти 3. После размещения информации в сектор буферной памяти 3 база процедуры, соде эжащей этот сектор, а также индкес сектора (номер сектора в щюцедуре) заносятся в соответствующую пару баэа-41ндекс устройства 2. База и индекс, вьщеленные соответственно ий дескриптора и команды, испол ауются блоком 1 в качестве адресов поиска требуемой информации в буферной паМвяс 3. Для этого индексная и базовая информшия из блока 1 поступают соот ветствшнр на входной индексный регистр и входаой регистр 7. Поиск требуемой информации происходит путем однозременно« го сравнеивя содержимого входного регист ра 7 и индексжюго регистра 8 с соответст вующими парами базаг ндекс из регистров 8 и регистров 9 на схемах Ю и 11. Каждой паре база-индекс соответствует пера схема 10 - схема 11 и элемент И 12 группы, на входь которого поступают Сигналы сравнения с HHMeKcoNf и базой. Сравнение содержимого входных регистров 6 и 7 с одной из множества пар база-индекс вызывает срабатьюание со- ответствукицего элемента И 12. Выходы элементов И 12 соединены с шифратором 18, который в зависимости от позиции пары база-индекс, с которой произошло сравнение, формирует соответствующий номер сектора. Выход шифратЪра 18 и 9-12 разряды входного индексного регист ра 6 в совокупности образуют адрес обращения к буферной камяти 3 и поступают на регистр 17. Обмен информацией между оперативной памятью происходит блоками по четьфе слова, в связи с чем каждый сектор буферной памяти делится также на четьфё блока. Для установления факта наличия знанимой информации в блоке сектора служит память 16 битов значимости. Количество ячеек памяти 16 равно количеству секторов в буферной памяти. Каждая ячейка хранит четыре бита, по одному на блок. В процессе решения задачи блок 1 производит считывание информации из оперативной и буферной памятей, а .также запись информации в них. Выполнение операций считывания и за-писи состоит ИЗ нескольких этапов. 1.Блок 1 выделяет базу из дескриптора и индекс из команды, после чего базовая и индексная информация из блока 1 подаются на входные регистры 7 а 6 устройства 2. 2.Блок 1 формирует исполнительный адрес путем суммирования базыи индекса, после чего адрес из блока 1 передается в блок 4. Одновременно с этим 1фо исходит сравнение регистров 6 и 7 с регистрами 8 и 9. Результаты сравнения поступают через элементы И 12 и блок 13 элементов ИЛИ в коммутаторы 14, 15 и далее через коммутатор 15 к бло- ку 4. 3. Проверка состояния выхода коммутатора 15. Если произошло сравнение с одной из пар база-иидекс устройства 2, то переходят к восьмому этапу, если сравнения не произошло - к следующему . 4. Выделение сектора буферной памяти под новую информацию. Размещением информации в буферной памяти управляет коммутатор 14 по принципу первый вошел - первый вышел. Возбуждается один из выходов коммутатора 14, который соответствует выделяемому сектору. Вслед ствие этого содержимое входных регистрров 6 и 7 записьшается в регистры 8 н 9 выбранной пары база-индекс. Появляется сигнал на выходе соответствующего элемента И 12, который поступает на ши(}5)атор 18. Информация шифратора 18 и9-12 разряды входного индексного регистра 6 подаюпгся на регистр 17. По номеру сектора, определйемому по старшим разрядам регистра 17, обнуляется соответствующая ячейка памяти 16, 5,Исполнителыиый адрес подключается к выходу блока 4 и поступает в оперативную память. Информация со считанного блока данных поступает в блок 5 и в буферную память 3, где записывается по адресу, определяемому 0-6 разрядами регистра 17 адреса, по этому же адресу записьюается в соответствующий бит памяти 16, 6.При вьшолнении операции считывания выход блока 5 подключается к входу блока 1, который) принимает таким обрезом нужное ему слово. На этом операция заканчивается, 7..Если производилась операциязаписи, то записываемое слово подключается к информационному выходу блока 1 обработки данных, откуда поступает па ипфор771777 , . .-....... ....-,....-.. . -..- . .. - V L,..„.......а,.-,. ,.....-. ШШонныЙ вход буферной памята 3. В бзн ферную память 3 чйсэтозапйдьшается по Рвиящемуся па регистре 17 аи-реса. а в оперативную память - по адресу, поступающему с выхода блока 4 обра- s щения к оперативной пемяти. На этомоперашя зака&чиваетсз. шифратора 18 и 9-12 рааряЫ входного индексного penicTpia 6 постуч пают па реластр , откуда инфогмадия Ю передается 8 память 16 зна мости. Очпя- J памяти 16 бит через коммутаг Р. подключается к индикаторному входу блока 4 о ащепия к оперативной памяти. 9. Проверка состояния выкода коммун татора 15. Если бит {жаачвмости равен , выход буферной памяти 3 подключается к первому входу блока 5, далее переоеЬдйт к шестому этвшу, если бит значимости равен О, переходят к пятому этепу. Преимуществом изобретения является то, что при работе с любой процедурой обьемом М слов и размещении ее в буфер-г ной п&Аятя, единицей логического pa3(fe- ения которой 5авлается сектор М . слов, упом5анутая процедура в буферной памяти будет занимать максимум секторов,сли М делится па N без здтгатка, или-п + 1 секторов, т.е. во мвргчаос слу- чаях на один сектор меньше, чем в извёстном устройстве. БлагЬдаря этому умепыиается частота обновленной инфор- мации в буферной памяти, что повышает эффективность ее использования, д в ито ге повышает быстродеййтвие вычислитель вой,машины в целом на (в зависи-ч мости от решаемых задач). Формула изобретения Ус11ройсггво для а/фесации буферной , мяте, содержащее группу регистров базы, регистр адреса, первую группу схем сравншия, группу элементов И, згруппу индекс1 ,о . ,О ньй регистров, вторую группу схем оравтевЙя, входной регистр базы, вход которогб соедивен с первым входом устройсява, выход входной регистра базы соедннет с первыми входами схем сравнения первой группы, вторые входы которых соединены с выходами соответствующих ре- гистров базы группы, выходы схем фжпения пфвой группы собдинеты с первыми элементов И группы, о т л ичающееся тем, что, целью повыше- пия коэффициента использования обору дования.внего введены два коммутатора, шифратор, входной индексный регистр, блок элементов ИЛИ, память битов значимости, причем выход входного регистра базы сое- динен с информационными входами регистров базы группы, выходы схем сравнения второй группы соединены со вторыми вход мн соответствующих элеммтов И груоды выходы которых соединены с.соотвегствующими входами ши4ратора и блока элементов ИЛИ, выход которого соединен с входами пержого и второго коммутаторов, выходы первого коммутатора соедипены с у1ф являющими входе1ми соответст вующих регистров базы группы и индеконык pertiCTpoB группы, второй вход уст- ройства через влэдной индексный регистр соединен с первым входом регистра адреса информационными входами индексных регистров группы и пе1жыми входами схем сравнения второй группы, вторые входы которых соединены с выходами соответ- ствуюших вссдексяых регистров группы, вьюсод шифратора соединен оо вторым вхоч рр регистра адреса, выход которого соеч динен с первым выходом устройства и чел рез последовательно соединенные память битов значимости и второй коммутатор со вторым выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Патент QUA & 3693165, .кл. 340-172.5, 1972. 2. Патент США Ni 3588829, кл. 340-172.5, 1971.

Авторы

Даты

1980-02-25—Публикация

1978-01-18—Подача