1

Изобретение относится к вычислительвой технике.

Известно устройство для изменения ад- ресов в стековой памяти, соцержавдее регистры пртаема, выдачи, ацреса, блок управления и арифь етический блок 1.

Недостатком известного устройства является большая сложность и невысокое быстродействие.

Наиболее близким техническим решением к Предложенному изобретению является устройство для коррекции базовых регистров при стековом распределении памяти, содержащее регистр приема, блок формирования связующей информадии, блок формирования програм мной информации, блок управления, арифметический блок, блок базовых регистров, ре Гистр выдачи, регистр адреса, вход которого соединен с выходом .арифметического блока, а выход подключен к выходным адрес- вым шинам устройства, вход регистра приема соединен со входными информационными шинами устройства, входы блока формирова- .ния связующей информации подключены к вы ходам регистра приема, арифметического

блока и блока формирования программной информации, входы которого соединены с выходами регистра приема и арифметического блоки, входы которого соединены с выходами блока базовых регистров и блока формирования программной информации, входы блока базовых регистров соединены с выходом регистра приема и выходом блока формирования программной информации, вход регистра выдачи соединен с выходом блока формирования связующей информации, а выход - с выходными информационньтми шинами устройства, входы блока управления соединены со входными управляющими ши ками устройства и управляющим выходом блока базовых регистров, а выходы - с управляющими входами арифметического блока , блока формирования программной информации, блока формирования связующей информации, блока базовых регистров, регистра приема, регистра выдачи-и регистра адреса.

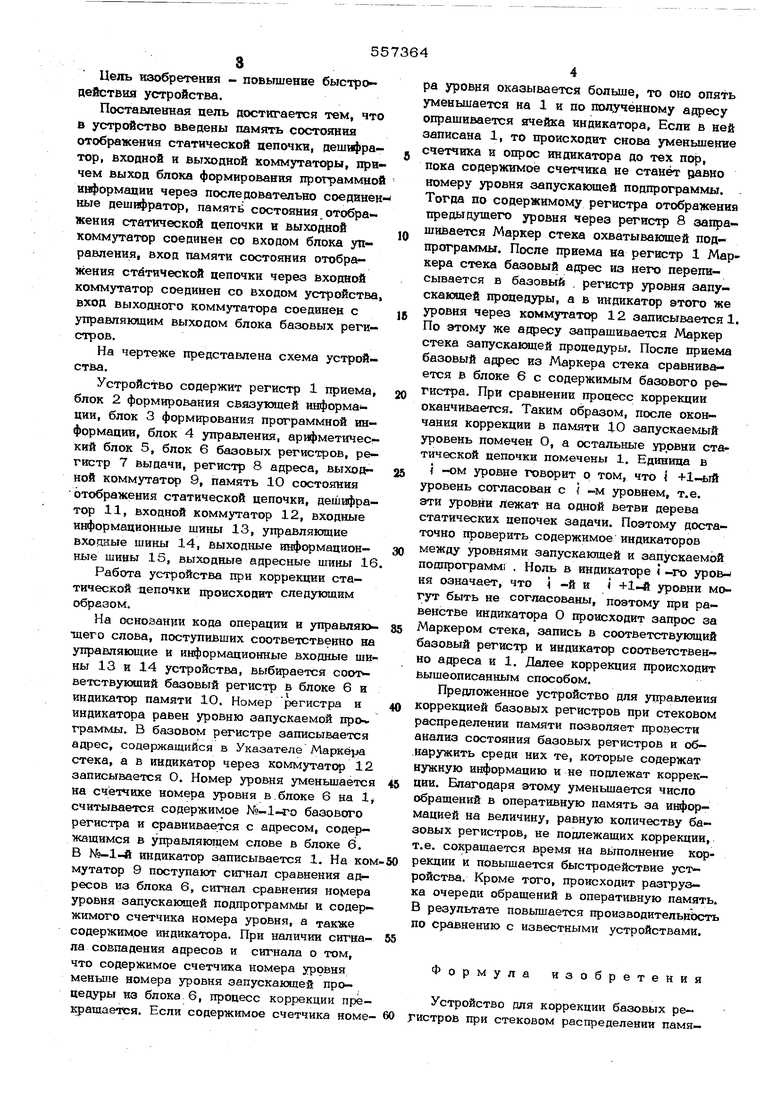

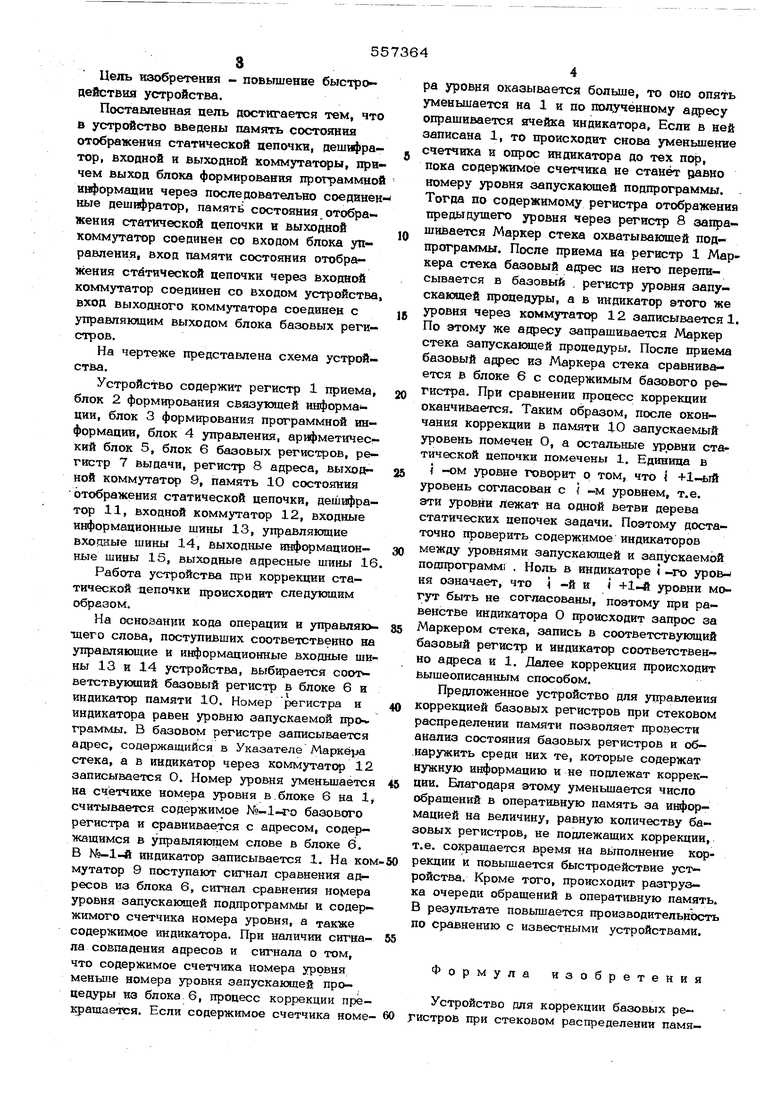

Недостатком известного устройства является низкое бьтстродействие при коррек ции базовьтх регистров адреса. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство введены память состояния отображения статической пепочки, дешифратор, входной и выходной коммутаторы, причем выход блока формирования программной информации через последовательно соединенHbie дешифратор, памяти состояния отображения статической цепочки и выходной коммз татор соединен со входом блока управления, вход памяти состояния отображения стйтической цепочки через входной коммутатор соединен со входом устройства, вход выходного коммутатора соединен с управляющим выходом блока базовых регистров. На чертеже представлена схема устройства. Устройство содержит регистр 1 приема, блок 2 формирования связующей информации, блок 3 формирования программной информации, блок 4 управления, арифметический блок 5, блок 6 базовых регистров, регистр 7 выдачи, регистр 8 адреса, выходной коммутатор 9, память 10 состояния отображения статической цепочки, дешифратор 11, входной коммутатор 12, входные информационные шины 13, управляющие входные шины 14, выходные информационные шины 15, выходные адресные шины 16 Работа устройства при коррекции статической цепочки происходит следующим образом. На основании кода операции и управляютцега слова, поступивших соответственно на управляющие и информационные входные шины 13 и 14 устройства, выбирается соответствукмдий базовый регистр в блоке 6 и индикатор памяти 10. Номер регистра и индикатора равен уровню запускаемой про граммы. В базовом регистре записывается адрес, содержащийся в Указателе Маркёра стека, а в индикатор через коммутатор 12 записывается О. Номер уровня уменьшается на счётчике номера уровня в блоке 6 на 1 считывается содержимое №-1-го базового регистра и сравнивается с адресом, содержащимся в управляклдем слове в блоке 6. В М9-.1-й индикатор записывается 1. На ко мутатор 9 поступают сигнал сравнения адресов из блока 6, сигнал сравнения номера уровня запускающей подпрограммы и содержимого счетчика номера уровня, а также содержимое индикатора. При наличии сигна ла совпадения адресов и сигнала о том, что содержимое счетчика номера уровня меньше номера уровня запускающей процедуры из блока б, процесс коррекции пре кращается. Если содержимое счетчика номе а уровня оказывается больше, то оно опять меньшается на 1 и по полученному адресу прашивается ячейка индикатора. Если в ней аписана 1, то происходит снова уменьшение четчика и опрос индикатора до тех пор, пока содержимое счетчика не станет равно номеру уровня запускающей подпрограммы. Тогда по содержимому регистра отображения предыдущего уровня через регистр 8 запрашивается Маркер стека охватывающей подпрограммы. После приема на регистр 1 Маркера стека базовый адрес из него переписывается в базовый . регистр уровня запускающей процедуры, а в индикатор этого же уровня через коммутатор 12 записывается. По этому же адресу запрашивается Маркер стека запускакяцей процедуры. После приема базовый адрес из Маркера стека сравнивается в блоке 6 с содержимым базового ре- гистра. При сравнении процесс коррекции оканчивается. Таким образом, после окончания коррекции в памяти Ю запускаемый Зфовень помечен О, а остальные уровни статической цепочки помечены 1. Единица в i -ом уровне говорит о том, что i +1-ый уровень согласован с } -м уровнем, т.е. эти уровни лежат на одной ветви дерева статических цепочек задачи. Поэтому достаточно проверить содержимое индикаторов между уровнями запускающей и запускаемой подпрограмм , Ноль в индикаторе I -го ypoBw ня означает, что i -и и +1-Л уровни могут быть не согласованы, поэтому при равенстве индикатора О происходит запрос за Маркером стека, запись в соответствующий базовый регистр и индикатор соответственно адреса и 1, Далее коррекция происходит вышеописанным способом, Предложенное устройство для управления коррекцией базовых регистров при стековом распределении памяти позволяет провести анализ состояния базовых регистров и обнаружить среди них те, которые содержат нужную информацию и не подлежат коррекиии. Благодаря этому уменьшается число обращений в оперативную память за информацией на величину, равную количеству базовых регистров, не подлежащих коррекции, т.е. сокращается время на выполнение коррекции и повышается быстродействие устройства. Кроме того, происходит разгрузка очереди обращений в оперативную память. В результате повышается производительность по сравнению с известными устройствами. Формула изобретения Устройство для коррекции базовых ре гистров при стековом распределении памя

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции базовых регистров | 1976 |

|

SU557365A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Процессор микропрограммируемой ЭВМ | 1979 |

|

SU860077A1 |

| Устройство для управления параллельным выполнением команд в стековой электронной вычислительной машине | 1976 |

|

SU556440A1 |

| Процессор ввода-вывода | 1980 |

|

SU934465A1 |

| Устройство для обработки выражений языков программирования | 1974 |

|

SU519715A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для синтаксически-управляемого перевода | 1982 |

|

SU1062721A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

Авторы

Даты

1977-05-05—Публикация

1976-04-15—Подача