Изобретение относится к области вычислительной техники, в частности к способу и устройству загрузки массивов данных из оперативной памяти в процессор, и может быть использовано при разработке различных вычислительных систем высокого быстродействия.

Доступ к данным памяти вне кристалла является, чаще всего, более медленным, чем выполнение команд центрального процессора, что замедляет выполнение программ процессором. Это особенно важно в тех случаях, когда из памяти в регистры должен быть загружен большой массив данных.

Для ускорения доступа к массивам данных применяются различные способы предварительной подкачки. Их можно условно разделить на программные, аппаратные и программно-аппаратные способы.

Программные способы предварительной подкачки характеризуются тем, что в программный код вводятся дополнительные команды, которые заранее подкачивают в кэш (буферную память) данные. Поскольку подкачка данных идет в кэш, программные способы могут "протирать" кэш, вытесняя из него нужные еще данные. Если кэш не полностью ассоциативный, то возможны конфликты между данными нескольких массивов. К недостаткам программных способов следует отнести дополнительные команды, которые выполняются процессором.

Аппаратные способы предварительной подкачки не обладают достаточной приспособленностью к последовательностям адресов по обращению за элементами массивов в память и эффективно работают лишь в простейших случаях подкачки вперед. Эти способы не адаптированы к возможным переменным задержкам памяти. Подкачка ведется также в кэш или регистровый файл и поэтому возможно "протирание" кэша и конфликты, особенно при работе с несколькими массивами, а также нерациональное использование дорогостоящего пространства регистрового файла.

Существующие программно-аппаратные способы предварительной подкачки в основном сводятся к подсказкам, которыми компилятор отмечает команды обращения в память, чтобы облегчить работу аппаратуры предварительной подкачки.

Известна система временного запоминания информации, содержащая буферную память для записи блока данных, входы данных, структурированных в блоки данных с постоянной или переменной длиной, которые соединены со входом буферной памяти, выходы данных, структурированных в блоки данных с постоянной или переменной длиной, соединенные с выходом буферной памяти, множество очередей ожидания, включающих связи между блоками данных, зарегистрированными в буферной памяти, а также логику управления очередями ожидания, при этом логика управления очередями ожидания блоков данных и выбора выхода содержит очередь ожидания, которая присваивается каждому выходному назначению (см. Патент РФ N 2138845 кл. G 06 F 9/00, от 30.08.91.).

Однако известное устройство не может производить асинхронную загрузку массивов данных, позволяющую достичь максимальную производительность системы.

По технической сущности наиболее близким техническим решением является способ загрузки массива данных из памяти в регистр процессора во время выполнения скомпилированной и скомпактированной циклической программы, включающий следующие шаги:

- назначение в очереди подкачки массива (ОПМ) позиции для загрузки данных массива,

- назначение в ОПМ позиции для обращения к данным массива и пересылки данных массива в регистр,

- исполнение операции считывания из памяти как комбинация двух операций:

а) операция считывания массива,

б) операция пересылки массива,

- при этом операция считывания массива включает обращение к данным массива в памяти и пересылку данных массива в позицию буферной памяти ОПМ, назначенную для загрузки данных массива, а операция пересылки включает пересылку данных массива из позиции буферной памяти ОПМ, указанной указателем считывания в регистр, определяемый операцией пересылки массива, а также система загрузки массива данных, реализующая этот способ, содержащая процессор, оперативную память, буферную память, блок контроллеров подкачки данных и их считывания из буферной памяти в регистры процессора (см. Патент США N 5889985).

Описанный способ является программно-аппаратным, при этом существует главная программа, которая аппаратно разбивается на два командных потока, которые выполняются синхронно со сдвигом, динамически определяемым временем обращения в память.

Недостатком известных способа и устройства является относительно низкая производительность процессов загрузки массивов данных. Это объясняется следующими причинами.

Как известно, из-за сложной иерархической структуры оперативной памяти время обращения (доступа) к различным адресам массива данных не является постоянным.

Хотя известные способ и система адаптированы к задержкам памяти, но процесс предварительной подкачки нельзя начать раньше, чем исполнение программы (тела) цикла. Также возможны потери в темпе предварительной подкачки из-за присутствия помимо считывания других типов операций.

Кроме того, из-за невозможности выполнения групповой подкачки нельзя полностью использовать пропускную способность трактов обращения в память.

Техническим результатом заявляемых изобретений является увеличение производительности процессов загрузки массивов данных путем их асинхронной загрузки с адаптацией к задержкам оперативной памяти.

Дополнительным техническим результатом является разгрузка арифметического устройства центрального процессора от вычисления адресов массивов данных.

Достигается это тем, что в способе асинхронной загрузки массивов данных из оперативной памяти в процессор, заключающемся в подкачке данных из оперативной памяти в буферную память в соответствии с программой подкачки одновременно с выполнением процессором основной программы и последующем считывании данных из буферной памяти в процессор с возможностью подкачки очередных данных в буферную память одновременно со считыванием из нее в процессор, согласно изобретению подкачку данных в буферную память осуществляют под управлением блока контроллеров подкачки данных по командам программы подкачки асинхронно по отношению к выполнению процессором основной программы, а считывание данных из буферной памяти в процессор осуществляют под управлением блока контроллеров считывания данных по командам основной программы, выполняемой процессором, кроме того, подкачку данных из оперативной памяти в буферную память производят в n областей буферной памяти, где n - целое число, каждая из которых определяется информацией четырех полей этих областей, которые располагают в памяти указателей областей, при этом поля содержат адрес начала области, размер области, адрес считывания и адрес записи внутри области, причем в каждую из n областей буферной памяти производят подкачку данных одного массива, кроме того, подкачку очередных данных осуществляют в том случае, когда разница между адресами считывания и записи внутри области меньше количества элементов массива данных, требуемого для выполнения задачи, или в том случае, когда разница между адресами считывания и записи внутри области меньше максимального разрешенного числа элементов массива данных, на которое предварительная подкачка может опережать считывание из буферной памяти в процессор, и при условии разницы между адресами считывания и записи внутри области, меньшей размера области буферной памяти. Предпочтительно подкачку данных из оперативной памяти в буферную память осуществлять порциями, каждая из которых содержит один или несколько элементов массива, и размер порции определять на основании шага считывания (инкремента элементов массива для оптимального использования буферной памяти и пропускной способности тракта считывания оперативной памяти.

Целесообразно максимальный размер порции данных, подкачиваемых за одно обращение в оперативную память, определять таким, который обеспечивает максимальную эффективность режима считывания из оперативной памяти, а минимальный размер порции определять как минимальную порцию считывания из буферной памяти, а также полезно минимальный размер порции задавать в команде подкачки, а подкачку элементов массивов производить путем многократного выполнения команды подкачки, причем адрес считывания из оперативной памяти вычислять как сумму начального адреса массива из памяти адресных данных, индекса элемента массива из памяти адресных данных и поля "константа" из команды подкачки, и для каждого нового выполнения команды подкачки индекс увеличивать на величину шага подкачки, который можно определять как размер порции подкачки в случае, если шаг считывания - инкремент элементов массива меньше или равен порции подкачки или как шаг считывания элементов массива в случае, если этот шаг больше порции подкачки, после чего новое значение индекса сохранять в памяти адресных данных.

Кроме того, подкачку элементов массива можно производить путем многократного выполнения команды подкачки, причем адрес считывания из оперативной памяти вычислять как сумму начального адреса массива из памяти адресных данных, поля "константа" из команды подкачки и индекса элемента массива, который под управлением блока контролеров подкачки данных считывают из буферной памяти, при этом процесс подкачки данных может быть прерван и продолжен после прерывания, для чего в оперативной памяти сохраняют начальные значения индексов, инкрементов и значение регистра итераций цикла, для которых элементы массивов были считаны в процессор из буферной памяти, и при возврате из прерывания продолжают подкачку элементов массивов, начиная с той итерации цикла, на которой вычислительный процесс был прерван, для чего текущие индексы этих элементов массивов вычисляют как сумму начального индекса и произведения количества итераций из регистра итераций цикла на величину инкремента и записывают полученные значения индексов в память адресных данных для использования при вычислении адресов обращения к оперативной памяти, кроме того, в случае возникновения ошибки при подкачке данных из оперативной памяти, процесс подкачки данного массива останавливают, а сообщение об ошибке отправляют в процессор только в том случае, когда блок контроллеров считывания данных по командам основной программы сделает попытку считать из буферной памяти элемент массива, при подкачке которого произошла ошибка.

Решение поставленной технической задачи достигается также тем, что система для асинхронной загрузки массивов данных содержит процессор, оперативную память, буферную память, блок контроллеров подкачки данных из М контроллеров, блок контроллеров считывания данных из К контроллеров, где М и К - целые числа, память адресных данных и память указателей областей, при этом к порту данных оперативной памяти подключены входы процессора и буферной памяти, имеющей связь с процессором, к адресному порту и порту считывания оперативной памяти подключены входы блока контроллеров подкачки данных, связанного с процессором, памятью адресных данных, буферной памятью, памятью указателей областей и блоком контроллеров считывания данных, связанного с буферной памятью, памятью указателей областей и процессором, кроме того, процессор может содержать устройство управления, включающее основной дешифратор команд, дешифратор команд асинхронной программы и буферную память команд, причем дешифратор команд асинхронной программы связан с блоком контроллеров подкачки данных и с буферной памятью команд, которая соединена с основным дешифратором команд, а система дополнительно может содержать память для хранения асинхронно выполняемой программы, соединенную с блоком контроллеров подкачки данных, кроме того, целесообразно, чтобы каждый контроллер блока контроллеров подкачки данных содержал устройство управления, включающее дешифратор команд и буферную память команд, а блок контроллеров подкачки данных имел связь с портом данных оперативной памяти.

Сущность изобретения для способа заключается в том, что для обеспечения асинхронной подкачки новых данных относительно считывания данных из буферной памяти в процессор цикловую часть исполняемой программы на этапе компиляции преобразуют в асинхронно выполняемую часть программы и в синхронно выполняемую часть программы, являющуюся частью основной программы, причем запуск асинхронно выполняемой части программы на выполнение осуществляют основной программой, в которой определяют время запуска таким образом, чтобы все необходимые данные массива находились в буферной памяти с упреждением до начала выполнения синхронно выполняемой части программы, а одновременную подкачку данных из оперативной памяти продолжают по мере выборки из буферной памяти ранее подкаченных данных синхронно выполняемой частью программы, которая управляет пересылкой элементов массива из буферной памяти в регистры процессора и выполняет все необходимые операции над элементами массива, включая запись в оперативную память результатов вычислений.

Сущность изобретения как устройства заключается в том, что особенности выполнения системы вышеописанным образом позволяют увеличить производительность процессов загрузки данных путем выполнения подкачки данных в буферную память под управлением блока контроллеров подкачки данных в соответствии с программой подкачки асинхронно по отношению к работе процессора по основной программе.

Сравнение заявленных изобретений с ближайшим аналогом позволяет утверждать о соответствии критерию "новизна", а отсутствие в известных аналогах отличительных признаков говорит о соответствии критерию "изобретательский уровень". Предварительные испытания позволяют судить о возможности широкого промышленного использования.

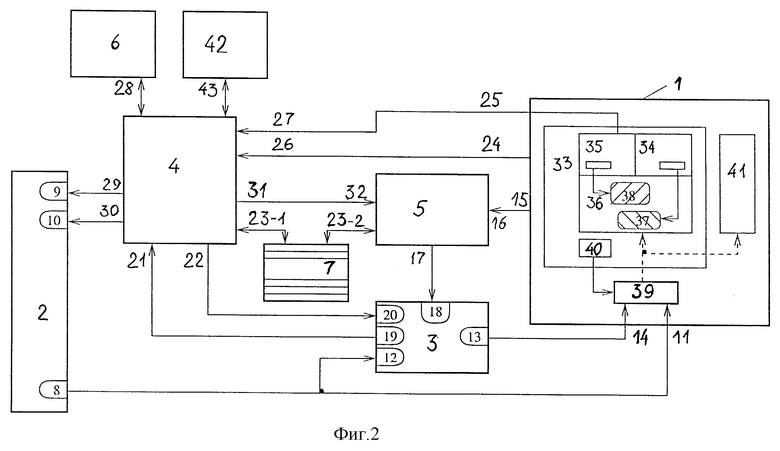

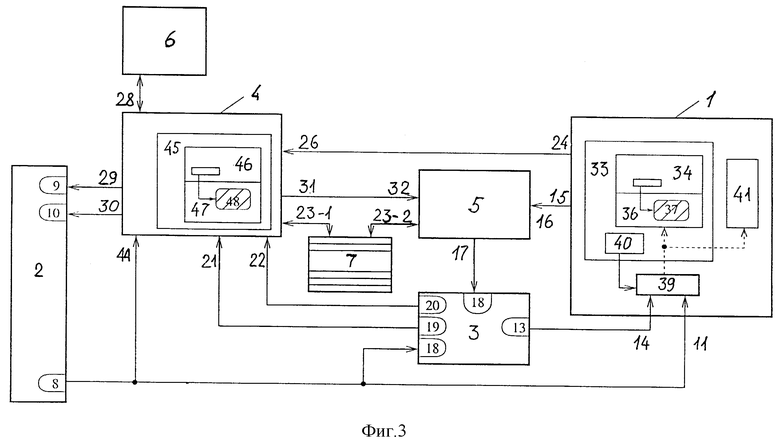

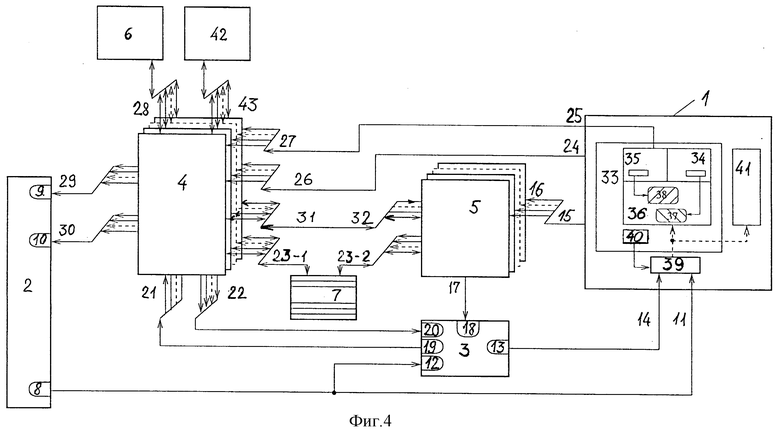

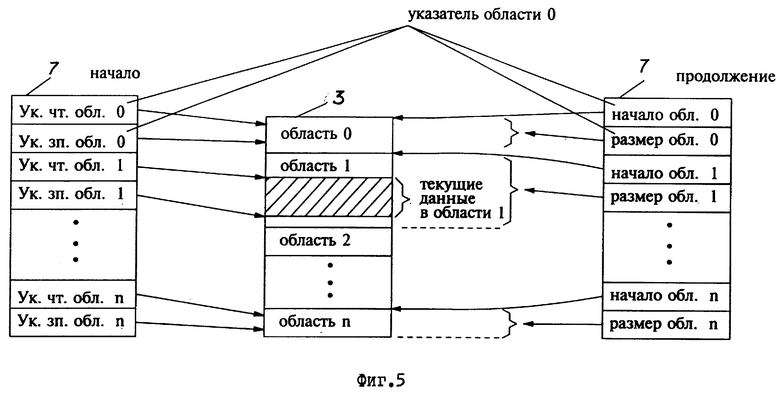

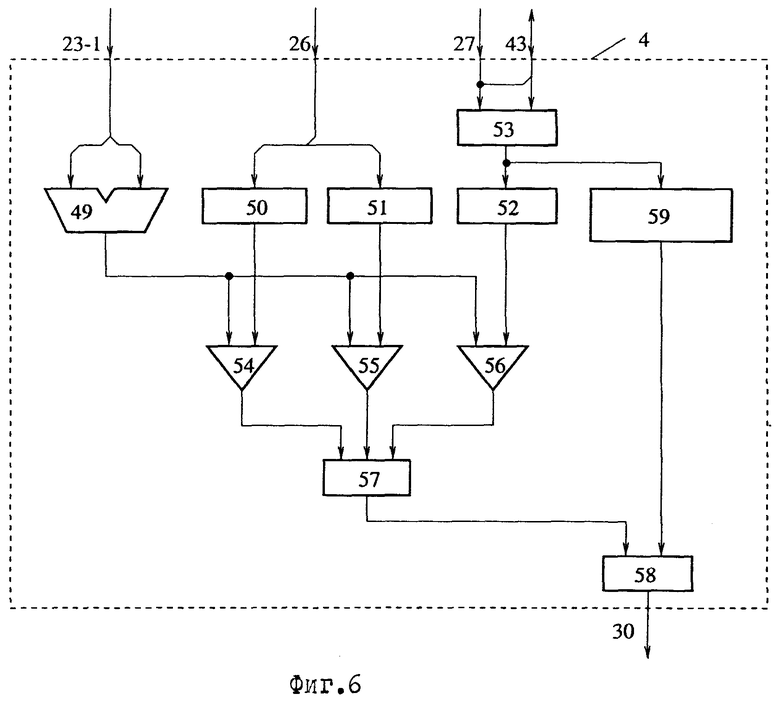

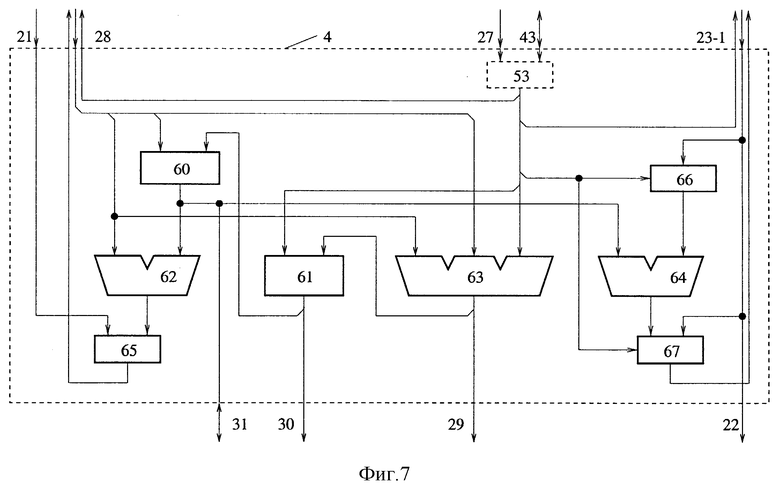

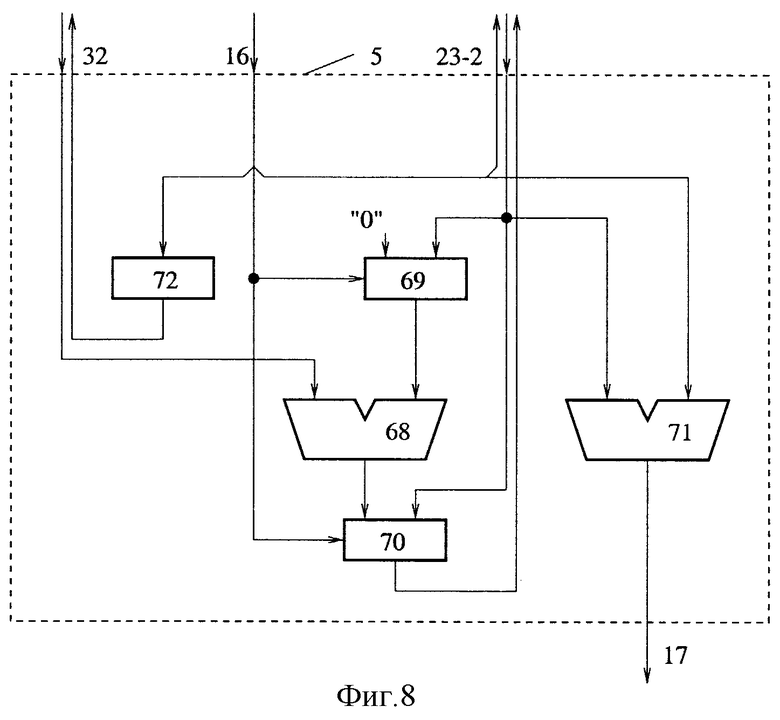

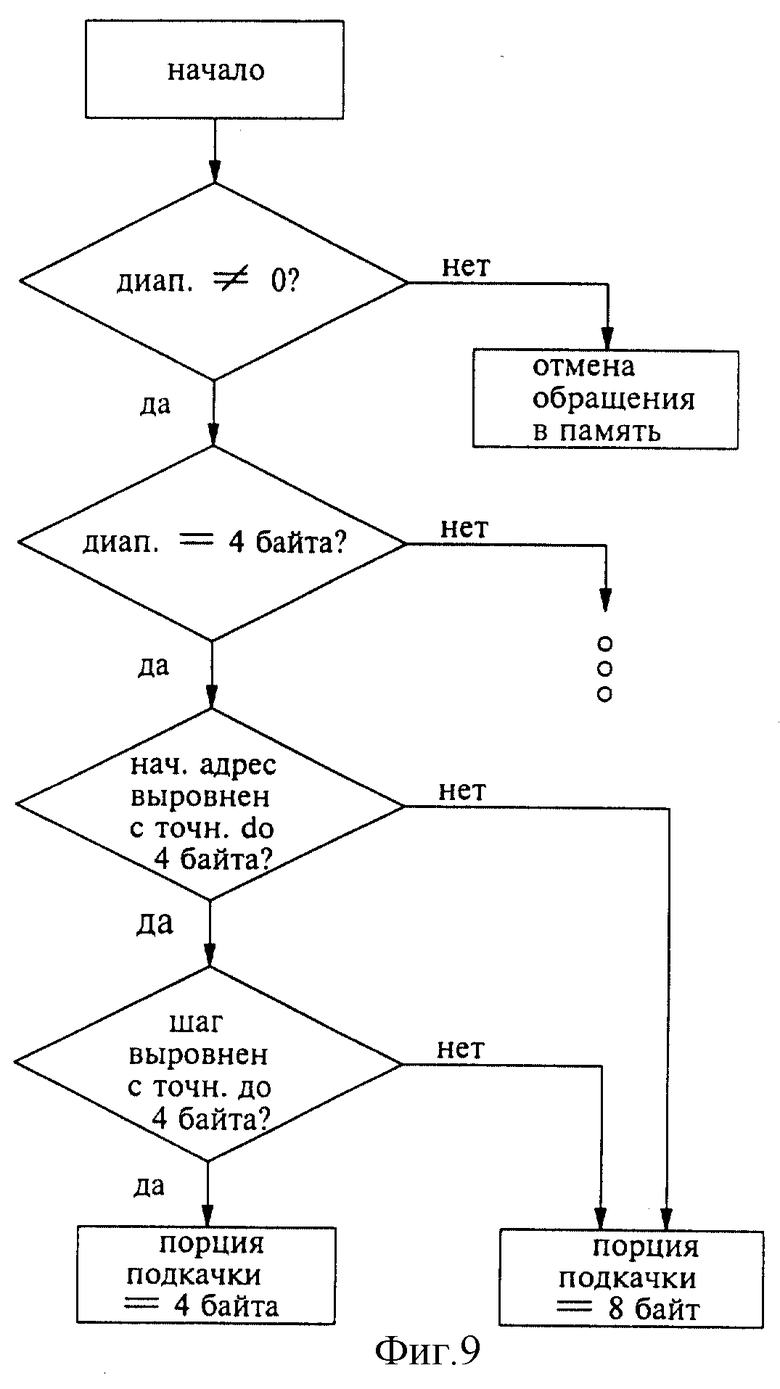

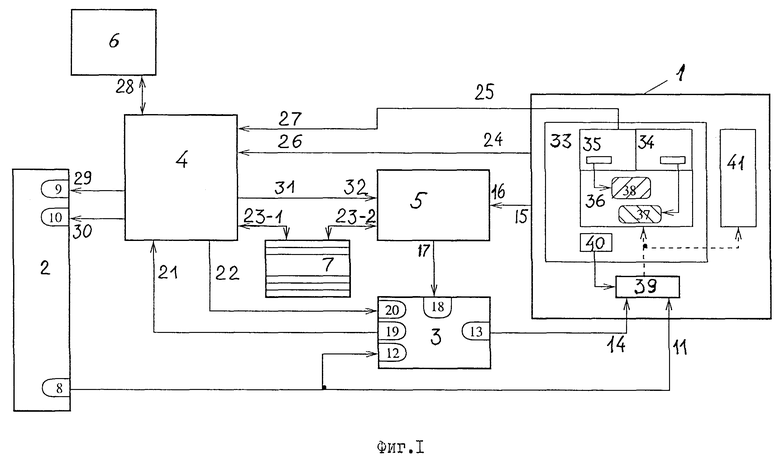

На фиг. 1-4 представлены функциональные блок-схемы вариантов предложенного устройства, реализующие заявляемый способ, на фиг. 5 - структура памяти указателей областей и буферной памяти данных, на фиг. 6, 7 - функциональная блок-схема контроллера блока контроллеров подкачки данных, на фиг. 8 - контроллера блока контроллеров считывания данных, на фиг. 9 - алгоритм работы формирователя порции подкачки контроллера блока контроллеров подкачки данных.

Система для асинхронной загрузки массива данных (фиг. 1) содержит процессор 1, оперативную память 2, буферную память 3, блок 4 контроллеров подкачки данных из М контроллеров, блок 5 контроллеров считывания данных из K контроллеров, где M и K - целые числа 1, 2, 3,..., память 6 адресных данных для хранения дескрипторов, индексов и инкрементов и память 7 указателей областей.

Оперативная память 2 имеет порты 8-10 данных - адресный и считывания соответственно. К порту 8 данных подключены первые входы 11 и 12 процессора 1 и буферной памяти 3 соответственно, первый выход 13 которой подключен ко второму входу 14 процессора 1, первый выход 15 которого подключен к входу 16 блока 5 контроллеров, выход 17 которого подключен ко второму входу 18 буферной памяти 3, связанной вторым выходом 19 и третьим входом 20 с первым входом 21 и первым выходом 22 блока 4 контроллеров подкачки данных, имеющего связь 23-1 с памятью 7 указателей областей. Последняя имеет связь 23-2 с блоком 5 контроллеров считывания данных.

Второй и третий выходы 24 и 25 процессора 1 подключены к соответствующим второму и третьему входам 26 и 27 блока 4 контроллеров подкачки данных, имеющему связь 28 с памятью 6 адресных данных для хранения дескрипторов, индексов и инкрементов.

К портам 9 и 10 - адресному и считывания оперативной памяти 2 подключены соответственно второй и третий выходы 29 и 30 блока 4 контроллеров подкачки данных, вход-выход 31 которого подключен к выходу-входу 32 блока 5 контроллеров считывания данных.

Процессор 1 содержит устройство 33 управления, включающее основной дешифратор 34 команд, дешифратор 35 команд асинхронной программы и буферную память 36 команд с областями 37 и 38 размещения основной и асинхронной программ, а также мультиплексор 39, управляемый флагом 40 доступа памяти и регистры 41.

На фиг. 1 отсутствуют стандартные узлы и связи, общепринятые для любой процессорной системы, в том числе для прототипа.

На фиг. 2 присутствует память 42 асинхронной программы, имеющая связь 43 с блоков 4 контроллеров подкачки данных.

На фиг. 3 показана дополнительная связь 44 блока 4 контроллеров подкачки данных с портом 8 данных оперативной памяти 2, а также конкретизация выполнения блока 4, каждый контроллер которого содержит устройство 45 управления, включающее дешифратор 46 команд и буферную память 47 команд, буферное устройство для хранения команд с областью 48 размещения асинхронной программы.

Каждый контроллер подкачки данных блока 4 (фиг. 6 и 7) содержит сумматор 49, регистры 50 - 52, мультиплексор 53, узлы 54-56 сравнения, элемент 57 "ИЛИ-НЕ", элемент "И", узел 59 управления, формирователь 60 шага подкачки, формирователь 61 порции подкачки, сумматоры 62-64, выходной мультиплексор 65, входной мультиплексор 66 и выходной мультиплексор 67.

Каждый контроллер блока 5 (фиг. 8) содержит сумматор 68 указателя считывания, мультиплексоры 69, 70 для зацикливания указателя считывания в пределах заданной области, сумматор 71 адреса считывания и регистр 72 итерации цикла.

Сумматор 49 предназначен для вычисления разницы между указателями (адресами) записи и считывания областей.

Регистр 50 служит для промежуточного хранения количества оставшихся элементов массива из процессора 1.

Регистр 51 служит для промежуточного хранения максимально разрешенного числа элементов массива, на которые предварительная подкачка может опережать считывание из буферной памяти 3 в процессор 1.

Регистр 52 служит для промежуточного хранения размера области в буферной памяти 3 из асинхронной команды.

Мультиплексор 53 асинхронных команд служит для коммутации асинхронных команд из процессора 1 или из памяти 42 асинхронной программы.

Узел 54 сравнения служит для сравнения разницы между указателями (адресами) записи и считывания с оставшимися элементами массива из процессора 1.

Узел 55 сравнения служит для сравнения разницы между указателями (адресами) записи и считывания с максимально разрешенным числом элементов массива, на которые предварительная подкачка может опережать считывание из буферной памяти 3 в процессор 1.

Узел 56 сравнения служит для сравнения разницы между указателями (адресами) записи и считывания с размером области из асинхронной команды.

Узел 59 управления служит для осуществления функции разрешения обращения в оперативную память 2.

Формирователь 60 служит для определения величины шага подкачки из инкремента и размера порции подкачки.

Формирователь 61 служит для определения порции подкачки в зависимости от диапазона подкачки из асинхронной команды.

В устройстве может быть использована стандартная система тактирующих импульсов. Цепи управляющих и тактирующих импульсов на фигурах не показаны.

Способ асинхронной загрузки массивов данных из оперативной памяти 2 в процессор 1 осуществляется программно-аппаратным методом и включает в себя операцию подкачки данных из оперативной памяти 2 в буферную память 3 на фоне выполнения процессором 1 основной программы и последующую операцию считывания данных из буферной памяти 3 в процессор 1. При этом обеспечена возможность подкачки очередных данных в буферную память 3 на фоне считывания из нее в процессор 1.

Особенностью данного способа является то, что подкачку данных в буферную память 3 осуществляют под управлением блока 4 контроллеров подкачки данных путем выполнения специальной программы подкачки асинхронно по отношению к выполнению процессором 1 основной программы, а считывание данных из буферной памяти 3 в процессор 1 осуществляют под управлением блока 5 контроллеров считывания данных по командам основной программы, выполняемой процессором 1.

Операция подкачки заключается в считывании из оперативной памяти 2 по определенному адресу части массива данных и записи его в буферную память 3.

Подкачку данных из оперативной памяти 2 в буферную память 3 производят в "n" областей буферной памяти 3, где n - целое число, причем каждая область предназначена для данных одного массива. Каждая из областей определяется информацией четырех полей этих областей, которые располагают в памяти 7 указателей областей, при этом поля содержат адрес начала области, размер области, адрес считывания и адрес записи внутри области.

Подкачку элементов массивов производят путем многократного выполнения команды подкачки, причем адрес считывания из оперативной памяти 2 вычисляют как сумму начального адреса массива и индекса элемента массива из памяти 6 адресных данных и поля "константа" из команды подкачки, для каждого нового выполнения команды индекс увеличивают на величину шага подкачки, который определяют как размер порции подкачки в случае, если шаг считывания (инкремент) элементов массива меньше или равен порции подкачки, или как шаг считывания элемента массива в случае, если этот шаг больше порции подкачки.

Подкачку очередных данных осуществляют при условии разницы между адресами считывания и записи внутри области, меньшей требуемого для выполнения задачи количества элементов массива данных. Также подкачку очередных данных осуществляют при условии разницы между адресами считывания записи внутри области, меньшей максимально разрешенного числа элементов массива данных, на которые предварительная подкачка может опережать считывание из буферной памяти в процессор.

Также подкачку очередных данных осуществляют при условии разницы между адресами считывания и записи внутри области, меньшей размера области буферной памяти.

Подкачку данных из оперативной памяти 2 в буферную память 3 осуществляют порциями, каждая из которых содержит один или несколько элементов массивов, а размер порции при этом нужно определять на основании шага считывания (инкремента) элементов массивов для оптимального использования буферной памяти 3 и пропускной способности тракта считывания оперативной памяти 2.

Целесообразно максимальный размер порции данных, подкачиваемых за одно обращение в оперативную память 2, определять таким, чтобы обеспечить максимальную эффективность режима считываний из оперативной памяти 2, а минимальный размер порции определять как минимальную порцию считывания из буферной памяти 3. Также возможно минимальный размер порции задавать в команде подкачки.

Кроме того, подкачку элементов массива производят путем многократного выполнения команды подкачки, причем адрес считывания из оперативной памяти 2 вычисляют как сумму начального адреса массива из памяти 6 адресных данных, поля "константа" из команды подкачки и индекса элемента массива, который считывает блоком 4 контроллеров подкачки данных из буферной памяти 3.

Процесс подкачки данных может быть прерван и продолжен после прерывания, для чего в оперативной памяти 2 сохраняют начальные значения индексов, инкрементов и значение регистра 72 итераций цикла, для которых элементы массивов были считаны в процессор 1 из буферной памяти 3, и при возврате из прерывания продолжают подкачку элементов массивов, начиная с той итерации цикла, на которой вычислительный процесс был прерван, для чего текущие индексы этих элементов массивов вычисляют как сумму начального индекса и произведения количества итераций цикла на величину инкремента и записывают полученные значения индексов в память 6 адресных данных для использования при вычислении адресов обращения к оперативной памяти 2.

В случае возникновения ошибки при подкачке данных из оперативной памяти 2 процесс подкачки данного массива останавливают, а сообщение об ошибке отправляют в процессор 1 только в том случае, когда блок 5 контроллеров считывания данных по командам основной программы сделает попытку считать из буферной памяти 3 элемент массива, при подкачке которого произошла ошибка.

Сущность способа заключается в том, что для обеспечения асинхронной подкачки новых данных относительно считывания данных из буферной памяти 3 в процессор 1 цикловую часть исполняемой программы на этапе компиляции преобразуют в асинхронно выполняемую часть программы и в синхронно выполняемую часть программы, являющейся частью основной программы, причем запуск асинхронно выполняемой части программы на выполнение осуществляют основной программой, в которой определяют время запуска таким образом, чтобы все необходимые данные массива находились в буферной памяти 3 с упреждением до начала выполнения синхронно выполняемой части программы, а одновременную подкачку данных из оперативной памяти 2 продолжают по мере выборки из буферной памяти 3 ранее подкаченных данных синхронно выполняемой частью программы, которая управляет пересылкой элементов массива из буферной памяти 3 в регистры процессора 1 и выполняет все необходимые операции над элементами массива, включая запись в оперативную память 2 результатов вычислений.

Асинхронность работы блока 4 контроллеров подкачки данных дает возможность обеспечить гладкую адаптацию высоко оптимизированного цикла к непредсказуемым динамическим ситуациям в подсистеме оперативной памяти 2.

Вычисление адресов массивов на специализированном устройстве - вышеописанных блоках контроллеров дает возможность освободить от этой работы арифметические устройства процессора 1 и повысить производительность системы в целом.

Основная программа исполняется процессором 1 (фиг. 1), при этом дешифрация команд основной программы расположенных в буферной памяти 36 команд в области 37 производится дешифратором 34 команд, который адресуется к этой области. Данные для работы основной программы могут поступать из выходного порта 8 данных оперативной памяти 2 в процессор 1 непосредственно через мультиплексор 39. Управление мультиплексором 39 осуществляется флагом 40 доступа памяти, устанавливаемым из основной программы.

При наличии в программе части, требующей вычислений с массивами данных, заблаговременно до начала вычислений производится подготовка к работе с массивами. Для этого с выхода 24 процессора 1 через блок 4 контроллеров подкачки данных осуществляется загрузка памяти 6 адресных данных дескриптора и, определяющими начальные адреса массивов по оперативной памяти 2, индексов элементов массивов и инкрементов, т.е. шагов по массиву. После этого запускается дешифрация команд асинхронной программы, расположенных в буферной памяти 36 команд в области 38. Это производится дешифратором 35, который адресуется к области 38. Асинхронные команды из дешифратора 35 через выход 25 процессора 1 циклически подаются на вход 27 блока 4 контроллеров подкачки данных, который в ответ на каждую из команд выполняет определенную последовательность операций. В предпочтительном варианте осуществления изобретения данная последовательность операций выполняется следующим образом.

Сначала блок 4 контроллеров подкачки данных по связи 23-1 устанавливает в памяти 7 значения полей начала области и размера области указателей областей, затем по адресам из асинхронной команды считывает значения дескриптора индекса и инкремента, хранящиеся в памяти 6 адресных данных, и на основе их значений и константы из асинхронной команды вычисляет адрес по оперативной памяти 2, выдает команду загрузки по этому адресу с выходов 29, 30 в порты 9, 10 оперативной памяти 2 и изменяет текущее значение индекса, используя значение инкремента.

Для лучшего понимания вышеописанные операции можно проиллюстрировать следующим примером. Предположим, что массив состоит из "10" элементов m1, m2, m3, ..., m10. Дескриптор данного массива определяет адрес в оперативной памяти 2, по которому хранится первый элемент m1 массива. Индекс массива определяет величину смещения внутри массива, как это описано ниже. Значение инкремента определяет размер шага в системе при изменении значения индекса, как это описано ниже.

Предположим, например, что дескриптор массива m определяет адрес A1="1" в оперативной памяти 2, индекс массива равен "3", инкремент равен "2" и константа равна "1". В данном случае один из контроллеров блока 4 контроллеров подкачки данных вычисляет адрес загрузки по формуле "значение адреса загрузки = значение дескриптора + значение индекса + значение константы", т. е. A1 + "3" + "1" = A5. Данный адрес пересылается в оперативную память 2 и считывается элемент m5. Затем контроллер блока 4 контроллеров подкачки данных увеличивает значение индекса на "2" (в результате индекс будет равен "5"). Таким образом, при выполнении следующей команды загрузки адрес загрузки будет равен A1 + "5" + "1" = A7.

Затем контроллер блока 4 контроллеров подкачки данных вычисляет адрес в буферную память 3 данных, определяющий местоположение в ней, куда будет производиться запись массива данных из оперативной памяти 2. Этот адрес формируется на основе значений полей указателя области - поля "начало области" и поля "указатель записи". Сформированный адрес передается в буферную память 3 данных через выход 22. Одновременно контроллер блока 4 контроллеров подкачки данных модифицирует поле "указатель записи" памяти 7 указателей областей через связь 23-1, таким образом продвигая указатель вниз относительно указателя считывания в иллюстрации, представленной на фиг. 5. Этим указатель записи перемещается в следующую позицию в буферной памяти 3 данных, определяя адрес записи следующей порции данных из оперативной памяти 2. Разница между указателями записи и считывания определяет количество данных, подкаченных из оперативной памяти 2 в буферную память 3 данных. Таким образом, блок 4 контроллеров подкачки данных вычисляет адреса для доступа к оперативной памяти 2 и производит загрузки элементов массива одновременно с выполнением основной программы процессором 1.

Более подробно работа контроллера блока 4 контроллеров подкачки данных поясняется при описании работы по фиг. 7. На трехвходовый сумматор 63, на котором вычисляется адрес по оперативной памяти 2, поступают по связи 28 значения дескриптора (начальный адрес) индекса, а из асинхронной команды со входа 27 через мультиплексор 53 - значение константы. Полученный адрес через выход 29 выдается в оперативную память 2. Одновременно на сумматоре 62 производится модификация индекса. Текущее значение индекса поступает по связи 28 на один вход сумматора 62, а инкремента со входа 28 через формирователь 60 шага подкачки на другой вход сумматора 62. Выдача нового значения индекса производится через мультиплексор 65 и связь 28 на запись в память 6 адресных данных. На сумматоре 64 производится вычисление нового значения указателя записи, которое через связь 23-1 подается в память 7 указателей областей. Текущее значение указателя записи через связь 23-1 поступает на вход сумматора 64, а также используется как адрес записи по буферной памяти 3 данных. Значение инкремента поступает через формирователь 60 шага подкачки на второй вход сумматора 64. Мультиплексоры 66 и 67 служат для зацикливания указателя записи в пределах размера области, заданной в асинхронной команде, поступающей со входа 27 через мультиплексор 53.

Управляемый основной программой процессор 1 осуществляет доступ к элементам массива в буферной памяти 3 данных с помощью команд считывания, содержащих ссылки на указатели областей памяти 7. При получении команды основной программы на считывание из буферной памяти 3 данных процессор 1 посылает соответствующую команду контроллеру блока 5 контроллеров считывания данных, чтобы он осуществил доступ к элементам массива буферной памяти 3 данных. При этой команде контроллер блока 5 контроллеров считывания данных формирует адрес на основе значений полей указателя области - поля начала области и поля указателя считывания и затем передает этот адрес в буферную память 3 данных с выхода 17. Одновременно контроллер блока 5 контроллеров считывания данных изменяет значение указателя считывания по связи 23-2, таким образом сдвигая указатель вниз, как показано на фиг. 5. При этом указатель перемещается на другую ячейку буферной памяти 3 данных, подлежащую считыванию, и освобождает место в данной области. Элементы массивов считываются из буферной памяти 3 данных через выход 13 и далее через мультиплексор 39 пересылаются в регистры 41 процессора 1.

Более подробно работа контроллера блока 5 контроллеров считывания данных поясняется при описании работы по фиг. 8. На сумматоре 68 производится вычисление нового значения указателя считывания, которое через связь 23-2 подается в память 7 указателей областей. Текущее значение указателя считывания через связь 23-2 поступает на вход сумматора 68. На другой вход сумматора 68 поступает инкремент со входа-выхода 32. Мультиплексоры 69 и 70 служат для зацикливания указателя записи в пределах размера области, заданной в команде, поступающей со входа 16. Текущее значение указателя считывания также используется для вычисления адреса считывания по буферной памяти 3 данных. Для этого используется сумматор 71 адреса, на второй вход которого поступает значение поля смещения из синхронной команды. С помощью этого поля смещения можно считывать соседние элементы массива, поскольку в буферной памяти 3 данных запоминаются не отдельные элементы массивов, а порции данных, отражающие непрерывные участки оперативной памяти 2, содержащие один и более элементов массивов. С выхода 17 сумматора 71 адрес считывания поступает на вход 18 буферной памяти 3 данных.

Вариант системы, представленный на фиг. 2, отличается от вышеописанного варианта по фиг. 1 дополнительной памятью 42 асинхронной программы, что позволяет освободить процессор 1 от работы, связанной с циклической подачей команд асинхронной программы в блок 4 контроллеров подкачки данных. В отличие от системы на фиг. 1 в системе на фиг. 2 процессор 1 при подготовке к вычислениям, требующим массивы данных, заблаговременно до начала вычислений однократно производит дешифрацию команд асинхронной программы, расположенных в буферной памяти 36 команд в области 38. Асинхронная программа из дешифратора 35 команд через выход 25 процессора 1 однократно поступает на вход 27 блока 4 контроллеров подкачки данных и далее через связь 43 запоминается в памяти 42 асинхронной программы. Процессор 1 с выхода 24 подает сигнал на вход 26 блока 4 контроллеров подкачки данных, по которому тот начинает самостоятельно считывать асинхронные команды из памяти 42 асинхронной программы. Далее система работает, как описано для варианта, показанного на фиг. 1.

Вариант системы, представленный на фиг. 3, отличается от вышеописанных вариантов особенностью выполнения блока 4 контроллеров подкачки данных процессора 1 и наличием дополнительной связи 44 блока 4 контроллеров подкачки данных с портом 8 данных оперативной памяти 2. Это позволяет без усложнения конструкции процессора 1 обеспечить функциональные возможности системы за счет расширения возможностей блока 4 контроллеров подкачки данных, который частично может выполнять функции процессора 1 в части считывания асинхронной программы из оперативной памяти 2 и дешифрации команд асинхронной программы. При этом блок 4 контроллеров подкачки данных содержит дополнительно устройство 45 управления, буферную память 47 команд, где располагается область 48 с асинхронными командами и дешифратор 46 команд. Процессор 1 с выхода 24 подает сигнал на вход 26 блока 4 контроллеров подкачки данных, по которому тот начинает самостоятельно считывать асинхронную программу из оперативной памяти 2. Далее система работает, как описано для варианта, показанного на фиг. 1.

В предпочтительном варианте основная программа определяет время подачи сигнала на запуск исполнения блоком 4 контроллеров подкачки данных таким образом, чтобы все необходимые данные уже находились в буферной памяти 3 данных до начала выполнения синхронной части циклической программы, т.е. заранее, до начала вычислений с элементами массивов. Однако, если необходимые данные еще не находятся в буферной памяти 3 данных, блок 5 контроллеров данных повторяет доступ к буферной памяти 3 данных до тех пор, пока требуемые элементы массива не поступят из оперативной памяти 2.

Оптимизация обращений к оперативной памяти 2.

В зависимости от расположения элементов массивов в оперативной памяти 2 и шага между ними блок 4 контроллеров подкачки данных оптимизирует режим обращения в оперативную память 2 и величину порции подкачки для экономии места в буферной памяти 3 данных. Для этого по диапазону, в котором расположены элементы массива из асинхронной команды, и начальному адресу элемента массива из дескриптора вычисляется требуемая порция подкачки. На фиг. 9 показан пример алгоритма вычисления порции подкачки для диапазона, равного "4" байта. Суть алгоритма состоит в том, чтобы требуемый диапазон данных, заданный в асинхронной команде, всегда находился в порции подкачки, определяемой параметрами конкретной используемой оперативной памяти 2. Таким образом, в буферной памяти 3 данных запоминаются не отдельные элементы массивов, а порции данных, отражающие непрерывные участки оперативной памяти 2, содержащие один или более элементов массивов.

Для оптимизации обращения в оперативную память 2 вычисляется шаг подкачки, который определяют как размер порции подкачки в случае, если инкремент элемента массива меньше или равен порции подкачки, или как шаг считывания элементов массива в случае, если этот шаг больше порции подкачки. Это позволяет осуществить режим работы с оперативной памятью 2 с максимальной производительностью (групповые обращения) или с меньшими квантами подкачки для экономии пространства буферной памяти 3 данных.

Адресация к массиву данных в оперативной памяти 2 через массив произвольных индексов.

Массив данных, подкаченных в какую-либо область буферной памяти 3 данных, может быть использован в качестве индексов при вычислении адресов элементов других массивов из оперативной памяти 2. Описываемая система позволяет асинхронно от выполнения основной программы осуществить предварительную подкачку элементов таких массивов. Блок 4 контроллеров подкачки данных считывает массив произвольных индексов через выход 19 из буферной памяти 3 данных и помещает их в память 6 адресных данных для формирования адресов обращения в оперативную память 2 за элементами массивов.

Первоначально массив произвольных индексов, как и любой другой массив данных загружается в область буферной памяти 3 сданных, как было описано выше. Из потока асинхронных команд блок 4 контроллеров подкачки данных выделяет команды чтения и направляет их с выхода-входа 31 в блок 5 контроллеров считывания данных на вход-выход 32. Асинхронные команды чтения имеют более низкий приоритет по отношению к синхронным командам чтения из процессора 1. Поэтому, если контроллер блока 5 занят выполнением синхронных команд чтения, асинхронные команды считывания не выполняются контроллером блока 5 контроллеров считывания данных.

Если контроллер блока 5 контроллеров считывания данных свободен, то асинхронная команда считывания начинает выполняться им, который через память 7 указателей областей формирует адреса для считывания элементов массивов. В случае неготовности данных в буферной памяти 3 данных, в отличие от случая выполнения синхронной команды чтения, контроллер блока 5 контроллеров считывания данных не останавливает основную программу, а только не выдает подтверждения считывания данных и переходит к выполнению следующей команды. Если данные готовы, они считываются из буферной памяти 3 через выход 19 и поступают в контролер блока 4 на вход 21, далее записываются в память 6 адресных данных в качестве индексов. При этом устанавливается соответствующий бит значимости в маске значимости индексов в памяти 6 адресных данных.

Когда контролер блока 4 подкачки данных в ответ на поступившую асинхронную команду обнаруживает установленный бит значимости в маске значимости индексов в памяти 6 адресных данных, то он формирует адрес для обращения в оперативную память 2 и выполняет это обращение за элементами массивов на фоне работы основной программы. Считанные из оперативной памяти 2 данные помещаются в области буферной памяти 3 данных, определенные памятью 7 указателей областей, и могут быть использованы как в регистрах 41, так и в качестве индексов в блоке 4 контроллеров подкачки данных.

Остановка подкачки данных.

Управление подкачкой данных в буферную память 3 данных в блоке 4 контроллеров подкачки данных осуществляется через механизм указателей областей массивов (указатели считывания, указатели записи) с использованием формата элементов массива из асинхронной команды, шага подкачки (приращения индекса), величины порции подкачки при обращении в оперативную память 2, размера области буферной памяти 3 данных. Остановка подкачки может произойти по трем описанным ниже условиям.

Во-первых, осуществляется контроль максимального разрешенного числа элементов массивов, на которое предварительная подкачка может опережать синхронную программу чтения из буферной памяти 3 данных. Это максимально разрешенное число элементов массивов определяется компилятором и прописывается в специальный регистр 51 (фиг. 6) в контроллере блока 4 контроллеров подкачки данных. При условии подкачки заданного числа элементов массивов, что определяет разница между указателями записи и считывания, вычисляемая сумматором 49, процесс подкачки приостанавливается. При условии уменьшения опережения процесс подкачки автоматически возобновляется. Данный контроль позволяет компилятору поддерживать согласованное состояние данных в буферной памяти 3 данных и оперативной памяти 2. Это необходимо для правильного выполнения программы в случаях, когда данные, записанные в оперативную память 2 в одной итерации цикла, затем считываются в более поздней итерации. Данное свойство является важной отличительной чертой описываемого устройства.

Во-вторых, осуществляется контроль заполненности данными буферной памяти 3 данных. При условии полного заполнения данными, содержащими элементы массива, на памяти какой-либо области буферной памяти 3 данных, что выражается в том, что расстояние между указателями записи и считывания равно размеру области буферной памяти 3 данных, процесс подкачки данных в эту область приостанавливается. При условии освобождения пространства в этой области (например, считывание данных из буферной памяти 3 данных блока 5 считывания данных) хотя бы на величину одной порции подкачки процесс подкачки данных в эту область автоматически возобновляется.

В-третьих, осуществляется контроль количества подкаченных элементов массива и точная остановка процесса подкачки в каждую область буферной памяти 3 данных при выдаче в оперативную память 2 необходимого числа запросов за требуемым количеством элементов массивов. Количество оставшихся элементов массива сохраняется на регистре 50. Данное свойство является важной отличительной чертой описываемого устройства, так как позволяет избежать лишних запросов в оперативную память 2, которые увеличивают нагрузку на нее и, кроме того, могут вызвать нарушения вычислительного процесса (выход за границу массива, отсутствие страницы в оперативной памяти 2).

Разрешение на обращение в оперативную память 2 выдается с выхода 30 блока 4 контроллеров подкачки данных.

Отложенное сообщение об ошибке подкачки данных.

В случае возникновения ошибки при подкачке данных из оперативной памяти 2 процесс подкачки данного массива останавливается. Это означает, что значение указателя записи из памяти 7 указателей областей больше не изменяют, поэтому оно сохраняется. Однако остановки выполнения блоком 4 контроллеров подкачки данных асинхронной программы - подкачки других массивов не происходит. При считывании данных из буферной памяти 3 данных производят сравнение указателей записи и считывания и при их совпадении, когда блок 5 контроллеров считывания данных пытается считать элемент массива, при подкачке которого произошла ошибка, в процессор 1 из буферной памяти 3 выдается сообщение об ошибке.

Прерывание и возобновление процесса подкачки.

Процесс предварительной подкачки может быть прерван процессором 1. При этом в оперативной памяти 2 сохраняется значение начального индекса и инкремента из памяти 6 адресных данных и ссылка на них из асинхронной команды. Из блока 5 контроллеров считывания данных сохраняется значение регистра 72 итерации цикла, определяющее количество итераций цикла, для которых элементы массивов были считаны в процессор 1 из буферной памяти 3 данных. Текущие значения индексов из памяти 6 адресных данных в оперативной памяти 2 не сохраняются. Текущее значение каждого индекса из памяти 6 адресных данных вычисляются процессором 1 заново при возврате из прерывания как сумма начального индекса и произведения величины инкремента на количество итераций из регистра 72 итераций цикла. Вычисленные значения индексов записываются в памяти 6 адресных данных и используются для вычисления адресов обращения к оперативной памяти 2. Это дает возможность продолжить подкачку данных в буферную память 3 данных с той итерации цикла, на которой он был прерван.

Таким образом, в предложенном способе и системе обеспечивается решение поставленной технической задачи.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выборки команд | 1978 |

|

SU726533A1 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| ПАРАЛЛЕЛЬНЫЙ ПРОЦЕССОР С ПЕРЕПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 1994 |

|

RU2110088C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ БОРТОВОЙ ИНДИКАТОР | 2000 |

|

RU2162204C1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение относится к вычислительной технике, в частности к способу и системе загрузки данных из оперативной памяти в процессор. Техническим результатом является увеличение производительности процессов загрузки массивов данных путем их асинхронной загрузки с адаптацией к задержкам оперативной памяти. Система содержит процессор, оперативную память, буферную память, блок контроллеров подкачки данных из М контроллеров, блок контроллеров считывания данных из К контроллеров, память адресных данных и память указателей областей. Способ описывает асинхронную загрузку массивов данных с использованием элементов указанной системы. 2 с. и 15 з.п. ф-лы, 9 ил.

| US 5889985 A, 30.03.1999 | |||

| СИСТЕМА ВРЕМЕННОГО ЗАПОМИНАНИЯ ИНФОРМАЦИИ | 1991 |

|

RU2138845C1 |

| УСТРОЙСТВО для ПРОПОРЦИОНАЛЬНОГО СЛ1ЕШИВАНИЯСРЕД | 0 |

|

SU173967A1 |

| УСТРОЙСТВО ДЛЯ ЭЛЕКТРОДИНАМИЧЕСКОГО | 0 |

|

SU334625A1 |

Авторы

Даты

2001-05-10—Публикация

2000-07-20—Подача